| Points missed:  | Student's Name: |  |

|-----------------|-----------------|--|

|                 |                 |  |

| Total score:/10 | 00 points       |  |

East Tennessee State University

Department of Computer and Information Sciences

CSCI 2150 (Tarnoff) – Computer Organization

TEST 2 for Fall Semester, 2005

# Section 001

### Read this before starting!

- The total possible score for this test is 100 points.

- This test is closed book and closed notes.

- All answers must be placed in space provided. Failure to do so may result in loss of points.

- 1 point will be deducted per answer for missing or incorrect units when required. No assumptions will be made for hexadecimal versus decimal, so you should always include the base in your answer.

- If you perform work on the back of a page in this test, indicate that you have done so in case the need arises for partial credit to be determined.

- *Calculators are not allowed.* Use the tables below for any conversions you may need. Leaving numeric equations is fine too.

| Binary | Hex | В |

|--------|-----|---|

| 0000   | 0   |   |

| 0001   | 1   |   |

| 0010   | 2   |   |

| 0011   | 3   |   |

| 0100   | 4   |   |

| 0101   | 5   |   |

| 0110   | 6   |   |

| 0111   | 7   |   |

| Binary | Hex |

|--------|-----|

| 1000   | 8   |

| 1001   | 9   |

| 1010   | A   |

| 1011   | В   |

| 1100   | C   |

| 1101   | D   |

| 1110   | Е   |

| 1111   | F   |

| Power of 2      | Equals |

|-----------------|--------|

| $2^3$           | 8      |

| $2^{4}$         | 16     |

| 2 <sup>5</sup>  | 32     |

| $2^{6}$         | 64     |

| 27              | 128    |

| 28              | 256    |

| 29              | 512    |

| 2 <sup>10</sup> | 1K     |

| $2^{20}$        | 1M     |

| $2^{30}$        | 1G     |

| $2^{30}$        |        |

"Fine print"

#### Academic Misconduct:

Section 5.7 "Academic Misconduct" of the East Tennessee State University Faculty Handbook, June 1, 2001:

"Academic misconduct will be subject to disciplinary action. Any act of dishonesty in academic work constitutes academic misconduct. This includes plagiarism, the changing of falsifying of any academic documents or materials, cheating, and the giving or receiving of unauthorized aid in tests, examinations, or other assigned school work. Penalties for academic misconduct will vary with the seriousness of the offense and may include, but are not limited to: a grade of 'F' on the work in question, a grade of 'F' of the course, reprimand, probation, suspension, and expulsion. For a second academic offense the penalty is permanent expulsion."

## Short answers – 2 points each

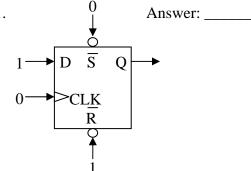

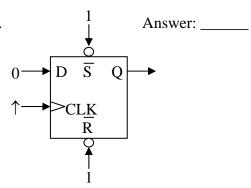

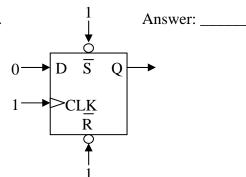

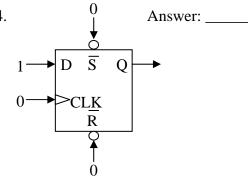

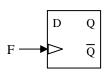

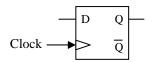

For the following *four* circuits, identify the value of the output Q from the following choices. Consider the D-latch a rising edge triggered latch.

- a.) 1 b.) 0

- c.) Q<sub>0</sub> (stored value of Q)

- d.)  $Q_0$  (inverse of stored value of Q)

1.

2.

3.

4.

- 5. The expression  $A \cdot B \cdot C + A \cdot B \cdot C + A \cdot B$  is not in proper Sum-of-Products format. What boolean algebra operation would you need to apply to correct this?

- a.) It's not a problem; illegal term drops out b.) Distributive Law

- c.) Use "F-O-I-L"

- d.) Take the inverse of the inverse

- e.) DeMorgan's Theorem

- f.) It can't be fixed

- 6. True or False: There exists exactly one pattern of rectangles for every pattern of 1's and 0's in a Karnaugh map.

- 7. True or False: In a Karnaugh map, there must be an adjacent cell for every possible single-variable change. For example, if a Karnaugh map has three input variables, then there must be three cells adjacent to every cell in the map where only one variable value changes in a move to that cell.

- 8. How many cells does a 3 input Karnaugh map have?

- a.) 4

- b.) 6

- c.) 8

- d.) 16

- e.) 24

- f.) 32

- 9. In a 4-variable Karnaugh map, how many input variables (A, B, C, or D) does a product have if its corresponding rectangle of 1's contains 2 cells?

- a.) 1

- b.) 2

- c.) 3

- d.) 4

- e.) Cannot be determined

- 10. A falling edge triggered latch copies data from the D input to the Q output when the clock is:

- a.) a logic 0

- b.) changing from a 1 to a 0

- c.) a logic 1

- d.) changing from a 0 to a 1

- 11. True or False: Both the  $\overline{S}$  and  $\overline{R}$  inputs to a D-latch have priority over the D and clock inputs.

- 12. Make the connections to the latch in the figure to the right that makes a divide-by-two circuit, i.e., divides the frequency F in half at the output Q.

- 13. Which of the following sums produces the truth table to the right?

- a.)  $A+B+\overline{C}$

- b.)  $\overline{A} + \overline{B} + C$

- c.)  $\overline{A} + B + \overline{C}$

- c.)  $\overline{B} + C$

- d.)  $B + \overline{C}$

- d.) None of the above

| A | В | C | X |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

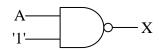

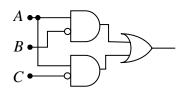

14. Fill in the truth table for the NAND circuit shown below.

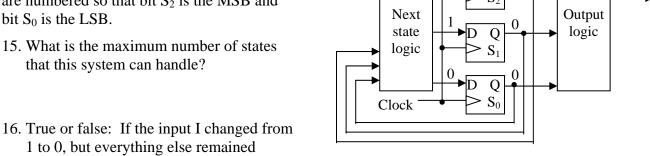

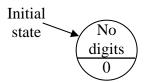

The next four problems use the state machine diagram to the right. Assume that the states are numbered so that bit S2 is the MSB and bit  $S_0$  is the LSB.

15. What is the maximum number of states that this system can handle?

I = 1

- 1 to 0, but everything else remained unchanged, the output of the system would remain unchanged.

- 17. What is the current state of this system? Keep your answer in binary.

- 18. If the clock were to pulse right now, what would the next state be? Keep your answer in binary.

- 19. True or False: Renumbering the states of a state machine has no effect on the "next state" logic for the digital hardware implementation.

- 20. How many latches will a state machine with 22 states require?

- a.) 1

- b.) 2

- c.) 3

- d.) 4

- e.) 5

- f.) 6

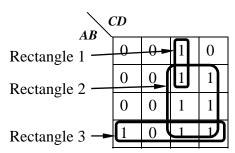

- g.) 7

- 21. If a group of four rows or columns in a Karnaugh map is identified with two variables, it is numbered 00, 01, 11, 10 instead of 00, 01, 10, 11. Why?

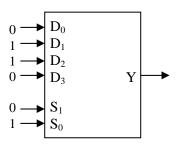

22. For the multiplexer/selector shown to the right, what is the output Y?

23. For the Karnaugh map to the right, identify the problems with each of the three rectangles shown. (2 points each)

Rectangle 1:

Rectangle 2:

Rectangle 3:

## Medium answers – 4 points each

24. Convert the Sum-of\_Products circuit shown below to NAND-NAND logic, i.e., a circuit that contains nothing but NAND gates (and possible inverters at inputs).

25. Complete the truth table to the right with the values for the following Sum-of-Products expression:

$$X = (\overline{A} \cdot C) + (A \cdot B \cdot \overline{C}) + (A \cdot \overline{B} \cdot \overline{C})$$

| A | В | C | X |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

26. In the Karnaugh map to the right, draw the best pattern of rectangles you can. *Do not derive the SOP expression.*

| $\setminus$ CD |    |    |    |    |  |  |

|----------------|----|----|----|----|--|--|

| AB             | 00 | 01 | 11 | 10 |  |  |

| 00             | 1  | 1  | 1  | 1  |  |  |

| 01             | 0  | 0  | 0  | X  |  |  |

| 11             | 0  | 1  | 0  | 1  |  |  |

| 10             | 1  | 1  | 1  | 1  |  |  |

27. Create a Karnaugh map from the truth table below. Do not worry about making the rectangles.

| A | В | C | X |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

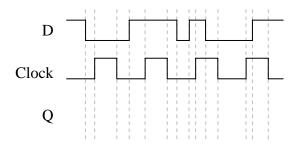

28. Show the D latch output waveform Q based on the inputs D,  $\overline{S}$ ,  $\overline{R}$ , and clock indicated in the graph to the right. Assume the latch captures on the rising edge. (The figure below is just for a reference.)

Longer answers - Points vary per problem

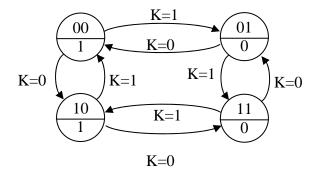

29. Make the state diagram that will output a '1' when the sequence '010' is detected in a serial stream of bits. For example, if the following binary stream is received:

then 1's will be output here. (Notice that the last zero of the second pattern is shared with the first zero of the third pattern.) At all other times, the system will output zeros. Label the input D. (8 points)

30. Derive the minimum SOP expression from the Karnaugh map below. (6 points)

| $\setminus C$ | D  |    |    |    |

|---------------|----|----|----|----|

| AB            | 00 | 01 | 11 | 10 |

| 00            | 1  | 0  | 0  | 1  |

| 01            | 0  | 0  | 0  | 0  |

| 11            | 0  | 0  | 1  | 1  |

| 10            | 1  | 0  | 1  | 1  |

31. Create the next state truth table and the output truth table for the state diagram to the right. Use the variable names  $S_1$  and  $S_0$  to represent the most significant and least significant bits respectively of the binary number identifying the state. Label the output 'X'. (8 points)

32. The three Boolean expressions below represent the *next state bits*  $(S_0'$  and  $S_1')$  and the *output bit* X based on the *current state*  $(S_0$  and  $S_1)$  and the *input* A. Draw the logic circuit for the state machine including the latches and output circuitry. Be sure to label the latch inputs and other *signals*.

(8 points)

$$S_0' = \overline{S}_1 \cdot A$$

$S_1' = \overline{S}_0 \cdot A$   $X = S_1 \cdot \overline{S}_0$