### **Estimating Delays**

- Would be nice to have a "back of the envelope" method for sizing gates for speed

- ▶ Logical Effort

- ▶ Book by Sutherland, Sproull, Harris

- Chapter 1 is on our web page

### **Gate Delay Model**

- ▶ First, normalize a model of delay to dimensionless units to isolate fabrication effects

- $\rightarrow$  d<sub>abs</sub> = d  $\tau$

- $\blacktriangleright \ \tau$  is the delay of a minimum inverter driving another minimum inverter with no parasitics

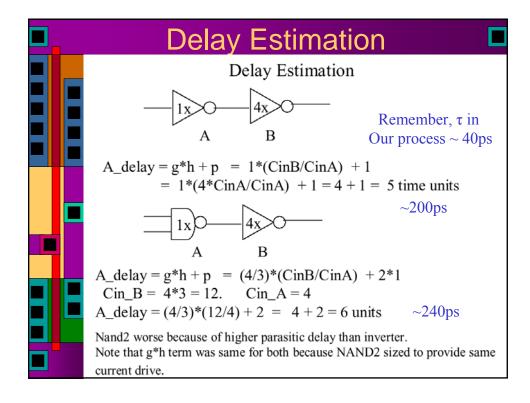

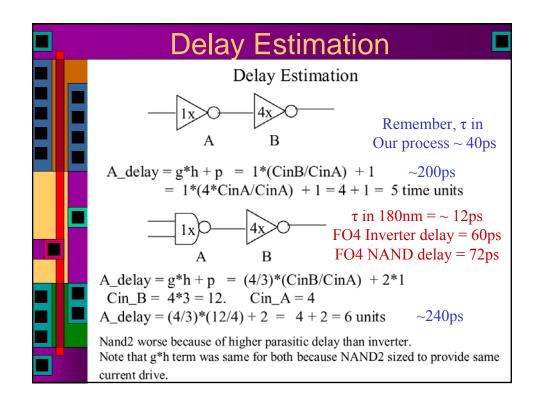

- ▶ In a 0.6u process, this is approx 40ps

- Now we can think about delay in terms of d and scale it to whatever process we're building the circuit in

### Gate Delay

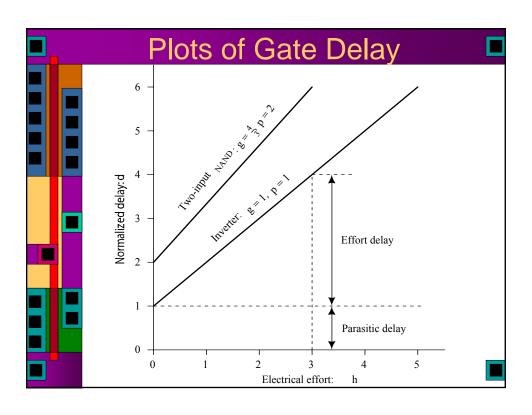

- ▶ Delay of a gate d has two components

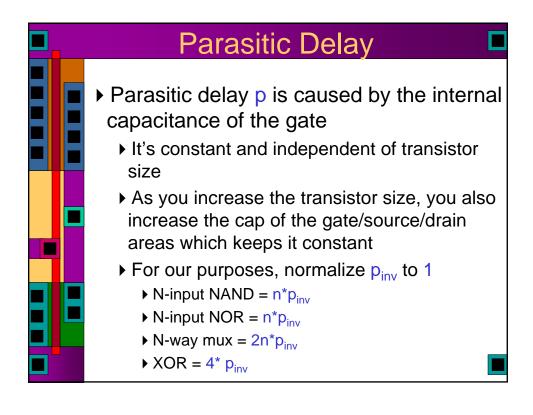

- ▶ A fixed part called parasitic delay p

- ▶ A part proportional to the load on the output called the *effort delay* or *stage effort* f

- ▶ Total delay is measured in units of  $\tau$ , and is sum of these delays

- $\rightarrow$  d = f + p

### **Effort Delay**

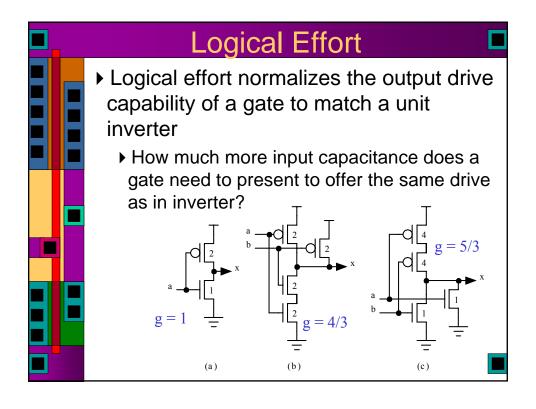

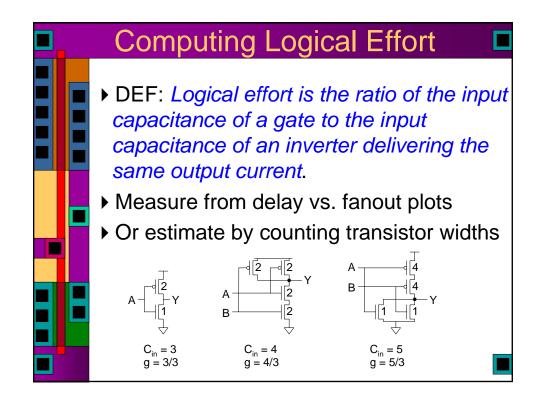

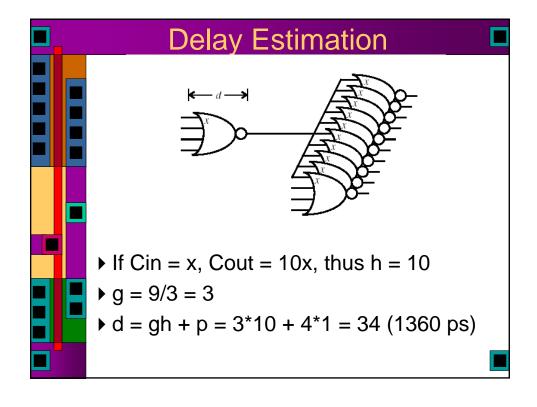

- ▶ The effort delay (due to load) can be further broken down into two terms

- ▶ f = g \* h

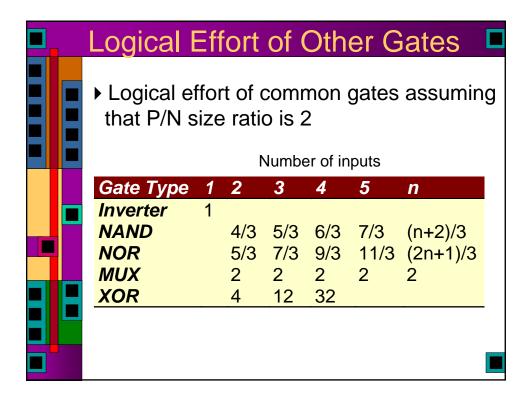

- ▶ g = logical effort which captures properties of the gate's structure

- ▶ h = electrical effort which captures properties of load and transistor sizes

- harpoonup harp

- $\blacktriangleright$   $\textbf{C}_{\text{out}}$  is capacitance that loads the output

- ▶ C<sub>in</sub> is capacitance presented at the input

- $\rightarrow$  So, d = gh + p

### Example: FO4 Inverter

▶ Estimate the delay of a fanout-of-4 (FO4) inverter

Logical Effort: g =

Electrical Effort: h =

Parasitic Delay: p =

Stage Delay: d =

### Example: FO4 Inverter

► Estimate the delay of a fanout-of-4 (FO4) inverter

The FO4 delay is about

200 ps in 0.6 μm process

Logical Effort: g = 1

60 ps in a 180 nm process

Electrical Effort: h = 4

f/3 ns in an  $f \mu m$  process

Parasitic Delay: p = 1

Stage Delay: d = gh + p = 5

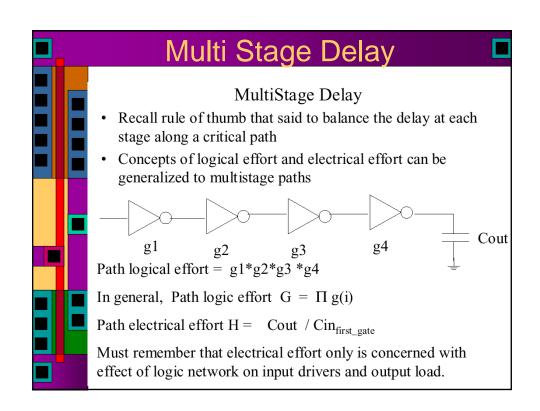

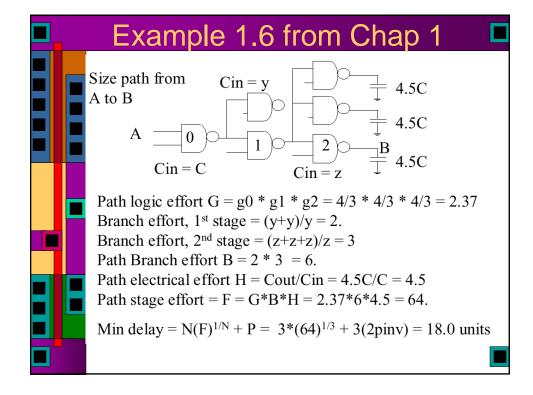

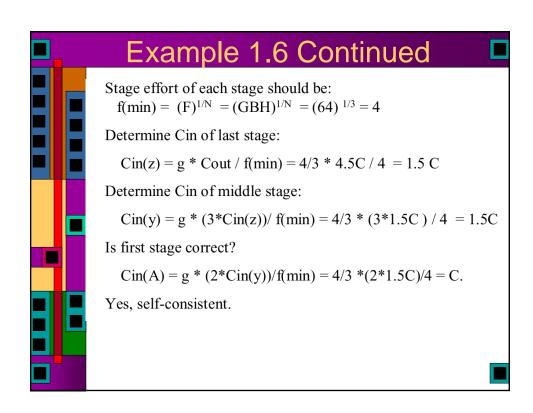

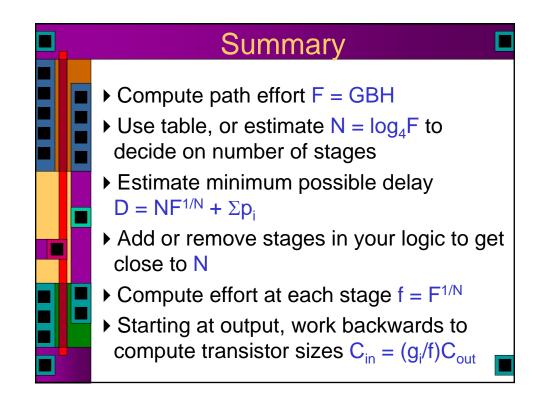

### Summary — multistage networks Logical effort generalizes to multistage networks Path Logical Effort $G = \prod g_i$ Path Electrical Effort $H = \frac{C_{out-path}}{C_{in-path}}$ Path Effort $F = \prod f_i = \prod g_i h_i$ Can we write F = GH?

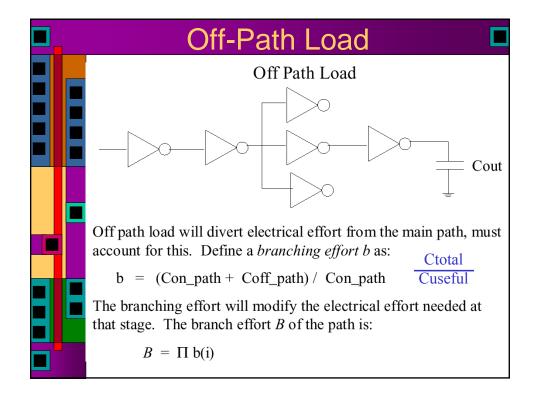

### **Branching Effort**

Accounts for branching between stages in path

$$b = \frac{C_{\text{on path}} + C_{\text{off path}}}{C_{\text{on path}}}$$

$$B = \prod b_i$$

Note:

$$\prod h_i = BH$$

Now we compute the path effort

### Multistage Delays

▶ Path Delay

$$D = \sum d_i = D_F + P$$

### **Designing Fast Circuits**

$$D = \sum d_i = D_F + P$$

Delay is smallest when each stage bears same effort

$$\hat{f} = g_i h_i = F^{\frac{1}{N}}$$

Thus minimum delay of N stage path is

$$D = NF^{\frac{1}{N}} + P$$

This is a key result of logical effort

- ▶ Find fastest possible delay

- ▶ Doesn't require calculating gate sizes

### Minimizing Path Delay

The absolute delay will have the parasitic delays of each stage summed together.

However, can *focus on just Path effort F* for minimization purposes since parasitic delays are constant.

For an N-stage network, the path delay is least when each stage in the path bears the same stage effort.

$$f(min) = g(i) * h(i) = F^{1/N}$$

Minimum achievable path delay

$$D(min) = N * F^{1/N} + P$$

Note that if N=1, then d = f + p, the original single gate equation.

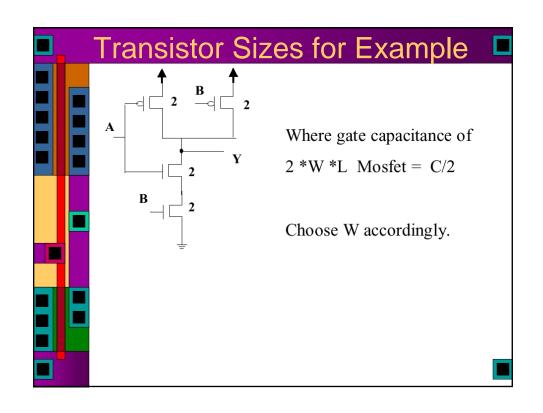

### **Choosing Transistor Sizes**

Remember that the stage effort h(i) is related to transistor sizes.

$$f(min) = g(i) * h(i) = F^{1/N}$$

So

$$h(i) \min = F^{1/N} / g(i)$$

To size transistors, start at end of path, and compute:

$$Cin(i) = gi * Cout(i) / f(min)$$

Once Cin(i) is know, can distribute this among transistors of that stage.

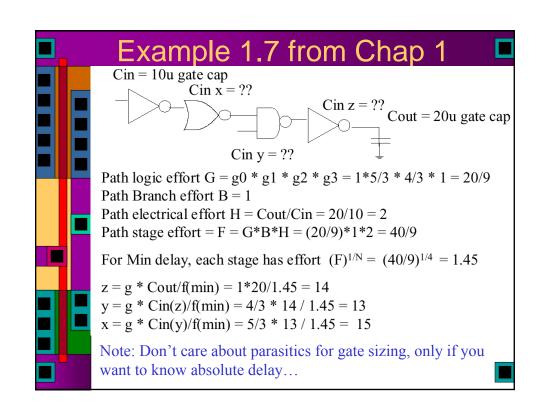

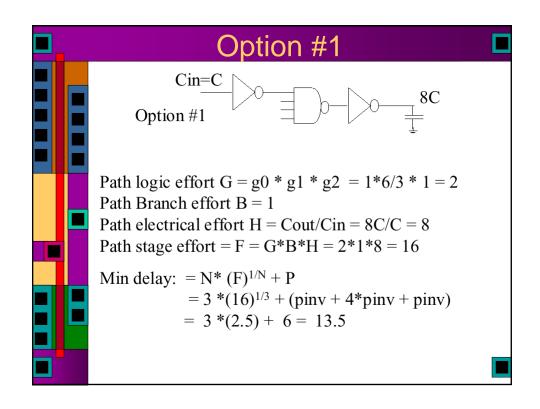

### Example

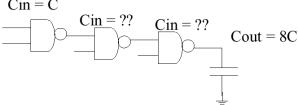

Cin = C

$$\frac{\text{Cin} = ??}{0} \frac{\text{Cin} = ??}{1} \frac{\text{Cout} = C}{2}$$

Size the transistors of the nand2 gates for the three stages shown.

Path logic effort =

$$G = g0 * g1 * g2 = 4/3 * 4/3 * 4/3 = 2.37$$

Branching effort B = 1.0 (no off-path load)

Electrical effort

$$H = Cout/Cin = C/C = 1.0$$

Min delay achievable =

$$3* (G*B*H)^{1/3} + 3 (2*pinv)$$

$$= 3 * (2.37*1*1)^{1/3} + 3 (2*1.0) = 10.0$$

The effort of each stage will be:

f min =

$$(G*B*H)^{1/3} = (2.37*1.0*1.0)^{1/3} = 1.33 = 4/3$$

Cin of last gate should equal:

Cin last gate (min) = gi \* Cout (i) / f(min)

=

$$4/3 * C / (4/3) = C$$

Cin of middle gate should equal:

Cin middle gate = gi \* Cin last gate / f(min)

=

$$4/3 * C/ (4/3) = C$$

All gates have same input capacitance, distribute it among transistors.

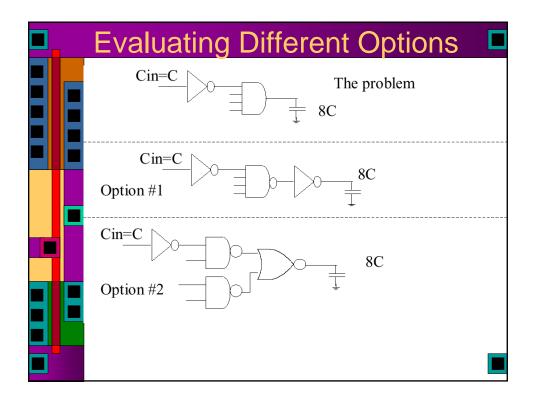

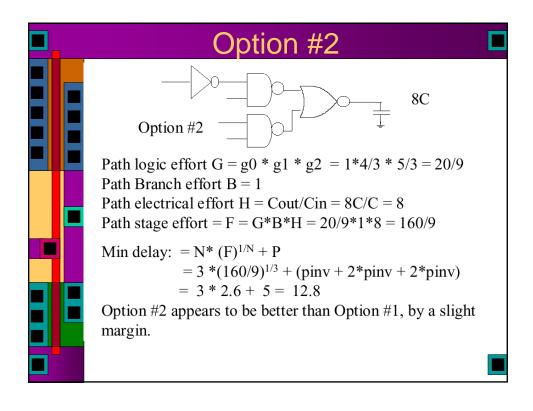

### Another Example, Larger Load

Let Load = 8C, what changes?

$$Cin = C$$

Size the transistors of the nand2 gates for the three stages shown.

Path logic effort =

$$G = g0 * g1 * g2 = 4/3 * 4/3 * 4/3 = 2.37$$

Branching effort B = 1.0 (no off-path load)

Electrical effort

$$H = Cout/Cin = 8C/C = 8.0$$

Min delay achievable =

$$3* (G*B*H)^{1/3} + 3 (2*pinv)$$

=  $3*(2.37*1*8)^{1/3} + 3 (2*1.0) = 14.0$

### 8C Load Example Cont.

The effort of each stage will be:

f min =

$$(G*B*H)^{1/3} = (2.37*1.0*8)^{1/3} = 2.67 = 8/3$$

Cin of last gate should equal:

Cin last gate (min) =

$$gi * Cout (i) / f(min)$$

=  $4/3 * 8C / (8/3) = 4C$

Cin of middle gate should equal:

Cin middle gate = gi \* Cin last gate / f(min)

=

$$4/3 * 4C/(8/3) = 2C$$

Note that each stage gets progressively larger, as is typical with a multi-stage path driving a large load.

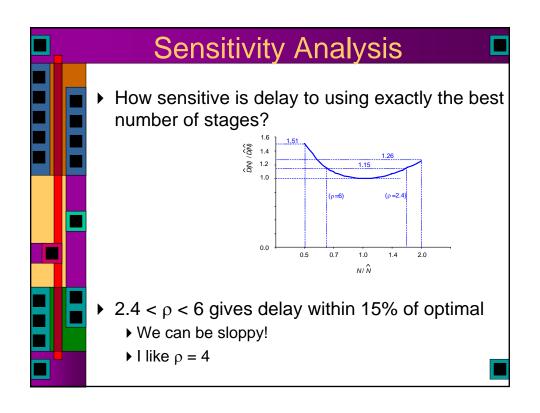

### How many stages? In all cases: G = 1, B = 1, and H = 25 Path delay is N(25)<sup>1/N</sup> + N P<sub>inv</sub> N = 1, D = 26 units N = 3, D = 11.8 units N = 5, D = 14.5 units Since N=3 is best, each stage will bear an effort of (25)<sup>1/3</sup> = 2.9 So, each stage is ~3x larger than the last In general, the best stage effort is between 3 and 4 (not e as often stated) The e value doesn't use parasitics...

| CI | <ul> <li>Noosing the Best # of Stages</li> <li>You can solve the delay equations to determine the number of stages N that will achieve the minimum delay</li> <li>Napproximate by Log₄F</li> </ul> |                            |                                                                         |                   |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|-------------------|--|

|    | Path Effort<br>F                                                                                                                                                                                   | Best<br>N                  | Min Delay<br>D                                                          | Stage effort<br>f |  |

|    | 22.3-82.2<br>82.2-300                                                                                                                                                                              | 1<br>2<br>3<br>4<br>5<br>6 | 1.0-6.8<br>6.8-11.4<br>11.4-16.0<br>16.0-20.7<br>20.7-25.3<br>25.3-29.8 | 3.0-4.2           |  |

## String of inverters driving an off-chip load Pad cap and load = 40pf Equivalent to 20,000 microns of gate cap Assume first inverter in chain has 7.2u of input cap How many stages in inv chain? H = 20,000/7.2 = 2777 From the table, 6 stages is best Stage effort = f = (2777)<sup>1/6</sup> = 3.75 Path delay D = 6\*3.75 +6\*Pinv = 28.5 D = 1.14ns if τ = 40ps

# Limits of Logical Effort Chicken and egg problem Need path to compute G But don't know number of stages without G Simplistic delay model Neglects input rise time effects Interconnect Iteration required in designs with wire Maximum speed only Not minimum area/power for constrained delay