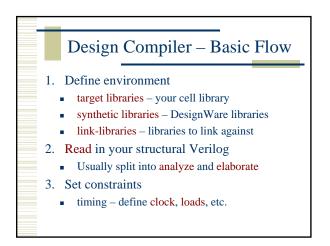

## Design Compiler - Basic Flow

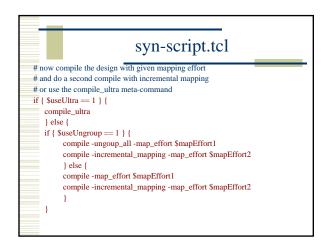

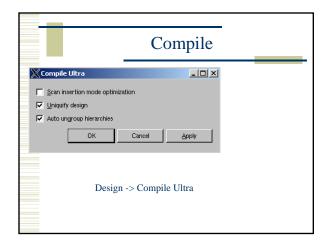

- 4. Compile the design

- compile or compile\_ultra

- Does the actual synthesis

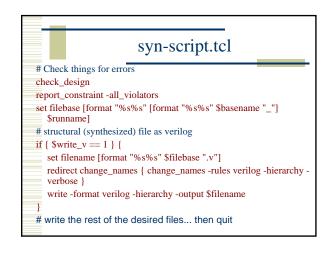

- 5. Write out the results

- Make sure to change\_names

- Write out structural verilog, report, ddc, sdc files

## What beh2str leaves out...

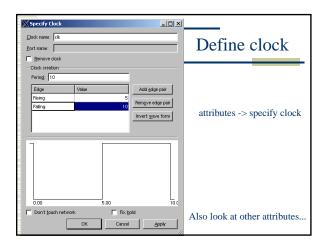

- Timing!

- No clock defined so no target speed

- No input drive defined so assume infinite drive

- No output load define so assume something

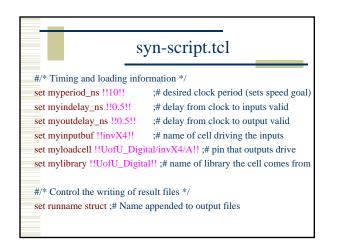

|                      | syn-script.tcl                              |

|----------------------|---------------------------------------------|

| #/* the following c  | ontrol which output files you want. They */ |

| #/* should be set to | o 1 if you want the file, 0 if not */       |

| set write_v 1        | ;# compiled structural Verilog file         |

| set write_db 0       | ;# compiled file in db format (obsolete)    |

| set write_ddc 0      | ;# compiled file in ddc format (XG-mode)    |

| set write_sdf 0      | ;# sdf file for back-annotated timing sim   |

| set write_sdc 1      | ;# sdc constraint file for place and route  |

| set write_rep 1      | ;# report file from compilation             |

| set write_pow 0      | ;# report file for power estimate           |

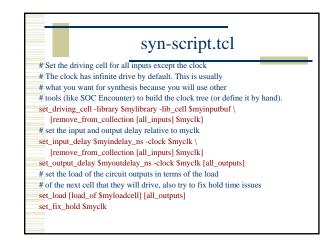

| syn-script.tcl                                                    |

|-------------------------------------------------------------------|

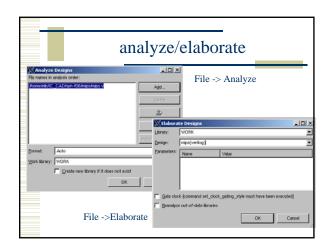

| # analyze and elaborate the files                                 |

| analyze -format \$fileFormat -lib WORK \$myfiles                  |

| elaborate \$basename -lib WORK -update                            |

| current_design \$basename                                         |

| # The link command makes sure that all the required design        |

| # parts are linked together.                                      |

| # The uniquify command makes unique copies of replicated modules. |

| link                                                              |

| uniquify                                                          |

| # now you can create clocks for the design                        |

| if { $virtual == 0$ } {                                           |

| create_clock -period \$myperiod_ns \$myclk                        |

| } else {                                                          |

| create_clock -period \$myperiod_ns -name \$myclk                  |

| }                                                                 |

- compile

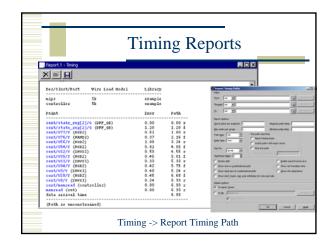

- write out results

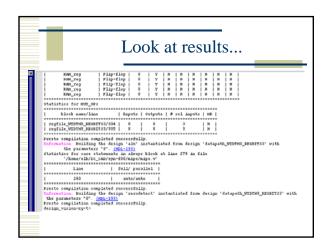

| W1                                             | rite Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data arrival time                              | 6.93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (Path is unconstrained)<br>design_vision-xg-t> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| History                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| esign_vision-xg-t> change_names -rules verile  | og -hierarohy > ohange_names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ,                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| change_names                                   | Los n Charlen An                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                | DW_INV_set_init_struct.doccounter.vft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                | 20056         00/jm_yrt/jmt/pitt         0xetr_jhut.dk.         0           246-51         Mm_flown(jhut.)         0xetr_jhut.h.         0           264-61         Mm_flown(jhut.)         0xetr_jhut.h.         0           264-61         Mm_flown(jhut.)         0xetr_jhut.h.         0           264-61         Mm_flown(jhut.)         0xetr_jhut.h.         0           264-61         Mm_flown(jhut.h.         0xetr_jhut.h.         0           266         0xetr_jhut.h.         0xetr_jhut.h.         0           266         0xetr_jhut.h.         0xetr_jhut.h.         0 |

|                                                | ab-51         Men_Benerij.stv.tv         covter_stv.tv         se           abevrij.1750-0         QUOL_Deptado         decrementer.v         se           abevrij.1850-0         Detexoral v         decrementer_struct dat.         se           28b.g.file         controller v         decrementer_struct dat.         se                                                                                                                                                                                                                                                           |

| etine all                                                                         | ×           |

|-----------------------------------------------------------------------------------|-------------|

| Basic Advanced                                                                    |             |

| Mode<br>Full Incremental Prototyping                                              | Place cells |

| Options  F Run Timing Driven Placement  F Reorder Scan Connection                 |             |

| Optimization Options Include Pre-Place Optimization Include In-Place Optimization |             |

| QK Apply Defaults Cancel                                                          |             |

| Place -> Place cells                                                              |             |

|                                                                                   |             |

|                                                                                   |             |

|                                                                                   |             |

| Service and the service of the servi | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

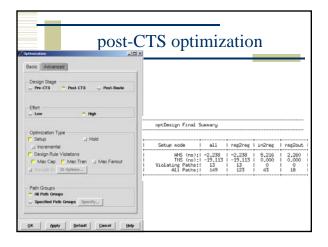

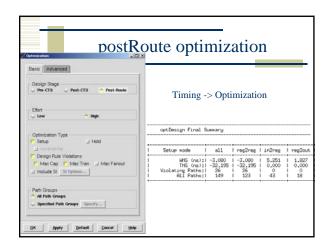

| Basic Advanced<br>Design Stage<br>Pre-CTS Prot-CTS Post-Roole<br>Effort<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Timing -> Optimization                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | optDesign Final Summary                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cotimization Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Setup acde   all   reg2reg   in2reg   reg2cut   in4                                                                                                                                                                                                                                                                                                                                                                                                  |

| incremental Cosign Rule Violations Max Cap Max Tran Max Fanout Grounde Si Bit Optimum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MMS         (ns):         -2,063         -2,063         3,996         3,911           TMS         (ns):         -2,063         -2,063         3,996         3,911         1           TMS         (ns):         -16,067         -16,057         0,000         0,000         0           Valoitang Paths:         12         12         0         0         0         0           All Paths:         149         123         43         18         18 |

| Path Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

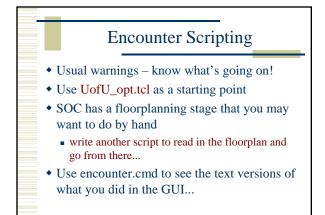

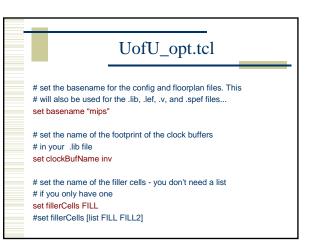

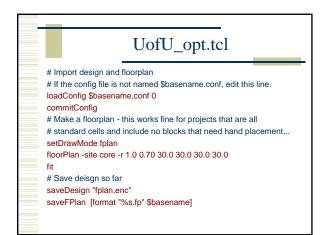

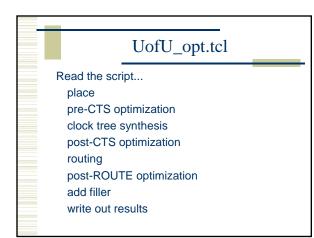

|         | UofU_opt.tcl                                                                       |

|---------|------------------------------------------------------------------------------------|

| ######  |                                                                                    |

|         | may not have to change things below this line - but check!                         |

| #       |                                                                                    |

|         | may want to do floorplanning by hand in which case you<br>some modification to do! |

| # nave  |                                                                                    |

|         |                                                                                    |

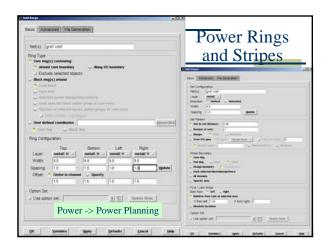

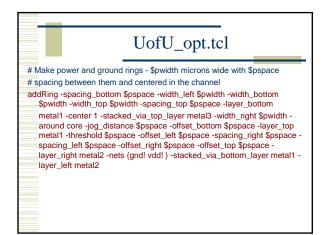

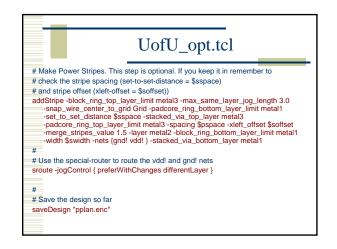

| # Set s | ome of the power and stripe parameters - you can change                            |

| # these | e if you like - in particular check the stripe space (sspace)                      |

| # and s | stripe offset (soffset)!                                                           |

| set pwi | dth 9.9                                                                            |

| set psp | pace 1.8                                                                           |

| set swi | dth 4.8                                                                            |

| set ssp | ace 249                                                                            |

| set sof | fset 126                                                                           |

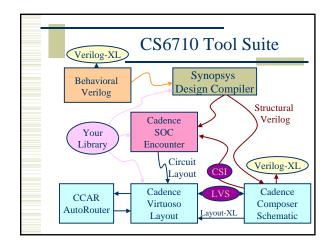

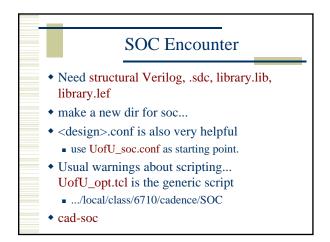

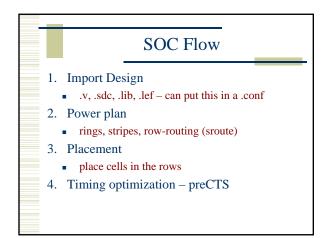

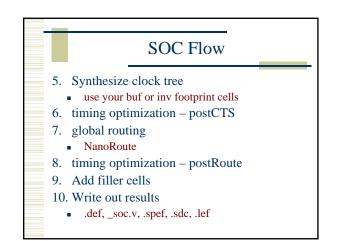

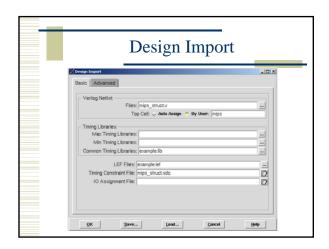

- Behavioral -> structural -> layout

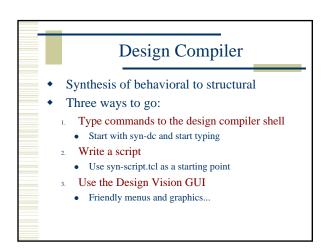

- Can be automated by scripting, but make sure you know what you're doing

- on-line tutorials for TCL

- Google "tcl tutorial"

- Synopsys documentation for design\_compiler

- encounter.cmd (and documentation) for SOC

- End up with placed and routed core layout

- or BLOCK for later use...