# Section 5 Functional Modeling

This chapter specifies the functional modeling for synthesis, formal verification, and simulation.

# 5.1 Combinational functions

This section defines the different types of combinational functions in ALF.

### 5.1.1 Combinational logic

Combinational logic can be described by continuous assignments of boolean values (*True* or *False*) to output variables as a function of boolean values of input variables. Such functions can be expressed in either boolean expression format or statetable format.

Let us consider an arbitrary continuous assignment

$z = f(a_1 \ldots \ldots a_n)$

In a dynamic or simulation context, the left-hand side (LHS) variable z is evaluated whenever there is a change in one of the right-hand side (RHS) variables  $a_i$ . No storage of previous states is needed for dynamic simulation of combinational logic.

### 5.1.2 Boolean operators on scalars

Table 5-1, Table 5-2, and Table 5-3 list unary, binary, and ternary boolean operators on scalars.

| Operator | Description       |

|----------|-------------------|

| 1,~      | logical inversion |

Table 5-1 : Unary boolean operators

| Table | 5-2: | Binary | boolean | operators |

|-------|------|--------|---------|-----------|

|-------|------|--------|---------|-----------|

| Operator | Description              |

|----------|--------------------------|

| &&, &    | logical AND              |

| ,        | logical OR               |

| ~^       | logic equivalence (XNOR) |

| *        | logic anti valence (XOR) |

| Operator | Description                                                                           |

|----------|---------------------------------------------------------------------------------------|

| ?        | boolean condition operator for construction of combi-<br>national if-then-else clause |

| :        | boolean else operator for construction of combinational if-then-else clause           |

#### Table 5-3 : Ternary operator

Combinational if-then-else clauses are constructed as follows:

<cond1>? <value1>: <cond2>? <value2>: <cond3>? <value3>: <default\_value>

If condl evaluates to boolean *True*, then value1 is the result; else if cond2 evaluates to boolean *True*, then value2 is the result; else if cond3 evaluates to boolean *True*, then value3 is the result; else default\_value is the result of this clause.

### 5.1.3 Boolean operators on words

Table 5-4 and Table 5-5 list unary and binary reduction operators on words (logic variables with one or more bits). The result of an expression using these operators shall be a logic value.

| Operator | Description   |

|----------|---------------|

| &        | AND all bits  |

| ~&       | NAND all bits |

|          | OR all bits   |

| ~        | NOR all bits  |

| *        | XOR all bits  |

| ~^       | XNOR all bits |

#### Table 5-4 : Unary reduction operators

#### Table 5-5 : Binary reduction operators

| Operator | Description                      |

|----------|----------------------------------|

| ==       | equality for case comparison     |

| ! =      | non-equality for case comparison |

| >        | greater                          |

| <        | smaller                          |

| >=       | greater or equal                 |

| <=       | smaller or equal                 |

Table 5-6 and Table 5-7 list unary and binary bitwise operators. The result of an expression using these operators shall be an array of bits.

| Operator | Description       |

|----------|-------------------|

| 2        | bitwise inversion |

#### Table 5-6 : Unary bitwise operators

#### Table 5-7 : Binary bitwise operators

| Operator | Description  |

|----------|--------------|

| &        | bitwise AND  |

|          | bitwise OR   |

| ^        | bitwise XOR  |

| ~^       | bitwise XNOR |

The following arithmetic operators, listed in Table 5-8, are also defined for boolean operations on words. The result of an expression using these operators shall be an extended array of bits.

#### Table 5-8 : Binary operators

| Operator | Description     |

|----------|-----------------|

| <<       | shift left      |

| >>       | shift right     |

| +        | addition        |

| -        | subtraction     |

| *        | multiplication  |

| 1        | division        |

| %        | modulo division |

The arithmetic operations addition, subtraction, multiplication, and division shall be *unsigned* if all the operands have the datatype *unsigned*. If any of the operands have the datatype signed, the operation shall be *signed*. See Table 6-23 for the DATATYPE definitions.

### 5.1.4 Operator priorities

The priority of binding operators to operands in boolean expressions shall be from strongest to weakest in the following order:

- 1. unary boolean operator  $(!, \sim, \&, \sim\&, |, \sim|, \uparrow, \sim^{\wedge})$

- 2. XNOR (~^), XOR (^), relational (>, <, >=, <=, ==, !=), shift (<<, >>)

- 3. AND (&, &&), NAND ( $\sim\&$ ), multiply (\*), divide (/), modulus (%)

- 4. Or (|, ||), NOR (~|), add (+), subtract (-)

- 5. ternary operators (?, :)

### 5.1.5 Datatype mapping

Logical operations can be applied to scalars and words. For that purpose, the values of the operands are reduced to a system of three logic values in the following way:

- н has the logic value 1

- $\tt L$  has the logic value  $\tt 0$

- w, z,  ${\tt u}$  have the logic value  ${\tt x}$

- A word has the logic value 1, if the unary OR reduction of all bits results in 1

- A word has the logic value 0, if the unary OR reduction of all bits results in 0

- A word has the logic value x, if the unary OR reduction of all bits results in x

Case comparison operations can also be applied to scalars and words. For scalars, they are defined in Table 5-9.

| A | В                | A==B | A!=B | A>B | A <b< th=""></b<> |

|---|------------------|------|------|-----|-------------------|

| 1 | 1                | 1    | 0    | 0   | 0                 |

| 1 | Н                | 0    | 1    | X   | X                 |

| 1 | 0                | 0    | 1    | 1   | 0                 |

| 1 | L                | 0    | 1    | 1   | 0                 |

| 1 | W, U, Z, X       | 0    | 1    | X   | 0                 |

| Н | 1                | 0    | 1    | X   | X                 |

| Н | Н                | 1    | 0    | 0   | 0                 |

| Н | 0                | 0    | 1    | 1   | 0                 |

| Н | L                | 0    | 1    | 1   | 0                 |

| Н | W, U, Z, X       | 0    | 1    | Х   | 0                 |

| 0 | 1                | 0    | 1    | 0   | 1                 |

| 0 | Н                | 0    | 1    | 0   | 1                 |

| 0 | 0                | 1    | 0    | 0   | 0                 |

| 0 | L                | 0    | 1    | Х   | X                 |

| 0 | W, U, Z, X       | 0    | 1    | 0   | X                 |

| L | 1                | 0    | 1    | 0   | 1                 |

| L | Н                | 0    | 1    | 0   | 1                 |

| L | 0                | 0    | 1    | X   | X                 |

| L | L                | 1    | 0    | 0   | 0                 |

| L | W, U, Z, X       | 0    | 1    | 0   | X                 |

| Х | X                | 1    | 0    | X   | X                 |

| X | U                | X    | X    | X   | X                 |

| Х | 0, 1, H, L, W, Z | 0    | 1    | X   | X                 |

Table 5-9 : Case comparison operators

| Α | В                        | A==B | A!=B | A>B | A <b< th=""></b<> |

|---|--------------------------|------|------|-----|-------------------|

| W | W                        | 1    | 0    | Х   | X                 |

| W | U                        | Х    | Х    | Х   | X                 |

| W | 0, 1, H, L, X, Z         | 0    | 1    | Х   | X                 |

| Ζ | Ζ                        | 1    | 0    | Х   | X                 |

| Ζ | U                        | Х    | Х    | Х   | X                 |

| Ζ | 0, 1, H, L, X, W         | 0    | 1    | Х   | X                 |

| U | 0, 1, H, L,<br>X,W, Z, U | Х    | Х    | Х   | Х                 |

| Table 5-9 : | Case | comparison | operators, | continued |

|-------------|------|------------|------------|-----------|

|-------------|------|------------|------------|-----------|

For word operands, the operations > and < are performed after reducing all bits to the 3-value system first and then interpreting the resulting number according to the datatype of the operands. For example, if datatype is *signed*, 'b1111 is smaller than 'b0000; if datatype is *unsigned*, 'b1111 is greater than 'b0000. If two operands have the same value 'b1111 and a different datatype, the unsigned 'b1111 is greater than the signed 'b1111.

The operations >= and <= are defined in the following way:

(a >= b) === (a > b) || (a == b) (a <= b) === (a < b) || (a == b)

### 5.1.6 Rules for combinational functions

If a boolean expression evaluates *True*, the assigned output value is 1. If a boolean expression evaluates *False*, the assigned output value is 0. If the value of a boolean expression cannot be determined, the assigned output value is x. Assignment of values other than 1, 0, or x needs to be specified explicitly.

For evaluation of the boolean expression, input value 'bH shall be treated as 'b1. Input value 'bL shall be treated as 'b0. All other input values shall be treated as 'bx.

Examples:

In equation form, these rules can be expressed as follows.

```

BEHAVIOR {

Z = A;

}

```

is equivalent to

```

BEHAVIOR {

Z = A ? 'b1 : 'b0;

}

```

More explicitly, this is also equivalent to

```

BEHAVIOR {

Z = (A=='b1 || A=='bH)? 'b1 : (A=='b0 || A=='bL)? 'b0 : 'bX;

}

```

In table form, this can be expressed as follows:

```

STATETABLE {

Α

:

Z;

?

:

(A);

}

```

which is equivalent to

}

STATETABLE { Α : Z; 0 : 0; : 1 1;

More explicitly, this is also equivalent to

```

STATETABLE {

z;

Α

:

0

:

0;

L

:

0;

1

:

1;

Η

:

1;

Х

:

X;

W

:

X;

Ζ

:

X;

U

:

X;

}

```

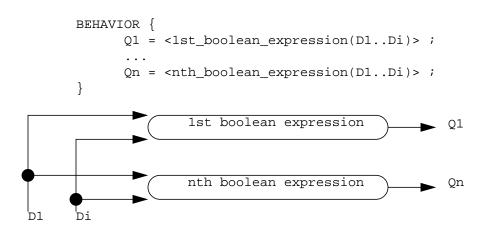

#### 5.1.7 **Concurrency in combinational functions**

Multiple boolean assignments in combinational functions are understood to be concurrent. The order in the functional description does not matter, as each boolean assignment describes a piece of a logic circuit. This is illustrated in Figure 5-1.

# 5.2 Sequential functions

This section defines the different types of sequential functions in ALF.

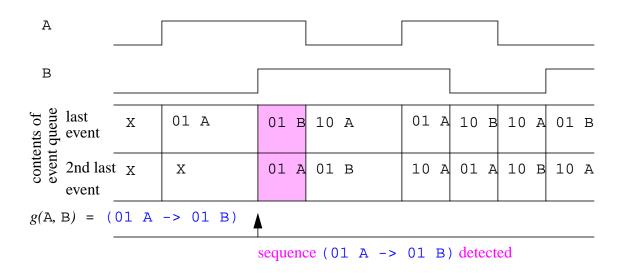

### 5.2.1 Level-sensitive sequential logic

In sequential logic, an output variable  $z_j$  can also be a function of itself, i.e., of its previous state. The sequential assignment has the form

$$z_j = f(a_1 \dots a_n, z_1 \dots z_m)$$

The RHS cannot be evaluated continuously, since a change in the LHS as a result of a RHS evaluation shall trigger a new RHS evaluation repeatedly, unless the variables attain stable values. Modeling capabilities of sequential logic with continuous assignments are restricted to systems with oscillating or self-stabilizing behavior.

However, using the concept of *triggering conditions* for the LHS enables everything which is necessary for modeling *level-sensitive* sequential logic. The expression of a triggered assignment can look like this:

@  $g(b_1 \dots b_k) z_j = f(a_1 \dots a_n, z_1 \dots z_m)$

The evaluation of f is activated whenever the *triggering function* g is *True*. The evaluation of g is self-triggered, i.e. at each time when an argument of g changes its value. If g is a boolean expression like f, we can model all types of *level-sensitive sequential logic*.

During the time when g is *True*, the logic cell behaves exactly like combinational logic. During the time when g is *False*, the logic cell holds its value. Hence, one memory element per state bit is needed.

### 5.2.2 Edge-sensitive sequential logic

In order to model *edge-sensitive sequential logic*, notations for logical transitions and logical states are needed.

If the triggering function g is sensitive to logical transitions rather than to logical states, the function g evaluates to *True* only for an infinitely small time, exactly at the moment when the transition happens. The sole purpose of g is to trigger an assignment to the output variable through evaluation of the function f exactly at this time.

Edge-sensitive logic requires storage of the previous output state and the input state (to detect a transition). In fact, all implementations of edge-triggered flip-flops require at least two storage elements. For instance, the most popular flip-flop architecture features a master latch driving a slave latch.

Using transitions in the triggering function for value assignment, the functionality of a positive edge triggered flip-flop can be described as follows in ALF:

@ (01 CP) {Q = D;}

which reads "at rising edge of CP, assign Q the value of D".

If the flip-flop also has an asynchronous direct clear pin (CD), the functional description consists of either two concurrent statements or two statements ordered by priority, as shown in Figure 5-2.

// concurrent style

@ (!CD) {Q = 0;}

@ (01 CP && CD) {Q = D;}

// priority (if-then-else) style

@ (!CD) {Q = 0;} : (01 CP) {Q = D;}

#### Figure 5-2: Model of a flip-flop with asynchronous clear in ALF

The following two examples show corresponding simulation models in Verilog and VHDL.

```

// full simulation model

always @(negedge CD or posedge CP) begin

if ( ! CD ) Q <= 0;

else if (CP && !CP_last_value) Q <= D;

else Q <= 1'bx;

end

always @ (posedge CP or negedge CP) begin

if (CP===0 | CP===1'bx) CP_last_value <= CP ;

end

// simplified simulation model for synthesis

always @(negedge CD or posedge CP) begin

if ( ! CD ) Q <= 0;

else Q <= D;

end

```

Figure 5-3: Model of a flip-flop with asynchronous clear in Verilog

```

// full simulation model

process (CP, CD) begin

if (CD = '0') then

Q <= '0';

elsif (CP'last value = '0' and CP = '1' and CP'event) then

Q <= D;

elsif (CP'last_value = '0' and CP = 'X' and CP'event) then

Q <= 'X';

elsif (CP'last_value = 'X' and CP = '1' and CP'event) then

Q <= 'X';

end if;

end process;

// simplified simulation model for synthesis

process (CP, CD) begin

if (CD = '0') then

Q <= '0';

elsif (CP = '1' and CP'event) then

Q <= D;

end if;

end process;

```

#### Figure 5-4: Model of a flip-flop with asynchronous clear in VHDL

The following differences in modeling style can be noticed: VHDL and Verilog provide the list of sensitive signals at the beginning of the process or always block, respectively. The information of level-or edge-sensitivity shall be inferred by if-then-else statements inside the block. ALF shows the level-or-edge sensitivity as well as the priority directly in the triggering expression. Verilog has another particularity: The sensitivity list indicates whether at least one of the triggering signals is edge-sensitive by the use of negedge or posedge. However, it does not indicate which one, since either none or all signals shall have negedge or posedge qualifiers.

Furthermore, posedge is any transition with 0 as initial state *or* 1 as final state. A positive-edge triggered flip-flop shall be inferred for synthesis, yet this flip-flop shall only work correctly if both the initial state is 0 *and* the final state is 1. Therefore, a simulation model for verification needs to be more complex than the model in the synthesizeable RTL code.

In Verilog, the extra non-synthesizeable code needs to also reproduce the relevant previous state of the clock signal, whereas VHDL has built-in support for last\_value of a signal.

### 5.2.3 Unary operators for vector expressions

A transition operation is defined using unary operators on a scalar net. The scalar constants (see Figure 11-6) shall be used to indicate the start and end states of a transition on a scalar net.

*bit bit // apply transition from bit value to bit value*

#### For example,

01 is a transition from 0 to 1.

No whitespace shall be allowed between the two scalar constants. The transition operators shown in Table 5-10 shall be considered legal.

| Operator | Description                                                                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------|

| 01       | signal toggles from 0 to 1                                                                                      |

| 10       | signal toggles from 1 to 0                                                                                      |

| 00       | signal remains 0                                                                                                |

| 11       | signal remains 1                                                                                                |

| 0?       | signal remains 0 or toggles from 0 to arbitrary value                                                           |

| 1?       | signal remains 1 or toggles from 1 to arbitrary value                                                           |

| ?0       | signal remains 0 or toggles from arbitrary value to 0                                                           |

| ?1       | signal remains 1 or toggles from arbitrary value to 1                                                           |

| ??       | signal remains constant or toggles between arbitrary values                                                     |

| 0*       | a number of arbitrary signal transitions, including possibility of constant value, with the initial value 0     |

| 1*       | a number of arbitrary signal transitions, including possibility of constant value, with the initial value 1     |

| ?*       | a number of arbitrary signal transitions, including possibility of constant value, with arbitrary initial value |

| *0       | a number of arbitrary signal transitions, including possibility of constant value, with the final value 0       |

| *1       | a number of arbitrary signal transitions, including possibility of constant value, with the final value 1       |

| *?       | a number of arbitrary signal transitions, including possibility of constant value, with arbitrary final value   |

Table 5-10 : Unary vector operators on bits

Unary operators for transitions can also appear in the STATETABLE.

Transition operators are also defined on words (and can appear the in STATETABLE as well):

'base word 'base word

In this context, the transition operator shall apply transition from first word value to second word value.

For example,

'hA'h5 is a transition of a 4-bit signal from 'b1010 to 'b0101.

No whitespace shall be allowed between *base* and *word*.

The unary and binary operators for transition, listed in Table 5-11 and Table 5-12 respectively, are defined on bits and words.

| Operator | Description                                                         |

|----------|---------------------------------------------------------------------|

| ?-       | no transition occurs                                                |

| ??       | apply arbitrary transition, including possibility of constant value |

| ?!       | apply arbitrary transition, excluding possibility of constant value |

| ?~       | apply arbitrary transition with all bits toggling                   |

Table 5-11 : Unary vector operators on bits or words

### 5.2.4 Basic rules for sequential functions

A sequential function is described in equation form by a boolean assignment with a condition specified by a boolean expression or a vector expression. If the condition evaluates to 1 (*True*), the boolean assignment is activated and the assigned output values follows the rules for combinational functions. If the vector expression evaluates to 0 (*False*), the output variables hold their assigned value from the previous evaluation.

For evaluation of a condition, the value 'bH shall be treated as *True*, the value 'bL shall be treated as *False*. All other values shall be treated as the unknown value 'bx.

Example:

The following behavior statement

```

BEHAVIOR {

@ (E) {Z = A;}

}

```

is equivalent to

```

BEHAVIOR {

@ (E=='bl || E=='bH) {Z = A;}

}

```

The following statetable statement, describing the same logic function

is equivalent to

| STATETABLE | { |   |      |

|------------|---|---|------|

| E          | А | : | Z ;  |

| 0          | ? | : | (Z); |

| L          | ? | : | (Z); |

| 1          | ? | : | (A); |

| Н          | ? | : | (A); |

| }          |   |   |      |

For edge-sensitive and higher-order event sensitive functions, transitions from or to 'bL shall be treated like transitions from or to 'b0, and transitions from or to 'bH shall be treated like transitions from or to 'b1.

Not every transition can trigger the evaluation of a function. The set of vectors triggering the evaluation of a function are called *active vectors*. From the set of active vectors, a set of *inactive vectors* can be derived, which shall clearly not trigger the evaluation of a function. There are is also a set of ambiguous vectors, which can trigger the evaluation of the function.

The set of active vectors is the set of vectors for which both observed states before and after the transition are known to be logically equivalent to the corresponding states defined in the vector expression.

The set of inactive vectors is the set of vectors for which at least one of the observed states before or after the transition is known to be not logically equivalent to the corresponding states defined in the vector expression.

Example:

For the following sequential function

```

@ (01 CP) { Z = A; }

```

the active vectors are

('b0'b1 CP) ('b0'bH CP) ('bL'b1 CP) ('bL'bH CP)

and the inactive vectors are

```

('b1'b0 CP)

('bl'bL CP)

('bl'bX CP)

('bl'bW CP)

('bl'bZ CP)

('bH'b0 CP)

('bH'bL CP)

('bH'bX CP)

('bH'bW CP)

('bH'bZ CP)

('bX'b0 CP)

('bX'bL CP)

('bW'b0 CP)

('bW'bL CP)

('bZ'b0 CP)

('bZ'bL CP)

('bU'b0 CP)

('bU'bL CP)

```

and the ambiguous vectors are

('b0'bX CP) ('b0'bW CP) ('b0'bZ CP) ('bL'bX CP) ('bL'bW CP) ('bL'bZ CP) ('bX'bl CP) ('bW'bl CP) ('bZ'bl CP) ('bX'bH CP) ('bW'bH CP) ('bZ'bH CP) ('bX'bW CP) ('bX'bZ CP) ('bW'bX CP) ('bW'bZ CP) ('bZ'bX CP) ('bZ'bW CP) ('bU'bX CP) ('bU'bW CP) ('bU'bZ CP)

For vectors using exclusively based literals, the set of active vectors is the vector itself, the set of inactive vectors is any vector with at least one different literal, and the set of ambiguous vectors is empty.

Therefore, ALF does not provide a default behavior for ambiguous vectors, since the behavior for each vector can be explicitly defined in vectors using based literals.

### 5.2.5 Concurrency in sequential functions

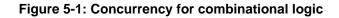

The principle of concurrency applies also for edge-sensitive sequential functions, where the triggering condition is described by a vector expression rather than a boolean expression. In edge-sensitive logic, the target logic variable for the boolean assignment (LHS) can also be an operand of the boolean expression defining the assigned value (RHS). Concurrency implies that the RHS expressions are evaluated immediately *before* the triggering edge, and the values are assigned to the LHS variables immediately *after* the triggering edge. This is illustrated in Figure 5-5.

Figure 5-5: Concurrency for edge-sensitive sequential logic

Statements with multiple concurrent conditions for boolean assignments can also be used in sequential logic. In that case conflicting values can be assigned to the same logic variable. A default conflict resolution is not provided for the following reasons:

- Conflict resolution might not be necessary, since the conflicting situation is prohibited by specification.

- For different types of analysis (e.g., logic simulation), a different conflict resolution behavior might be desirable, while the physical behavior of the circuit shall not change. For instance, pessimistic conflict resolution always assigns x, more accurate conflict resolution first checks whether the values are conflicting. Different choices can be motivated by a trade-off in analysis accuracy and runtime.

- If complete library control over analysis is desired, conflict resolution can be specified explicitly.

Example:

```

BEHAVIOR {

@ ( <condition_1> ) { Q = <value_1>; }

@ ( <condition_2> ) { Q = <value_2>; }

}

```

Explicit pessimistic conflict resolution can be described as follows:

```

BEHAVIOR {

@ ( <condition_1> && <condition_2> ) { Q = 'bX; }

@ ( <condition_1> && ! <condition_2>) { Q = <value_1>; }

@ ( <condition_2> && ! <condition_1>) { Q = <value_2>; }

}

```

Explicit accurate conflict resolution can be described as follows:

```

BEHAVIOR {

@ ( <condition_1> && <condition_2> ) {

Q = (<value_1>==<value_2>)? <value_1> : 'bX;

}

@ ( <condition_1> && ! <condition_2>) { Q = <value_1>; }

@ ( <condition_2> && ! <condition_1>) { Q = <value_2>; }

}

```

Since the conditions are now rendered mutually exclusive, equivalent descriptions with priority statements can be used. They are more elegant than descriptions with concurrent statements.

```

BEHAVIOR {

@ ( <condition_1> && <condition_2> ) {

Q = <conflict_resolution_value>;

}

: ( <condition_1> ) { Q = <value_1>; }

: ( <condition_2> ) { Q = <value_2>; }

}

```

Given the various explicit description possibilities, the standard does not prescribe a default behavior. The model developer has the freedom of incomplete specification.

### 5.2.6 Initial values for logic variables

Per definition, all logic variables in a behavioral description have the initial value u which means "uninitialized". This value cannot be assigned to a logic variable, yet it can be used in a behavioral description in order to assign other values than u after initialization.

Example:

```

BEHAVIOR {

@ ( Q1 == 'bU ) { Q1 = 'b1 ; }

@ ( Q2 == 'bU ) { Q2 = 'b0 ; }

// followed by the rest of the behavioral description

}

```

A template can be used to make the intent more obvious, for example:

```

TEMPLATE VALUE_AFTER_INITIALIZATION {

@ ( <logic_variable> == 'bU ) { <logic_variable> = <initial_value>

; }

}

BEHAVIOR {

VALUE_AFTER_INITIALIZATION ( Q1 'b1' )

VALUE_AFTER_INITIALIZATION ( Q2 'b0' )

// followed by the rest of the behavioral description

}

```

Logic variables in a vector expression shall be declared as PINS. It is possible to annotate initial values directly to a pin. Such variables shall never take the value U. Therefore vector expressions involving U for such variables (see the previous example) are meaningless.

Example:

```

PIN Q1 { INITIAL_VALUE = 'b1 ; }

PIN Q2 { INITIAL_VALUE = 'b0 ; }

```

# 5.3 Higher-order sequential functions

This section defines the different types of higher-order sequential functions in ALF.

### 5.3.1 Vector-sensitive sequential logic

Vector expressions can be used to model generalized higher order sequential logic; they are an extension of the boolean expressions. A *vector expression* describes sequences of logical events or transitions in addition to static logical states. A vector expression represents a description of a logical stimulus without timescale. It describes the order of occurrence of events.

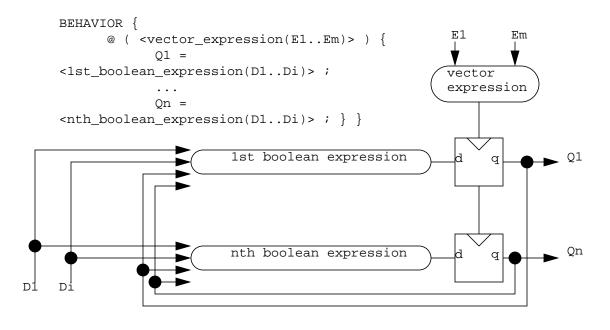

The -> operator (*followed by*) gives a general capability of describing a sequence of events or a vector. For example, consider the following vector expression:

01 A -> 01 B

which reads "rising edge on A is followed by rising edge on B".

A vector expression is evaluated by an event sequence detection function. Like a single event or a transition, this function evaluates *True* only at an infinitely short time when the event sequence is detected, as shown in Figure 5-6.

### Figure 5-6: Example of event sequence detection function

The event sequence detection mechanism can be described as a queue that sorts events according to their order of arrival. The event sequence detection function evaluates *True* at exactly the time when a new event enters the queue and forms the required sequence, i.e., *the sequence specified by the vector expression* with its preceding events.

A vector-sensitive sequential logic can be called (N+1) order sequential logic, where N is the number of events to be stored in the queue. The implementation of (N+1) order sequential logic requires N memory elements for the event queue and one memory element for the output itself.

A sequence of events can also be gated with static logical conditions. In the example,

(01 CP -> 10 CP) && CD

the pin CD shall have state 1 from some time before the rising edge at CP to some time after the falling edge of CP. The pin CD can not go low (state 0) after the rising edge of CP and go high again before the falling edge of CP because this would insert events into the queue and the sequence "rising edge on CP followed by falling edge on CP" would not be detected.

The formal calculation rules for general vector expressions featuring both states and transitions are detailed in Section 5.3.2 and Section 5.3.3.

The concept of vector expression supports functional modeling of devices featuring digital communication protocols with arbitrary complexity.

### 5.3.2 Canonical binary operators for vector expressions

The following canonical binary operators are necessary to define sequences of transitions:

- vector\_followed\_by for completely specified sequence of events

- vector\_and for simultaneous events

- vector\_or for alternative events

- vector\_followed\_by for incompletely specified sequence of events

The symbols for the boolean operators for AND and OR are overloaded for vector\_and and vector\_or, respectively. The new symbols for the vector\_followed\_by operators are shown in Table 5-12.

| Operator | Operands                | LHS, RHS<br>commutative | Description                                                                                                                    |

|----------|-------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| ->       | 2 vector<br>expressions | no                      | Left-hand side (LHS) transition <i>is followed by</i> Right-hand side (RHS) transition, no transition can occur in-between     |

| &&, &    | 2 vector<br>expressions | yes                     | LHS and RHS transition occur simultaneously                                                                                    |

| ,        | 2 vector<br>expressions | yes                     | LHS or RHS transition occur alternatively                                                                                      |

| ~>       | 2 vector<br>expressions | no                      | Left-hand side (LHS) transition <i>is followed by</i> Right-hand side (RHS) transition, other transitions can occur in-between |

Per definition, the  $\rightarrow$  and  $\rightarrow$  operators shall not be commutative, whereas the && and  $\mid \mid$  operators on events shall be commutative.

01 a && 01 b === 01 b && 01 a 01 a || 01 b === 01 b || 01 a The -> and ~> operators shall be freely associative.

01 a -> 01 b -> 01 c === (01 a -> 01 b) -> 01 c === 01 a -> (01 b -> 01 c)

$01 a \rightarrow 01 b \rightarrow 01 c == (01 a \rightarrow 01 b) \rightarrow 01 c == 01 a \rightarrow (01 b \rightarrow 01 c)$ The && operator is defined for single events and for event sequences with the same number of -> operators each.

(01 A1 .. -> ... 01 AN) & (01 B1 .. -> ... 01 BN) === 01 A1 & 01 B1 ... -> ... 01 AN & 01 BN

The || operator reduces the set of edge operators (unary vector operators) to canonical and noncanonical operators.

(?? a) === (?! a) || (?- a) //a does or does not change its value Hence ?? is non-canonical, since it can be defined by other operators.

If <value1><value2> is an edge operator consisting of two based literals value1 and value2 and word is an expression which can take the value value1 or value2, then the following vector expressions are considered equivalent:

```

<value1><value2> <word>

=== 10 (<word> == <value1>) && 01 (<word> == <value2>)

=== 01 (<word> != <value1>) && 01 (<word> == <value2>)

=== 10 (<word> == <value1>) && 10 (<word> != <value2>)

== 01 (<word> != <value1>) && 10 (<word> != <value2>)

// all expressions describe the same event:

// <word> makes a transition from <value1> to <value2>

```

Hence vector expressions with edge operators using based literals can be reduced to vector expressions using only the edge operators 01 and 10.

### 5.3.3 Complex binary operators for vector expressions

Table 5-13 defines the complex binary operators for vector operators.

| Operator | Operands                | LHS, RHS<br>commutative | Description                                                                                |

|----------|-------------------------|-------------------------|--------------------------------------------------------------------------------------------|

| <->      | 2 vector<br>expressions | yes                     | LHS transition follows or is followed by RHS transition                                    |

| &>       | 2 vector<br>expressions | no                      | LHS transition <i>is followed by or occurs simultaneously</i> with RHS transition          |

| <&>      | 2 vector<br>expressions | yes                     | LHS transition follows or is followed by or occurs simulta-<br>neously with RHS transition |

Table 5-13 : Complex binary vector operators

The following expressions shall be considered equivalent:

(01 a <-> 01 b) === (01 a -> 01 b) | |(01 b -> 01 a) (01 a &> 01 b) === (01 a -> 01 b) | |(01 a && 01 b) (01 a <&> 01 b) === (01 a -> 01 b) | |(01 b -> 01 a) | |(01 a && 01 b) By their symmetric definition, the <-> and <&> operators are commutative.

01 a <-> 01 b === 01 b <-> 01 a 01 a <&> 01 b === 01 b <&> 01 a

The commutative complex binary vector operators are defined in Table 5-12. The commutativity rules are only defined for two operands:

• commutative "followed by":

```

vect_expr1 <-> vect_expr2 ===

vect_expr1 -> vect_expr2 // vect_expr1 occurs first

| vect_expr2 -> vect_expr1 // vect_expr2 occurs first

```

• commutative "followed by or simultaneously occurring":

```

vect_expr1 <&> vect_expr2 ===

vect_expr1 -> vect_expr2 // vect_expr1 occurs first

| vect_expr2 -> vect_expr1 // vect_expr2 occurs first

| vect_expr1 && vect_expr2 // both occur simultaneously

```

#### 5.3.3.1 Extension to N operands

This section defines how to use *N* operands.

A complex\_vector\_expression of the form

```

vector_expression { <-> vector_expression }

```

shall be commutative for all operands. The complex\_vector\_expression describes alternative event sequences in which the temporal order of each constituent vector\_expression is completely permutable, excluding simultaneous occurrence of each constituent vector\_expression.

A complex\_vector\_expression of the form

```

vector_expression { <&> vector_expression }

```

shall be commutative for all operands. The complex\_vector\_expression describes alternative event sequences in which the temporal order of each constituent vector\_expression is completely permutable, including simultaneous occurrence of each constituent vector\_expression.

Example:

```

01 A <-> 01 B <-> 01 C ===

01 A -> 01 B -> 01 C

01 B -> 01 C -> 01 A

01 C -> 01 A -> 01 B

01 C -> 01 A -> 01 B

01 B -> 01 A -> 01 C

01 A -> 01 C -> 01 B

```

01 A < &> 01 B < &> 01 C === 01 A -> 01 B -> 01 C 01 B -> 01 C -> 01 A 01 C -> 01 A -> 01 B 01 C -> 01 A -> 01 B 01 C -> 01 B -> 01 A 01 B -> 01 A -> 01 C 01 A -> 01 C -> 01 B 01 A & 01 B -> 01 C 01 A -> 01 B & 01 C 01 B & 01 C -> 01 A 01 B -> 01 C & 01 A 01 B -> 01 C & 01 A 01 C & 01 A -> 01 B 01 C -> 01 A & 01 B 01 C -> 01 A & 01 B 01 A & 01 C -> 01 C

#### 5.3.3.2 Boolean rules

The following rule applies for a boolean AND operation with three operands:

rule 1: A & B & C === (A & B) & C | A & (B & C)

A corresponding rule also applies to the commutative followed-by operation with three operands:

```

rule 2:

01 A <-> 01 B <-> 01 C ===

(01 A <-> 01 B) <-> 01 C

| 01 A <-> (01 B <-> 01 C)

```

The alternative boolean expressions (A & B) & C and A & (B & C) in rule 1 are equivalent. Therefore, rule 1 can be reduced to the following:

```

rule 3:

A & B & C === (A & B) & C === (B & C) & A

```

A corresponding rule does *not* apply to complex vector operands, since each expression with associated operands generates only a subset of permutations:

```

(01 A <-> 01 B) <-> 01 C ===

((01 A <-> 01 B) -> 01 C)

| (01 C -> (01 A <-> 01 B)) ===

01 A -> 01 B -> 01 C

| 01 B -> 01 A -> 01 C

| 01 C -> 01 A -> 01 B

| 01 C -> 01 B -> 01 A

```

The permutations

01 A -> 01 C -> 01 B 01 B -> 01 C -> 01 A are missing.

```

01 A <-> (01 B <-> 01 C) ===

(01 A -> (01 B <-> 01 C))

((01 B <-> 01 C) -> 01 A) ===

01 A -> 01 B -> 01 C

01 A -> 01 C -> 01 B

01 B -> 01 C -> 01 A

01 C -> 01 B -> 01 A

```

The permutations

01 B -> 01 A -> 01 C 01 C -> 01 A -> 01 B

are missing.

#### 5.3.4 Operators for conditional vector expressions

The definitions of the &&, ?, and : operators are also overloaded to describe a *conditional vector expression* (involving boolean expressions and vector expressions), as shown in Table 5-14. The clauses are boolean expressions; while vector expressions are subject to those clauses.

| Operator | Operands                                           | LHS, RHS<br>commutative | Description                                                                                                                    |

|----------|----------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| &&. &    | 1 vector<br>expression,<br>1 boolean<br>expression | yes                     | boolean expression (LHS or RHS) is <i>True</i> while sequence of transitions, defined by vector expression (RHS or LHS) occurs |

| ?        | 1 vector<br>expression,<br>1 boolean<br>expression | no                      | boolean condition operator for construction of if-then-else<br>clause involving vector expressions                             |

| :        | 1 vector<br>expression,<br>1 boolean<br>expression | no                      | boolean else operator for construction of if-then-else<br>clause involving vector expressions                                  |

Table 5-14 : Operators for conditional vector expressions

An example for conditional vector expression using && is given below:

(01 a && !b) // a rises while b==0

The order of the operands in a conditional vector expression using && shall not matter.

<vector\_exp> && <boolean\_exp> === <boolean\_exp> && <vector\_exp>

The && operator is still commutative in this case, although one operand is a boolean expression defining a static state, the other operand is a vector expression defining an event or a sequence of events. However, since the operands are distinguishable per se, it is not necessary to impose a particular order of the operands.

An example for conditional vector expression using ? and : is given below.

!b ? 01 a : c ? 10 b : 01 d === !b & 01 a | !(!b) & c & 10 b | !(!b) & !c & 01 d

This example shows how a conditional vector expression using ternary operators can be expressed with alternative conditional vector expressions.

A conditional vector expression can be reduced to a non-conditional vector expression in some cases (see Section 5.4.11).

Every binary vector operator can be applied to a conditional vector expression.

### 5.3.5 Operators for sequential logic

Table 5-15 defines the complex binary operators for vector operators.

| Operator | Description                                                                                                                                                                                |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| @        | sequential if operator, followed by a boolean logic expression (for<br>level-sensitive assignment) or by a vector expression (for edge-sen-<br>sitive assignment)                          |

| :        | sequential else if operator, followed by a boolean logic expres-<br>sion (for level-sensitive assignment) or by a vector expression (for<br>edge-sensitive assignment) with lower priority |

Table 5-15 : Operators for sequential logic

Sequential assignments are constructed as follows:

```

@ ( <trigger1> ) { <action1> } : ( <trigger2> ) { <action2> } :

( <trigger3> ) { <action3> }

```

If trigger1 event is detected, then action1 is performed; else if trigger2 event is detected, then action2 is performed; else if trigger3 event is detected, then action3 is performed as a result of this clause.

### 5.3.6 Operator priorities

The priority of binding operators to operands in non-conditional vector expressions shall be from strongest to weakest in the following order:

- 1. unary vector operators (edge literals)

- 2. complex binary vector operators (<->, &>, <&>)

- 3. vector AND (&, &&)

- 4. vector\_followed\_by operators (->, ~>)

- 5. vector OR(|, ||)

### 5.3.7 Using PINs in VECTORs

A VECTOR defines state, transition, or sequence of transitions of pins that are controllable and observable for characterization.

Within a CELL, the set of PINS with SCOPE=behavior or SCOPE=measure or SCOPE=both is the default set of variables in the event queue for vector expressions relevant for BEHAVIOR or VECTOR statements or both, respectively.

For detection of a sequence of transitions it is necessary to observe the set of variables in the event queue. For instance, if the set of pins consists of A, B, C, D, the vector expression

(01 A -> 01 B)

implies no transition on A, B, C, D occurs between the transitions 01 A and 01 B.

The default set of pins applies only for vector expressions without conditions. The conditional event AND operator limits the set of variables in the event queue. In this case, only the state of the condition and the variables appearing in the vector expression are observed.

Example:

(01 A -> 01 B) && (C | D)

No transition on A, B occurs between 01 A and 01 B, and (C | D) needs to stay *True* in-between 01 A and 01 B as well. However, C and D can change their values as long as (C | D) is satisfied.

## 5.4 Modeling with vector expressions

Vector expressions provide a formal language to describe digital waveforms. This capability can be used for functional specification, for timing and power characterization, and for timing and power analysis.

In particular, vector expressions add value by addressing the following modeling issues:

- Functional specification: complex sequential functionality, e.g., bus protocols.

- *Timing analysis*: complex timing arcs and timing constraints involving more than two signals.

- *Power analysis*: temporal and spatial correlation between events relevant for power consumption.

- *Circuit characterization and test*: specification of characterization and/or test vectors for particular timing, power, fault, or other measurements within a circuit.

Like boolean expressions, vector expressions provide the means for describing the functionality of digital circuits in various contexts without being self-sufficient. Vector expressions enrich this functional description capability by adding a "dynamic" dimension to the otherwise "static" boolean expressions.

The following subsections explain the semantics of vector expressions step-by-step. The vector expression concept is explained using terminology from simulation event reports. However, the application of vector expressions is not restricted to post-processing event reports.

Some application tools (e.g., power analysis tools) can actually evaluate vector expressions during post-processing of event reports from simulation. Other application tools, especially

simulation model generators, need to respect the causality between the triggering events and the actions to be triggered. While it is semantically impossible to describe cause and effect in the same vector expression for the purpose of functional modeling, both cause and effect can appear in a vector expression used for a timing arc description.

ALF does not make assumption about the physical nature of the event report. Vector expressions can be applied to an actual event report written in a file, to an internal event queue within a simulator, or to a hypothetical event report which is merely a mathematical concept.

### 5.4.1 Event reports

This section describes the terminology of event reports from simulation, which is used to explain the concept of ALF vector expressions. The intent of ALF vector expressions is not to *replace* existing event report formats. Non-pertinent details of event report formats are not described here.

Simulation events (e.g., from Verilog or VHDL) can be reported in a value change dump (VCD) file, which has the following general form:

The set of variables for which simulation events are reported, i.e., the *scope* of the event report needs to be defined beforehand. Each variable also has a definition for the *set of states* it can take. For instance, there can be binary variables, 16-bit integer variables, 1-bit variables with drive-strength information, etc. Furthermore, the initial state of each variable shall be defined as well. In an ALF context, the terms *signal* and *variable* are used interchangeably. In VHDL, the corresponding term is *signal*. In Verilog, there is no single corresponding term. All input, output, wire, and reg variables in Verilog correspond to a signal in VHDL.

The time values <time1>, <time2>, <time3>, etc. shall be in increasing order. The order in which simultaneous events are reported does not matter. The number of time points and the number of simultaneous events at a certain time point are unlimited.

In the physical world, each event or change of state of a variable takes a certain amount of time. A variable cannot change its state more than once at a given point in time. However, in simulation, this time can be smaller than the resolution of the time scale or even zero (0). Therefore, a variable can change its state more than once at a given point in simulation time. Those events are, strictly speaking, not simultaneous. They occur in a certain order, separated by an infinitely small delta-time. Multiple simultaneous events of the same variable are not reported in the VCD. Only the final state of each variable is reported.

A VCD file is the most compact format that allows reconstruction of entire waveforms for a given set of variables. A more verbose form is the test pattern format.

<TIME> <variableA> <variableB> <variableC> <variableD> <time1> <stateU> <stateV> ... ... <time2> <stateU> <stateV> <stateW> <stateX> <time3> ... ...

The test pattern format reports the state of each variable at every point in time, regardless of whether the state has changed or not. Previous and following states are immediately available in the previous and next row, respectively. This makes the test pattern format more readable than the VCD and well-suited for taking a snapshot of events in a time window.

An example of an event report in VCD format:

```

// initial values

A 0

в 1

C1 DX

Ε1

// event dump

A 1

D 0

109

258

в 0

573

C 0

586

A 0

643

A 1

788

A 0

B1 C1

915

A 1

1062 E 0

1395 B O

C 0

1640 A O

D 1

// end of event dump

```

An example of an event report in test pattern format:

| time | А | В | С | D | Е |

|------|---|---|---|---|---|

| 0    | 0 | 1 | 1 | Х | 1 |

| 109  | 1 | 1 | 1 | 0 | 1 |

| 258  | 1 | 0 | 1 | 0 | 1 |

| 573  | 1 | 0 | 0 | 0 | 1 |

| 586  | 0 | 0 | 0 | 0 | 1 |

| 643  | 1 | 0 | 0 | 0 | 1 |

| 788  | 0 | 1 | 1 | 0 | 1 |

| 915  | 1 | 1 | 1 | 0 | 1 |

| 1062 | 1 | 1 | 1 | 0 | 0 |

| 1395 | 1 | 0 | 0 | 0 | 0 |

| 1640 | 0 | 0 | 0 | 1 | 0 |

Both VCD and test pattern formats represent the same amount of information and can be translated into each other.

### 5.4.2 Event sequences

For specification of a functional waveform (e.g., the write cycle of a memory), it is not practical to use an event report format, such as a VCD or test pattern format. In such waveforms, there is no absolute time. And the relative time, for example, the setup time between address change and write enable change, can vary from one instance to the other.

The main purpose of vector\_expressions is waveform specification capability. The following operators can be used:

• vector\_unary (also called *edge operator* or *unary vector operator*)

The edge operator is a prefix to a variable in a vector expression. It contains a pair of states, the first being the previous state, the second being the new state. Edge operators can describe a change of state or no change of state.

vector\_and (also called *simultaneous event operator*)

This operator uses the overloaded symbol & or && interchangeably. The & operator is the separator between simultaneously occurring events

vector\_followed\_by (also called *followed-by operator*)

The "immediately followed-by operator" using the symbol -> is treated first. The -> operator is the separator between consecutively occurring events.

These operators are necessary and sufficient to describe the following subset of vector\_expressions:

• vector\_single\_event

A change of state in a single variable, for example:

01 A

• vector\_event

A simultaneous change of state in one or more variables, for example:

01 A & 10 B

vector\_event\_sequence

Subsequently occurring changes of state in one or more variables, for example: 01 A & 10 B -> 10 A

The vector\_and operator has a higher binding priority than the vector\_followed\_by operator.

We can now express the pattern of the sample event report in a vector\_event\_sequence expression:

01 A & X0 D -> 10 B -> 10 C -> 10 A -> 01 A -> 10 A & 01 B & 01 C -> 01 A -> 10 E -> 10 B & 10 C -> 10 A & 01 D

We can define the *length* of a vector\_event\_sequence expression as the number of subsequent events described in the vector\_event\_sequence expression. The length is equal to the number of -> operators plus one (1).

Although the vector expression format contains an inherent redundancy, since the old state of each variable is always the same as the new state of the same variable in a previous event, it is more human-readable, especially for waveform description. On the other hand, it is more compact than the test pattern format. For short event sequences, it is even more compact than the VCD, since it eliminates the declaration of initial values. To be accurate, for variables with exactly one event the vector expression is more compact than the VCD. For variables with more than one event the VCD is more compact than the vector expression. In summary, the vector expression format offers readability similar to the test pattern format and compactness close to the VCD format.

//(1) content is A

//(2) content is B, C

### 5.4.3 Scope and content of event sequences

The *scope* applicable to a vector expression defines the set of variables in the event report. The *content* of a vector expression is the set of variables that appear in the vector expression itself. The content of a vector expression shall be a subset of variables within scope.

- PINS with the annotation SCOPE = BEHAVIOR are applicable variables for vector expressions within the context of BEHAVIOR.

- PINS with the annotation SCOPE = MEASURE are applicable variables for vector expressions within the context of VECTOR.

- PINS with the annotation SCOPE = BOTH are applicable variables for all vector expressions.

A vector\_event\_sequence expression is an event pattern without time, containing only the variables within its own content. This event pattern is evaluated against the event report containing all variables within scope. The vector expression is *True* when the event pattern matches the event report.

Example:

| time  | A      | В | С | D | Е    | // scope is A, B, C, D, E |

|-------|--------|---|---|---|------|---------------------------|

| 0     | 0      | 1 | 1 | Х | 1    |                           |

| 109   | 1      | 1 | 1 | 0 | 1    |                           |

| 258   | 1      | 0 | 1 | 0 | 1    |                           |

| 573   | 1      | 0 | 0 | 0 | 1    |                           |

| 586   | 0      | 0 | 0 | 0 | 1    |                           |

| 643   | 1      | 0 | 0 | 0 | 1    |                           |

| 788   | 0      | 1 | 1 | 0 | 1    |                           |

| 915   | 1      | 1 | 1 | 0 | 1    |                           |

| 1062  | 1      | 1 | 1 | 0 | 0    |                           |

| 1395  | 1      | 0 | 0 | 0 | 0    |                           |

| 1640  | 0      | 0 | 0 | 1 | 0    |                           |

| • • • | 1 C 11 | • |   |   | • .1 |                           |

Consider the following vector expressions in the context of the sample event report:

```

01 A

//event pattern expressed by (1):

// A

// 0

// 1

```

(1) is *True* at time 109, time 643, and time 915.

```

10 B -> 10 C

//event pattern expressed by (2):

// B C

// 1 1

// 0 1

// 0 0

```

(2) is *True* at time 573.

```

10 A -> 01 A

//(3) content is A

//event pattern expressed by (3):

11

Α

11

1

11

0

11

1

(3) is True at time 643 and time 915.

01 D

//(4) content is D

//event pattern expressed by (4):

11

D

11

0

11

1

(4) is True at time 1640.

01 A -> 10 C

//(5) content is A, C

//event pattern expressed by (5):

11

А

С

11

0

1

11

1

1

11

1

Ο

```

(5) is not be *True* at any time, since the event pattern expressed by (5) does not match the event report at any time.

#### 5.4.4 Alternative event sequences

The following operator can be used to describe alternative events:

vector\_or, also called *event-or operator* or *alternative-event operator*, using the overloaded symbol | or | | interchangeably. The | operator is the separator between alternative events or alternative event sequences.

In analogy to boolean operators, | has a lower binding priority than & and ->. Parentheses can be used to change the binding priority.

Example:

(01 A -> 01 B) | 10 C === 01 A -> 01 B | 10 C 01 A -> (01 B | 10 C) === 01 A -> 01 B | 01 A -> 10 C

Consider the following vector expressions in the context of the sample event report:

```

01 A | 10 C

//(6)

//event pattern expressed by (6):

11

Α

11

0

11

1

//alternative event pattern expressed by (6):

11

С

1

11

11

0

```

(6) is *True* at time 109, time 573, time 643, time 915, and time 1395.

//(8)

```

10 B -> 10 C | 10 A -> 01 A

//(7)

//event pattern expressed by (7):

В

С

11

1

11

1

11

0

1

11

0

0

//alternative event pattern expressed by (7):

11

Α

11

1

11

0

11

1

```

(7) is *True* at time 573, time 643, and time 915.

```

01 D | 10 B -> 10 C

//event pattern expressed by (8):

11

D

11

0

//

1

//alternative event pattern expressed by (8):

11

В

С

11

1

1

11

0

1

11

0

0

```

(8) is *True* at time 573 and time 1640.

```

10 B -> 10 C | 10 A

//(9)

//event pattern expressed by (9):

11

В

С

1

1

11

11

0

1

11

0

0

//alternative event pattern expressed by (9):

11

Α

11

1

11

0

```

(9) is *True* at time 573, time 586, time 788, and time 1640.

The following operators provide a more compact description of certain alternative event sequences:

- &> events occur simultaneously or follow each other in the order RHS after LHS

- <-> a LHS event followed by a RHS event or a RHS event followed by a LHS event

- <&> events occur simultaneously or follow each other in arbitrary order •

Example:

01 A &> 01 C 01 A & 01 C | 01 A -> 01 C === 01 A <-> 01 C 01 A -> 01 C | 01 C -> 01 A === 01 A <-> 01 C | 01 A & 01 C 01 A <&> 01 C ===

The binding priority of these operators is higher than of & and ->.

### 5.4.5 Symbolic edge operators

Alternative events of the same variable can be described in a even more compact way through the use of edge operators with symbolic states. The symbol ? stands for "any state".

- edge operator with ? as the previous state: transition from any state to the defined new state

- edge operator with ? as the next state: transition from the defined previous state to any state.

Both edge operators include the possibility no transition occurred at all, i.e., the previous and the next state are the same. This situation can be explicitly described with the following operator:

edge operator with next state = previous state, also called *non-event operator* The operand stays in the state defined by the operator.

The following symbolic edge operators also can be used:

- ?- no transition on the operand

- ?! transition from any state to any state different from the previous state

- ?? transition from any state to any state or no transition on the operand

- ?~ transition from any state to its bitwise complementary state

Example: Let A be a logic variable with the possible states 1, 0, and x.

| ?0 A === 00 A | 10 A   X0 A                                           |

|---------------|-------------------------------------------------------|

| ?1 A === 01 A | 11 A   X1 A                                           |

| ?X A === 0X A | 1X A   XX A                                           |

| 0? A === 00 A | 01 A   0X A                                           |

| 1? A === 10 A | 11 A   1X A                                           |

| X? A === X0 A | X1 A   XX A                                           |

| ?! A === 01 A | 0X A   10 A   1X A   X0 A   X1 A                      |

| ?~ A === 01 A | 10 A   XX A                                           |

| ?? A === 00 A | 01 A   0X A   10 A   11 A   1X A   X0 A   X1 A   XX A |

| ?- A === 00 A | 11 A   XX A                                           |

For variables with more possible states (e.g., logic states with different drive strength and multiple bits) the explicit description of alternative events is quite verbose. Therefore the symbolic edge operators are useful for a more compact description.

This completes the set of vector\_binary operators necessary for the description of a subset of vector\_expressions called vector\_complex\_event expressions. All vector\_binary operators have two vector\_complex\_event expressions as operands. The set of vector\_event\_sequence expressions is a subset of vector\_complex\_event expressions. Every vector\_complex\_event expression can be expressed in terms of alternative vector\_event\_sequence expressions. The latter could be called *minterms*, in analogy to boolean algebra.

### 5.4.6 Non-events

A vector\_single\_event expression involving a non-event operator is called a *non-event*. A rigorous definition is required for vector\_complex\_event expressions containing non-events. Consider the following example of a flip-flop with clock input CLK and data output Q.

```

01 CLK -> 01 Q // (i)

01 CLK -> 00 Q // (ii)

```

The vector expression (i) describes the situation where the output switches from 0 to 1 after the rising edge of the clock. The vector expression (ii) describes the situation where the output remains at 0 after the rising edge of the clock.

How is it possible to decide whether (i) or (ii) is *True*, without knowing the delay between CLK and Q? The only way is to wait until any event occurs after the rising edge of CLK. If the event is not on Q and the state of Q is 0 during that event, then (ii) is *True*.

Hence, a non-event is *True* every time when another event happens and the state of the variable involved in the non-event satisfies the edge operator of the non-event.

Example:

| time | А | В | С | D | E |

|------|---|---|---|---|---|

| 0    | 0 | 1 | 1 | Х | 1 |

| 109  | 1 | 1 | 1 | 0 | 1 |

| 258  | 1 | 0 | 1 | 0 | 1 |

| 573  | 1 | 0 | 0 | 0 | 1 |

| 586  | 0 | 0 | 0 | 0 | 1 |

| 643  | 1 | 0 | 0 | 0 | 1 |

| 788  | 0 | 1 | 1 | 0 | 1 |

| 915  | 1 | 1 | 1 | 0 | 1 |

| 1062 | 1 | 1 | 1 | 0 | 0 |

| 1395 | 1 | 0 | 0 | 0 | 0 |

| 1640 | 0 | 0 | 0 | 1 | 0 |

The test pattern format represents an event, for example 01 A, in no different way than a nonevent, for example 11 E. This non-event is *True* at times 109, 258, 573, 586, 643, 788, and 915; in short, every time when an event happens while E is constant 1.

### 5.4.7 Compact and verbose event sequences

A vector\_event\_sequence expression in a compact form can be transformed into a verbose form by padding up every vector\_event expression with non-events. The next state of each variable within a vector\_event expression shall be equal to the previous state of the same variable in the subsequent vector\_event expression.

Example:

01 A -> 10B === 01 A & 11 B -> 11 A & 10 B

A vector expression for a complete event report in compact form resembles the VCD, whereas the verbose form looks like the test pattern.

```

// compact form

01 A & X0 D -> 10 B -> 10 C -> 10 A -> 01 A

-> 10 A & 01 B & 01 C -> 01 A -> 10 E

-> 10 B & 10 C -> 10 A & 01 D

===

// verbose form

?0 A & ?1 B & ?1 C & ?X D & ?1 E->

01 A & 11 B & 11 C & X0 D & 11 E->

11 A & 10 B & 11 C & 00 D & 11 E->

11 A & 00 B & 10 C & 00 D & 11 E->

10 A & 00 B & 00 C & 00 D & 11 E->

01 A & 00 B & 00 C & 00 D & 11 E->

10 A & 01 B & 01 C & 00 D & 11 E->

01 A & 11 B & 11 C & 00 D & 11 E->

11 A & 11 B & 11 C & 00 D & 10 E->

11 A & 10 B & 10 C & 00 D & 00 E->

10 A & 00 B & 00 C & 01 D & 00 E

```

The transformation rule needs to be slightly modified in case the compact form contains a vector\_event expression consisting only of non-events. By definition, the non-event is *True* only if a real event happens simultaneously with the non-event. Padding up a vector\_event expression consisting of non-events with other non-events make this impossible. Rather, this vector\_event expression needs to be padded up with unspecified events, using the ?? operator. Eventually, unspecified events can be further transformed into partly specified events, if a former or future state of the involved variable is known.

Example:

01 A -> 00 B === 01 A & 00 B -> ?? A & 00 B

In the first transformation step, the unspecified event ?? A is introduced.

01 A & 00 B -> ?? A & 00 B === 01 A & 00 B -> 1? A & 00 B

In the second step, this event becomes partly specified. ?? A is bound to be 1? A due to the previous event on A.

#### 5.4.8 Unspecified simultaneous events within scope

Variables which are within the scope of the vector expression yet do not appear in the vector expression, can be used to pad up the vector expression with unspecified events as well. This is equivalent to omitting them from the vector expression.

Example:

```

01 A -> 10 B // let us assume a scope containing A, B, C, D, E

===

01 A & 10 B & ?? C & ?? D & ?? E -> 11 A & 10 B & ?? C & ?? D & ?? E

```

This definition allows unspecified events to occur *simultaneously* with specified events or specified non-events. However, it disallows unspecified events to occur *in-between* specified events or specified non-events.

At first sight, this distinction seems to be arbitrary. Why not disallow unspecified events altogether? Yet there are several reasons why this definition is practical.

If a vector expression disallows simultaneously occurring unspecified events, the application tool has the burden not only to match the pattern of specified events with the event report but also to check whether the other variables remain constant. Therefore, it is better to specify this extra pattern matching constraint explicitly in the vector expression by using the ?- operator.

There are many cases where it actually does not matter whether simultaneously occurring unspecified events are allowed or disallowed:

- Case 1: Simultaneous events are impossible by design of the flip-flop. For instance, in a flip-flop it is impossible for a triggering clock edge 01 CK and a switch of the data output ? Q to occur at the same time. Therefore, such events can not appear in the event report. It makes no difference whether 01 CK & ?- Q, 01 CK & ?? Q, or 01 CK is specified. The only occurring event pattern is 01 CK & ?- Q and this pattern can be reliably detected by specifying 01 CK.

- Case 2: Simultaneous events are prohibited by design. For instance, in a flip-flop with a positive setup time and positive hold time, the triggering clock edge 01 CK and a switch of the data input ?! D is a timing violation. A timing checker tool needs the violating pattern specified explicitly, i.e., 01 CK & ?! D. In this context, it makes sense to specify the non-violating pattern also explicitly, i.e., 01 CK & ?- D. The pattern 01 CK by itself is not applicable.

- *Case 3*: Simultaneous events do not occur in correct design. For instance, power analysis of the event 01 CK needs no specification of ?! D or ?- D. In the analysis of an event report with timing violations, the power analysis is less accurate anyway. In the analysis of the event report for the design without timing violation, the only occurring event pattern is

01 CK & ?- D and this pattern can be reliably detected by specifying 01 CK.<sup>1</sup>

- *Case 4*: The effects of simultaneous events are not modeled accurately. This is the case in static timing analysis and also to some degree in dynamic timing simulation. For instance, a NAND gate can have the inputs A and B and the output z. The event sequence exercising the timing arc 01 A -> 10 z can only happen if B is constant 1. No event on B can happen in-between 01 A and 10 z. Likewise, the timing arc 01 B -> 10 z can only happen if A is constant 1 and no event happens in-between 01 B and 10 z. The timing arc with simultaneously switching inputs is commonly ignored. A tool encountering the scenario 01 A & 01 B -> 10 z has no choice other than treating it arbitrarily as 01 A -> 10 z or as 01 B -> 10 z.

- *Case 5*: The effects of simultaneous events are modeled accurately. Here it makes sense to specify all scenarios explicitly, e.g., 01 A & ?- B -> 10 Z, 01 A &?! B -> 10 Z, ?- A

<sup>1.</sup> The power analysis tool relates to a timing constraint checker in a similar way as a parasitic extraction tool relates to a DRC tool. If the layout has DRC violations, for instance shorts between nets, the parasitic extraction tool shall report inaccurate wire capacitance for those nets. After final layout, the DRC violations shall be gone and the wire capacitance shall be accurate.

& 01 B -> 10 Z, etc., whereas the patterns 01 A -> 10 Z and 01 B -> 10 Z by themselves apply only for less accurate analysis (see *Case 4*).

There is also a formal argument why unspecified events on a vector expression need to be allowed rather than disallowed. Consider the following vector expressions within the scope of two variables A and B.

01 A // (i) 01 B // (ii) 01 A & 01 B // (iii)

The natural interpretation here is (iii) == (i) & (ii). This interpretation is only possible by allowing simultaneously occurring unspecified events.

Allowing simultaneously occurring unspecified events, the vector expressions (i) and (ii), respectively, are interpreted as follows:

01 A & ?? B // (i') ?? A & 01 B // (ii')

*Disallowing* simultaneously occurring unspecified events, the vector expressions (i) and (ii), respectively, are interpreted as follows:

01 A & ?- B // (i'') ?- A & 01 B // (ii'')

The vector expressions (i') and (ii') are compatible with (iii), whereas (i'') and (ii'') are not.

### 5.4.9 Simultaneous event sequences

The semantic meaning of the "simultaneous event operator" can be extended to describe simultaneously occurring *event sequences*, by using the following definition:

(01 A#1 .. -> ... 01 A#N) & (01 B#1 .. -> ... 01 B#N) === 01 A#1 & 01 B#1 ... -> ... 01 A#N & 01 B#N

This definition is analogous to scalar multiplication of vectors with the same number of indices. The number of indices corresponds to the number of  $vector\_event$  expressions separated by -> operators. If the number of -> in both vector expressions is not the same, the shorter vector expression can be left-extended with unspecified events, using the ?? operator, in order to align both vector expressions.

Advanced Library Format (ALF) Reference Manual

Example:

(01 A -> 01 B -> 01 C) & (01 D -> 01 E) === (01 A -> 01 B -> 01 C) & (?? D -> 01 D -> 01 E) === 01 A & ?? D -> 01 B & 01 D -> 01 C & 01 E === 01 A -> 01 B & 01 D -> 01 C & 01 E The easiest way to understand the meaning of "simultaneous event sequences" is to consider the event report in test pattern format. If each vector\_event\_sequence expression matches the event report in the same time window, then the event sequences happen simultaneously.

| time | А | В | С | D | Е |  |

|------|---|---|---|---|---|--|

| 0    | 0 | 1 | 1 | Х | 1 |  |

| 109  | 1 | 1 | 1 | 0 | 1 |  |

| 258  | 1 | 0 | 1 | 0 | 1 |  |

| 573  | 1 | 0 | 0 | 0 | 1 |  |

| 586  | 0 | 0 | 0 | 0 | 1 |  |

| 643  | 1 | 0 | 0 | 0 | 1 |  |

| 788  | 0 | 1 | 1 | 0 | 1 |  |

| 915  | 1 | 1 | 1 | 0 | 1 |  |

| 1062 | 1 | 1 | 1 | 0 | 0 |  |

| 1395 | 1 | 0 | 0 | 0 | 0 |  |

| 1640 | 0 | 0 | 0 | 1 | 0 |  |

#### Example:

01 A -> 10 B === 01 A & 11 B -> 11 A & 10 B // (10a) // event pattern expressed by (10a): 11 А В 11 0 1 11 1 1 11 1 0 X0 D -> 00 D // (10b) // event pattern expressed by (10b): 11 D 11 Х 0 11 11 0

$(01 A \rightarrow 10 B) \& (X0 D \rightarrow 00 D)$ //(10) === (10a)&(10b)

Both (10a) and (10b) are *True* at time 258. Therefore (10) is *True* at time 258.

```

10 C

=== ?? C -> ?? C -> 10 C

=== ?? C -> ?1 C -> 10 C

// (11a)

// event pattern expressed by (11a):

11

С

11

?

11

?

11

1

11

0

```

(11a) is left-extended to match the length of the following (11b).

01 A -> 00 D -> 11 E === 01 A & 00 D & ?? E -> ?? A & 00 D & ?? E -> ?? A & ?? D & 11 E === 01 A & 00 D & ?? E

|    |       | 00 D &  | •         |            |   | // | (11b) |

|----|-------|---------|-----------|------------|---|----|-------|

| 11 | event | pattern | expressed | d by (11b) | : |    |       |

| // | A     | D       | E         |            |   |    |       |

| // | 0     | 0       | ?         |            |   |    |       |

| // | 1     | 0       | ?         |            |   |    |       |

| 11 | ?     | 0       | 1         |            |   |    |       |

| // | ?     | ?       | 1         |            |   |    |       |

(11b) contains explicitly specified non-events. The non-event 00 D calls for the unspecified events ?? A and ?? E. The non-event 00 E calls for the unspecified events ?? A and ?? D. By propagating well-specified previous and next states to subsequent events, some unspecified events become partly specified.

10 C & (01 A -> 00 D -> 11 E) // (11) === (11a)&(11b)

(11a) is *True* at time 573 and time 1395. (11b) is *True* at time 573 and time 915. Therefore, (11) is *True* at time 573.

### 5.4.10 Implicit local variables

Until now, vector expressions are evaluated against an event report containing all variables within the scope of a cell. It is practical for the application to work with only one event report per cell or, at most, two event reports if the set of variables for BEHAVIOR (scope=behavior) and VECTOR (scope=measure) is different. However, for complex cells and megacells, it is sometimes necessary to change the scope of event observation, depending on operation modes. Different modes can require a different set of variables to be observed in different event reports.

The following definition allows to *extend* the scope of a vector expression locally:

Edge operators apply not only to variables, but also to boolean expressions involving those variables. Those boolean expressions represent *implicit local variables* that are visible only within the vector expression where they appear.

Suppose the local variables (A & B), (A | B) are inserted into the event report:

| 0       0       1       1       X       1       0       1         109       1       1       1       0       1       1       1         258       1       0       1       0       1       0       1         573       1       0       0       0       1       0       1         586       0       0       0       1       0       0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 258         1         0         1         0         1         0         1           573         1         0         0         0         1         0         1                                                                                                                                                                     |

| 573 1 0 0 0 1 0 1                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                   |

| 586 0 0 0 0 1 0 0                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                   |