# Advanced Library Format for ASIC Cells & Blocks

containing Power, Timing, Functional and Physical Information for Synthesis, Analysis, Design Planning and Test

Version 1.1

April 6, 1999

**Open Verilog International**

Copyright<sup>©</sup> 1996-1999 by Open Verilog International, Inc. All rights reserved.

No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means -- graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems --- without the prior approval of Open Verilog International.

Additional copies of this manual may be purchased by contacting Open Verilog International at the address shown below.

#### Notices

The information contained in this manual represents the definition of the Advanced Library Format (ALF) as reviewed and released by OVI (PS-TSC) in April 1999.

Open Verilog International reserves the right to make changes to the ALF language and this manual in subsequent revisions and makes no warranties whatsoever with respect to the completeness, accuracy, or applicability of the information in this manual, when used for production design and/or development.

Open Verilog International does not endorse any particular simulator or other CAE tool that is based on the Advanced Library Format.

Suggestions for improvements to the Advanced Library Format and/or to this manual are welcome. They should be sent to the ALF email reflector

#### alf@eda.org

or to the address below.

Information about Open Verilog International and membership enrollment can be obtained by inquiring at the address below.

- Published as: Advanced Library Format (ALF) Reference Manual Version 1.1, April 1999.

- Published by: Open Verilog International 15466 Los Gatos Blvd., #109071 Los Gatos, CA 95032 Phone: (408) 358-9510 Fax: (408) 358-3910

Printed in the United States of America.

Verilog<sup>®</sup> is a registered trademark of Cadence Design Systems, Inc.

The following individuals contributed to the creation, editing and review of this document.

| Jay Abraham             | Silicon Integration Initiative |                  |

|-------------------------|--------------------------------|------------------|

| Mike Andrews            | Mentor Graphics                | Co-Chairman      |

| Tim Ayres               | Synopsys - Viewlogic           |                  |

| Arun Balakrishnan       | NEC                            |                  |

| Tim Baldwin             | Cadence - Ambit                |                  |

| John Beatty             | IBM                            |                  |

| Victor Berman           | VI / IEEE                      |                  |

| Dennis Brophy           | Mentor Graphics / OVI / IEEE   |                  |

| Jose De Castro          | LSI Logic                      |                  |

| Renlin Chang            | Cadence                        |                  |

| Shir-Shen Chang, PhD    | Synopsys                       |                  |

| Sanjay Churiwala        | Cadworx                        |                  |

| Timothy Ehrler          | VLSI Technology                |                  |

| Ted Elkind              | Cadence                        |                  |

| Paul Foster             | Avant!                         |                  |

| Vassilios Gerousis, PhD | Siemens / OVI                  |                  |

| Kevin Grotjohn          | LSI Logic                      |                  |

| Mitch Heins             | Cadence - Ambit                |                  |

| Eric Howard             | Cadence                        |                  |

| Tim Jennings            | Motorola                       |                  |

| Timothy Jordan          | Motorola                       |                  |

| Archie Lachner          | Mentor Graphics                |                  |

| Tai Le                  | Avant!                         |                  |

| Johnson Chan Limqueco   | Cadence - Ambit                |                  |

| Ta-Yung Liu             | Avant!                         |                  |

| Saumendra Nath Mandal   | Duet Technologies              |                  |

| Hamid Rahmanian         | Mentor Graphics                |                  |

| Darshan Rauniyar        | Mentor Graphics                |                  |

| Wolfgang Roethig, PhD   | NEC                            | Chairman         |

| Larry Rosenberg, PhD    | Cadence / VSIA                 |                  |

| Ambar Sarkar, PhD       | Synopsys - Viewlogic           |                  |

| Itzhak Shapira          | Cadence                        |                  |

| Jin-Sheng Shyr          | Toshiba                        |                  |

| Sergei Sokolov          | Sente                          |                  |

| Peter Suaris            | Mentor Graphics                |                  |

| Toru Toyoda             | NEC                            |                  |

| Yatin Trivedi           | Seva Technologies              | Technical Editor |

| Devadas Varma           | Cadence - Ambit                |                  |

| David Wallace           | Mentor Graphics - Exemplar     |                  |

| Cary Wei                | Fujitsu                        |                  |

| Frank Weiler            | Avant! / OVI                   |                  |

| Jeff Wilson             | Mentor Graphics                |                  |

| Amir Zarkesh, PhD       | TDT                            |                  |

### Revision history:

| 1st draft:     | 11/20/96 |

|----------------|----------|

| 2nd draft:     | 12/20/96 |

| 3rd draft:     | 3/22/97  |

| 4th draft:     | 3/31/97  |

| 5th draft:     | 4/22/97  |

| 6th draft:     | 6/1/97   |

| 7th draft:     | 6/25/97  |

| 8th draft:     | 8/13/97  |

| 9th draft:     | 10/14/97 |

| Version 1.0    | 11/14/97 |

| Version 1.0.1  | 3/20/98  |

| Version 1.0.2  | 4/8/98   |

| Version 1.0.3  | 5/15/98  |

| Version 1.0.4  | 5/31/98  |

| Version 1.0.5  | 6/15/98  |

| Version 1.0.6  | 9/20/98  |

| Version 1.0.7  | 11/15/98 |

| Version 1.0.8  | 1/12/99  |

| Version 1.0.9  | 2/5/99   |

| Version 1.0.10 | 2/19/99  |

| Version 1.0.11 | 3/12/99  |

# **Table of Contents**

| 1 | Intr | oductio  | n                                    |    |

|---|------|----------|--------------------------------------|----|

|   | 1.1  | Motiva   | ation                                | 11 |

|   | 1.2  | Goals    |                                      | 11 |

|   | 1.3  | Target   | Applications                         | 12 |

|   | 1.4  | Conve    | ntions                               | 15 |

|   | 1.5  | Organi   | ization of this manual               | 16 |

| 2 | Cha  | racteriz | zation and Modeling                  |    |

|   | 2.1  | Basic (  | Concepts                             | 17 |

|   | 2.2  | Functi   | onal Modeling                        | 18 |

|   |      | 2.2.1    | Combinational Logic                  | 18 |

|   |      | 2.2.2    | Level Sensitive Sequential Logic     | 18 |

|   |      | 2.2.3    | Edge Sensitive Sequential Logic      | 18 |

|   |      | 2.2.4    | Vector-Sensitive Sequential Logic    | 21 |

|   | 2.3  | Perform  | mance Modeling for Characterization  | 22 |

|   |      | 2.3.1    | Timing Modeling                      | 22 |

|   |      | 2.3.2    | Power Modeling                       | 23 |

|   |      | 2.3.3    | Modeling for signal integrity        | 25 |

|   | 2.4  | Physic   | al modeling for synthesis and test   | 26 |

|   |      | 2.4.1    | Cell modeling                        | 26 |

|   |      | 2.4.2    | Wire modeling                        | 27 |

| 3 | Libi | rary Fo  | rmat Specification                   |    |

|   | 3.1  | Object   | Model                                | 29 |

|   |      | 3.1.1    |                                      | 29 |

|   |      | 3.1.2    | -                                    | 30 |

|   |      | 3.1.3    | Library-specific objects             | 33 |

|   |      | 3.1.4    | Arithmetic models                    | 33 |

|   |      | 3.1.5    | Functions                            | 33 |

|   | 3.2  | Lexica   | ll rules                             | 36 |

|   |      | 3.2.1    | Character set                        | 36 |

|   |      | 3.2.2    | Lexical tokens                       | 37 |

|   |      | 3.2.3    | Whitespace Characters                | 37 |

|   |      | 3.2.4    | Reserved and Non-reserved Characters | 37 |

|   |      | 3.2.5    | Delimiters                           | 38 |

|   |      | 3.2.6    | Comments                             | 38 |

|     | 3.2.7   | Numbers                           | 38 |

|-----|---------|-----------------------------------|----|

|     | 3.2.8   | Bit Literals                      | 39 |

|     | 3.2.9   | Based Literals                    | 40 |

|     | 3.2.10  | Edge Literals                     | 41 |

|     | 3.2.11  | Quoted Strings                    | 41 |

|     | 3.2.12  | Identifiers                       | 42 |

|     | 3.2.13  | Rules against parser ambiguity    | 43 |

|     | 3.2.14  | Cross-reference of lexical tokens | 43 |

| 3.3 | Keywoi  | rds                               | 44 |

|     | 3.3.1   | Keywords for Objects              | 44 |

|     | 3.3.2   | Keywords for Operators            | 45 |

|     | 3.3.3   | Context-Sensitive Keywords        | 45 |

| 3.4 | Syntax  | Rules                             | 45 |

|     | 3.4.1   | Assignments                       | 45 |

|     | 3.4.2   | Expressions                       | 46 |

|     | 3.4.3   | Instantiations                    | 47 |

|     | 3.4.4   | Literals                          | 48 |

|     | 3.4.5   | Operators                         | 49 |

|     | 3.4.6   | Auxiliary Objects                 | 51 |

|     | 3.4.7   | Generic Objects                   | 51 |

|     | 3.4.8   | CELL                              | 53 |

|     | 3.4.9   | LIBRARY                           | 53 |

|     | 3.4.10  | PIN                               | 53 |

|     | 3.4.11  | PRIMITIVE                         | 54 |

|     | 3.4.12  | SUBLIBRARY                        | 54 |

|     | 3.4.13  | VECTOR                            | 54 |

|     | 3.4.14  | WIRE                              | 55 |

|     | 3.4.15  | Arithmetic Model                  | 55 |

|     | 3.4.16  | FUNCTION                          | 56 |

|     | 3.4.17  | Cross-reference of BNF items      | 57 |

| 3.5 | Operato | Drs                               | 61 |

|     | 3.5.1   | Arithmetic operators              | 61 |

|     | 3.5.2   | Boolean operators on scalars      | 62 |

|     | 3.5.3   | Boolean operators on words        | 63 |

|     | 3.5.4   | Vector operators                  | 64 |

|     | 3.5.5   | Operators for sequential logic    | 68 |

|     | 3.5.6   | Operator priorities               | 68 |

|     | 3.5.7   | Datatype mapping                  | 69 |

| 3.6 | Context | t-sensitive keywords              | 71 |

|     | 3.6.1   | Annotation Containers             | 71 |

|      | 3.6.2    | Keywords for referencing objects used as annotation   | 73  |

|------|----------|-------------------------------------------------------|-----|

|      | 3.6.3    | Annotations for a PIN object                          | 73  |

|      | 3.6.4    | Annotations for a VECTOR object                       | 78  |

|      | 3.6.5    | Annotations for a CELL object                         | 80  |

|      | 3.6.6    | Attributes                                            | 84  |

|      | 3.6.7    | Keywords for arithmetic models                        | 85  |

|      | 3.6.8    | Containers for arithmetic models                      | 93  |

|      | 3.6.9    | Keywords for arithmetic submodels                     | 95  |

|      | 3.6.10   | Annotations for arithmetic models                     | 100 |

| 3.7  | Library  | Organization                                          | 108 |

|      | 3.7.1    | Scoping Rules                                         | 108 |

|      | 3.7.2    | Use of multiple files                                 | 109 |

| 3.8  | Referen  | ceable objects                                        | 109 |

|      | 3.8.1    | Referencing PRIMITIVEs or CELLs                       | 110 |

|      | 3.8.2    | Referencing PINs in FUNCTIONs                         | 111 |

|      | 3.8.3    | Referencing PINs in VECTORs                           | 113 |

|      | 3.8.4    | Referencing multi-dimensional PINs                    | 113 |

|      | 3.8.5    | Referencing arithmetic models                         | 115 |

| 3.9  | Functio  | nal modeling styles and rules                         | 117 |

|      | 3.9.1    | Rules for combinational functions                     | 117 |

|      | 3.9.2    | Basic rules for sequential functions                  | 118 |

|      | 3.9.3    | Concurrency in combinational and sequential functions | 120 |

|      | 3.9.4    | Initial values for logic variables                    | 123 |

| 3.10 | Primitiv | /es                                                   | 124 |

|      | 3.10.1   | Concept of user-defined and predefined primitives     | 124 |

|      | 3.10.2   | Predefined combinational primitives                   | 126 |

|      | 3.10.3   | Predefined tristate Primitives                        | 129 |

|      | 3.10.4   | Predefined multiplexor                                | 131 |

|      | 3.10.5   | Predefined flipflop                                   | 132 |

|      | 3.10.6   | Predefined latch                                      | 133 |

| 3.11 | Parame   | terizeable Cells                                      | 135 |

| 3.12 | Modeli   | ng with Vector Expressions                            | 138 |

|      | 3.12.1   | Event reports                                         | 139 |

|      | 3.12.2   | Event Sequences                                       | 140 |

|      | 3.12.3   | Scope and content of event sequences                  | 141 |

|      | 3.12.4   | Alternative event sequences                           | 143 |

|      | 3.12.5   | Symbolic edge operators                               | 145 |

|      | 3.12.6   | Non-events                                            | 146 |

|      | 3.12.7   | Compact and verbose event sequences                   | 146 |

|      | 3.12.8   | Unspecified simultaneous events within scope          | 147 |

|   |      | 3.12.9    | Simultaneous event sequences                    | 149 |

|---|------|-----------|-------------------------------------------------|-----|

|   |      | 3.12.10   | Implicit local variables                        | 151 |

|   |      | 3.12.11   | Conditional event sequences                     | 152 |

|   |      | 3.12.12   | Alternative conditional event sequences         | 154 |

|   |      | 3.12.13   | Change of scope within a vector expression      | 156 |

|   |      | 3.12.14   | Sequences of conditional event sequences        | 159 |

|   |      | 3.12.15   | Incompletely specified event sequences          | 161 |

|   |      | 3.12.16   | Well-specified vector expressions               | 163 |

| 4 | Appl | lications |                                                 | 165 |

|   | 4.1  | Truth Ta  | able vs Boolean Equation                        | 165 |

|   |      | 4.1.1     | NAND gate                                       | 165 |

|   |      | 4.1.2     | Flipflop                                        | 166 |

|   | 4.2  | Use of p  | primitives                                      | 166 |

|   |      | 4.2.1     | D-Flipflop with asynchronous clear              | 166 |

|   |      | 4.2.2     | JK-flipflop                                     | 167 |

|   |      | 4.2.3     | D-Flipflop with synchronous load and clear      | 168 |

|   |      | 4.2.4     | D-Flipflop with input multiplexor               | 168 |

|   |      | 4.2.5     | D-latch                                         | 169 |

|   |      | 4.2.6     | SR-latch                                        | 169 |

|   |      | 4.2.7     | JTAG BSR                                        | 170 |

|   |      | 4.2.8     | Combinational Scan Cell                         | 170 |

|   |      | 4.2.9     | Scan Flipflop                                   | 172 |

|   |      | 4.2.10    | Quad D-Flipflop                                 | 173 |

|   | 4.3  | Templat   | tes and vector-specific models                  | 174 |

|   |      | 4.3.1     | Vector-specific delay and power Tables          | 174 |

|   |      | 4.3.2     | Use of TEMPLATE                                 | 176 |

|   |      | 4.3.3     | Vector description styles for timing arcs       | 178 |

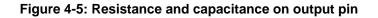

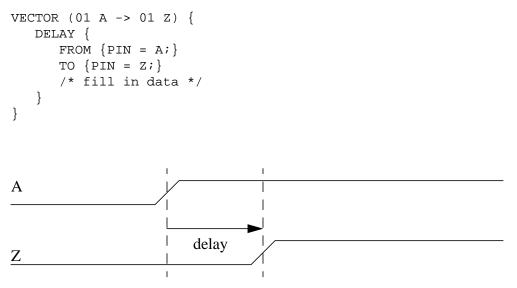

|   |      | 4.3.4     | Vectors for delay, power and timing constraints | 179 |

|   | 4.4  | Combin    | ing tables and equations                        | 181 |

|   |      | 4.4.1     | Table vs equation                               | 181 |

|   |      | 4.4.2     | Cell with Multiple Output Pins                  | 182 |

|   |      | 4.4.3     | PVT Derating                                    | 183 |

|   | 4.5  | Use of A  | Annotations                                     | 185 |

|   |      | 4.5.1     | Annotations for a PIN                           | 185 |

|   |      | 4.5.2     | Annotations for a timing arc                    | 186 |

|   |      | 4.5.3     | Creating Self-explaining Annotations            | 187 |

|   | 4.6  | Providir  | ng a fall-back position for applications        | 187 |

|   |      | 4.6.1     | Use of DEFAULT                                  | 187 |

|   | 4.7  | Bus Mo    | deling                                          | 189 |

|   |      |           |                                                 |     |

|      | 4.7.1    | Tristate Driver                                           | 189    |

|------|----------|-----------------------------------------------------------|--------|

|      | 4.7.2    | Bus with multiple drivers                                 | 191    |

|      | 4.7.3    | Busholder                                                 | 192    |

| 4.8  | Wire mo  | odels                                                     | 192    |

|      | 4.8.1    | Basic Wire Model                                          | 192    |

|      | 4.8.2    | Wire select model                                         | 193    |

| 4.9  | Megace   | ll Modeling                                               | 194    |

|      | 4.9.1    | Expansion of Timing Arcs                                  | 194    |

|      | 4.9.2    | Two-port memory                                           | 195    |

|      | 4.9.3    | Three-port memory                                         | 198    |

|      | 4.9.4    | Annotation for pins of a bus                              | 198    |

|      | 4.9.5    | Skew for simultaneously switching signals on a bus        | 199    |

| 4.10 | Special  | cells                                                     | 200    |

|      | 4.10.1   | Pulse generator                                           | 200    |

|      | 4.10.2   | VCO                                                       | 200    |

| 4.11 | Core M   | odeling                                                   | 201    |

|      | 4.11.1   | Digital Filter                                            | 201    |

| 4.12 | Connect  | tivity                                                    | 203    |

|      | 4.12.1   | External connections between pins of a cell               | 203    |

|      | 4.12.2   | Allowed connections for classes of pins                   | 204    |

| 4.13 | Signal I | ntegrity                                                  | 206    |

|      | 4.13.1   | I/V curves                                                | 206    |

|      | 4.13.2   | Driver resistance                                         | 208    |

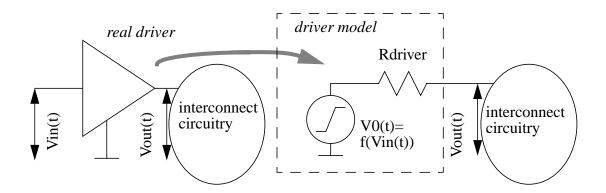

| 4.14 | Resistar | nce and Capacitance on a Pin                              | 211    |

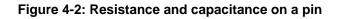

|      | 4.14.1   | Self-Resistance and Capacitance on Input Pin              | 211    |

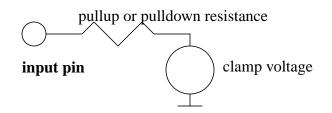

|      | 4.14.2   | Pullup and Pulldown Resistance on Input Pin               | 211    |

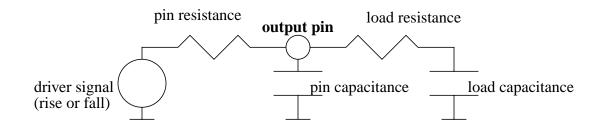

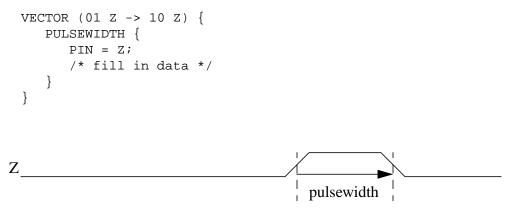

|      | 4.14.3   | Pin and Load Resistance and Capacitance on Output Pin     | 212    |

| 4.15 | ALF/SD   | DF cross reference                                        | 213    |

|      | 4.15.1   | SDF delays                                                | 213    |

|      | 4.15.2   | SDF timing constraints                                    | 218    |

|      | 4.15.3   | SDF conditions and labels for delays and timing constrain | nts226 |

|      |          |                                                           |        |

# Section 1 Introduction

### 1.1 Motivation

Design of digital integrated circuits has become an increasingly complex process. More functions get integrated into a single chip, yet the cycle time of electronic products and technologies has become considerably shorter. It would be impossible to successfully design a chip of today's complexity within the time-to-market constraints without extensive use of EDA tools, which have become an integral part of the complex design flow. The efficiency of the tools and the reliability of the results for simulation, synthesis, timing analysis, and power analysis rely significantly on the quality of available information about the cells in the technology library.

New challenges in the design flow, e.g. power analysis, arise as the traditional tools and design flows hit their limits of capability in processing complex designs. As a result, new tools emerge, and libraries are needed in order to make them work properly. Library creation (generation) itself has become a very complex process and the choice or rejection of a particular application (tool) is often constrained or dictated by the availability of a library for that application. The library constraint may prevent designers from choosing an application program that is best suited for meeting specific design challenges. Similar considerations may inhibit the development and productization of such an application program altogether. As a result, competitiveness and innovation of the whole electronic industry may stagnate.

In order to remove these constraints, an industry-wide standard for library format, Advanced Library Format (ALF), is proposed. It enables the EDA industry to develop innovative products and the ASIC designers to choose the best product without library format constraints. Since ASIC vendors have to support a multitude of libraries according to the preferences of their customers, a common standard library is expected to significantly reduce the library development cycle and facilitate the deployment of new technologies sooner.

## 1.2 Goals

The basic goals of the proposed library standard are:

- *simplicity* library creation process must be easy to understand and not become a cumbersome process only known by a few experts.

- *generality* tools of any level of sophistication must be able to retrieve necessary information from the library.

- expandability for early adoption and future enhancement possibilities

- *flexibility* the choice of keeping information in one library or in separate libraries must be in the hand of the user; it should not be dictated by the standard.

- *efficiency* the complexity of the design information requires that the process of retrieving information from the library does not become a bottleneck. The right trade-off between compactness and verbosity must be found.

- *ease of implementation* backward compatibility with existing libraries must be provided, and translation to the new library must be an easy task.

- · conciseness unambiguous description and accuracy of contents

- acceptance preference for the new standard library over existing libraries.

### 1.3 Target Applications

The fundamental purpose of ALF is to serve as the primary database for all 3rd party applications of ASIC cells. In other words, it is an elaborate and formalized version of the databook.

In the early days, databooks provided all the information a designer needed for choosing a cell in a particular application: Logic symbols, schematics and truth table provided the functional specification for simple cells. For more complex blocks, the name of the cell (e.g. asynchronous ROM, synchronous 2-port RAM, 4-bit synchronous up-down counter) and timing diagrams conveyed the functional information. The performance characteristics of each cell were provided by the loading characteristics, delay and timing constraints, and some information about DC and AC power consumption. The designers chose the cell type according to the functionality, estimated the performance of the design, and eventually re-implemented it in an optimized way as necessary to meet performance constraints.

Design automation enabled tremendous progress in efficiency, productivity and the ability to deal with complexity, yet it did not change the fundamental requirements for ASIC design. Therefore, ALF needs to provide models with *functional* information and *performance* information, primarily including timing and power. Signal integrity characteristics, such as noise margin can also be included under performance category. Such information is typically found in any databook for analog cells. At deep sub-micron levels digital cells behave similar to analog cells as electronic devices bound by physical laws and therefore not infinitely robust against noise.

Table 1-1 shows a list of applications used in ASIC design flow and their relationship to ALF. The boundary between supported and not supported applications can be defined by the *physical* information provided by ALF. Information needed for area and performance estimation and optimization, notably by synthesis and design planning tools, is provided by ALF. On the other hand, layout information is considered to be available in complementary libraries such as LEF. Please note that ALF covers *library* data, whereas *design* data must be provided in other formats.

| application         | functional model | performance model | physical model       |

|---------------------|------------------|-------------------|----------------------|

| timing analysis     | N/A              | supported by ALF  | N/A                  |

| power analysis      | N/A              | supported by ALF  | N/A                  |

| simulation          | derived from ALF | derived from ALF  | N/A                  |

| synthesis           | supported by ALF | supported by ALF  | supported by ALF     |

| scan insertion      | supported by ALF | N/A               | N/A                  |

| RTL design planning | derived from ALF | supported by ALF  | planned for ALF      |

| signal integrity    | N/A              | supported by ALF  | N/A                  |

| layout              | N/A              | N/A               | not supported by ALF |

| Table 1-1 | Target applications | and models sur | norted by ALE |

|-----------|---------------------|----------------|---------------|

|           | rarget applications | anu moueis sup |               |

Historically, a functional model was virtually identical to a simulation model. A functional gate-level model was used by the proprietary simulator of the ASIC company, and it was easy to lump it together with a rudimentary timing model. Timing analysis was done through dynamic functional simulation. However, with the advanced level of sophistication of both functional simulation and timing analysis, this is no longer the case. The capabilities of the functional simulators have evolved far beyond the gate-level, and timing analysis has been decoupled from simulation.

RTL design planning is an emerging application type aiming to produce "virtual prototypes" of complex for system-on-chip (SOC) designs. RTL design planning is thought of as a combination of some or all of RTL floorplanning and global routing, timing budgeting, power estimation, and functional verification, as well as analysis of signal integrity, EMI, and thermal effects. The library components for RTL design planning range from simple logic gates to parameterizeable macro-functions, such as memories, logic building blocks, and cores.

From the point of view of library requirements, applications involved in RTL design planning need functional, performance, and physical data. The functional aspect of design planning includes RTL simulation and formal verification. The performance aspect covers timing and power as primary issues, while signal integrity, EMI, and thermal effects are emerging issues. The physical aspect is floorplanning. As stated previously, the functional and performance models of components can be described in ALF. ALF partially covers the requirements for physical data, while the layout information is considered as complementary.

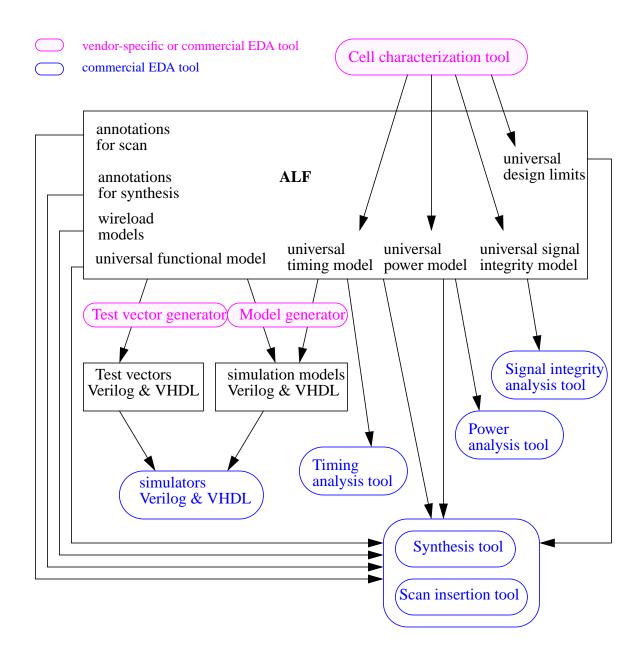

The figure 1-1 shows how ALF provides information to various design tools.

Figure 1-1: ALF and its target applications

The worldwide accepted standards for hardware description and simulation are VHDL and Verilog. Both languages have a wide scope of describing the design at various levels of abstraction: behavioral, functional, synthesizable RTL, gate level. There are many ways to describe gate-level functions. The existing simulators are implemented in such a way that some constructs are more efficient for simulation run time than others. Also, how the simulation model handles timing constraints is a trade-off between efficiency and accuracy. Developing efficient simulation models which are functionally reliable (i.e. pessimistic for detecting timing constraint violation) is a major development effort for ASIC companies.

Hence, the use of a particular VHDL or Verilog simulation model as primary source of functional description of a cell is not very practical. Moreover, the existence of two simulation standards makes it difficult to pick one as a reference with respect to the other. The purpose of a generic functional model is to serve as an absolute reference for all applications that require functional information. Applications such as synthesis, which need functional information merely for recognizing and choosing cell types, can use the generic functional model directly. For other applications such as simulation and test, the generic functional model enables automated simulation model and test vector generation and verification, which has a tremendous benefit for the ASIC industry.

With progress of technology, not only the cost constraints but also the set of physical constraints under which the design will function or not have increased dramatically. Therefore the requirements for detailed characterization and analysis of those constraints, especially timing and power in deep submicron design, are much more sophisticated than they used to be. Only a subset of the increasing amount of characterization data appears in today's databooks.

ALF provides a generic format for all type of characterization data, without restriction to stateof-the art timing models. Power models are the most immediate extension, and they have been the starter and primary driver for ALF.

Detailed timing and power characterization needs to take into account the *mode of operation* of the ASIC cell, which is related to the functionality. ALF introduces the concept of *vector-based modeling*, which is a generalization and a superset of today's timing and power modeling approaches. All existing timing and power analysis applications can retrieve the necessary model information from ALF.

### 1.4 Conventions

The syntax for description of lexical and syntax rules uses following conventions.

| ::=    | definition of a syntax rule                                           |  |  |

|--------|-----------------------------------------------------------------------|--|--|

|        | alternative definition                                                |  |  |

| [item] | an optional item                                                      |  |  |

| [item1 | item2   ]<br>optional item with alternatives                          |  |  |

| {item} | optional item that can be repeated                                    |  |  |

| {item1 | item2 $\mid$ } optional items with alternatives which can be repeated |  |  |

| item   | item in boldface font is taken verbatim                               |  |  |

| item   | item in italic is for explanation purpose only                        |  |  |

The syntax for explanation of semantics of expressions uses the following conventions.

=== left side and right side expressions are equivalent

<item> a placeholder for an item in regular syntax

## 1.5 Organization of this manual

This document presents the Advanced Library Format (ALF), a new standard library format for ASIC cells, blocks and cores, containing power, timing, functional, and physical information.

In the first chapter, motivation and goals of ALF are defined.

The second chapter describes the underlying concepts for functional modeling, cell characterization for timing and power, and additional modeling features for synthesis and test.

The third chapter is the Language Reference Manual (LRM).

The fourth chapter provides application notes.

# Section 2 Characterization and Modeling

This chapter elaborates on the basics of cell modeling and characterization, which is the primary source of library information.

## 2.1 Basic Concepts

The functional models within an ASIC library describe functions and algorithms of hardware components, as opposed to synthesizeable functions or algorithms. The functional modeling language for the ASIC library is designed to make the description of existing hardware easy and efficient. The scope here is different from a hardware description language (HDL) or a programming language designed to specify functionality without other aspects of hardware implementation.

Functional description provides boolean functions or truth tables, including state variables for sequential logic. Boolean and arithmetic operators for scalars and vectors are also provided. Combinational and sequential logic cells, macrocells (e.g. adders, multipliers, comparators), and atomic megacells (e.g. memories) can be modeled with these capabilities.

Vectors describe the stimuli for characterization. This encompasses both the concept of timing arcs and logical conditions. An exhaustive set of vectors can be generated from functional information, although the complexity of the exhaustive set precludes it from practical usage. The characterizer makes a choice of the relevant subset for characterization.

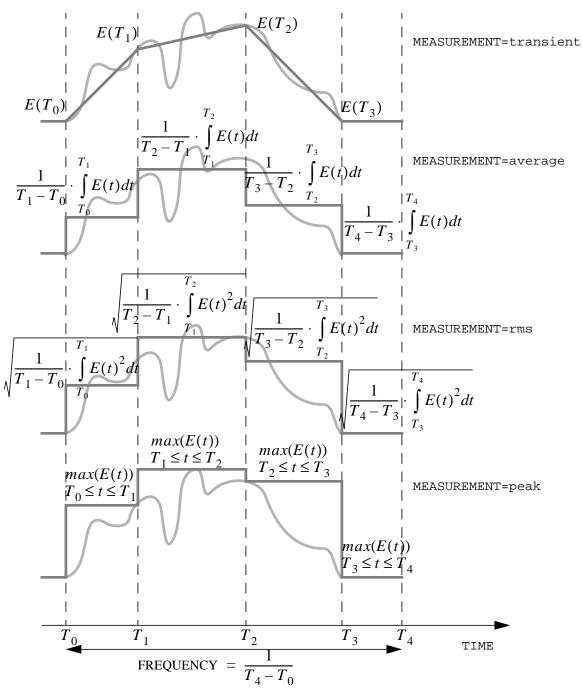

Power characterization is a superset of timing characterization using the same set and range of characterization variables: load, input slew rate, skew between multiple switching inputs, voltage, temperature. Characterization measurements, such as delay, output slew rate, average current in time window, bounds of allowed skew for timing constraints, etc. can be described as functions of the characterization variables, either by equations or using lookup tables. More complicated calculation algorithms cannot be described explicitly in the library, but can be referenced using templates.

A core is not an atomic megacell, since it can be split up into smaller components. Templates provide the capability of defining and reusing blocks consisting of atomic constructs or of other blocks. Thus a hierarchical description of the complete core can be created in a simple and efficient way.

Abstraction is required for the characterization of megacells: vectors describe events on buses rather than on scalar pins; number and range of switching pins within a bus become additional characterization variables. Characterization measurements are expandable and can be extrapolated from scalar pin to bus.

## 2.2 Functional Modeling

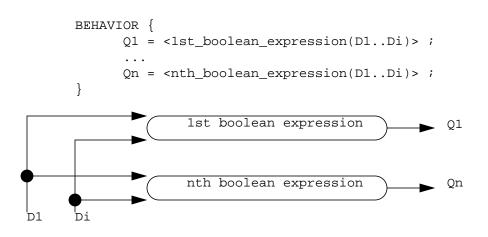

### 2.2.1 Combinational Logic

Combinational logic can be described by continuous assignments of boolean values (True, False) to output variables as a function of boolean values of input variables. Such functions can be expressed in either equation format or table format<sup>1</sup>.

Let us consider an arbitrary continuous assignment

$z = f(a_1 \dots, a_n)$

In a dynamic or simulation context, the left-hand side (LHS) variable z is evaluated whenever there is a change in one of the right-hand side (RHS) variables  $a_i$ . No storage of previous states is needed for dynamic simulation of combinational logic.

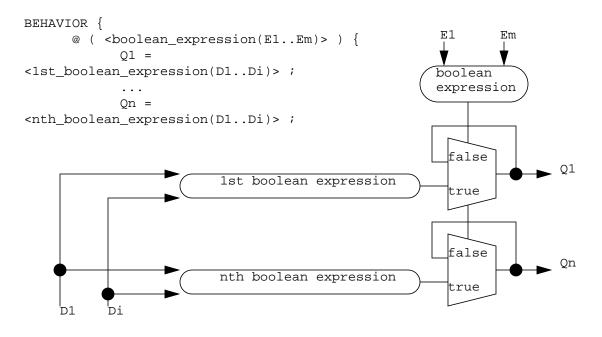

### 2.2.2 Level Sensitive Sequential Logic

In sequential logic, an output variable  $z_j$  can also be a function of itself, i.e. of its previous state. The sequential assignment has the form

$z_{j} = f(a_{1} \dots a_{n}, z_{1} \dots z_{m})$

The RHS cannot be evaluated continuously, since a change in the LHS as a result of a RHS evaluation will trigger a new RHS evaluation repeatedly, unless the variables attain stable values. Modeling capabilities of sequential logic with continuous assignments would be restricted to systems with oscillating or self-stabilizing behavior.

However, if we introduce the concept of triggering conditions for the LHS, we have everything we need for modeling *level-sensitive* sequential logic. The expression of a triggered assignment can look like this:

$@ g(b_1 \ldots, \ldots b_k) z_j = f(a_1 \ldots, \ldots a_n , z_1 \ldots, \ldots z_m)$

The evaluation of f is activated whenever the *triggering function* g is true. The evaluation of g is self-triggered, i.e. at each time when an argument of g changes its value. If g is a boolean expression like f, we can model all types of *level-sensitive sequential logic*.

During the time when g is true, the logic cell behaves exactly like combinational logic. During the time when g is false, the logic cell holds its value. Hence one memory element per state bit is needed.

### 2.2.3 Edge Sensitive Sequential Logic

In order to model *edge-sensitive sequential logic*, we need to introduce notations for logical transitions in addition to logical states.

If the triggering function g is sensitive to logical transitions rather than to logical states, the function g evaluates to true only for an infinitely small time, exactly at the moment when the

<sup>1.</sup> Rather than defining a new syntax for boolean equations, we are just adopting existing notations people are familiar with. Those notations can already be found in the ANSI C standard, and they are widely used in popular script languages such as PERL as well as in HDLs like VERILOG.

transition happens. The sole purpose of g is to trigger an assignment to the output variable through evaluation of the function f exactly at this time.

Edge-sensitive logic requires storage of the previous output state and the input state (to detect a transition). In fact, all implementations of edge-triggered flipflops require at least two storage elements. For instance, the most popular flipflop architecture features a master latch driving a slave latch.

Using transitions in the triggering function for value assignment, the functionality of a positive edge triggered flipflop can be described as follows in ALF:

@ (01 CP)  $\{Q = D;\}$

which reads "at rising edge of CP, assign Q the value of D".

If the flipflop also has an asynchronous direct clear pin (CD), the functional description consists of either two concurrent statements or two statements ordered by priority:

```

// concurrent style

@ (!CD) {Q = 0;}

@ (01 CP && CD) {Q = D;}

// priority (if-then-else) style

@ (!CD) {Q = 0;} : (01 CP) {Q = D;}

```

#### Figure 2-1: Model of a flipflop with asynchronous clear in ALF

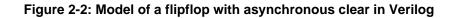

The following two examples show corresponding simulation models in Verilog and VHDL:

```

// full simulation model

always @(negedge CD or posedge CP) begin

if ( ! CD ) Q <= 0;

else if (CP && !CP_last_value) Q <= D;

else Q <= 1'bx;

end

always @ (posedge CP or negedge CP) begin

if (CP===0 | CP===1'bx) CP_last_value <= CP ;

end

// simplified simulation model for synthesis

always @(negedge CD or posedge CP) begin

if ( ! CD ) Q <= 0;

else Q <= D;

end

```

```

// full simulation model

process (CP, CD) begin

if (CD = '0') then

Q <= '0';

elsif (CP'last value = '0' and CP = '1' and CP'event) then

Q \leq D;

elsif (CP'last_value = '0' and CP = 'X' and CP'event) then

Q <= 'X';

elsif (CP'last_value = 'X' and CP = '1' and CP'event) then

Q <= 'X';

end if;

end process;

// simplified simulation model for synthesis

process (CP, CD) begin

if (CD = '0') then

Q <= '0';

elsif (CP = '1' and CP'event) then

Q <= D;

end if;

end process;

```

#### Figure 2-3: Model of a flipflop with asynchronous clear in VHDL

The following differences in modeling style can be noticed: VHDL and Verilog provide the list of sensitive signals at the beginning of the process or always block, respectively. The information of level-or edge-sensitivity must be inferred by if-then-else statements inside the block. ALF shows the level-or-edge sensitivity as well as the priority directly in the triggering expression. Verilog has another particularity: The sensitivity list indicates whether at least one of the triggering signals is edge-sensitive, by the use of negedge or posedge. However, it does not indicate which one, since either none or all signals must have negedge or posedge qualifiers. Furthermore, posedge is any transition with 0 as initial state or 1 as final state. A positive-edge triggered flipflop will be inferred for synthesis, yet this flipflop will only work correctly if both the initial state is 0 and the final state is 1. Therefore a simulation model for verification must be more complex than the model in the synthesizeable RTL code. In Verilog, the extra non-synthesizeable code must also reproduce the relevant previous state of the clock signal, whereas VHDL has built-in support for last\_value of a signal.

Other aspects of simulation models include performance and trade-off between accuracy and runtime, timing annotation etc.

ALF provides a canonical, compact and highly self-explaining description of the *functional specification* of a cell, from which simulation models for various applications can be derived.

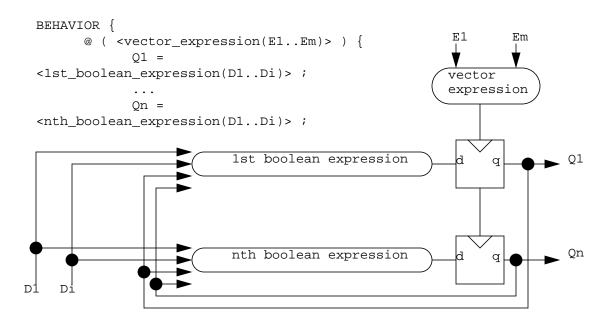

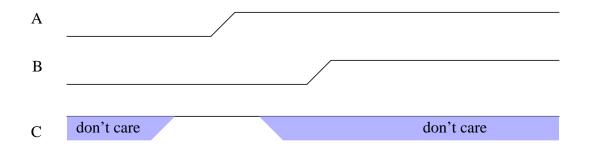

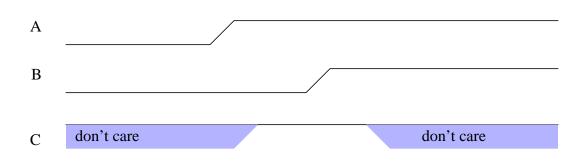

### 2.2.4 Vector-Sensitive Sequential Logic

In order to model generalized higher order sequential logic, the concept of vector expressions is introduced, an extension of the boolean expressions.

A vector expression describes sequences of logical events or transitions in addition to static logical states. A vector expression represents a description of a logical stimulus without timescale. It describes the order of occurrence of events.

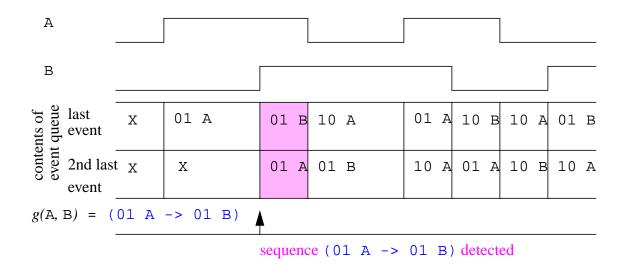

Using the -> operator (*followed by* operator), we have a general capability of describing a sequence of events or a vector. For example, consider the following vector expression:

01 A -> 01 B

which reads "rising edge on A is followed by rising edge on B".

A vector expression is evaluated by an event sequence detection function. Like a single event or a transition, this function evaluates true only at an infinitely short time when the event sequence is detected.

#### Figure 2-4: Example of event sequence detection function

The event sequence detection mechanism can be described as a queue that sorts events according to their order of arrival. The event sequence detection function evaluates true at exactly the time when a new event enters the queue and forms the required sequence, *i.e. the sequence specified by the vector expression* with its preceding events.

A vector-sensitive sequential logic can be called (N+1) order sequential logic, where N is the number of events to be stored in the queue. The implementation of (N+1) order sequential logic requires N memory elements for the event queue and 1 memory element for the output itself.

A sequence of events can also be gated with static logical conditions. For example,

(01 CP -> 10 CP) && CD

the pin CD must have state 1 from some time before the rising edge at CP to some time after the falling edge of CP. The pin CD can not go low (state 0) after the rising edge of CP and go high again before the falling edge of CP because this would insert events into the queue, and the sequence "rising edge on CP followed by falling edge on CP" would not be detected.

The formal calculation rules for general vector expressions featuring both states and transitions will be introduced in Section 3.5.4.

The concept of vector expression supports functional modeling of devices featuring digital communication protocols with arbitrary complexity.

## 2.3 Performance Modeling for Characterization

### 2.3.1 Timing Modeling

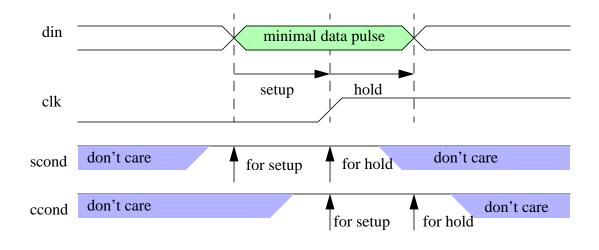

The timing models of cells consist of two types: *delay models* for combinational and sequential cells, and *timing constraint models* for sequential cells. Both types can be described by timing arcs. A timing arc is a sequence of two events that can be described by a vector expression "event e1 is followed by event e2".

For example, a particular input to output delay of an inverting logic cell is identified by the following timing arc:

01 A -> 10 Z

which reads "rising edge on input A is followed by falling edge on output Z".

A setup constraint between data and clock input of a positive edge triggered flipflop is identified by the following timing arc:

01 D -> 01 CP

which reads "rising edge on input D is followed by rising edge on input CP".

A crucial part in ASIC cell development is to characterize a model that describes the behavior of each timing arc with sufficient accuracy in order to guarantee correct functional behavior under all required operational conditions.

A delay model usually needs two output variables:

- *intrinsic delay*, measured between a well-defined threshold value of the input signal and a well-defined threshold value of the output signal

- *transition delay*, measured between two well-defined threshold values of the output signal. Hence the transition delay is a fraction of the total output transition time, also called *slew rate* or *edge rate*.

A timing constraint model needs just one output variable:

• A timing constraint is the *minimum or maximum allowed elapsed time* between two signals, measured between well-defined threshold values between those two signals. This definition is similar to the intrinsic delay, except there is no input-output relationship between the two signals. Both signals are usually inputs to the cell.

The actual values of transition times and load capacitances seen by each pin of a cell instance are calculated by a delay predictor. Delay prediction can be separated into two tasks:

- 1. Acquisition of information on pin capacitance, extracted or estimated layout parasitics for each net and fitting those into the load characterization model (lumped C, R, etc.)

- 2. Calculation of internal signal transition times based on the extracted internal load and on load and transition times at the boundaries of the system.

Lookup tables provide a general modeling capability without precluding any level of accuracy.

Equations may feature polynomial expressions, exponentials and logarithms, and arbitrary transcendent functions. For practical purpose, only the four basic arithmetic operations (+, -, \*, /) and exponentiation and logarithm will be supported for standard models.

Some models may require transcendent functions or complicated algorithms that cannot be expressed directly in equations. Other models and algorithms may need protection from being visible. In order to address needs that go beyond standard modeling features, a template-reference scheme is proposed: Any model which is neither in table nor in equation format needs to be a pointer to a customer-defined model which may reside outside the library.

| type of model | features                                            | purpose                                                                                                                                                                    |

|---------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| table         | discrete points, multidimensional                   | direct storage of characterization data,<br>direct accuracy control through mesh<br>granularity                                                                            |

| equation      | expressions with +, -, *, /, exponent,<br>logarithm | analytical model, well-suited for optimi-<br>zation purpose, more compact than table,<br>also usable for arithmetic operations on<br>tabulated data (scale, add, subtract) |

| reference     | pointer to any type of model                        | reuse of predefined model (which may<br>be table or equation), protection of user-<br>defined model                                                                        |

Table 2-1 Modeling choices for cell characterization library

Regardless of which type of model is chosen, there is a need to specify explicitly the meaning of the variables and the units. The specification of variables and units can be made outside the model and independent of the chosen model.

Since the set of variables should not be restrictive in order to allow any enhancements (e.g. move from a lumped capacitance to an RC model), *context-sensitive keywords* are proposed (e.g. "load", "slewrate"). The application parser need not know the meaning of the context-sensitive keyword, except that it is used as a variable in a model and that it has some unit attached to it, e.g. picofarad, nanosecond etc.

### 2.3.2 Power Modeling

A power model is an extension of the delay model for each timing arc using a third variable:

• *scaled average current*, measured by integrating and scaling the total transient current through the power supply of the cell for the specific timing arc or vector. The current measurement can start anytime before the first event of the vector starts and can end anytime after all transients of the vector have stabilized.

Variants of this model are scaled average power and energy, which are obtained by simple scaling of average current measurements:

```

power = current * Vdd

energy = current * Vdd * integration time

```

The set of vectors causing power consumption within a cell is a superset of those vectors causing the cell output to switch. While only the vectors with switching output are needed for delay characterization, more vectors are needed for accurate power characterization.

For example, consider a flipflop, which consumes power at every edge of the clock, even if the output does not switch. The vectors for delay and power characterization can be described as follows:

01 CP -> 01 Q 01 CP -> 10 Q

The vectors for power characterization with only clock-switching can be described as follows:

01 CP && Q==D 10 CP && Q==D

The D input having the same value as the Q output is a necessary and sufficient condition that the output will not switch at the rising edge of CP and that the value transferred to the master latch at the falling edge of CP will be the same as already stored. Hence those two vectors capture the actual power dissipation only within the clock buffers. Additional power vectors can be defined to capture the power dissipation within the data buffers and the master latch etc.

For a 2-input AND gate with input pins A, B and output pin z a *glitch* is observed if the event 01 A is detected and then the event 10 B is detected before the input-to-output delay elapses. It is possible to describe the glitch by a higher-order vector.

In dynamic simulation with transport delay mode, the glitch would appear as follows:

01 A -> 10 B -> 01 Z -> 10 Z

Simulation featuring *transport delay mode with invalid-value-detection* would exhibit the glitch as follows:<sup>2</sup>

01 A -> 10 B -> 'b0'bX Z -> 'bX'b0 Z

Simulation with *inertial delay mode* would suppress the output transitions:

(01 A -> 10 B) && !Z

The last expression can be used for each of the three simulation modes, since !z is always true from beginning to end of the sequence  $01 A \rightarrow 10 B$ , in particular at the time when the sequence  $01 A \rightarrow 10 B$  is detected.

<sup>2.</sup> use based edge literals to avoid parser ambiguity.

Each way of expressing vectors can be derived from the cell functionality. The different examples for delay vectors (i.e. timing arcs), power vectors, and glitch vectors emphasize the rich potential of modeling capabilities using vector expressions.

State-dependent *static power* is also within the scope of vector-based power models. Static power consumption is activated by a simulation model in the same way as level-sensitive logic in functional modeling by a boolean expression, whereas *transient power* consumption is activated similar to edge-sensitive logic by a vector expression.

The advantages of adding power models within each delay vector and providing extra power vectors are the following:

- straightforward extension of delay characterization

- capable of yielding the most detailed and accurate model on gate-level

- each vector defines a comprehensive stimulus for power measurements

More abstract vector expressions are provided for power modeling of complex blocks, where simplification is needed in order to deal with the complexity of characterization vectors.

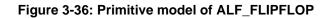

### 2.3.3 Modeling for signal integrity

The concept of vector-based cell characterization with multiple variables also accommodates the requirements for signal integrity modeling. Although signal integrity is closely related to interconnect parasitics, i.e. extracted *design* information, there must be data in the cell *library* in order to support signal integrity analysis.

- Crosstalk analysis needs characterization of *driver resistance* on output pins and *noise margin* on input pins.

- IR drop and electromigration analysis on power supply lines needs characterization of average currents as for power analysis, *RMS currents* and *current waveforms*.

- Electromigration (EM) analysis within cells needs characterization of *current limits*. In a direct evaluation approach, the current limits are checked against the actual currents. The latter data comes from the characterization for power and IR drop. In an indirect evaluation approach, the current limits may be expressed as *frequency-dependent load limits* and/or *slewrate limits*.

- Hot electron (HE) analysis within cells needs characterization of *flux* (charge density) or *fluence* (accumulated charge density over time) and its respective limits for performance degradation. In a direct evaluation approach, the flux or fluence limits are checked against the actual flux or fluence, respectively. In an indirect evaluation approach, the limits of performance degradation due to fluence may be expressed as *frequency-dependent load limits* and/or *slewrate limits*, in the same way as for electromigration.

The characterization vector set for driver resistance is a subset of delay characterization vectors. In buffered cells, the driving input does not matter, since the driver resistance seen at

the output is the same. However, there is always a different driver resistance for rise and fall, which is also dependent on process, voltage, temperature.

Noise margin characterization is especially important for control and data pins of sequential cells. The set of characterization vectors is complementary to the timing constraint characterization vectors. For instance, noise margin on a clock pin is complementary to the pulsewidth constraint. If pulsewidth corresponds to the smallest possible signal causing a *valid* functional reaction, then noise margin corresponds to the largest possible signal causing *no* functional reaction.

The characterization vector set for IR drop and EM on power supply lines is essentially the same as for power analysis, only the set of data per vector is richer. IR drop analysis may use average currents, peak currents, or current waveforms. EM analysis may use average, peak, RMS or a combination of the above.

The characterization vector set for EM and HE effect occurring within cells is very similar to the characterization vector set for power analysis, depending whether a direct or indirect evaluation approach is used.

In summary, modeling for crosstalk is a natural extension of modeling for timing, whereas IR drop, EM and HE modeling are natural extensions of modeling for power.

## 2.4 Physical modeling for synthesis and test

### 2.4.1 Cell modeling

Physical modeling of cells requires annotating cell properties (e.g. area, height, width, aspect ratio). The set of annotated properties give an application such as synthesis a choice to pick one cell from a set of functionally equivalent cells, if one property is more desirable than another one under given synthesis goals and constraints.

Cell pins can also have annotated properties, such as pin capacitance, voltage swing, switching threshold etc.

Most of the requirements for the modeling of test are already fulfilled by the functional model. Declaration of pins and their direction (input, output, bidirectional) is already a generic requirement for cell modeling.

Scan insertion tools require specific annotations about cell and pin properties relevant for scan test. They also require reference to equivalent non-scan cells. An equivalent non-scan cell is a scan cell, when all scan specific hardware (e.g. multiplexor, scan clock) is removed.

The variables used in the functional model must have their counterpart in the pin declaration. Only primary input pins can be primary inputs of functions, while primary output pins, internal pins, or virtual pins can be primary or intermediate outputs of functions. Furthermore, test vectors for fault coverage can be derived from the functional model in a formal way.

The remainder of the modeling for test requirements can be covered by annotations of cell properties and cell pin properties. For instance, a cell can be labeled as a scan-flipflop, a pin can be labeled as scan input or mode select pin.

### 2.4.2 Wire modeling

The purpose of *wire modeling* is to get good estimates of *parasitic resistance* and *capacitance* as a function of *fanout*. These estimates are technology specific, and they depend on metal layer, sheet resistance, self-capacitance per unit wirelength, fringe capacitance per unit wirelength, via resistance for wires routed through multiple layers.

The wires can be characterized by types, in a similar to cells. For example,

```

// wire with fanout ≤ 5 routed in metal 1, 2

WIRE small_wire {

ATTRIBUTE { metal1 metal2 }

LIMIT { FANOUT { MAX = 5; } }

/* fill in data */

}

// wire with 10 ≤ fanout ≤ 20 routed in metal 1, 2, 3, 4, 5

WIRE big_wire {

ATTRIBUTE { metal1 metal2 metal3 metal4 metal5 }

LIMIT { FANOUT { MIN = 10; MAX = 20; } }

/* fill in data */

}

```

From a modeling standpoint, no particular language is required for performance modeling of wires that would be different from performance modeling of cells. The fanout will be an input variable, and capacitance and resistance would be output variables. The values can be expressed either in tables or in equations. Usually first order equations (with slope and intercept) are used for wire modeling.

# **Section 3**

# **Library Format Specification**

This section discusses the object model used by ALF and provides the syntax rules for all objects. The syntax rules are provided in standard BNF form.

## 3.1 Object Model

A *library* consists of one or more *objects*. Each object is defined by a keyword and an optional name for the object and an optional *value* of the object.

A *keyword* defines the type of the object. Section 3.1.2 and Section 3.1.3 define various types of objects used in ALF and related keywords.

An optional *identifier* (also called *name*) following the keyword defines the *name of the object*. This name must be used while referencing an object inside other objects in the library. If an object is not referenced by name, then the object need not be named.

A *literal* defines an optional value associated with the object. An *expression* can be used when the value of the object cannot be expressed as a literal.

An object may contain one or more objects. The containing object is called a *hierarchical object*. The contained objects are called *children objects*. The children objects are defined and referenced inside curly braces ({}) in the description of the hierarchical object. An object without children is called an *atomic object*.

*Forward referencing* of objects is not allowed. Therefore, all objects must be defined before they can be instantiated. This allows library parsers to be one-pass parsers.

### 3.1.1 Syntax conventions

In order to make ALF easy to parse, we use syntax conventions that are followed by the existing syntax rules (see Section 3.4) and should also be followed for future extensions of the grammar.

The first token of the object is the object type identifier, followed by a name (mandatory or optional, depending on object type), followed by (mandatory or optional) = and value assignment, followed by (mandatory or optional) children objects enclosed by curly braces. Objects with more than one token (i.e. name and/or value) and without children are terminated with *i*.

Examples:

1. unnamed object without value assignment:

MY\_OBJECT\_TYPE

```

or

MY_OBJECT_TYPE {

//fill in children objects

}

2. unnamed object with value assignment:

MY_OBJECT_TYPE = my_object_value;

or

MY_OBJECT_TYPE = my_object_value {

//fill in children objects

}

3. named object without value assignment:

MY_OBJECT_TYPE my_object_name;

or

MY OBJECT TYPE my object name {

//fill in children objects

}

4. named object with value assignment:

MY_OBJECT_TYPE my_object_name = my_object_value;

or

MY_OBJECT_TYPE my_object_name = my_object_value {

//fill in children objects

}

```

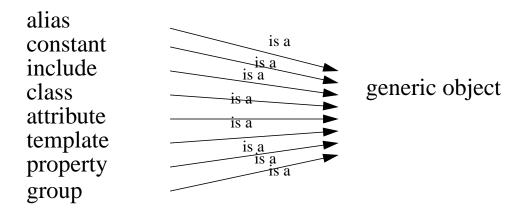

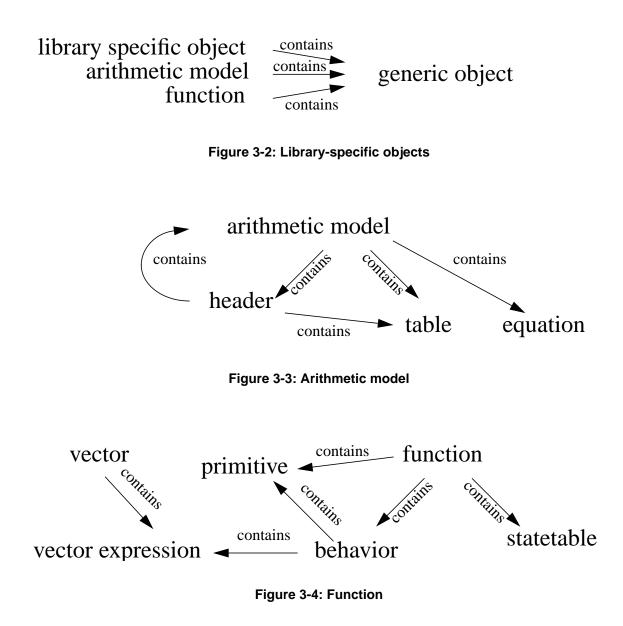

The objects in ALF are divided into four categories - generic objects, library-specific objects, arithmetic models, and functions.

### 3.1.2 Generic Objects

A generic object can appear at every level in the library within any scope. The semantics of a generic object must be understood by any ALF compiler if the generic object is within the scope of application for that compiler.

The following objects shall be considered generic objects:

Figure 3-1: Generic objects

### 3.1.2.1 CONSTANT

A *CONSTANT* object is a named object with value assignment and without children objects. Value is a number.

Example:

CONSTANT vdd = 3.3;

### 3.1.2.2 ALIAS

An ALIAS object is a named object with value assignment and without children objects. Value is a string.

Example:

ALIAS RAMPTIME = SLEWRATE;

### 3.1.2.3 INCLUDE

An *INCLUDE* object is a named object without value assignment and without children. The name is a quoted string containing the name of a file to be included.

Example:

INCLUDE "primitives.alf";

Since the file name is a quoted string, any special symbols (like  $\sim$  or \*) are allowed within the filename. The interpretation of those (for file search path etc.) is up to the application.

### 3.1.2.4 CLASS

A *CLASS* object is a named object with optional value assignments and children objects. The name can be used by other objects to reference the class object.

Example:

```

CLASS my_class { ... }

...

MY_OBJECT_TYPE my_object {

CLASS = my_class;

} // my_object belongs to my_class

```

### 3.1.2.5 ATTRIBUTE

An *ATTRIBUTE* object is an unnamed object without value, but has children objects. The attribute object shall be the child object of another object. The children of the attribute object are unnamed objects that can have other unnamed objects as children objects. The purpose of an attribute object is to provide free association of objects with attributes when there is no special category available for the attributes.

Examples:

```

CELL rr_8x128 {

ATTRIBUTE {ROM ASYNCHRONOUS STATIC}

}

PIN read_write_select {

ATTRIBUTE {READ{POLARITY=low;} WRITE{POLARITY=high;}}

}

```

#### 3.1.2.6 TEMPLATE

A *TEMPLATE* object is a named object with one or more children objects. Any valid ALF object can be a child object of a template object. Identifiers enclosed between < and > are recognized as *placeholders*. When a template object is used, each of its placeholders must be referenced by order or by explicit name association.

Example:

```

TEMPLATE std_table {

CAPACITANCE {PIN=<pinl>; UNIT=pF; TABLE {0.02 0.04 0.08 0.16}}

SLEWRATE {PIN=<pin2>; UNIT=ns; TABLE {0.1 0.3 0.9}}

}

```

An instantiation of the above template object with explicit reference to placeholders by name:

std\_table{pin1=out; pin2=in;}

An instantiation of the above template object with implicit reference to placeholders by order:

std\_table{out in}

If a symbol within a placeholder appears more than once in the template definition, the order for implicit reference is defined by the first appearance of the symbol. Explicit referencing improves the readability and is the recommended usage.

A template instantiation can appear at any place within a hierarchical object, as long as the template object contains the structure of valid objects inside. Hierarchical templates contain other template objects.

#### 3.1.2.7 PROPERTY

A *PROPERTY* object is a named or an unnamed *annotation container*. It can be used at any level in the library. It is used for arbitrary parameter-value assignment.

Example:

```

PROPERTY items {

parameter1=value1;

parameter2=value2;

}

```

#### 3.1.2.8 GROUP

A GROUP object is a set of elements with commonality between them. Thus the common characteristics can be defined once for the group instead of being repeated for each element.

Example:

```

GROUP time_measurements = {DELAY SLEWRATE SKEW JITTER}

```

Thus the statement

```

time_measurements { UNIT = ns; }

```

replaces the following statements:

| DELAY    | $\{ UNIT = ns; \}$ |

|----------|--------------------|

| SLEWRATE | $\{ UNIT = ns; \}$ |

| SKEW     | $\{ UNIT = ns; \}$ |

| JITTER   | $\{ UNIT = ns; \}$ |

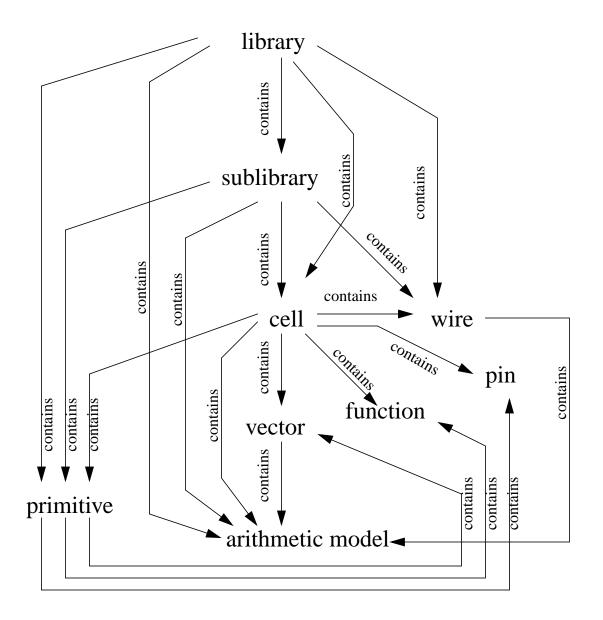

#### 3.1.3 Library-specific objects

The library-specific objects define their nature and their relationship to each other by containment rules. For example, a library may contain a cell, but a cell may not contain a library. However, both the library object and the cell object may contain any generic object. A generic object defined at the library level makes it visible inside the scope of that library. defining it on the cell level makes it visible inside the scope of that cell and its children objects.

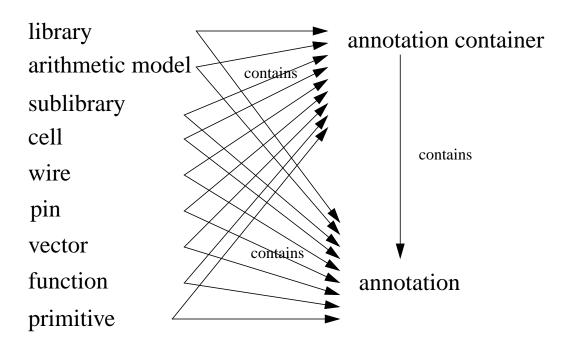

#### 3.1.4 Arithmetic models

An arithmetic model is an object that describes characterization data, or a more abstract, measurable relationship between physical quantities. The modeling language allows tabulated data as well as linear and non-linear equations. The equations consist of arithmetic expressions, for which the IEEE standards have been adopted.

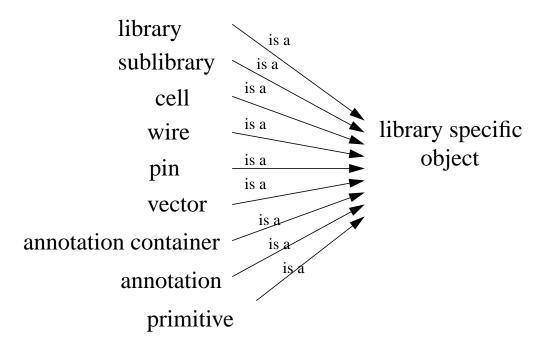

#### 3.1.5 **Functions**

A function is an object that describes the functional specification of a digital circuit (or a digital model of an analog or a mixed-signal circuit) in a canonical form. The modeling language allows behavioral models as well as statetables and structural models with primitives. The behavioral models contain boolean expressions, for which the IEEE standards have been adopted. Since boolean expressions are insufficient to describe sequential logic, ALF introduces new operators and symbols that can be used in conjunction with boolean operators and symbols. Expressions that use both the IEEE operators and the new operators, are called vector expressions.

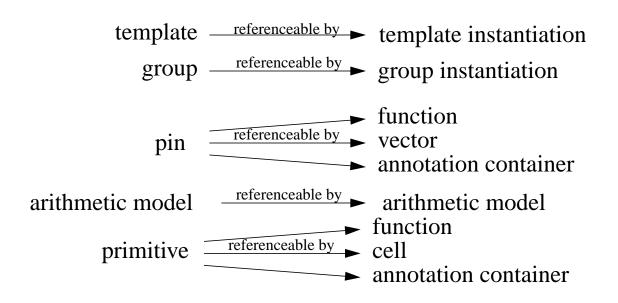

The following figures describe the four types of objects and their relationships with each other.

Note that a function can contain a primitive and a primitive can contain a function. See figure 3-7 and syntax descriptions in Section 3.4.11 and Section 3.4.16.

Figure 3-5: Annotations

Figure 3-6: Library-specific objects

Figure 3-7: Library objects and their relationships

Note that a function can contain a primitive and a primitive can contain a function. See figure 3-7 and syntax descriptions in Section 3.4.11 and Section 3.4.16.

### 3.2 Lexical rules

### 3.2.1 Character set

Each graphic character corresponds to a unique code of the ISO eight-bit coded character set [ISO 8859-1 : 1987(E)], and is represented (visually) by a graphical symbol.

# 3.2.2 Lexical tokens

The ALF source text files shall be a stream of lexical tokens. Each lexical token is either a *delimiter*, a *comment*, a *bit literal*, a *based literal*, an *edge literal*, a *number*, a *quoted string* or an *identifier*.

## 3.2.3 Whitespace Characters

The following characters shall be considered whitespace characters:

| Character            | ASCII code (hex) |

|----------------------|------------------|

| space                | 20               |

| vertical tab         | 0B               |

| horizontal tab       | 09               |

| line feed (new line) | 0A               |

| carriage return      | 0D               |

| form feed            | 0C               |

#### Figure 3-8: List of whitespace characters

Comments are also considered white space (see Section 3.2.6).

A whitespace character shall be ignored except when it separates other lexical tokens or when it appears in a quoted string.

## 3.2.4 Reserved and Non-reserved Characters

The ASCII character set shall be divided in three categories - whitespace (Section 3.2.3), reserved characters, and non-reserved characters. The reserved characters are symbols that make up punctuation marks and operators. The non-reserved characters shall be used for creating identifiers and numbers.

```

reserved_character ::=

& | | | ^ | ~ | + | - | * | / | % | ? | ! | = | < | > | :

| ( | ) | [ | ] | { | } | @ | ; | , | . | " | '

nonreserved_character ::=

letter | digit | _ | $

letter ::=

a | b | c | d | e | f | g | h | i | j | k | 1 | m

| n | o | p | q | r | s | t | u | v | w | x | y | z

| A | B | C | D | E | F | G | H | I | J | K | L | M

| N | O | P | Q | R | S | T | U | V | W | X | Y | Z

digit ::=

0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9

escape_character ::=

\

```

```

any_character ::=

reserved_character

nonreserved_character

escape_character

whitespace

```

#### Figure 3-9: Reserved and non-reserved characters

ALF shall treat uppercase and lowercase characters as the same characters. In other words, ALF is a *case-insensitive language*.

#### 3.2.5 Delimiters

A *delimiter* is either a reserved character or one of the following compound operators, each composed of two or three adjacent reserved characters:

#### Figure 3-10: Tokens that make up delimiters

Each special character in a single character delimiter list shall be a single delimiter unless this character is used as a character in a compound operator or as a character in a quoted string.

## 3.2.6 Comments

ALF has two forms to introduce comments.

A *single-line comment* shall start with the two characters // and end with a new line.

A *block comment* shall start with /\* and end with \*/. Comments shall not be nested. The single-line comment token // shall not have any special meaning in a block comment.

```

comment ::=

single_line_comment

block_comment

```

#### Figure 3-11: Single-line and block comments

#### 3.2.7 Numbers

Constant numbers can be specified as integer or real.

The *integer* is a decimal integer constant.

sign ::= + | -

```

unsigned ::= digit { _ | digit }

integer ::= [ sign ] unsigned

non_negative_number ::=

unsigned [ • unsigned ]

| unsigned [ • unsigned ] E [ sign ] unsigned

number ::=

[ sign ] non_negative_number

```

#### Figure 3-12: Integer and real numbers

### 3.2.8 Bit Literals

A bit literal shall represent a single bit constant.

```

bit_literal ::=

numeric_bit_literal

alphabetic_bit_literal

dont_care_literal

random_literal

numeric_bit_literal ::= 0 | 1

alphabetic_bit_literal ::=

X | Z | L | H | U | W

| x | Z | 1 | h | u | w

dont_care_literal ::= ?

random_literal ::= *

```

| Literal | Description                                  |

|---------|----------------------------------------------|

| 0       | value is logic zero                          |

| 1       | value is logic one                           |

| X or x  | value is unknown                             |

| L or l  | value is logic zero with weak drive strength |

| H or h  | value is logic one with weak drive strength  |

| W or w  | value is unknown with weak drive strength    |

| Z or z  | value is high-impedance                      |

| U or u  | value is uninitialized                       |

| ?       | value is any of the above, yet stable        |

| *       | value may randomly change                    |

| Table 3-1 : Single bit constants | Table | 3-1 : | Single | bit c | onstants |

|----------------------------------|-------|-------|--------|-------|----------|

|----------------------------------|-------|-------|--------|-------|----------|

## 3.2.9 Based Literals

A *based literal* is a constant expressed in a form that specifies the base explicitly. The base can be specified in *binary*, *octal*, *decimal* or *hexadecimal* format.

```

based literal ::=

binary_base { _ | binary_digit }

| octal_base { _ | octal_digit }

decimal_base { _ | digit }

hex_base { _ | hex_digit }

binary base ::=

'B | 'b

octal_base ::=

'0 | 'o

decimal_base ::=

'D | 'd

hex_base ::=

'H | 'h

binary_digit ::=

bit_literal

octal_digit ::=

binary_digit | 2 | 3 | 4 | 5 | 6 | 7

hex digit ::=

octal_digit | 8 | 9 | A | B | C | D | E | F | a | b | c | d | e | f

```

#### Figure 3-13: Based constants

The underscore (\_) shall be legal anywhere in the number except as the first character, and this character is ignored. This feature can be used to break up long numbers for readability purposes. No white space shall be allowed between base and digit token in a based literal.

When an alphabetic bit literal is used as an octal digit, it shall represent 3 repeated bits with the same literal. When an alphabetic bit literal is used as a hex digit, it shall represent 4 repeated bits with the same literal.

For example,

| 'o2xw0u | is same as | 'b010_xxx_www_000_uuu |

|---------|------------|-----------------------|

| 'hLux   | is same as | 'bLLL_uuuu_xxxx       |

# 3.2.10 Edge Literals

An *edge literal* shall be constructed by two bit literals or two based literals. It shall describe the transition of a signal from one discrete value to another. No white space shall be allowed within (between) the two literals. An underscore shall be allowed.

#### Figure 3-14: Edge literals

## 3.2.11 Quoted Strings

The *quoted string* shall be a sequence of zero or more characters enclosed between two quotation marks (") and contained on a single line. Character *escape codes* are used inside the string literal to represent some common special characters. The characters that may follow the backslash (\) and their meanings are listed below in Table 3-2.

#### Figure 3-15: A quoted string

| Symbol | ASCII Code<br>(octal) | Meaning               |

|--------|-----------------------|-----------------------|

| /a     | 007                   | alert/bell            |

| ∖h     | 010                   | backspace             |

| \t     | 011                   | horizontal tab        |

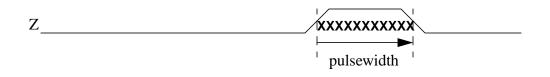

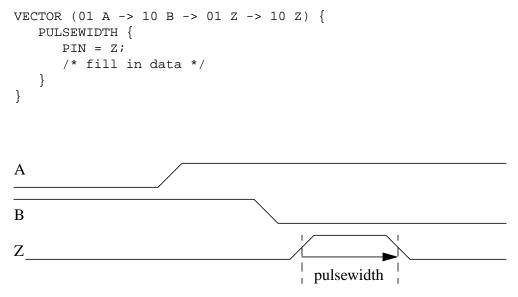

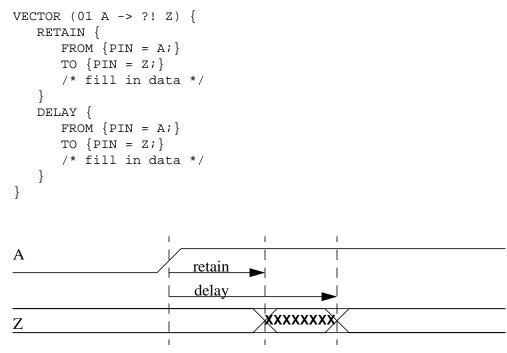

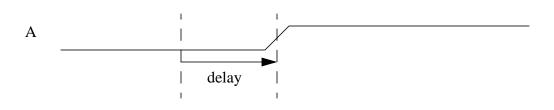

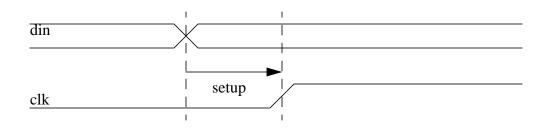

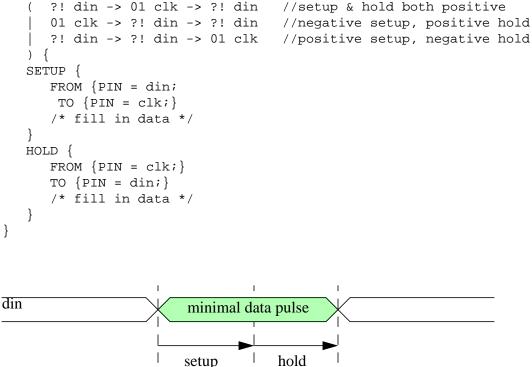

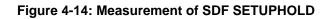

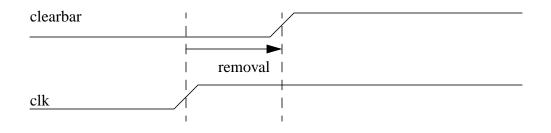

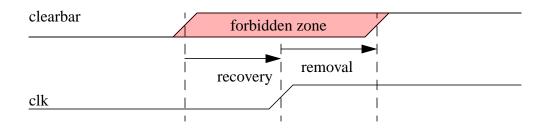

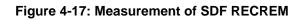

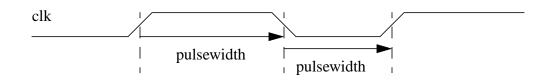

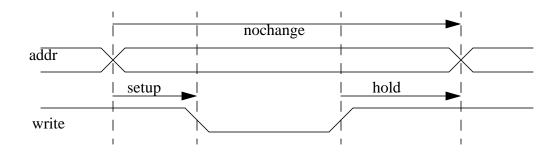

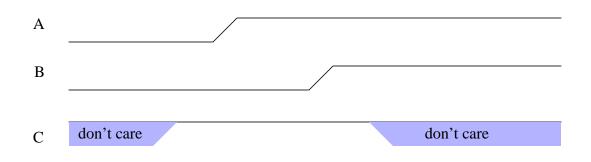

| ∖n     | 012                   | new line              |