| A standard for an Advanced Library Format (ALF) describing Integrated Circuit (IC) | 5  |

|------------------------------------------------------------------------------------|----|

| technology, cells, and blocks                                                      | 10 |

| This is an unapproved draft for an IEEE standard and subject to change             | 20 |

| IEEE P1603 Draft 7                                                                 | 25 |

| October 24, 2002                                                                   | 30 |

|                                                                                    | 35 |

|                                                                                    | 40 |

|                                                                                    | 45 |

|                                                                                    | 30 |

| 1  | Copyright <sup>©</sup> 2001, 2002, 2003 by IEEE. All rights reserved. |

|----|-----------------------------------------------------------------------|

| 5  | put in IEEE verbiage                                                  |

| 10 |                                                                       |

| 15 |                                                                       |

| 20 |                                                                       |

| 25 |                                                                       |

| 30 |                                                                       |

| 35 |                                                                       |

| 40 |                                                                       |

| 45 |                                                                       |

| 50 |                                                                       |

| 55 |                                                                       |

The following individuals contributed to the creation, editing, and review of this document

Official Reporter and WG Chair Wolfgang Roethig, Ph.D. wroethig@eda.org Technical Editor Joe Daniels

chippewea@aol.com

10

5

1

15

20

25

30

35

40

45

50

## 1 Revision history:

| 5  | IEEE P1596 Draft 0 | August 19, 2001    |

|----|--------------------|--------------------|

|    | IEEE P1603 Draft 1 | September 17, 2001 |

| 10 | IEEE P1603 Draft 2 | November 12, 2001  |

| 10 | IEEE P1596 Draft 3 | April 17, 2002     |

|    | IEEE P1603 Draft 4 | May 15, 2002       |

|    | IEEE P1603 Draft 5 | June 21, 2002      |

| 15 |                    |                    |

| 25 |  |  |  |

|----|--|--|--|

|    |  |  |  |

|    |  |  |  |

| 40 |  |  |  |

|----|--|--|--|

|    |  |  |  |

| 50 |  |  |  |

|----|--|--|--|

|    |  |  |  |

## **Table of Contents**

| 1. | Introduction                                             | 1  |

|----|----------------------------------------------------------|----|

|    | 11.36 2. 2                                               | 1  |

|    | 1.1 Motivation                                           |    |

|    | 1.2 Goals                                                |    |

|    | 1.3 Target applications                                  |    |

|    | 1.4 Conventions                                          |    |

|    | 1.5 Contents of this standard                            | 5  |

| 2  | References                                               | ,  |

| 2. | Kelerences                                               |    |

| 3. | Definitions                                              |    |

| 4. | Acronyms and abbreviations                               | 11 |

| 5. | ALF language construction principles and overview        | 13 |

|    | 51 AIF 1                                                 | 10 |

|    | 5.1 ALF meta-language                                    |    |

|    | 5.2 Categories of ALF statements                         |    |

|    | 5.3 Generic objects and library-specific objects         |    |

|    | 5.4 Singular statements and plural statements            |    |

|    | 5.5 Instantiation statement and assignment statement     |    |

|    | 5.6 Annotation, arithmetic model, and related statements |    |

|    | 5.7 Statements for parser control                        |    |

|    | 5.8 Name space and visibility of statements              | 23 |

| 6. | Lexical rules                                            | 25 |

| 0. | Lealed Tules                                             | 20 |

|    | 6.1 Character set                                        | 25 |

|    | 6.2 Comment                                              | 27 |

|    | 6.3 Delimiter                                            | 27 |

|    | 6.4 Operator                                             | 28 |

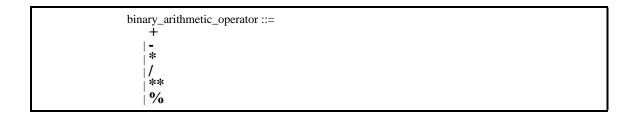

|    | 6.4.1 Arithmetic operator                                |    |

|    | 6.4.2 Boolean operator                                   |    |

|    | 6.4.3 Relational operator                                | 29 |

|    | 6.4.4 Shift operator                                     | 30 |

|    | 6.4.5 Event sequence operator                            | 30 |

|    | 6.4.6 Meta operator                                      |    |

|    | 6.5 Number                                               |    |

|    | 6.6 Multiplier prefix symbol                             |    |

|    | 6.7 Bit literal                                          |    |

|    | 6.8 Based literal                                        |    |

|    | 6.9 Edge literal                                         |    |

|    | 6.10 Quoted string                                       |    |

|    | 6.11 Identifier                                          |    |

|    | 6.11.1 Non-escaped identifier                            |    |

|    | 1                                                        |    |

|    | 6.11.2 Escaped identifier                                |    |

|    |                                                          |    |

|    | 6.11.4 Hierarchical identifier                           | 30 |

| 1   |    | 6.12 Keyword                                                              | 36 |

|-----|----|---------------------------------------------------------------------------|----|

|     |    | 6.13 Vector expression macro                                              | 37 |

|     |    | 6.14 Rules for whitespace usage                                           |    |

|     |    | 6.15 Rules against parser ambiguity                                       |    |

| 5   |    |                                                                           |    |

|     | 7. | Auxiliary syntax rules                                                    | 39 |

|     |    | 7.1 All-purpose value                                                     |    |

| 10  |    | 7.2 Multiplier prefix value                                               | 39 |

|     |    | 7.3 String value                                                          | 39 |

|     |    | 7.4 Arithmetic value                                                      | 39 |

|     |    | 7.5 Boolean value                                                         | 40 |

|     |    | 7.6 Edge value                                                            | 40 |

| 15  |    | 7.7 Index value                                                           | 40 |

|     |    | 7.8 Index                                                                 |    |

|     |    | 7.9 Pin variable and pin value                                            | 41 |

|     |    | 7.10 Pin assignment                                                       | 41 |

|     |    | 7.11 Annotation                                                           |    |

| 20  |    | 7.12 Annotation container                                                 | 42 |

|     |    | 7.13 ATTRIBUTE statement                                                  |    |

|     |    | 7.14 PROPERTY statement                                                   |    |

|     |    | 7.15 INCLUDE statement                                                    |    |

|     |    | 7.16 ASSOCIATE statement and FORMAT annotation                            |    |

| 25  |    | 7.17 REVISION statement                                                   |    |

|     |    | 7.18 Generic object                                                       |    |

|     |    | 7.19 Library-specific object                                              |    |

|     |    | 7.20 All purpose item                                                     | 46 |

| 30  | 8. | Generic objects and related statements                                    | 47 |

|     |    |                                                                           |    |

|     |    | 8.1 ALIAS declaration                                                     |    |

|     |    | 8.2 CONSTANT declaration                                                  |    |

|     |    | 8.3 KEYWORD declaration                                                   |    |

| 35  |    | 8.4 SEMANTICS declaration                                                 |    |

|     |    | 8.5 Annotations and rules related to a KEYWORD or a SEMANTICS declaration |    |

|     |    | 8.5.1 VALUETYPE annotation                                                |    |

|     |    | 8.5.2 VALUES annotation                                                   |    |

| 4.0 |    | 8.5.3 DEFAULT annotation                                                  |    |

| 40  |    | 8.5.4 CONTEXT annotation                                                  |    |

|     |    | 8.5.5 REFERENCETYPE annotation                                            |    |

|     |    | 8.5.6 SI_MODEL annotation                                                 |    |

|     |    | 8.5.7 Rules for legal usage of KEYWORD and SEMANTICS declaration          |    |

| 4.5 |    | 8.6 CLASS declaration                                                     |    |

| 45  |    | 8.7 Annotations related to a CLASS declaration                            |    |

|     |    | 8.7.1 General CLASS reference annotation                                  |    |

|     |    | 8.7.2 USAGE annotation                                                    |    |

|     |    | 8.8 GROUP declaration                                                     |    |

| 50  |    | 8.9 TEMPLATE declaration                                                  |    |

| 50  |    | 8.10 TEMPLATE instantiation                                               | 58 |

|     | 9. | Library-specific objects and related statements                           | 63 |

|     |    | 0.1 LIDDADY LCUDI IDDADY 1-1-2                                            |    |

| 55  |    | 9.1 LIBRARY and SUBLIBRARY declaration                                    |    |

| 55  |    | 7.4 AIIIIOIAIIOIIS TETAIEU IO A LIDNAN I OI A SUDLIDNAN I UECTAFAIIOII    | 03 |

|      | 9.2.1    | LIBRARY reference annotation.                    | 63  | 1  |

|------|----------|--------------------------------------------------|-----|----|

|      | 9.2.2    | INFORMATION annotation container                 | 64  |    |

| 9.3  | CELL (   | declaration                                      | .65 |    |

| 9.4  | Annota   | tions related to a CELL declaration              | .66 |    |

|      | 9.4.1    | CELL reference annotation                        | 66  | 5  |

|      | 9.4.2    | CELLTYPE annotation                              | 66  |    |

|      | 9.4.3    | SWAP_CLASS annotation                            | 67  |    |

|      | 9.4.4    | RESTRICT_CLASS annotation                        | 67  |    |

|      | 9.4.5    | SCAN_TYPE annotation                             | 69  | 10 |

|      | 9.4.6    | SCAN_USAGE annotation                            | 69  |    |

|      | 9.4.7    | BUFFERTYPE annotation                            | 70  |    |

|      | 9.4.8    | DRIVERTYPE annotation                            | 70  |    |

|      | 9.4.9    | PARALLEL_DRIVE annotation                        | 71  |    |

|      | 9.4.10   | PLACEMENT_TYPE annotation                        | 71  | 15 |

|      | 9.4.11   | SITE reference annotation for a CELL             | 72  |    |

|      |          | ATTRIBUTE values for a CELL                      |     |    |

| 9.5  | PIN de   | claration                                        | .74 |    |

|      |          | OUP declaration                                  |     |    |

|      |          | tions related to a PIN or a PINGROUP declaration |     | 20 |

|      | 9.7.1    | PIN reference annotation                         |     |    |

|      | 9.7.2    | MEMBERS annotation                               |     |    |

|      | 9.7.3    | VIEW annotation                                  |     |    |

|      | 9.7.4    | PINTYPE annotation.                              |     |    |

|      | 9.7.5    | DIRECTION annotation.                            |     | 25 |

|      | 9.7.6    | SIGNALTYPE annotation                            |     |    |

|      | 9.7.7    | ACTION annotation                                |     |    |

|      | 9.7.8    | POLARITY annotation                              |     |    |

|      | 9.7.9    | CONTROL_POLARITY annotation container            |     |    |

|      | 9.7.10   | DATATYPE annotation                              |     | 30 |

|      |          | INITIAL_VALUE annotation                         |     |    |

|      | 9.7.12   | SCAN_POSITION annotation                         | 85  |    |

|      | 9.7.13   | STUCK annotation                                 | 85  |    |

|      | 9.7.14   | SUPPLYTYPE annotation                            |     |    |

|      |          | SIGNAL_CLASS annotation                          |     | 35 |

|      |          | SUPPLY_CLASS annotation                          |     |    |

|      |          | DRIVETYPE annotation                             |     |    |

|      |          | SCOPE annotation                                 |     |    |

|      | 9.7.19   | CONNECT_CLASS annotation                         | 90  |    |

|      | 9.7.20   | SIDE annotation                                  | 90  | 40 |

|      | 9.7.21   | ROW and COLUMN annotation                        | 91  |    |

|      | 9.7.22   | ROUTING_TYPE annotation                          | 92  |    |

|      | 9.7.23   | PULL annotation                                  | 92  |    |

|      | 9.7.24   | ATTRIBUTE values for a PIN or a PINGROUP         | 93  |    |

| 8.6  | PRIMI'   | TIVE declaration                                 | .95 | 45 |

| 9.9  | WIRE     | declaration                                      | .95 |    |

| 9.10 | ) Annota | tions related to a WIRE declaration              | .96 |    |

|      | 9.10.1   | WIRE reference annotation                        | 96  |    |

|      |          | WIRETYPE annotation                              |     |    |

|      | 9.10.3   | SELECT_CLASS annotation                          | 97  | 50 |

| 9.11 | NODE     | declaration                                      | .98 |    |

| 9.12 | 2 Annota | tions related to a NODE declaration              | .98 |    |

|      | 9.12.1   | NODE reference annotation                        | 98  |    |

|      | 9.12.2   | NODETYPE annotation                              | 99  |    |

|      | 9.12.3   | NODE_CLASS annotation                            | 100 | 55 |

| 1         |     | 9.13 VECTOR declaration                               | 101 |

|-----------|-----|-------------------------------------------------------|-----|

|           |     | 9.14 Annotations related to a VECTOR declaration.     | 101 |

|           |     | 9.14.1 VECTOR reference annotation                    | 101 |

|           |     | 9.14.2 PURPOSE annotation                             | 101 |

| 5         |     | 9.14.3 OPERATION annotation                           | 102 |

|           |     | 9.14.4 LABEL annotation                               | 103 |

|           |     | 9.14.5 EXISTENCE_CONDITION annotation                 | 103 |

|           |     | 9.14.6 EXISTENCE_CLASS annotation                     | 104 |

| 10        |     | 9.14.7 CHARACTERIZATION_CONDITION annotation          | 104 |

|           |     | 9.14.8 CHARACTERIZATION_VECTOR annotation             | 105 |

|           |     | 9.14.9 CHARACTERIZATION_CLASS annotation              | 105 |

|           |     | 9.14.10 MONITOR annotation                            | 105 |

|           |     | 9.15 LAYER declaration                                |     |

| 15        |     | 9.16 Annotations related to a LAYER declaration       |     |

|           |     | 9.16.1 LAYER reference annotation                     | 106 |

|           |     | 9.16.2 LAYERTYPE annotation                           | 106 |

|           |     | 9.16.3 PITCH annotation                               | 107 |

|           |     | 9.16.4 PREFERENCE annotation                          | 107 |

| 20        |     | 9.17 VIA declaration                                  |     |

|           |     | 9.18 Annotations related to a VIA declaration         | 108 |

|           |     | 9.18.1 VIA reference annotation                       | 108 |

|           |     | 9.18.2 VIATYPE annotation                             | 109 |

|           |     | 9.19 RULE declaration                                 | 109 |

| 25        |     | 9.20 ANTENNA declaration                              |     |

|           |     | 9.21 BLOCKAGE declaration                             | 110 |

|           |     | 9.22 PORT declaration                                 |     |

|           |     | 9.23 Annotations related to a PORT declaration        |     |

|           |     | 9.23.1 CONNECT_TYPE annotation                        |     |

| 30        |     | 9.24 SITE declaration                                 |     |

|           |     | 9.25 Annotations related to a SITE declaration        |     |

|           |     | 9.25.1 SITE reference annotation                      |     |

|           |     | 9.25.2 ORIENTATION_CLASS annotation                   |     |

|           |     | 9.25.3 SYMMETRY_CLASS annotation                      |     |

| 35        |     | 9.26 ARRAY declaration                                |     |

|           |     | 9.27 Annotations related to an ARRAY declaration      |     |

|           |     | 9.27.1 ARRAYTYPE annotation                           |     |

|           |     | 9.27.2 LAYER reference annotation for ARRAY           |     |

|           |     | 9.27.3 SITE reference annotation for ARRAY            |     |

| 40        |     | 9.28 PATTERN declaration                              |     |

|           |     | 9.29 Annotations related to a PATTERN declaration     |     |

|           |     | 9.29.1 PATTERN reference annotation                   |     |

|           |     | 9.29.2 SHAPE annotation                               |     |

| 4.5       |     | 9.29.3 VERTEX annotation                              |     |

| 45        |     | 9.29.4 ROUTE annotation                               | -   |

|           |     | 9.29.5 LAYER reference annotation for PATTERN         |     |

|           |     | 9.30 REGION declaration                               |     |

|           |     | 9.31 Annotations related to a REGION declaration      |     |

| <b>50</b> |     | 9.31.1 REGION reference annotation                    |     |

| 50        |     | 9.31.2 BOOLEAN annotation                             | 120 |

|           | 10. | Description of functional and physical implementation | 121 |

|           |     | 10.1 FUNCTION statement                               | 121 |

| 55        |     | 10.2 TEST statement                                   | 121 |

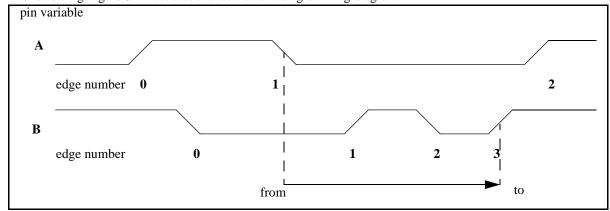

| 10.3 Declaration of a pin variable                                         | 122  |

|----------------------------------------------------------------------------|------|

| 10.4 BEHAVIOR statement                                                    | 123  |

| 10.5 STRUCTURE statement and CELL instantiation                            | 124  |

| 10.6 STATETABLE statement                                                  |      |

| 10.7 NON_SCAN_CELL statement                                               |      |

| 10.8 RANGE statement                                                       |      |

| 10.9 Boolean expression                                                    |      |

| 10.10Boolean value system                                                  |      |

| 10.10.1 Scalar boolean value                                               |      |

| 10.10.2 Vectorized boolean value                                           |      |

| 10.10.3 Non-assignable boolean value                                       |      |

| 10.11Boolean operations and operators                                      |      |

| 10.11.1 Logical operation                                                  |      |

| 10.11.2 Bitwise operation                                                  |      |

| 10.11.3 Conditional operation                                              |      |

| 10.11.4 Integer arithmetic operation                                       |      |

| 10.11.5 Shift operation                                                    |      |

| 10.11.6 Comparison operation                                               |      |

| 10.11.7 Operator priorities                                                |      |

| 10.12Vector expression                                                     |      |

| 10.13Operators for event specification                                     |      |

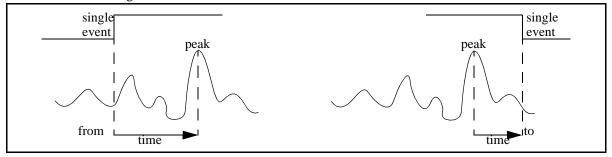

| 10.13.1 Specification of a single event.                                   |      |

| 10.13.2 Temporal order within an event sequence                            |      |

| 10.13.3 Canonical specification of a sequence of events                    |      |

| 10.13.4 Specification of a completely permutable event                     |      |

| 10.13.5 Specification of a conditional event                               |      |

| 10.13.6 Operator priorities                                                |      |

| 10.14Predefined PRIMITIVE                                                  |      |

| 10.14.1 Predefined PRIMITIVE ALF_BUF                                       |      |

| 10.14.1 Predefined PRIMITIVE ALT_BOT                                       |      |

| 10.14.2 Predefined PRIMITIVE ALF_NOT                                       |      |

| 10.14.4 Predefined PRIMITIVE ALF_NAND                                      | 146  |

| 10.14.5 Predefined PRIMITIVE ALF_OR                                        |      |

| 10.14.6 Predefined PRIMITIVE ALF_OR                                        |      |

| 10.14.0 Predefined PRIMITIVE ALF_NOK  10.14.7 Predefined PRIMITIVE ALF_XOR |      |

| 10.14.7 Predefined PRIMITIVE ALF_XOR                                       |      |

|                                                                            |      |

| 10.14.9 Predefined PRIMITIVE ALF_BUFIF1                                    |      |

|                                                                            |      |

| 10.14.11Predefined PRIMITIVE ALF_NOTIF1                                    |      |

|                                                                            |      |

| 10.14.13Predefined PRIMITIVE ALF_MUX                                       |      |

| 10.14.14Predefined PRIMITIVE ALF_LATCH                                     |      |

| 10.14.15Predefined PRIMITIVE ALF_FLIPFLOP                                  |      |

| 10.15WIRE instantiation                                                    |      |

| 10.16Geometric model                                                       |      |

| 10.17Predefined geometric models using TEMPLATE                            |      |

| 10.17.1 Predefined TEMPLATE RECTANGLE                                      |      |

| 10.17.2 Predefined TEMPLATE LINE                                           |      |

| 10.18Geometric transformation                                              |      |

| 10.19ARTWORK statement                                                     |      |

| 10.20VIA instantiation                                                     | 157  |

| Description of electrical and physical measurements                        | 159  |

| Describtion of electrical and physical measurements                        | 1.19 |

11.

55

| 1          | 11.1 Arithmetic expression                                       | 159 |

|------------|------------------------------------------------------------------|-----|

|            | 11.2 Arithmetic operations and operators                         | 159 |

|            | 11.2.1 Unary arithmetic operator                                 |     |

|            | 11.2.2 Binary arithmetic operator                                |     |

| 5          | 11.2.3 Macro arithmetic operator                                 |     |

|            | 11.2.4 Operator priorities                                       |     |

|            | 11.3 Arithmetic model                                            |     |

|            | 11.4 HEADER, TABLE, and EQUATION statements                      |     |

| 10         | 11.5 MIN, MAX, and TYP statements                                |     |

|            | 11.6 Auxiliary arithmetic model                                  |     |

|            | 11.7 Arithmetic submodel                                         |     |

|            | 11.8 Arithmetic model container                                  |     |

|            | 11.8.1 General arithmetic model container                        |     |

| 15         | 11.8.2 Arithmetic model container LIMIT                          |     |

| 13         | 11.8.3 Arithmetic model container EARLY and LATE                 |     |

|            |                                                                  |     |

|            | 11.9 Generally applicable annotations for arithmetic models      |     |

|            | 11.9.1 UNIT annotation                                           |     |

| 20         | 11.9.2 CALCULATION annotation                                    |     |

| 20         | 11.9.3 INTERPOLATION annotation                                  |     |

|            | 11.9.4 DEFAULT annotation                                        |     |

|            | 11.9.5 MODEL reference annotation                                |     |

|            | 11.10VIOLATION statement, MESSAGE TYPE and MESSAGE annotation    |     |

|            | 11.11Arithmetic models for timing, power and signal integrity    |     |

| 25         | 11.11.1 TIME                                                     |     |

|            | 11.11.2 FREQUENCY                                                |     |

|            | 11.11.3 DELAY                                                    | 178 |

|            | 11.11.4 RETAIN                                                   | 178 |

|            | 11.11.5 SLEWRATE                                                 | 179 |

| 30         | 11.11.6 SETUP and HOLD                                           | 181 |

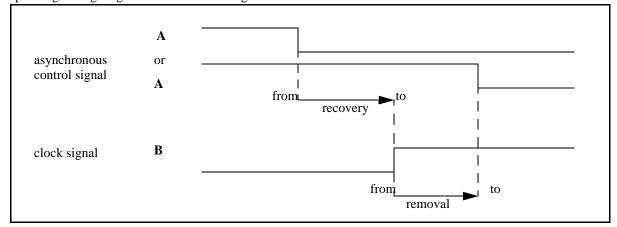

|            | 11.11.7 RECOVERY and REMOVAL                                     | 181 |

|            | 11.11.8 NOCHANGE and ILLEGAL                                     | 182 |

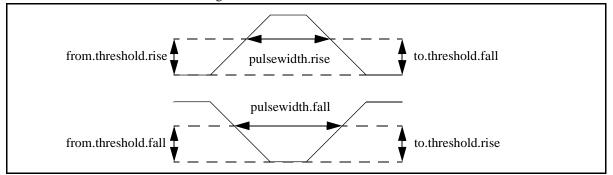

|            | 11.11.9 PULSEWIDTH                                               | 183 |

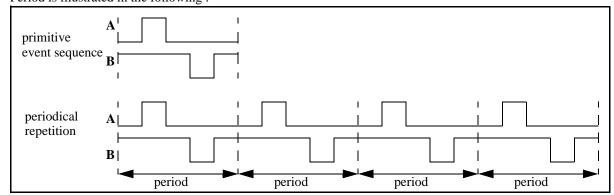

|            | 11.11.10PERIOD                                                   | 185 |

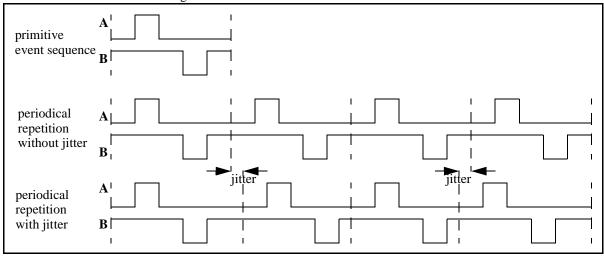

| 35         | 11.11.11JITTER                                                   | 186 |

|            | 11.11.12SKEW                                                     | 186 |

|            | 11.11.13THRESHOLD                                                |     |

|            | 11.11.14NOISE and NOISE_MARGIN                                   |     |

|            | 11.11.15POWER and ENERGY                                         |     |

| 40         | 11.12FROM and TO statements                                      |     |

|            | 11.13Annotations related to timing, power and signal integrity   |     |

|            | 11.13.1 EDGE_NUMBER annotation                                   |     |

|            | 11.13.2 PIN reference and EDGE NUMBER annotation for FROM and TO |     |

|            | 11.13.3 PIN reference and EDGE_NUMBER annotation for SLEWRATE    |     |

| 45         | 11.13.4 PIN reference and EDGE_NUMBER annotation for PULSEWIDTH  |     |

| 10         | 11.13.5 PIN reference and EDGE_NUMBER annotation for SKEW        |     |

|            | 11.13.6 PIN reference annotation for NOISE and NOISE_MARGIN      |     |

|            | 11.13.7 MEASUREMENT annotation                                   |     |

|            | 11.14Arithmetic models for environmental conditions              |     |

| 50         |                                                                  |     |

| 30         | 11.14.1 PROCESS                                                  |     |

|            | 11.14.2 DERATE_CASE                                              |     |

|            | 11.14.3 TEMPERATURE                                              |     |

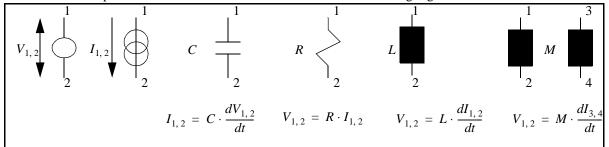

|            | 11.15Arithmetic models for electrical circuits                   |     |

| <i>E E</i> | 11.15.1 VOLTAGE                                                  |     |

| 55         | 11.15.2 CURRENT                                                  | 201 |

| 11.1            | 5.3 CAPACITANCE                                                  | 202 | 1  |

|-----------------|------------------------------------------------------------------|-----|----|

| 11.1            | 5.4 RESISTANCE                                                   | 203 |    |

| 11.1            | 5.5 INDUCTANCE                                                   | 205 |    |

| 11.16An         | notations for electrical circuits                                | 206 |    |

| 11.1            | 6.1 NODE reference annotation for electrical circuits            | 206 | 5  |

| 11.1            | 6.2 COMPONENT reference annotation                               | 207 |    |

| 11.1            | 6.3 PIN reference annotation for electrical circuits             | 207 |    |

| 11.1            | 6.4 FLOW annotation                                              | 209 |    |

| 11.17Mi         | scellaneous arithmetic models                                    | 210 | 10 |

| 11.1            | 7.1 DRIVE STRENGTH                                               | 210 |    |

|                 | 7.2 SWITCHING_BITS with PIN reference annotation                 |     |    |

|                 | thmetic models related to structural implementation              |     |    |

|                 | 8.1 CONNECTIVITY                                                 |     |    |

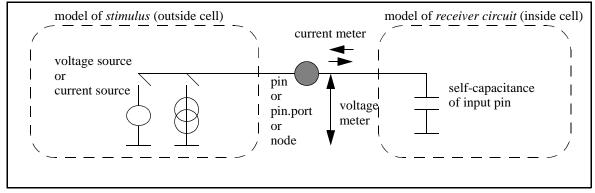

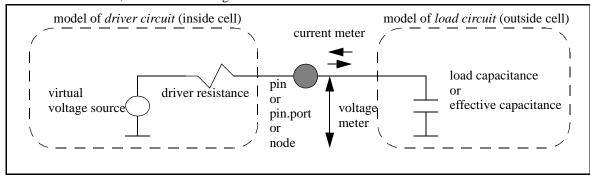

|                 | 8.2 DRIVER and RECEIVER                                          |     | 15 |

|                 | 8.3 FANOUT, FANIN and CONNECTIONS                                |     | 10 |

|                 | thmetic models related to layout implementation                  |     |    |

|                 | 9.1 SIZE.                                                        |     |    |

|                 | 9.2 AREA                                                         |     |    |

|                 | 9.3 PERIMETER                                                    |     | 20 |

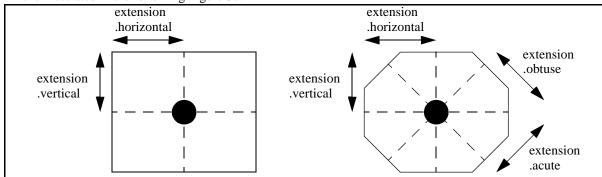

|                 | 9.4 EXTENSION                                                    |     | 20 |

|                 | 9.5 THICKNESS                                                    |     |    |

|                 | 9.6 HEIGHT                                                       |     |    |

|                 | 9.0 HEIGHT                                                       |     |    |

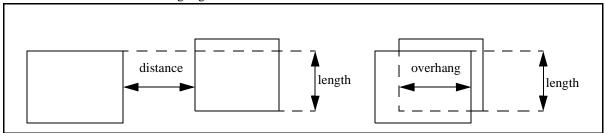

|                 | 9.8 LENGTH                                                       |     | 25 |

|                 |                                                                  |     | 25 |

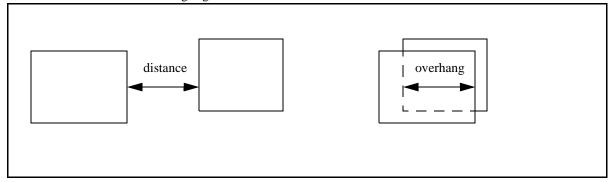

|                 | 9.9 DISTANCE                                                     |     |    |

|                 | 9.10OVERHANG                                                     |     |    |

|                 | 9.11DENSITY                                                      |     |    |

|                 | notations related to arithmetic models for layout implementation |     | •  |

|                 | 0.1 CONNECT_RULE annotation                                      |     | 30 |

|                 | 0.2 BETWEEN annotation                                           |     |    |

|                 | 0.3 BETWEEN annotation for CONNECTIVITY                          |     |    |

|                 | 0.4 BETWEEN annotation for DISTANCE, LENGTH, OVERHANG            |     |    |

|                 | 0.5 MEASURE annotation                                           |     |    |

|                 | 0.6 REFERENCE annotation container                               |     | 35 |

|                 | 0.7 ANTENNA reference annotation                                 |     |    |

|                 | 0.8 TARGET annotation                                            |     |    |

|                 | 0.9 PATTERN reference annotation                                 |     |    |

| 11.21Ar         | thmetic submodels for timing and electrical data                 | 229 |    |

| 11.22Ar         | thmetic submodels for physical data                              | 230 | 40 |

|                 |                                                                  |     |    |

| (informative)Sy | ntax rule summary                                                | 233 |    |

|                 |                                                                  |     |    |

| A.1             | ALF meta-language                                                | 233 |    |

|                 |                                                                  |     | 45 |

| A.2             | Lexical definitions                                              | 233 |    |

|                 |                                                                  |     |    |

| A.3             | Auxiliary definitions                                            | 237 |    |

| A.4             | Generic definitions                                              | 238 | 50 |

|                 |                                                                  |     |    |

| A.5             | Library definitions                                              | 240 |    |

| A.6             | Function definitions                                             | 243 |    |

|                 |                                                                  |     | 55 |

| 1  | A.7             | Arithmetic definitions            | 246 |

|----|-----------------|-----------------------------------|-----|

|    | (informative)Se | mantics rule summary              | 251 |

| 5  | B.1             | Auxiliary and generic definitions | 251 |

|    | B.2             | Library definitions               | 252 |

| 10 | B.3             | Arithmetic definitions            | 258 |

|    | (informative)Bi | bliography                        | 261 |

| 15 |                 |                                   |     |

|    |                 |                                   |     |

|    |                 |                                   |     |

| 20 |                 |                                   |     |

|    |                 |                                   |     |

| 25 |                 |                                   |     |

|    |                 |                                   |     |

| 20 |                 |                                   |     |

| 30 |                 |                                   |     |

|    |                 |                                   |     |

| 35 |                 |                                   |     |

|    |                 |                                   |     |

| 40 |                 |                                   |     |

|    |                 |                                   |     |

|    |                 |                                   |     |

| 45 |                 |                                   |     |

|    |                 |                                   |     |

| 50 |                 |                                   |     |

|    |                 |                                   |     |

|    |                 |                                   |     |

# List of Figures

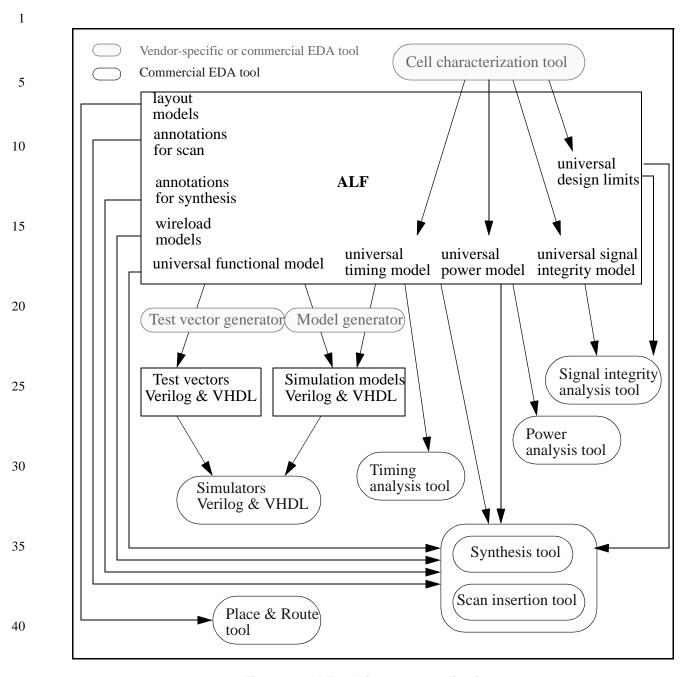

ALF and its target applications 4

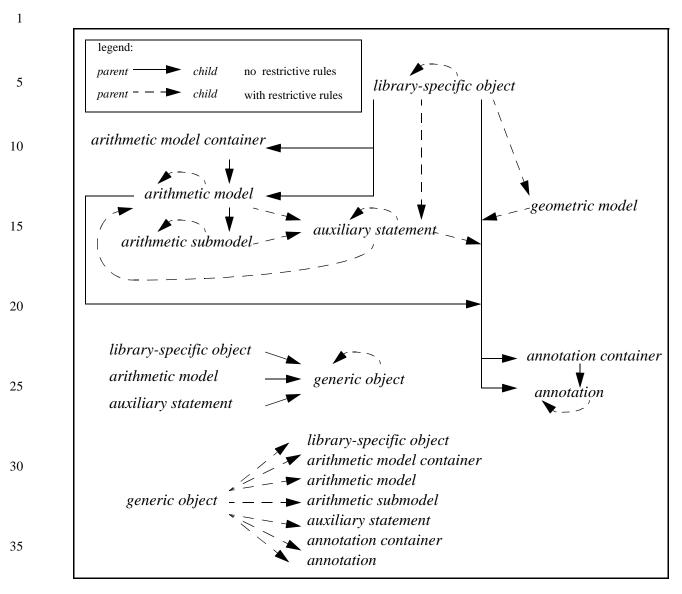

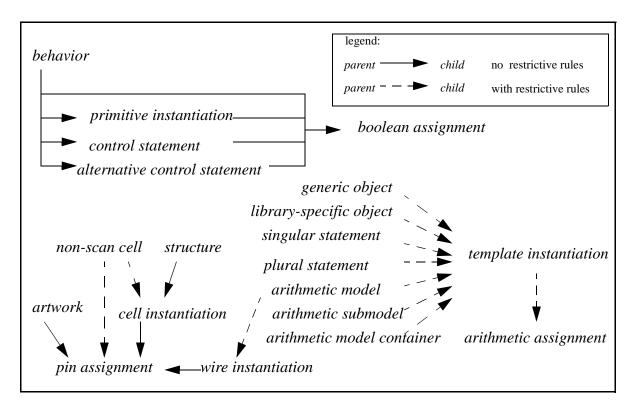

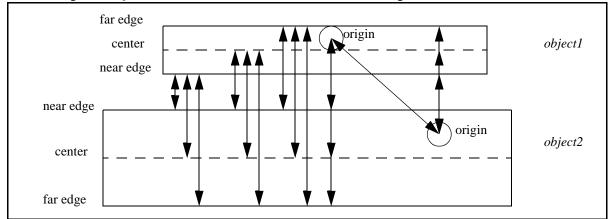

Parent/child relationship between ALF statements 16

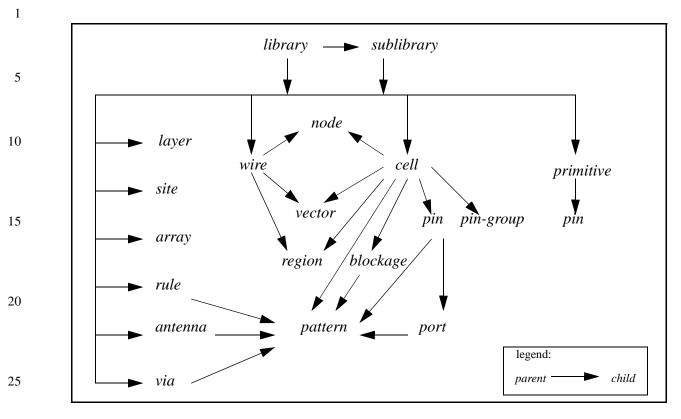

Parent/child relationship amongst library-specific objects 18

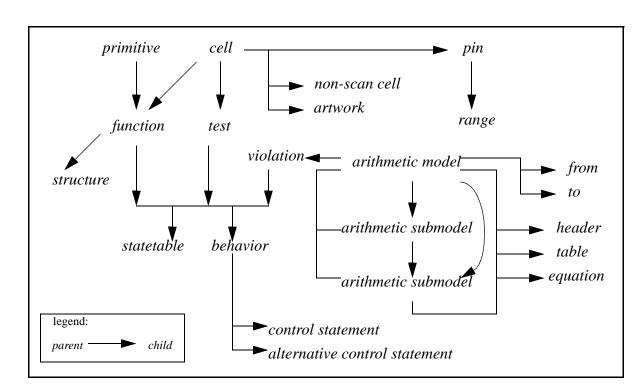

Parent/child relationship involving singular statements and plural statements 20

Parent/child relationship involving instantiation and assignment statements 21

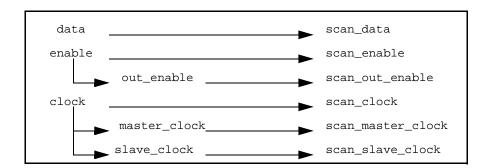

Scheme for construction of composite signaltype values 80

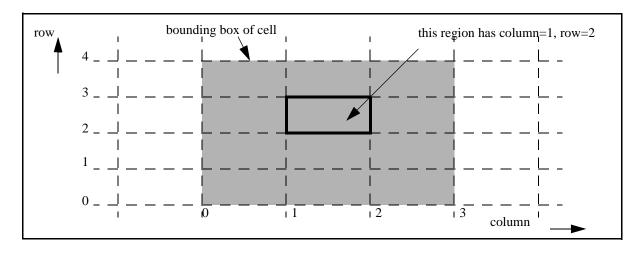

ROW and COLUMN relative to a bounding box of a CELL 91

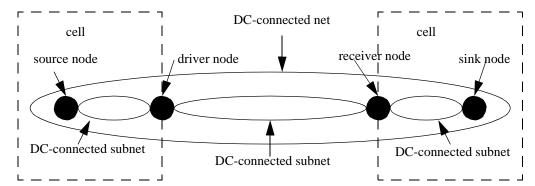

NODETYPE in context of a DC-connected net 100

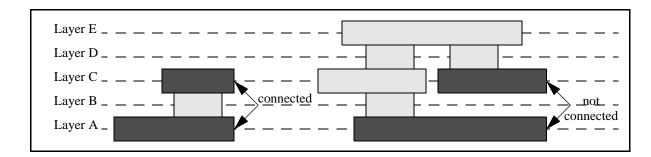

Connection between layers during manufacturing 110

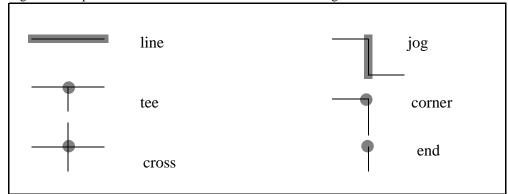

SHAPE annotation illustration 117

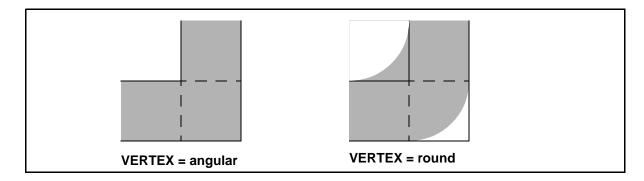

VERTEX annotation illustration 118

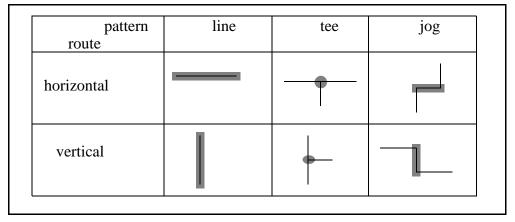

**ROUTE** annotation illustration 119

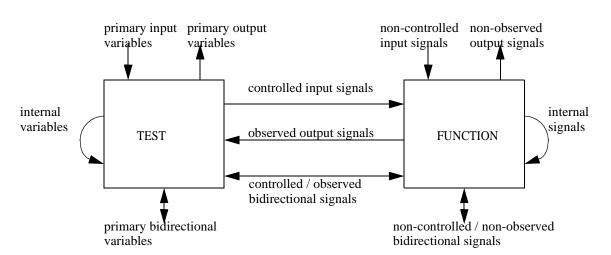

Relationship between FUNCTION and TEST 123

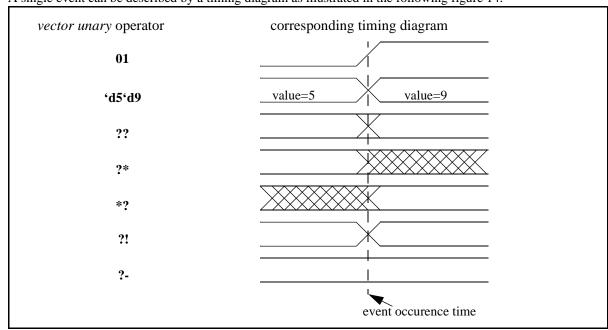

Timing diagrams for single events 138

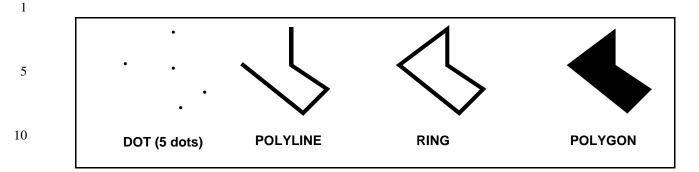

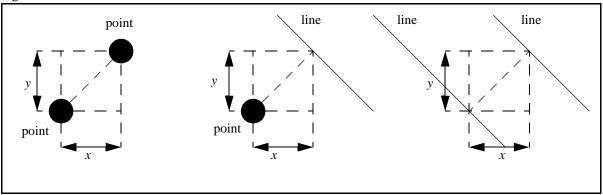

Illustration of geometric models 152

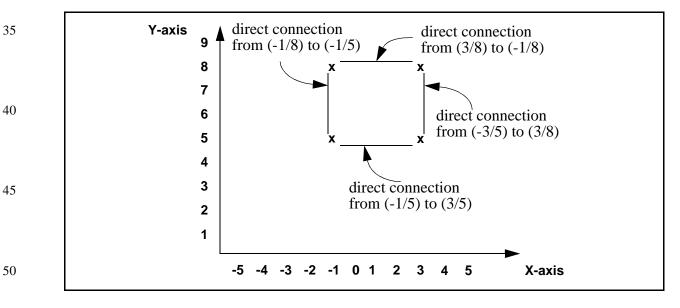

Illustration of direct point-to-point connection 152

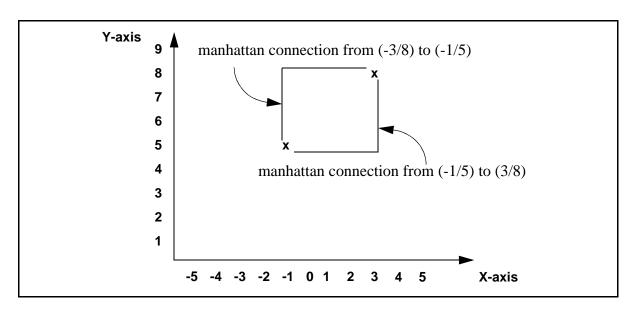

Illustration of manhattan point-to-point connection 153

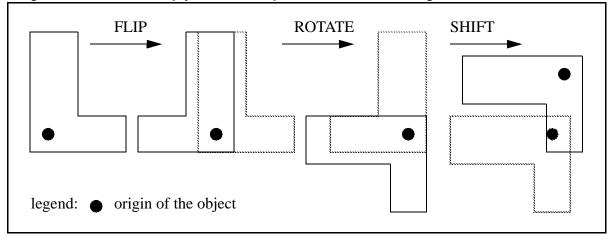

Illustration of FLIP, ROTATE, and SHIFT 155

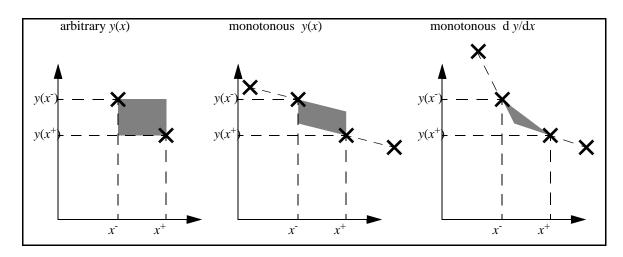

Bounding regions for y(x) with INTERPOLATION=fit 172

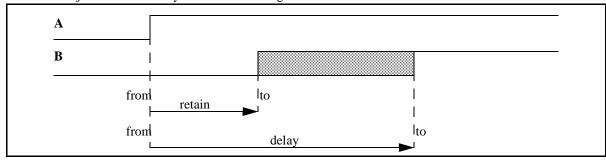

Illustration of RETAIN and DELAY 179

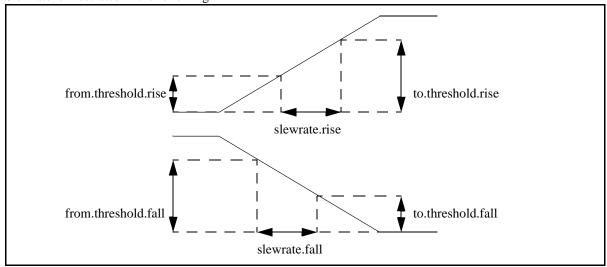

Illustration of SLEWRATE 180

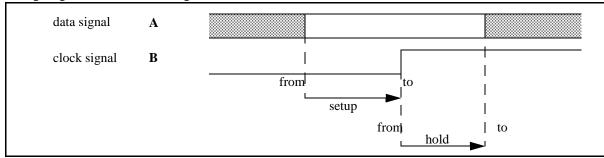

Illustration of SETUP and HOLD 181

**RECOVERY and REMOVAL 182**

Illustration of NOCHANGE and ILLEGAL 183

Illustration of PULSEWIDTH 185

Illustration of PERIOD 185

Illustration of JITTER 186

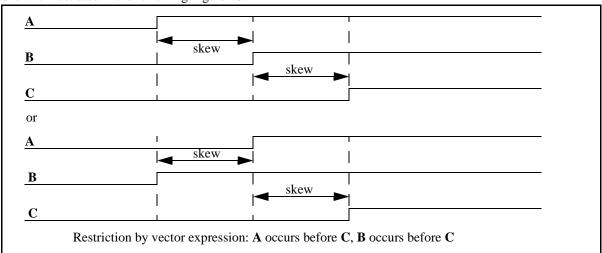

Illustration of SKEW 187

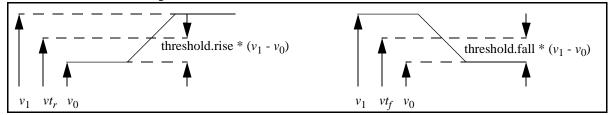

THRESHOLD measurement definition 188

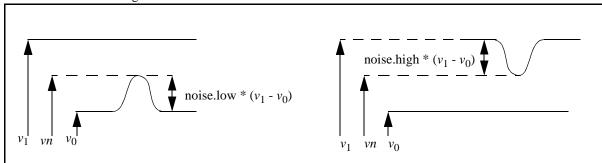

NOISE measurement definition 189

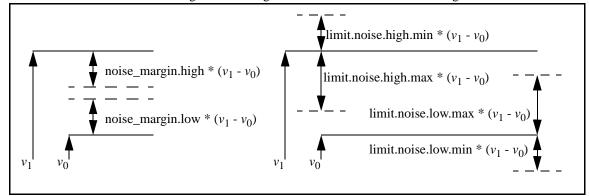

Definition of NOISE MARGIN and LIMIT for NOISE 190

Illustration of PIN reference and EDGE NUMBER annotation within FROM and TO 194

Illustration of peak measurement with FROM or TO statement 197

Electrical components and their terminals 207

Association between electrical components and an input pin 208

Association between electrical components and an output pin 209

Illustration of EXTENSION 217

Illustration of DISTANCE versus OVERHANG 222

IIllustration of DISTANCE versus OVERHANG versus LENGTH 225

Illustration of MEASURE 226

Illustration of REFERENCE for DISTANCE 227

## **List of Tables**

| Table 1—  | Target applications and models supported by ALF2      |

|-----------|-------------------------------------------------------|

| Table 2—  |                                                       |

| Table 3—  |                                                       |

| Table 4—  | Library-specific objects17                            |

| Table 5—  | Singular statements 18                                |

|           | Plural statements19                                   |

|           |                                                       |

| Table 8—  |                                                       |

| Table 9—  | Other categories of ALF statements22                  |

| Table 10— |                                                       |

| Table 11— |                                                       |

| Table 12— | Statements for ALF parser control23                   |

| Table 13— | List of whitespace characters25                       |

| Table 14— | List of special characters26                          |

| Table 15— | List arithmetic operators 28                          |

| Table 16— | List of boolean operators29                           |

| Table 17— | List of relational operators29                        |

| Table 18— | List of shift operators 30                            |

| Table 19— | List of event sequence operators 30                   |

| Table 20— | List of meta operators30                              |

| Table 21— |                                                       |

| Table 22— |                                                       |

| Table 23— | FORMAT annotation values44                            |

|           | Legal string values within the REVISION statement45   |

| Table 25— | Syntax item identifier48                              |

| Table 26— | VALUETYPE annotation49                                |

| Table 27— | SI_MODEL annotation53                                 |

|           | USAGE annotation56                                    |

|           |                                                       |

|           |                                                       |

|           | Predefined values for RESTRICT_CLASS68                |

|           |                                                       |

|           | SCAN_USAGE annotations for a CELL object69            |

|           | BUFFERTYPE annotations for a CELL object70            |

|           |                                                       |

|           | PLACEMENT_TYPE annotations for a CELL object72        |

|           |                                                       |

|           |                                                       |

|           |                                                       |

|           |                                                       |

|           | VIEW annotations for a PIN object77                   |

|           | PINTYPE annotations for a PIN object78                |

|           |                                                       |

| Table 44  | Fundamental SIGNALTYPE appointing for a DIN abject 70 |

| 1           | Table 45— |                                                             |

|-------------|-----------|-------------------------------------------------------------|

|             |           |                                                             |

|             |           |                                                             |

|             |           | POLARITY annotations for a PIN82                            |

| 5           | Table 49— | POLARITY applicable in conjunction with SIGNALTYPE values82 |

|             |           |                                                             |

|             |           | STUCK annotations for a PIN object85                        |

| 10          | Table 52— | SUPPLYTYPE annotations for a PIN object86                   |

| 10          | Table 53— | DRIVETYPE annotations for a PIN object88                    |

|             | Table 54— | SCOPE annotations for a PIN object89                        |

|             | Table 55— |                                                             |

|             | Table 56— | ROUTING-TYPE annotations for a PIN object92                 |

| 15          | Table 57— | PULL annotations for a PIN object93                         |

|             | Table 58— |                                                             |

|             | Table 59— |                                                             |

|             | Table 60— |                                                             |

| 20          | Table 61— | PIN or PINGROUP attributes for memory BIST94                |

| 20          | Table 62— |                                                             |

|             | Table 63— |                                                             |

|             | Table 64— | PURPOSE annotation values102                                |

|             | Table 65— | OPERATION annotation values 103                             |

| 25          | Table 66— | LAYERTYPE annotation values107                              |

|             | Table 67— | PREFERENCE annotation values 108                            |

|             | Table 68— | VIATYPE annotation values 109                               |

|             | Table 69— |                                                             |

|             | Table 70— | ARRAYTYPE annotation values115                              |

| 30          |           | SHAPE annotation values 117                                 |

|             |           | VERTEX annotation values118                                 |

|             |           |                                                             |

|             |           | Scalar boolean values128                                    |

| 35          |           |                                                             |

|             |           |                                                             |

|             |           | Symbolic boolean values131                                  |

|             |           | Logical Operation132                                        |

|             |           | Bitwise Operation 132                                       |

| 40          |           |                                                             |

|             |           |                                                             |

|             |           | Shift Operation134                                          |

|             |           |                                                             |

| 45          |           | Equal comparison considering drive strength135              |

| <b>-1</b> 3 |           |                                                             |

|             |           | Specification of a single event137                          |

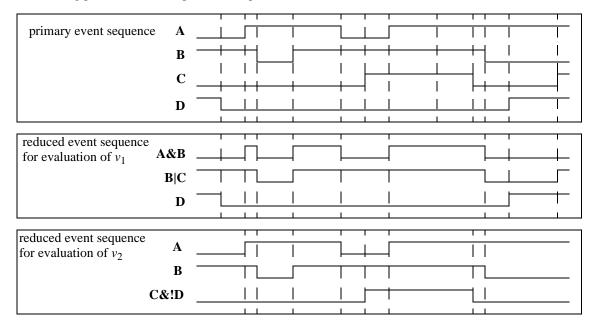

|             |           |                                                             |

|             |           | Specification of a completely permutable event143           |

| 50          |           | Specification a conditional event145                        |

|             |           | Geometric model identifiers151                              |

|             |           | Unary arithmetic operators 159                              |

|             |           | Binary arithmetic operators 160                             |

| <i></i>     |           | Macro arithmetic operators 160                              |

| 55          | Table 94— |                                                             |

| Table 95—  | Interpolation annotation171                                        | 1  |

|------------|--------------------------------------------------------------------|----|

| Table 96—  | MESSAGE_TYPE annotation175                                         |    |

| Table 97—  |                                                                    |    |

| Table 98—  | Predefined arithmetic values for PROCESS197                        |    |

| Table 99—  | Predefined arithmetic values for DERATE CASE198                    | 5  |

|            | FLOW annotation 209                                                |    |

| Table 101— | Boolean values for CONNECTIVITY211                                 |    |

| Table 102— |                                                                    | 10 |

|            |                                                                    | 10 |

| Table 104— |                                                                    |    |

| Table 105— |                                                                    |    |

| Table 106— | Overview of arithmetic submodels for timing and electrical data229 |    |

| Table 107— | Overview of arithmetic submodels for physical data230              | 15 |

|            |                                                                    |    |

|            |                                                                    |    |

|            |                                                                    |    |

# IEEE Standard for an Advanced Library Format (ALF) describing Integrated Circuit (IC) technology, cells, and blocks

1. Introduction 25

\*\*Add a lead-in OR change this to parallel an IEEE intro section\*\*

#### 1.1 Motivation

Designing digital integrated circuits has become an increasingly complex process. More functions get integrated into a single chip, yet the cycle time of electronic products and technologies has become considerably shorter. It would be impossible to successfully design a chip of today's complexity within the time-to-market constraints without extensive use of EDA tools, which have become an integral part of the complex design flow. The efficiency of the tools and the reliability of the results for simulation, synthesis, timing and power analysis, layout and extraction rely significantly on the quality of available information about the cells in the technology library.

New challenges in the design flow, especially signal integrity, arise as the traditional tools and design flows hit their limits of capability in processing complex designs. As a result, new tools emerge, and libraries are needed in order to make them work properly. Library creation (generation) itself has become a very complex process and the choice or rejection of a particular application (tool) is often constrained or dictated by the availability of a library for that application. The library constraint can prevent designers from choosing an application program that is best suited for meeting specific design challenges. Similar considerations can inhibit the development and productization of such an application program altogether. As a result, competitiveness and innovation of the whole electronic industry can stagnate.

In order to remove these constraints, an industry-wide standard for library formats, the Advanced Library Format (ALF), is proposed. It enables the EDA industry to develop innovative products and ASIC designers to choose the best product without library format constraints. Since ASIC vendors have to support a multitude of libraries according to the preferences of their customers, a common standard library is expected to significantly reduce the library development cycle and facilitate the deployment of new technologies sooner.

1

5

10

15

20

30

35

40

45

#### 1.2 Goals

1

5

10

15

20

25

30

35

40

45

The basic goals of the proposed library standard are

- simplicity library creation process needs to be easy to understand and not become a cumbersome process only known by a few experts.

- *generality* tools of any level of sophistication need to be able to retrieve necessary information from the library.

- expandability this needs to be done for early adoption and future enhancement possibilities.

- flexibility the choice of keeping information in one library or in separate libraries needs to be in the hand

of the user not the standard.

- efficiency the complexity of the design information requires the process of retrieving information from the library does not become a bottleneck. The right trade-off between compactness and verbosity needs to be established.

- ease of implementation backward compatibility with existing libraries shall be provided and translation to the new library needs to be an easy task.

- conciseness unambiguous description and accuracy of contents shall be detailed.

- acceptance there needs to be a preference for the new standard library over existing libraries.

#### 1.3 Target applications

The fundamental purpose of ALF is to serve as the primary database for all third-party applications of ASIC cells. In other words, it is an elaborate and formalized version of the *databook*.

In the early days, databooks provided all the information a designer needed for choosing a cell in a particular application: Logic symbols, schematics, and a truth table provided the functional specification for simple cells. For more complex blocks, the name of the cell (e.g., asynchronous ROM, synchronous 2-port RAM, or 4-bit synchronous up-down counters) and timing diagrams conveyed the functional information. The performance characteristics of each cell were provided by the loading characteristics, delay and timing constraints, and some information about DC and AC power consumption. The designers chose the cell type according to the functionality, estimated the performance of the design, and eventually re-implemented it in an optimized way as necessary to meet performance constraints.

Design automation enabled tremendous progress in efficiency, productivity, and the ability to deal with complexity, yet it did not change the fundamental requirements for ASIC design. Therefore, ALF needs to provide models with *functional* information and *performance* information, primarily including timing and power. Signal integrity characteristics, such as noise margin can also be included under performance category. Such information is typically found in any databook for analog cells. At deep sub-micron levels, digital cells behave similar to analog cells as electronic devices bound by physical laws and therefore are not infinitely robust against noise.

Table 1 shows a list of applications used in ASIC design flow and their relationship to ALF.

NOTE — ALF covers *library* data, whereas *design* data needs to be provided in other formats.

Table 1—Target applications and models supported by ALF

| Application     | Functional model | Performance model | Physical model   |

|-----------------|------------------|-------------------|------------------|

| Simulation      | Derived from ALF | N/A               | N/A              |

| Synthesis       | Supported by ALF | Supported by ALF  | Supported by ALF |

| Design for test | Supported by ALF | N/A               | N/A              |

55

Table 1—Target applications and models supported by ALF (Continued)

| Application      | Functional model | Performance model | Physical model   |

|------------------|------------------|-------------------|------------------|

| Design planning  | Supported by ALF | Supported by ALF  | Supported by ALF |

| Timing analysis  | N/A              | Supported by ALF  | N/A              |

| Power analysis   | N/A              | Supported by ALF  | N/A              |

| Signal integrity | N/A              | Supported by ALF  | N/A              |

| Layout           | N/A              | N/A               | Supported by ALF |

Historically, a functional model was virtually identical to a simulation model. A functional gate-level model was used by the proprietary simulator of the ASIC company and it was easy to lump it together with a rudimentary timing model. Timing analysis was done through dynamic functional simulation. However, with the advanced level of sophistication of both functional simulation and timing analysis, this is no longer the case. The capabilities of the functional simulators have evolved far beyond the gate-level and timing analysis has been decoupled from simulation.

RTL design planning is an emerging application type aiming to produce "virtual prototypes" of complex for system-on-chip (SOC) designs. RTL design planning is thought of as a combination of some or all of RTL floorplanning and global routing, timing budgeting, power estimation, and functional verification, as well as analysis of signal integrity, EMI, and thermal effects. The library components for RTL design planning range from simple logic gates to parameterizeable macro-functions, such as memories, logic building blocks, and cores.

From the point of view of library requirements, applications involved in RTL design planning need functional, performance, and physical data. The functional aspect of design planning includes RTL simulation and formal verification. The performance aspect covers timing and power as primary issues, while signal integrity, EMI, and thermal effects are emerging issues. The physical aspect is floorplanning. As stated previously, the functional and performance models of components can be described in ALF.

ALF also covers the requirements for physical data, including layout. This is important for the new generation of tools, where logical design merges with physical design. Also, all design steps involve optimization for timing, power, signal integrity, i.e. electrical correctness and physical correctness. EDA tools need to be knowledgeable about an increasing number of design aspects. For example, a place and route tool needs to consider congestion as well as timing, crosstalk, electromigration, antenna rules etc. Therefore it is a logical step to combine the functional, electrical and physical models needed by such a tool in a unified library.

Figure 1 shows how ALF provides information to various design tools.

Figure 1—ALF and its target applications

The worldwide accepted standards for hardware description and simulation are VHDL and Verilog. Both languages have a wide scope of describing the design at various levels of abstraction: behavioral, functional, synthesizable RTL, and gate level. There are many ways to describe gate-level functions. The existing simulators are implemented in such a way that some constructs are more efficient for simulation run time than others. Also, how the simulation model handles timing constraints is a trade-off between efficiency and accuracy. Developing efficient simulation models which are functionally reliable (i.e., pessimistic for detecting timing constraint violation) is a major development effort for ASIC companies.

Hence, the use of a particular VHDL or Verilog simulation model as primary source of functional description of a cell is not very practical. Moreover, the existence of two simulation standards makes it difficult to pick one as a

45

50

reference with respect to the other. The purpose of a generic functional model is to serve as an absolute reference for all applications that require functional information. Applications such as synthesis, which need functional information merely for recognizing and choosing cell types, can use the generic functional model directly. For other applications, such as simulation and test, the generic functional model enables automated simulation model and test vector generation and verification, which has a tremendous benefit for the ASIC industry.

With progress of technology, the set of physical constraints under which the design functions have increased dramatically, along with the cost constraints. Therefore, the requirements for detailed characterization and analysis of those constraints, especially timing and power in deep submicron design, are now much more sophisticated. Only a subset of the increasing amount of characterization data appears in today's databooks.

ALF provides a generic format for all type of characterization data, without restriction to state-of-the art timing models. Power models are the most immediate extension and they have been the starter and primary driver for ALF.

Detailed timing and power characterization needs to take into account the *mode of operation* of the ASIC cell, which is related to the functionality. ALF introduces the concept of *vector-based modeling*, which is a generalization and a superset of today's timing and power modeling approaches. All existing timing and power analysis applications can retrieve the necessary model information from ALF.

#### 1.4 Conventions

The syntax for description of lexical and syntax rules uses the following conventions.

\*\*Consider using the BNF nomenclature from IEEE 1481-1999\*\*

The syntax for explanation of semantics of expressions uses the following conventions.

```

=== left side and right side expressions are equivalent <item>a placeholder for an item in regular syntax

```

#### 1.5 Contents of this standard

The organization of the remainder of this standard is

- Clause 2 (References) provides references to other applicable standards that are assumed or required for ALF.

- Clause 3 (Definitions) defines terms used throughout the different specifications contained in this standard.

- Clause 4 (Acronyms and abbreviations) defines the acronyms used in this standard.

- Clause 5 (ALF language construction principles and overview) defines the language construction principles.

- Clause 6 (Lexical rules) specifies the lexical rules.

- Clause 7 (Auxiliary syntax rules) defines syntax and semantics of auxiliary items used in this standard.

1

5

10

15

20

25

30

35

40

45

50

- 1 Clause 8 (Generic objects and related statements) defines syntax and semantics of generic objects used in this standard.

- Clause 9 (Library-specific objects and related statements) defines syntax and semantics of library-specific objects used in this standard.

- Clause 10 (Description of functional and physical implementation) defines syntax and semantics of the control expression language used in this standard

- Clause 11 (Description of electrical and physical measurements) defines syntax and semantics of arithmetic models used in this standard.

- Annexes. Following Clause 11 are a series of normative and informative annexes.

5

10

20

25

30

35

40

45

50

2. References \*\*Fill in applicable references, i.e. standards on which the herein proposed standard depends. This standard shall be used in conjunction with the following publication. When the following standard is superseded by an approved revision, the revision shall apply. \*\*The following is only an example. ALF does not depend on C. ISO/IEC 9899:1990, Programming Languages—C.<sup>1</sup> [ISO 8859-1: 1987(E)] ASCII character set

1

5

10

15

20

25

30

35

40

45

50

<sup>&</sup>lt;sup>1</sup>ISO publications are available from the ISO Central Secretariat, Case Postale 56, 1 rue de Varembé, CH-1211, Genève 20, Switzerland/ Suisse (http://www.iso.ch/). IEC publications are available from the Sales Department of the International Electrotechnical Commission, Case Postale 131, 3, rue de Varembé, CH-1211, Genève 20, Switzerland/Suisse (http://www.iec.ch/). ISO/IEC publications are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

| 3. Definitions                                                                                                                                                                                                                                                                                                                                        | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| For the purposes of this standard, the following terms and definitions apply. The <i>IEEE Standard Dictionary of Electrical and Electronics Terms</i> [B4] should be consulted for terms not defined in this standard.                                                                                                                                | 5  |

| **Fill in definitions of terms which are used in the herein proposed standard.                                                                                                                                                                                                                                                                        | 3  |

| 3.1 <b>advanced library format:</b> The format of any file that can be parsed according to the syntax and semantics defined within this standard.                                                                                                                                                                                                     | 10 |

| 3.2 <b>application</b> , <b>electric design automation (EDA) application</b> : Any software program that uses data represented in the Advanced Library Format (ALF). Examples include RTL (Register Transfer Level) synthesis tools, static timing analyzers, etc. <i>See also:</i> <b>advanced library format</b> ; <b>register transfer level</b> . | 15 |

| 3.3 arc: See: timing arc.                                                                                                                                                                                                                                                                                                                             | 13 |

| 3.4 <b>argument:</b> A data item required for the mathematical evaluation of an arithmetic model. <i>See also:</i> <b>arithmetic model</b> .                                                                                                                                                                                                          | 20 |

| 3.5 <b>arithmetic model:</b> A representation of a library quantity that can be mathematically evaluated.                                                                                                                                                                                                                                             | 20 |

| 3.6                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.7 <b>register transfer level:</b> A behavioral representation of a digital electronic design allowing inference of sequential and combinational logic components.                                                                                                                                                                                   | 25 |

| 3.8                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.9 <b>timing arc:</b> An abstract representation of a measurement between two points in time during operation of a library component.                                                                                                                                                                                                                | 30 |

| 3.10                                                                                                                                                                                                                                                                                                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                       | 35 |

|                                                                                                                                                                                                                                                                                                                                                       |    |

|                                                                                                                                                                                                                                                                                                                                                       | 40 |

|                                                                                                                                                                                                                                                                                                                                                       | 40 |

|                                                                                                                                                                                                                                                                                                                                                       |    |

|                                                                                                                                                                                                                                                                                                                                                       | 45 |

|                                                                                                                                                                                                                                                                                                                                                       |    |

|                                                                                                                                                                                                                                                                                                                                                       | 50 |

|                                                                                                                                                                                                                                                                                                                                                       |    |

### 4. Acronyms and abbreviations

This clause lists the acronyms and abbreviations used in this standard.

| ALF   | advanced library format, title of the herein proposed standard                        | 5  |

|-------|---------------------------------------------------------------------------------------|----|

| ASIC  | application specific integrated circuit                                               |    |

| AWE   | asymptotic waveform evaluation                                                        |    |

| BIST  | built-in self test                                                                    | 10 |

| BNF   | Backus-Naur Form                                                                      | 10 |

| CAE   | computer-aided engineering [the term electronic design automation (EDA) is preferred] |    |

| CAM   | content-addressable memory                                                            |    |

| CLF   | Common Library Format from Avant! Corporation                                         |    |

| CPU   | central processing unit                                                               | 15 |

| DCL   | Delay Calculation Language from IEEE 1481-1999 std                                    |    |

| DEF   | Design Exchange Format from Cadence Design Systems Inc.                               |    |

| DLL   | delay-locked loop                                                                     |    |

| DPCM  | Delay and Power Calculation Module from IEEE 1481-1999 std                            | 20 |

| DPCS  | Delay and Power Calculation System from IEEE 1481-1999 std                            |    |

| DSP   | digital signal processor                                                              |    |

| DSPF  | Detailed Standard Parasitic Format                                                    |    |

| EDA   | electronic design automation                                                          | 25 |

| EDIF  | Electronic Design Interchange Format                                                  |    |

| HDL   | hardware description language                                                         |    |

| IC    | integrated circuit                                                                    |    |

| IP    | intellectual property                                                                 | 30 |

| ILM   | Interface Logic Model from Synopsys Inc.                                              | 30 |

| LEF   | Library Exchange Format from Cadence Design Systems Inc.                              |    |

| LIB   | Library Format from Synopsys Inc.                                                     |    |

| LSSD  | level-sensitive scan design                                                           |    |

| MPU   | micro processor unit                                                                  | 35 |

| OLA   | Open Library Architecture from Silicon Integration Initiative Inc.                    |    |

| PDEF  | Physical Design Exchange Format from IEEE 1481-1999 std                               |    |

| PLL   | Phase-locked loop                                                                     |    |

| PVT   | process/voltage/temperature (denoting a set of environmental conditions)              | 40 |

| QTM   | Quick Timing Model                                                                    |    |

| RAM   | random access memory                                                                  |    |

| RC    | resistance times capacitance                                                          |    |

| RICE  | rapid interconnect circuit evaluator                                                  | 45 |

| ROM   | read-only memory                                                                      |    |

| RSPF  | Reduced Standard Parasitic Format                                                     |    |

| RTL   | Register Transfer Level                                                               |    |

| SDF   | Standard Delay Format from IEEE 1497 std                                              | 50 |

| SDC   | Synopsys Design Constraint format from Synopsys Inc.                                  | 50 |

| SPEF  | Standard Parasitic Exchange Format from IEEE 1481-1999 std                            |    |

| SPF   | Standard Parasitic Format                                                             |    |

| SPICE | Simulation Program with Integrated Circuit Emphasis                                   |    |

| STA   | Static Timing Analysis                                                                | 55 |

| 1  | l | STAMP<br>TCL  | (STA Model Parameter ?) format from Synopsys Inc.                                                                |

|----|---|---------------|------------------------------------------------------------------------------------------------------------------|

|    |   | TLF           | Tool Command Language (supported by multiple EDA vendors) Timing Library Format from Cadence Design Systems Inc. |

| 5  | 5 | VCD           | Value Change Dump format (from IEEE 1364 std ?)                                                                  |