## Motivation

#### Fast Introduction of new Technologies requires Efficient Library Generation

Time to Market Efficient Use of Resources Cost Reduction Automation Quality Assignment

#### **Cost of ASIC Library Development**

Resources e.g. 60 people

Time e.g. 4 months

20 person years -> 50% productivity increase saves 10 person years

Freed-up resources can help to make your next product even more competitive or bring it faster to market!

#### **Extensive Collaboration between EDA and ASIC Vendors necessary for Success**

Leverage for New EDA Tools

Fair Comparison Between Tools

The ALF standard can make life easier for everybody!

| The ALF Story                                                                  |                                    |

|--------------------------------------------------------------------------------|------------------------------------|

| ALF work group started as OVI PS-TSC                                           | 6/96                               |

| ALF named and announced at IVC/VIUF                                            | 3/97                               |

| ALF integrated in ECSI OMILIBRES project                                       | 9/97                               |

| ALF1.0 approved by OVI                                                         | 12/97                              |

| OLA project for integration of ALF and DCL approved by ASIC council and OVI    | 2/98                               |

| OLA demonstrator from ASIC council / SI2                                       | 6/98 (DAC)                         |

| ALF libraries from ASIC council companies                                      | prototypes 4/98<br>production 9/98 |

| Commitment for ALF support from EDA<br>Ambit, Avant!, Cadence, Mentor Graphics | 2/98                               |

| ALF work group preparing ALF1.1                                                | ongoing                            |

# The ALF Story (cont.)

Companies currently active in ALF work group, coordinated by OVI

Ambit, Avant!, Cadence, Cadworx, Duet, Fujitsu, LSI Logic, Mentor Graphics, Motorola, NEC, Toshiba, VLSI Technologies

Companies involved in OLA (ALF-DCL integration project), coordinated by SI2

Ambit, Avant!, Cadence, Cadworx, Duet, IBM, LSI Logic, Lucent Technologies, Mentor Graphics, Motorola, NEC, Synopsys, TI, VLSI Technologies

Other EDA vendors interested in ALF

ASC, Sente Inc., Tera Systems, Verysys

Other ASIC and System vendors interested in ALF Alcatel, I&D Telefonica, Siemens, Sun Microsystems

Other standardization bodies interested in ALF ECSI, VSIA

### Relation between ALF, DCL, OLA (cont.)

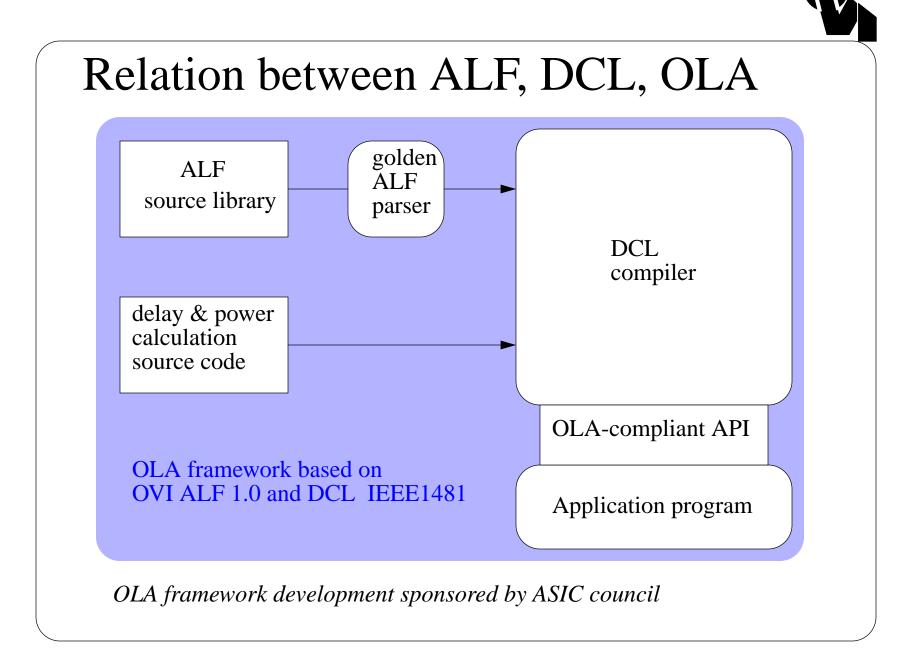

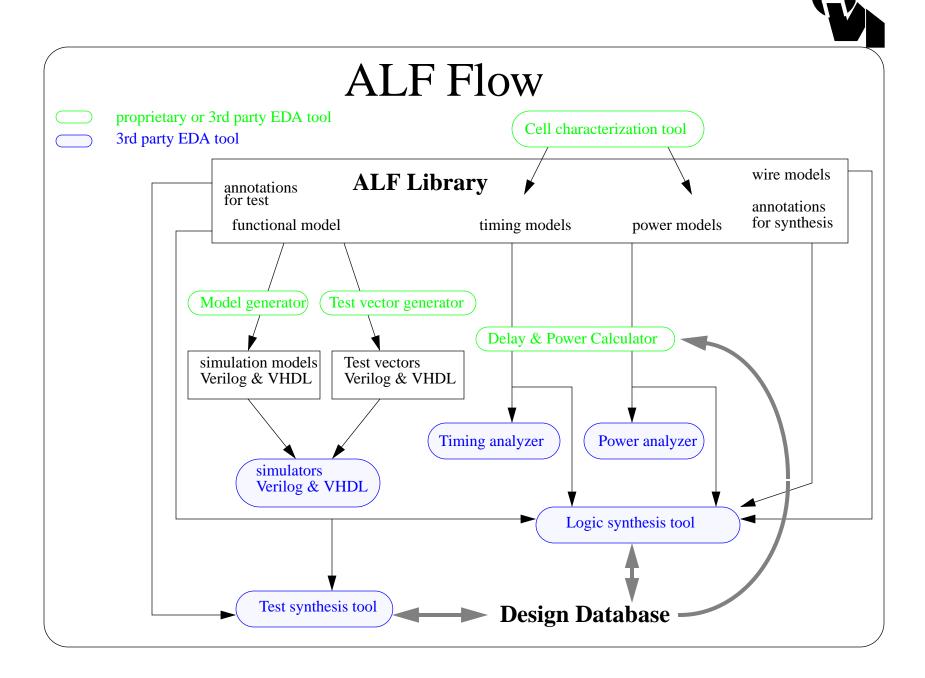

ALF (Advanced Library Format) is the source for cell characterization data

Golden parser preprocesses ALF source for correct syntax and semantics

DCL (Delay Calculation Language) is the source for delay & power calculation algorithms

Delay & power calculation requires both *library* and *design* data as input Results of calculation are required by application

DCL compiler digests both ALF and DCL source and transforms them into optimized code for performance and memory usage

OLA (Open Library API) is the interface between ALF, DCL and the application program

OLA makes delay & power data and calculation algorithms transparent ALF and DCL sources cannot be retrieved technically

Functional models and annotations are accessible through OLA ALF source can be retrieved Source access protection can be embedded in API

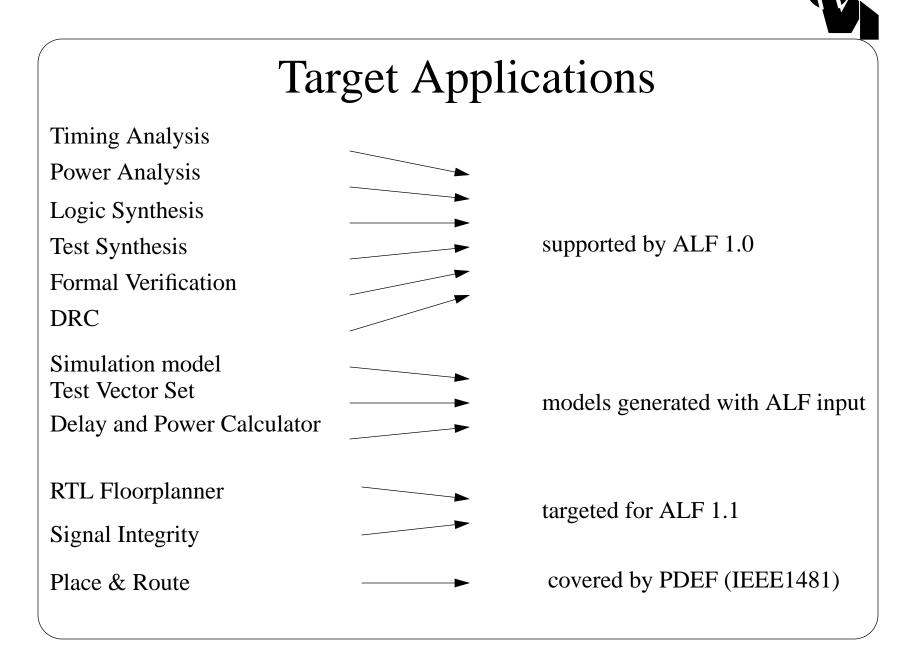

### ALF Features

#### **Modeling Scope**

Combinational and sequential cells

IO cells

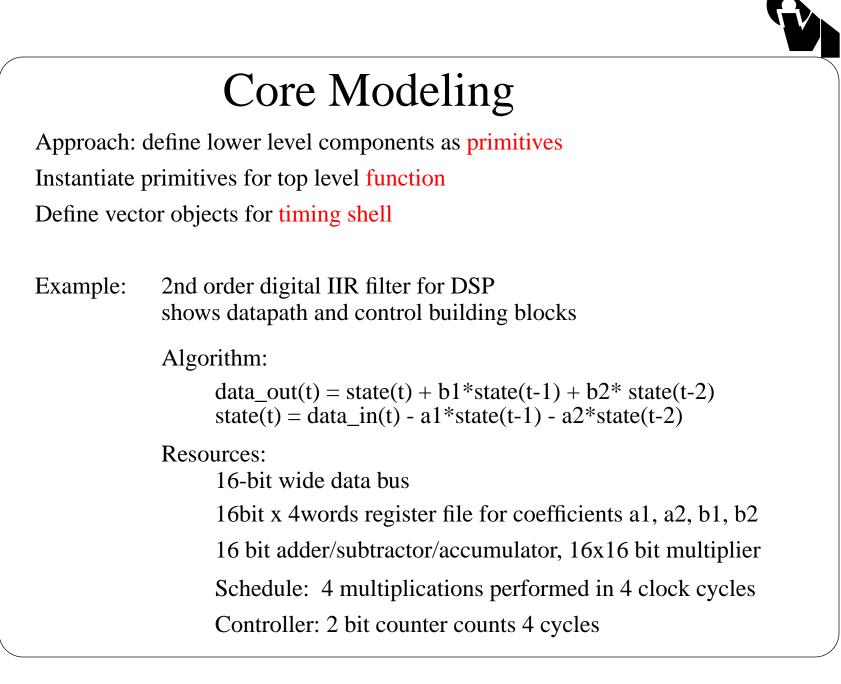

Datapath: counters, adders, multipliers, comparators ...

Memories

Cores

#### **Generic Functional Model**

Canonical functional specification language Supports logic expressions, event expressions, state and transition tables Predefined and user-defined primitives Hierarchical modeling, emulation of netlists

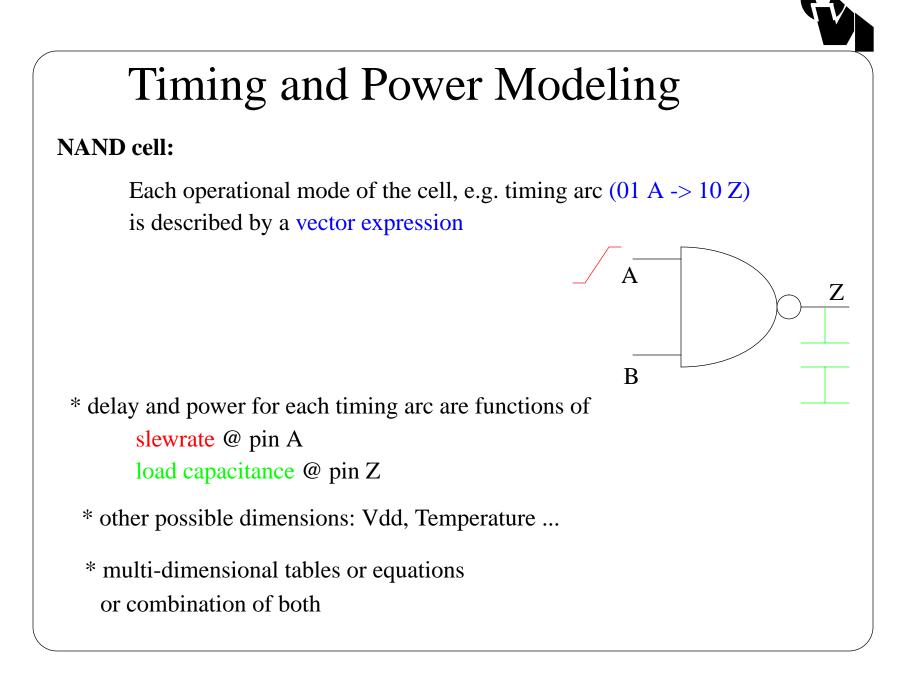

#### Generic Model for CharacterizationData of Cells and Blocks

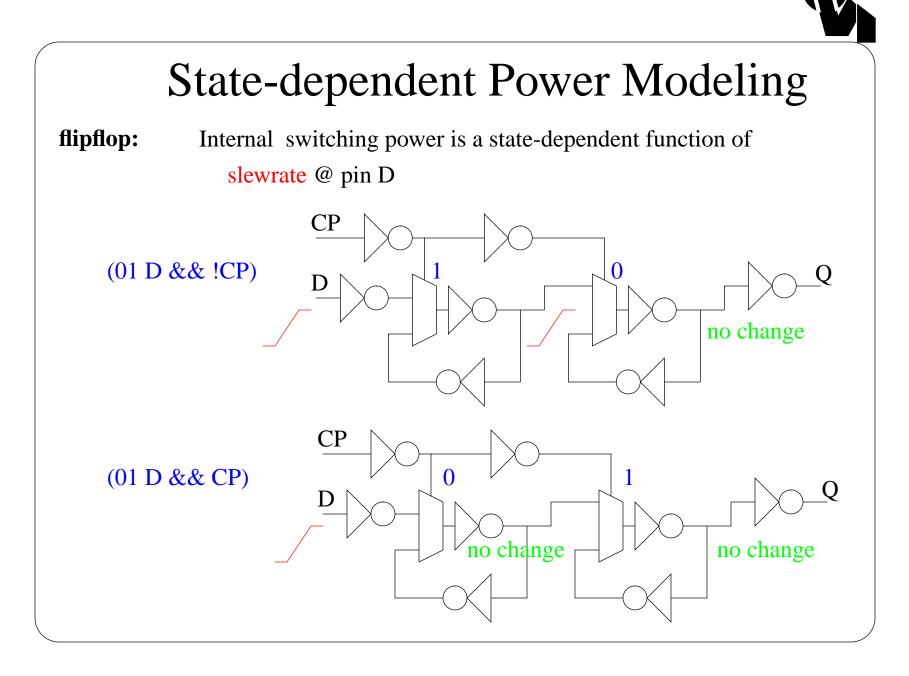

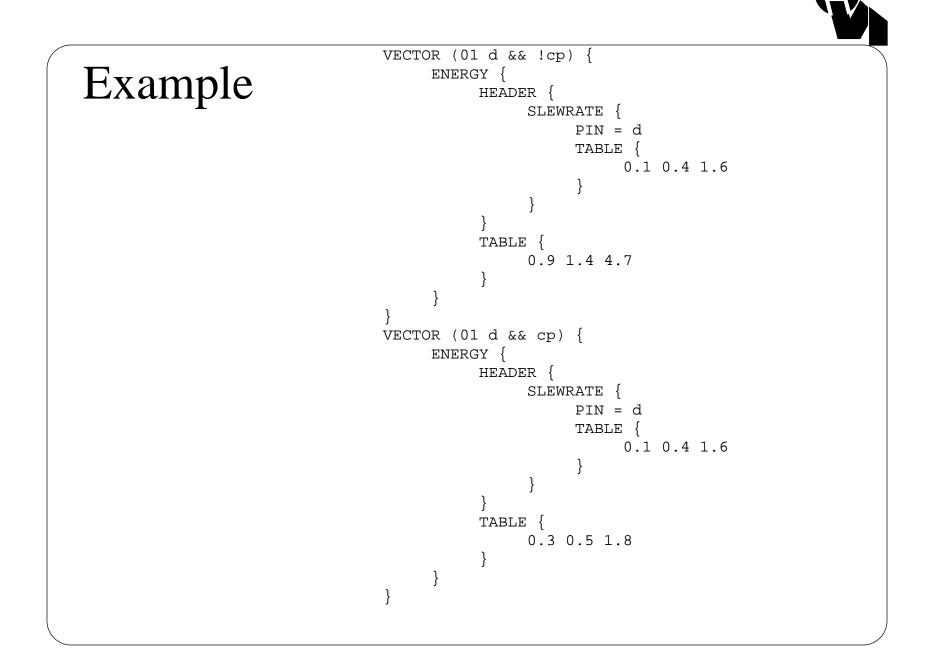

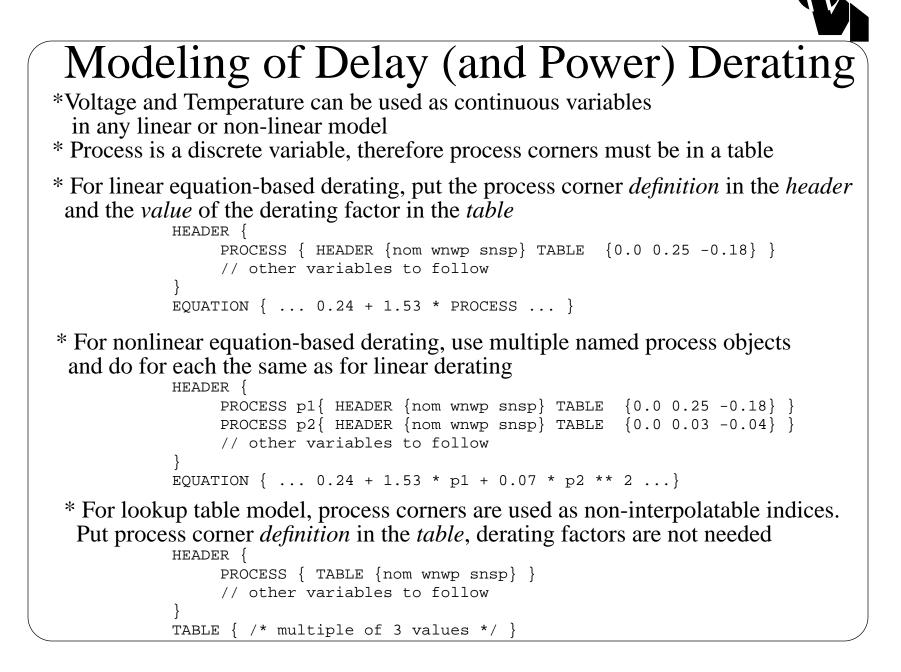

Wide range of variables, including timing and power Equation or Table Based Models Vector-based modeling encompassed timing arcs, state-dependency and more

#### **Generic Physical Model**

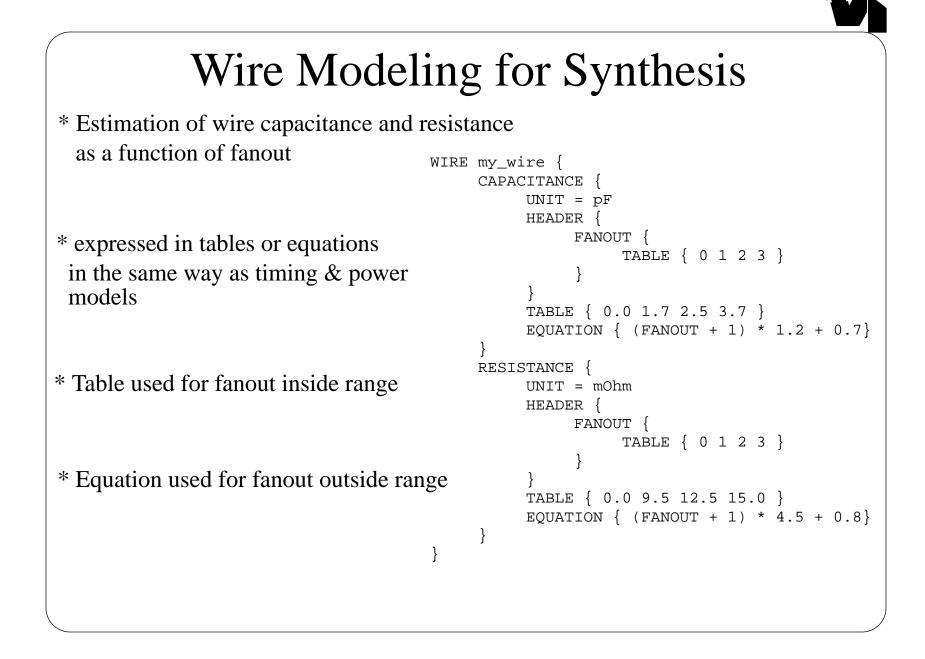

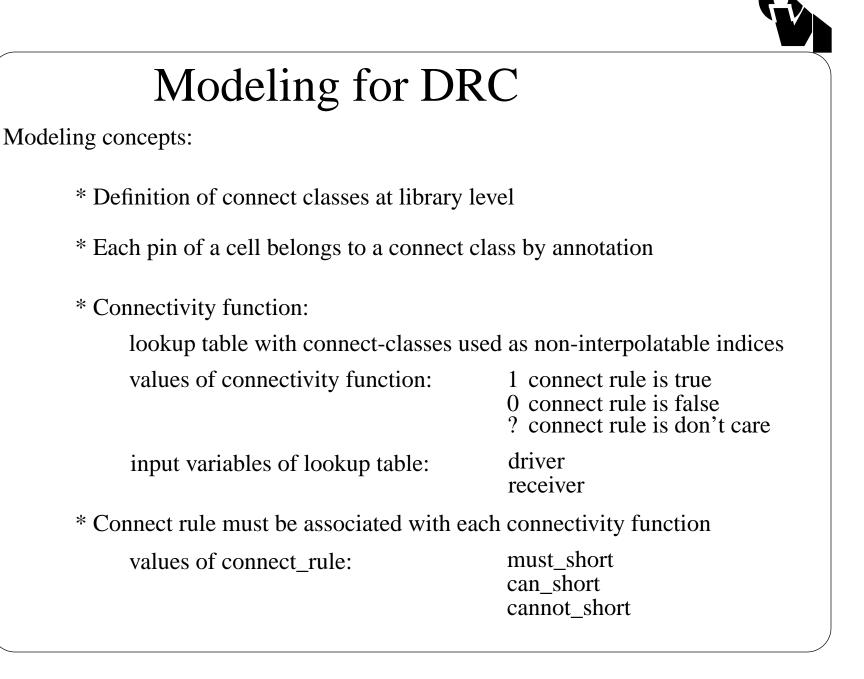

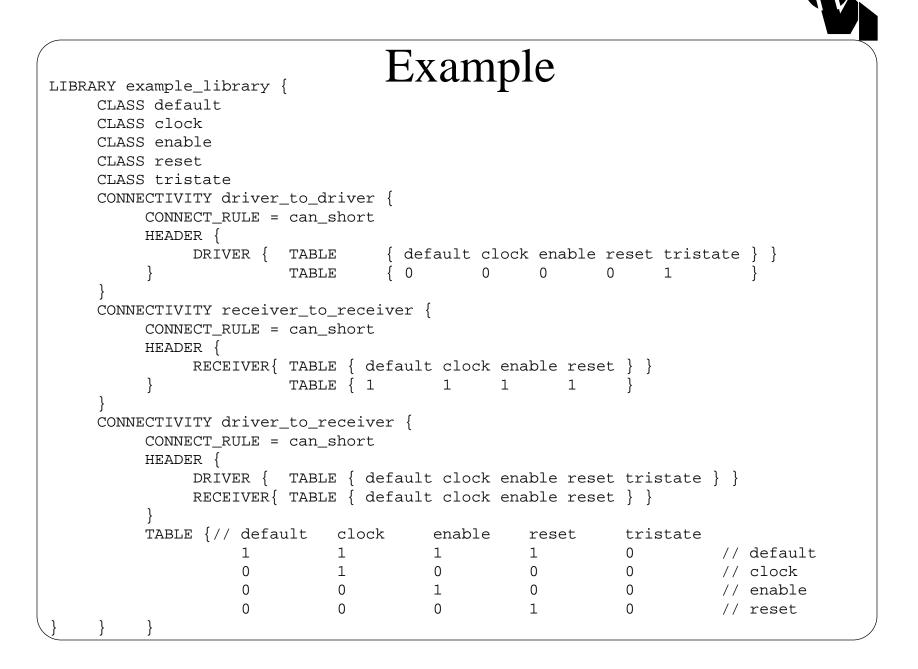

Annotation of Physical Cell Properties for Logic and Test Synthesis Equation or Table Based Wire Models Support for DRC

### A Simple Self-Explaining Example

```

LIBRARY sample_library {

```

}

```

//\ {\rm written} by ALFRED CLEARMAN

```

```

CAPACITANCE {UNIT = pF}

SLEWRATE {UNIT = ns}

DELAY {UNIT = ns}

ENERGY {UNIT = pJ}

```

```

CELL nand2 {

// fill in cell information

}

```

```

CELL d_flipflop {

// fill in cell information

}

```

```

CELL nand2 {

PIN a {

DIRECTION = input

CAPACITANCE = 20 \{ \text{UNIT} = \text{ff} \}

PIN b {

DIRECTION = input

CAPACITANCE = 20 \{ \text{UNIT} = \text{ff} \}

PIN z {

DIRECTION = output

FUNCTION {

BEHAVIOR {

z = !(a \&\& b);

VECTOR (10 \ a \rightarrow 01 \ z)

// fill in characterization data

VECTOR (01 \ a \rightarrow 10 \ z)

// fill in characterization data

VECTOR (10 b -> 01 z) {

// fill in characterization data

VECTOR (01 b -> 10 z) {

// fill in characterization data

```

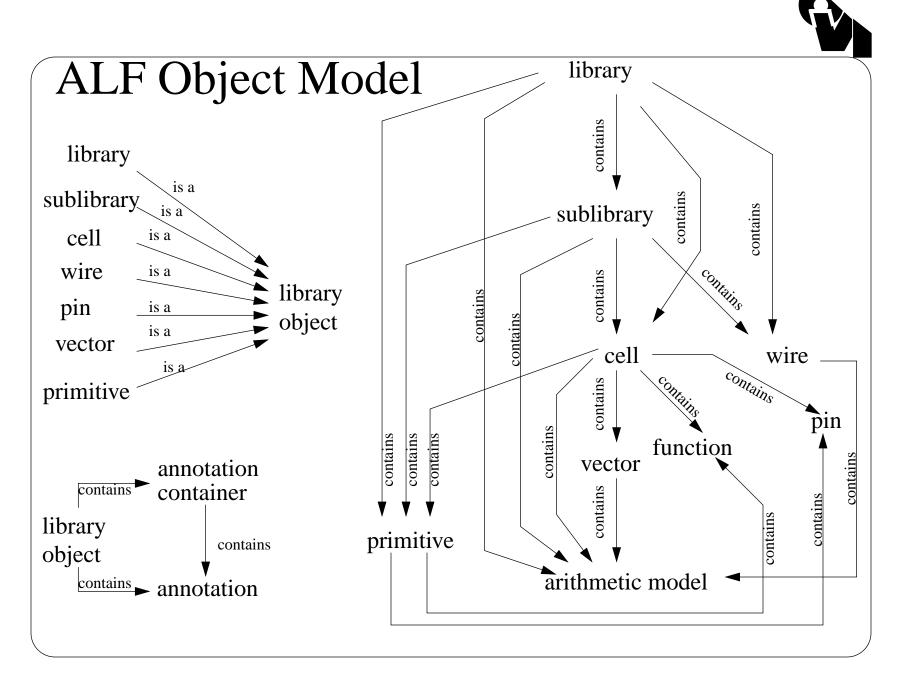

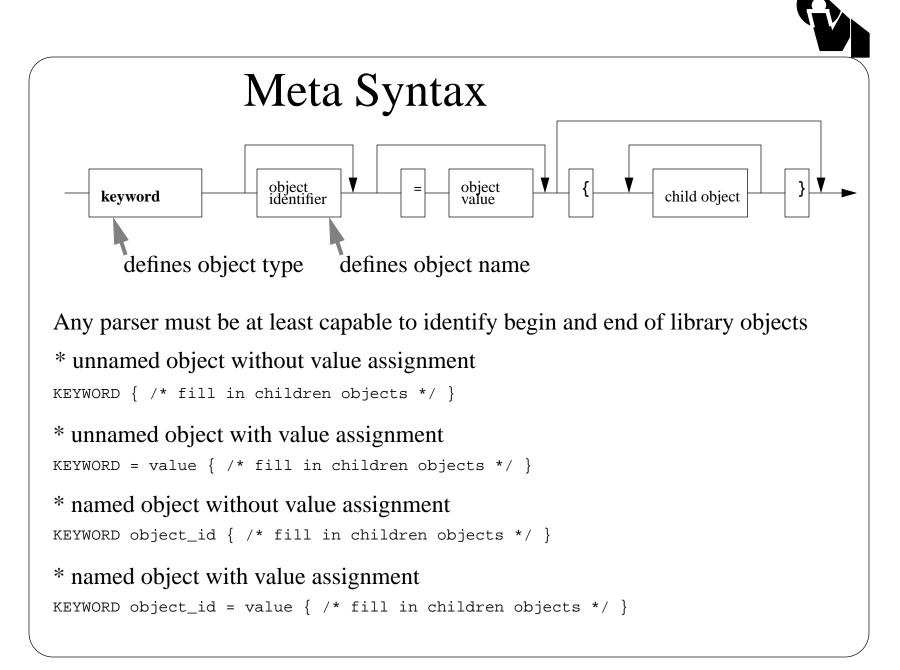

### Semantic Features of ALF

\* Each object type is recognized by a keyword

\* general purpose objects use hard keywords

\* library objects, especially arithmetic models, use context-specific keywords

- expandable modeling space for various applications

- customized modeling possible

ALF is case-insensitive However, keywords are written in upper case in all examples for clarity

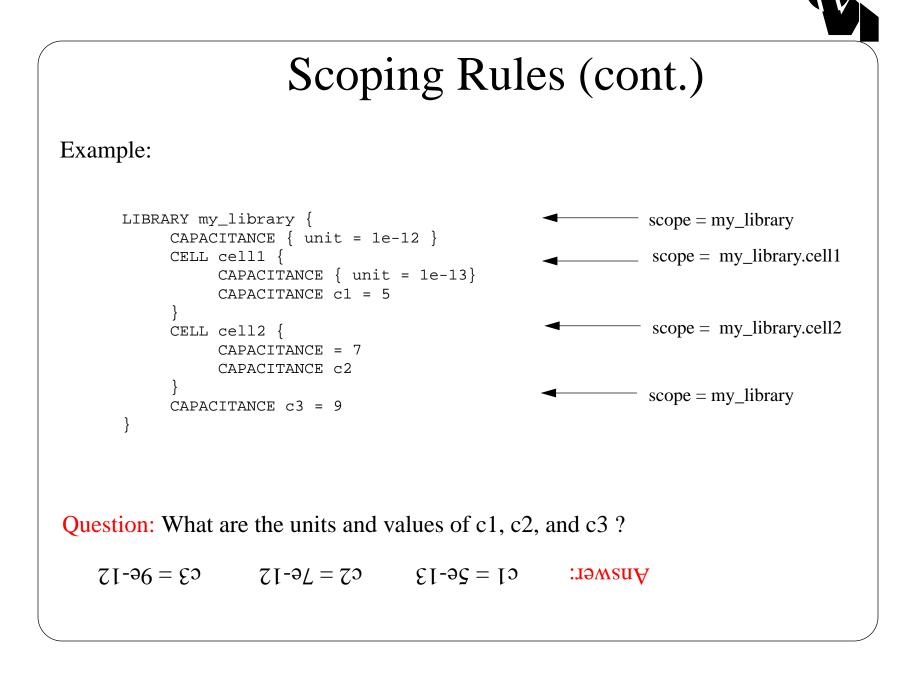

# Scoping Rules

- \* curly parenthesis { } change the scope

- \* children objects are not visible outside their scope

- \* parent objects propagate their visibility through their children objects

- \* no more than one unnamed object of the same type allowed within the same scope

- \* no unnamed object after a named object of the same type in the same scope (unnamed object, if any, must come first)

- \* unlimited number of named objects of same type allowed within the same scope

- \* named objects inherit properties of nearest visible unnamed object

- \* any inherited property can be overwritten by the object itself

- \* each library object may contain general purpose objects as well

- \* general purpose objects may not contain arbitrary general purpose objects

- \* the meaning of a general purpose object must be understood by any parser, whereas some tool-specific parsers may skip particular library objects (e.g. scan insertion tool does not need power consumption information)

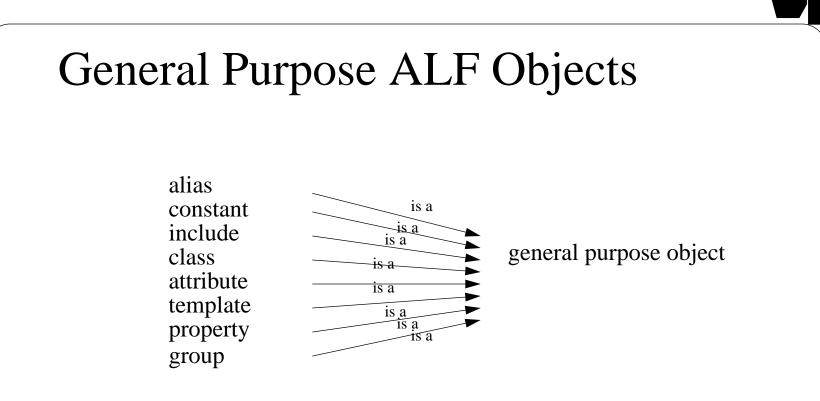

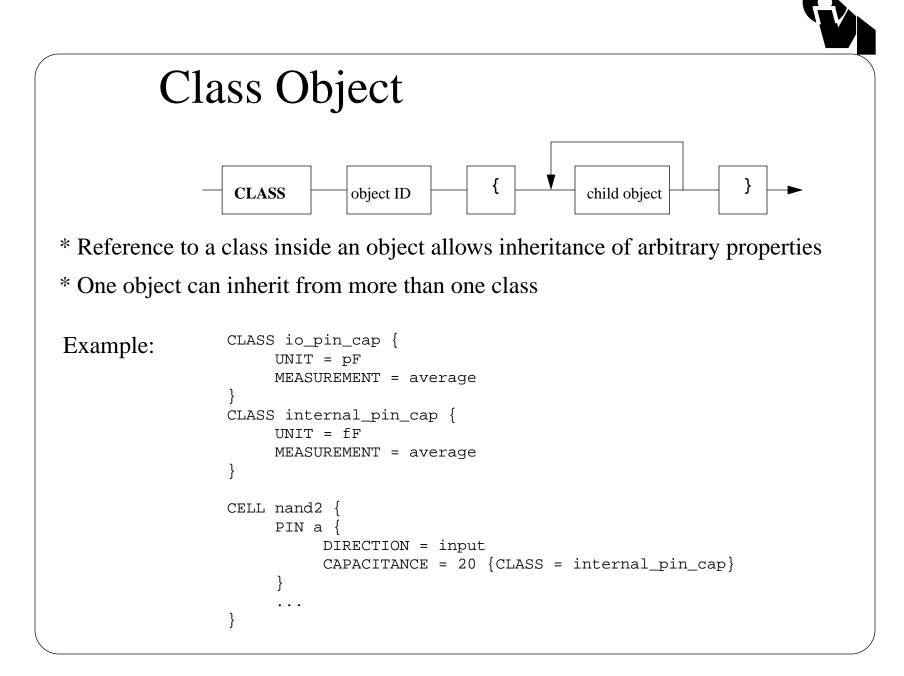

```

General Purpose ALF Objects (cont.)

* alias: useful for customized renaming of context-sensitive keywords

ALIAS RAMPTIME = SLEWRATE

* constant: useful for constant numbers

CONSTANT vdd = 3.3

* include: inclusion of external ALF file

INCLUDE 'primitives.alf'

* attribute: association of arbitrary unordered attributes

CELL rom_8x128 {

ATTRIBUTE {ROM ASYNCHRONOUS STATIC}

* property: useful for arbitrary parameter-value assignment

PROPERTY items {

parameter1 = value1 ;

parameter2 = value2 ;

}

```

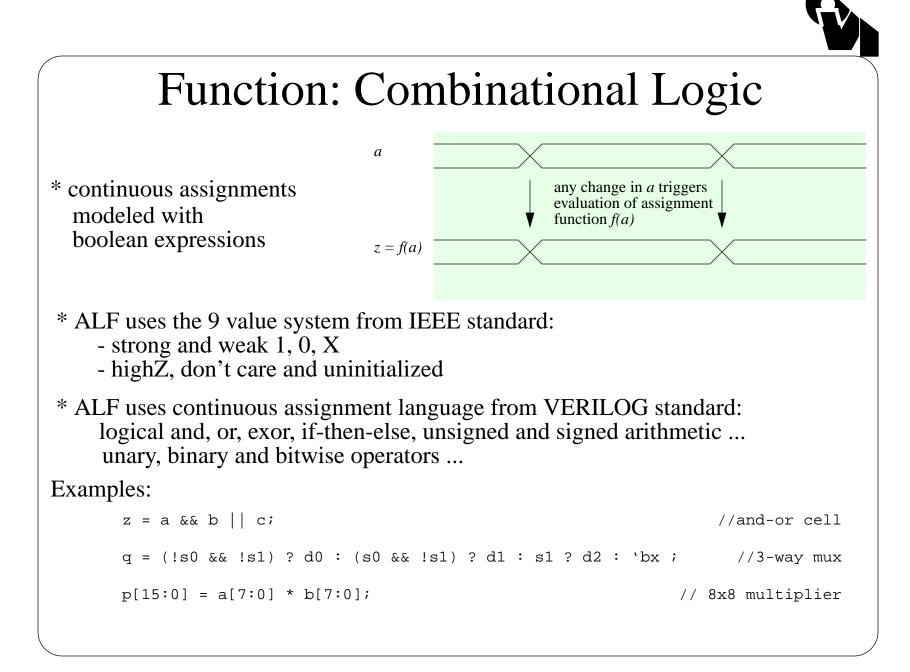

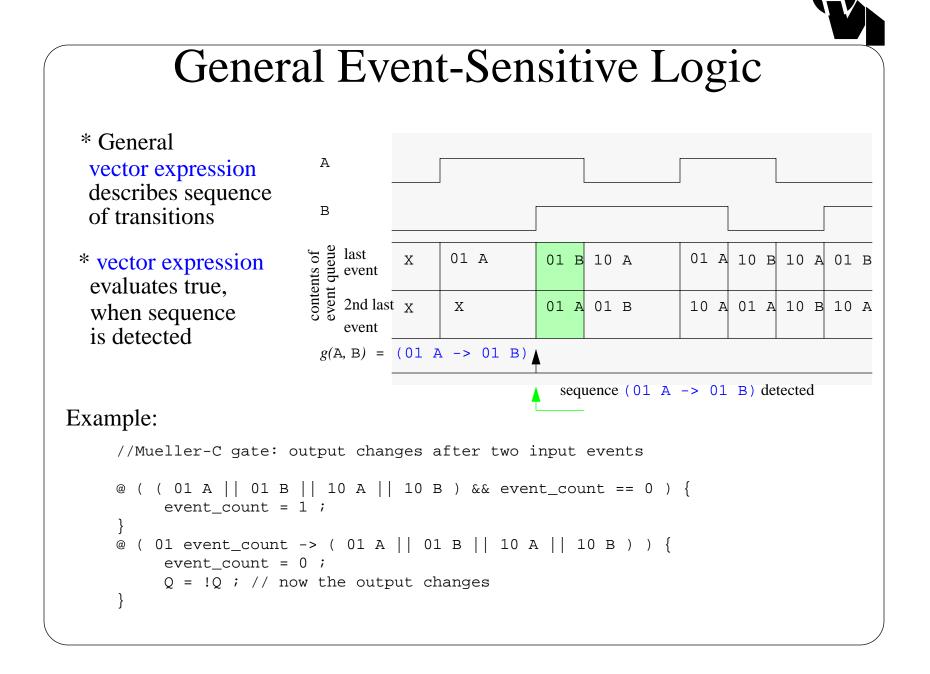

### Expressions

- \* Boolean expressions and vector expressions are used in functions and vectors

- \* Arithmetic expressions are used in arithmetic models

- \* Expressions can be nested

- \* Set of operators for arithmetic and boolean expressions adopted from IEEE standards

- \* Extended set of operators for vector expressions

- \* Standard priority rules for operators

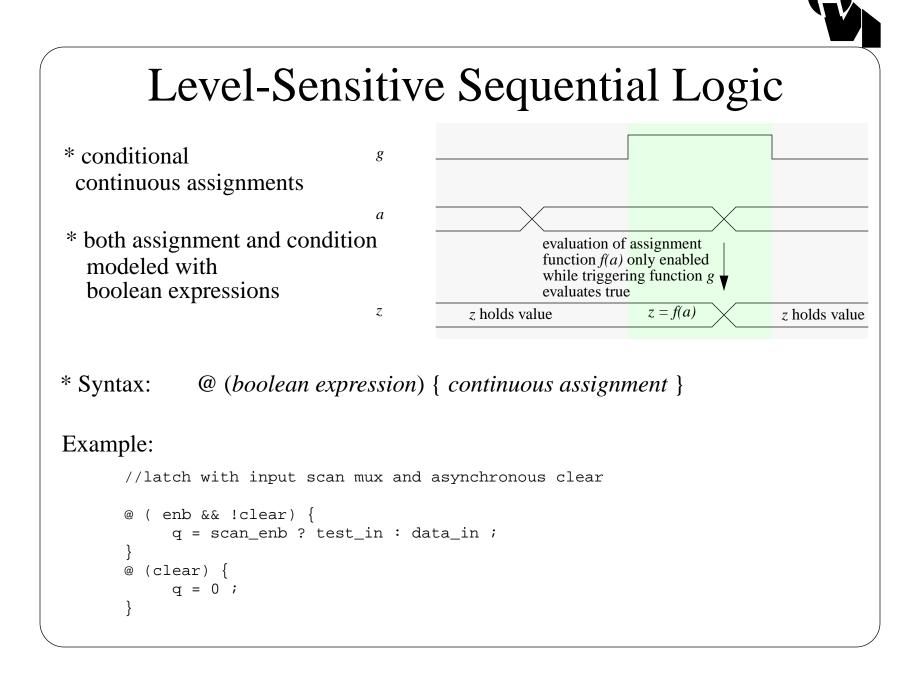

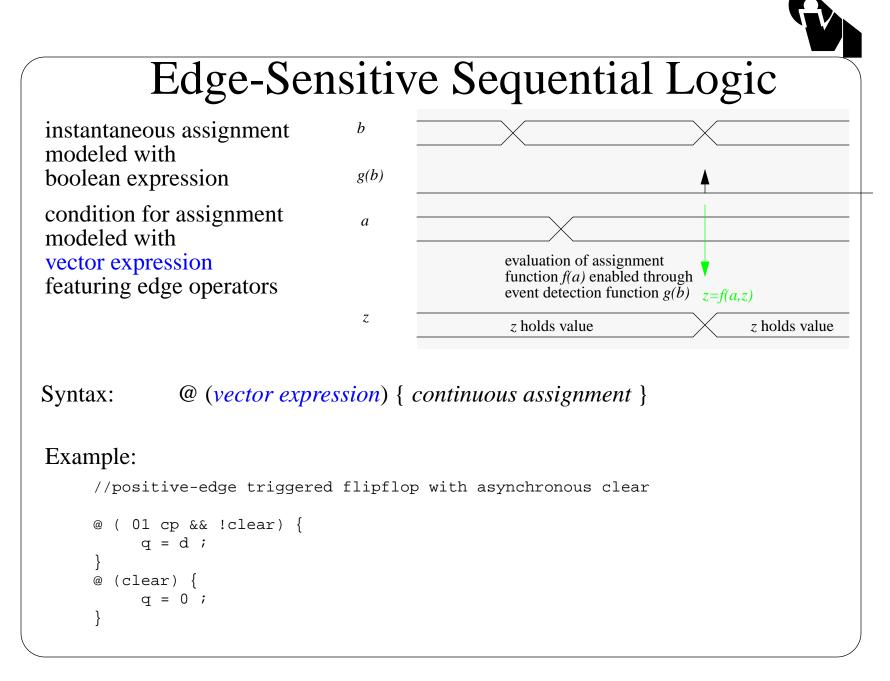

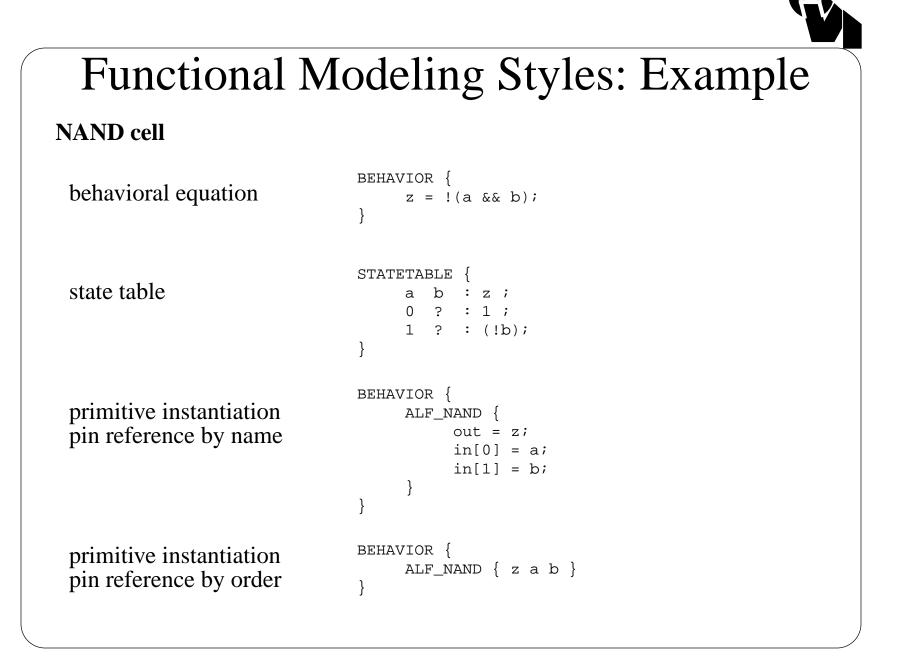

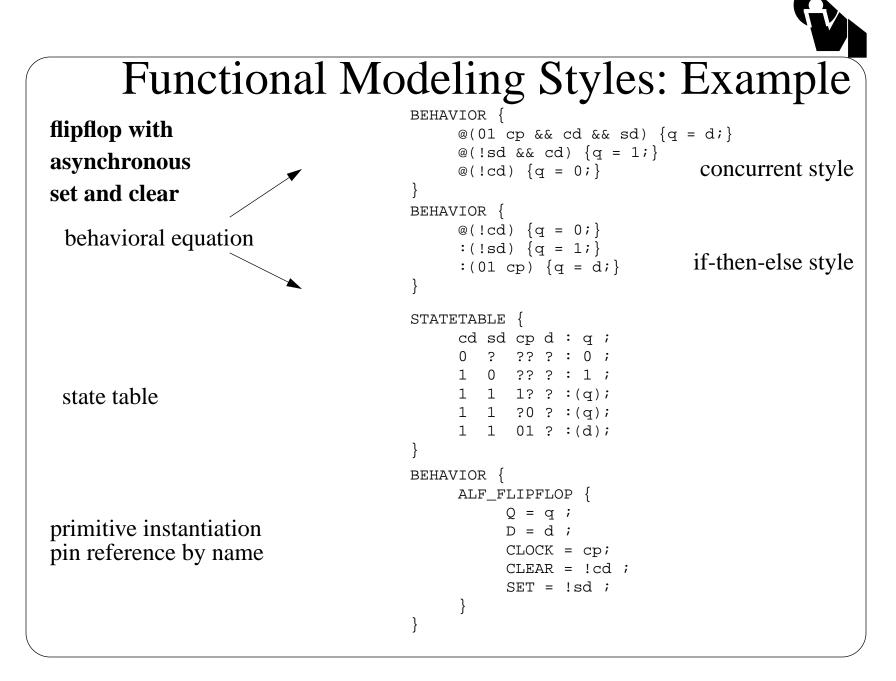

## Choice of Functional Modeling Styles

logic behavior

logic statetable

hybrid modeling style is legal

primitive instantiation

- \* a primitive is a user-defineable object, which has pins and function like a cell, but no arithmetic model

- \* modeler may define arbitrary **primitives** at different levels of scope for hierarchical netlist-style modeling

- \* ALF provides a set of predefined primitives, starting with ALF\_ prefix ALF\_BUF, ALF\_NOT ALF\_AND, ALF\_OR, ALF\_XOR, ALF\_NAND, ALF\_NOR, ALF\_NXOR ALF\_BUFIF1, ALF\_BUFIF0, ALF\_NOTIF1, ALF\_NOTIF0 ALF\_MUX, ALF\_LATCH, ALF\_FLIPFLOP

- \* Names starting with ALF\_ are reserved for future predefined primitives

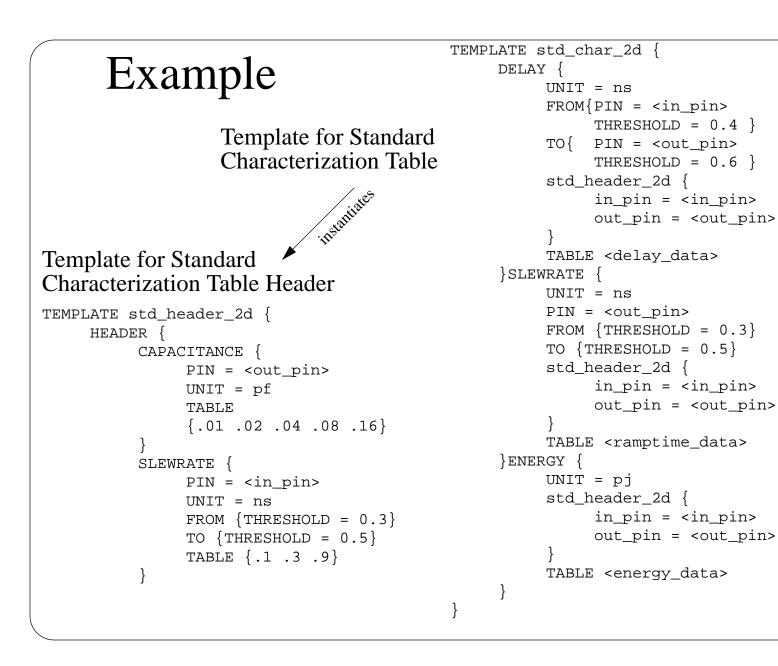

```

CELL nand2 {

Example (cont.)

PIN a {

DIRECTION = input

CAPACITANCE = 0.02 {UNIT = pf}

Use of template

PIN b {

in delay & power table

DIRECTION = input

for NAND gate

CAPACITANCE = 0.02 {UNIT = pf}

std_char_2d {

PIN z {

in_pin = a

DIRECTION = output

out_pin = z

delay_data {

FUNCTION {

0.1 0.2 0.4 0.8 1.6

BEHAVIOR {

0.2 0.3 0.5 0.9 1.7

z = !(a \&\& b);

0.4 0.5 0.7 1.1 1.9

ramptime_data {

VECTOR (10 \ a \rightarrow 01 \ z)

std_char_2d { ... }

0.1 0.2 0.4 0.8 1.6

0.1 0.2 0.4 0.8 1.6

VECTOR (01 \ a \rightarrow 10 \ z)

0.2 0.4 0.6 1.0 1.8

std_char_2d { ... }

energy_data {

0.21 0.32 0.64 0.98 1.96

VECTOR (10 b -> 01 z) {

0.22 0.33 0.65 0.99 1.97

std_char_2d { ... }

0.31 0.42 0.74 1.08 2.06

VECTOR (01 b -> 10 z) {

}

std_char_2d { ... }

```

# Rules for Table Format

\* Table format is defined by the order of appearance of the arguments in the header

\* Each argument must have a one- dimensional table itself

\* First argument defines innermost index

\* Target table contains just data separated by whitespace

```

Example: DELAY {

HEADER {

CAPACITANCE { TABLE { 0.5 1.0 2.0 } }

SLEWRATE { TABLE { 0.3 0.9 } }

VOLTAGE { TABLE { 0.3 0.9 } }

TABLE {

0.3 0.5 0.8

0.6 1.0 1.4

0.2 0.4 0.7

0.5 0.8 1.2

}

Question: What is the delay for capacitance=1.0, slewrate=0.9, voltage=3.0 ?

(xəpui qıç) 0.1 = \Lambdaeləp :.IəMSUV

```

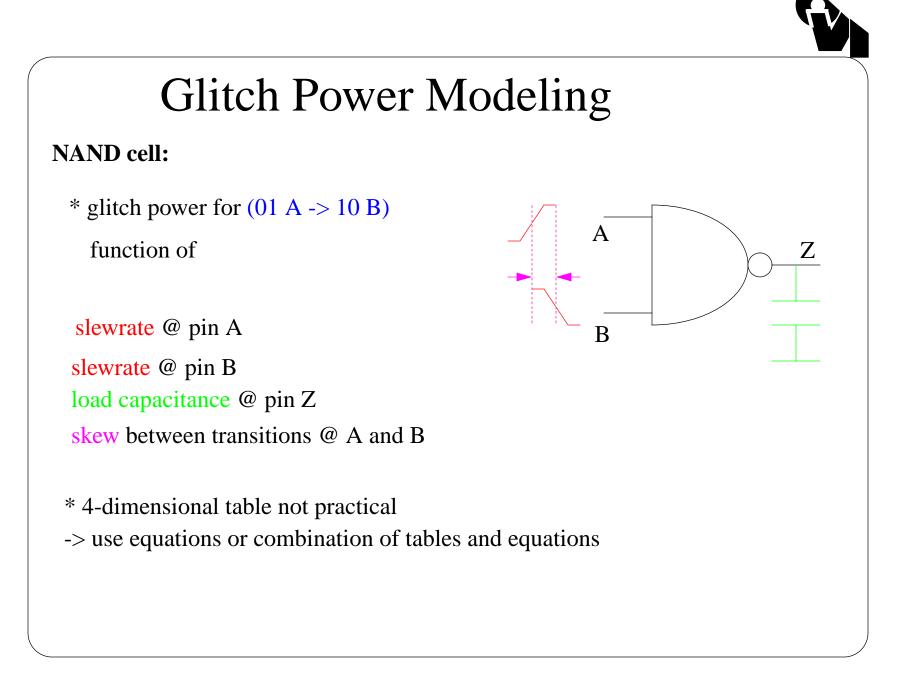

```

VECTOR (01 a -> 10 b) {

Example

ENERGY {

HEADER {

SLEWRATE s_a { PIN = a }

SLEWRATE s_b { PIN = b }

model glitch energy for a

DELAY dt {

specific vector as a function of

FROM \{ PIN = a \}

\{ PIN = b \}

ТО

- slewrate on each pin

ENERGY e_a {

- skew between input signals

HEADER {

SLEWRATE {

- energy for each input transition

PIN = a

which itself is a function of

TABLE {0.1 0.4 1.6}

- slewrate on each pin

TABLE {0.21 0.48 1.85}

ENERGY e_b {

HEADER {

SLEWRATE {

energy for each input

PIN = b

is modeled as table

TABLE {0.1 0.4 1.6}

TABLE {0.23 0.46 1.79}

energy for resulting glitch

is modeled as equation

EQUATION {

(e_a + e_b) * dt / (s_a + s_b)

```

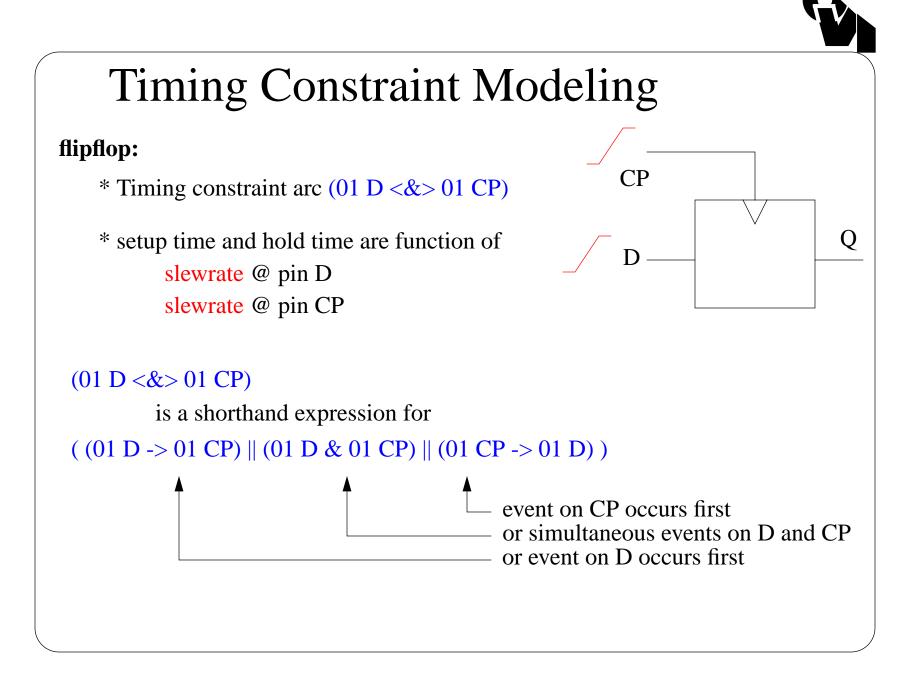

### Example

}

```

VECTOR (01 d <&> 01 cp)

SETUP {

FROM { PIN = d; THRESHOLD = 0.35; }

TO { PIN = cp; THRESHOLD = 0.35; }

header {

SLEWRATE s_d {

PIN = d

TABLE { 0.2 0.4 0.8 }

SLEWRATE s_cp {

PIN = cp

TABLE { 0.2 0.4 0.8 }

}

TABLE {

0.1 0.4 0.9

-0.2 0.1 0.6

-0.3 0.0 0.4

}

VIOLATION {

BEHAVIOR { q = bx; }

MESSAGE_TYPE = error

MESSAGE = "setup violation rising d to rising cp"

}

}

```

# Modeling for Test

- \* Annotations of Cell and Pin Properties for Scan Insertion and Test

- \* Reference to non-scan replacement model

#### Example:

| CELL | DFF2SC {                     |

|------|------------------------------|

|      | PIN Q {DIRECTION=output}     |

|      | PIN QN {DIRECTION=output}    |

|      | PIN D {DIRECTION=input }     |

|      | PIN CP {DIRECTION=input }    |

|      | PIN CD {DIRECTION=input }    |

|      | PIN SD {DIRECTION=input }    |

|      | FUNCTION {                   |

|      | $@(CD) {QN = 1;}$            |

|      | $@(SD) \{Q = 1;\}$           |

|      | $@(CD \&\& !SD) \{Q = 0; \}$ |

|      | $@(SD \&\& !CD) {QN = 0;}$   |

|      | @(01 CP && !CD && !SD)       |

|      | $\{Q = D; QN = !D; \}$       |

|      | }                            |

| }    |                              |

|      |                              |

|      |                              |

| CELL | S000 | <pre>{ PIN H01 {} PIN H02 {} PIN H03 {} PIN H03 {} PIN H04 {} PIN H05 {} PIN H06 {} PIN N01 {} PIN N02 {}</pre>                          |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| }    | SCAN | <pre>{ scan_type = mux_scan non_scan_cell = DFF2SC {     D = H06     CP = H02     CD = H05     SD = H04     Q = N01     QN = N02 }</pre> |

\* For Power modeling, number of switching bits can be used as a variable

```

CELL async_2port_ram {

Example

PIN enable_write {

DIRECTION = input

}

PIN [4:0] adr_write {

DIRECTION = input

PIN [4:0] adr_read {

DIRECTION = input

Asynchronous

PIN [7:0] data_write {

dual-port memory

DIRECTION = input

}

PIN [7:0] data_read {

DIRECTION = output

PIN [7:0] data_store [0:31]{

DIRECTION = output; VIEW = none; SCOPE = modeling;

} // array of virtual pins

FUNCTION {

BEHAVIOR {

data_read = data_store[adr_read];

@(enable_write) {

data_store[adr_write] = data_write;

// to be followed by timing and power arcs

```

```

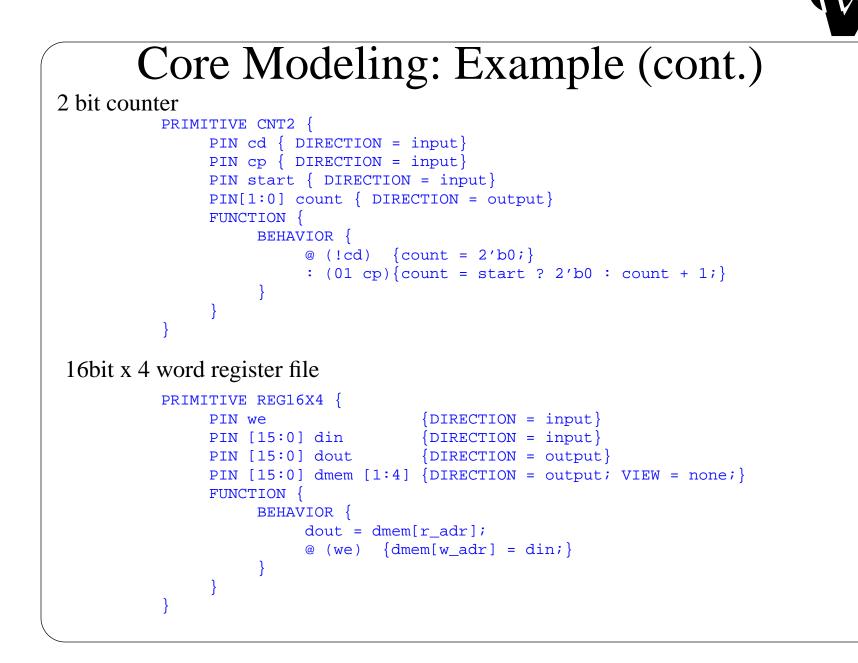

Core Modeling: Example

top-level view

CELL digital_filter {

// external pins

PIN [15:0] data out {DIRECTION = output;}

PIN [15:0] data_in

{DIRECTION = input; }

PIN [1:0] index_coeff{DIRECTION = input; }

PIN [15:0] coeff in

{DIRECTION = input;

PIN clock

{DIRECTION = input; }

PIN reset

{DIRECTION = input; }

PIN write coeff

{DIRECTION = input; }

PIN data_strobe

{DIRECTION = input; }

// internal pins

{DIRECTION = output; VIEW = none; }

PIN [1:0] count

PIN [15:0] coeff_out {DIRECTION = output; VIEW = none;}

// user-defined primitives

{ . . . }

PRIMITIVE CNT2

PRIMITIVE REG16X4 {

. . .

PRIMITIVE IIR2

// function

FUNCTION { ... }

// timing shell

GROUP index \{15 : 0\}

VECTOR (01 clock -> 01 data_out[index]) { DELAY { ... } }

VECTOR (01 clock -> 10 data_out[index]) { DELAY { ... }

VECTOR (01 clock <&> 01 data_in[index]) { SETUP { ... } HOLD { ... } }

VECTOR (01 clock <&> 10 data_in[index]) { SETUP { ... } HOLD { ...

}

```

```

datapath (2nd order digital IIR filter)

PRIMITIVE IIR2 {

PIN cd { DIRECTION = input}

PIN cp { DIRECTION = input }

PIN [15:0] dout {DIRECTION = output}

{DIRECTION = input}

PIN [15:0] din

PIN [1:0] cntrl {DIRECTION = input}

PIN [15:0] coeff {DIRECTION = input}

PIN [15:0] product {DIRECTION = output; VIEW = none}

PIN [15:0] accu

{DIRECTION = output; VIEW = none}

PIN [15:0] state1 {DIRECTION = output; VIEW = none}

{DIRECTION = output; VIEW = none}

PIN [15:0] state2

FUNCTION { BEHAVIOR {

sum =

(cntrl=='d0)? din - product :

(cntrl=='d1)? accu - product :

(cntrl=='d2 || cntrl=='d3)? accu + product ;

@ (!cd) {

product = 16'b0; accu = 16'b0; dout = 16'b0;

state1 = 16'b0; state2 = 16'b0;

: (01 cp){

product =

(cntrl=='d0 || cntrl=='d2)? coeff * state2 :

(cntrl=='d1 || cntrl=='d3)? coeff * state1 ;

accu = sum;

dout = (cntrl=='d0) ? accu : dout ;

state2 = (cntrl=='d0) ? state1 : state2;

state1 = (cntrl=='d0) ? accu : state1;

} } }

```

#### top-level function

```

CELL digital_filter {

. . .

FUNCTION {

BEHAVIOR {

CNT2

ul {

cd = reset;

= clock;

ср

count = count;

start = data_strobe;

}

REG16x4 u2 {

we = write_coeff;

din = coeff_in;

dout = coeff_out;

}

IIR2

u3 {

cd

= reset;

= clock;

ср

cntrl = count;

din = data_in;

dout = data_out;

coeff = coeff_out;

}

. . .

```

### Conclusion (cont.)

#### What ALF is **NOT**

- \* A programming language

- \* A delay or power calculation language

- \* A tool-specific data representation for Simulation, Static timing etc.

- \* Design data file

- \* The library seen by the final customer

- \* Replacement for

- SDF

- SPF

- PDEF

- Verilog

- VHDĽ

- DCL

## Conclusion (cont.)

#### What ALF IS

- \* A unified source for consistent library data

- \* A prefered data entry from modeling engineers who are not programmers

- \* A file format forASIC functional, timing and power modeling for synthesis, analysis and test

- \* Library data file

- \* source, allowing the application to compile for efficiency

- \* complementary to other standards

- SDF

- SPF

- PDEF

- Verilog

- VHDL

- DCL

## Acknowledgements

### Contributors to ALF 1.0

| Wolfgang Roethig, PhD   | NEC, formerly LSI Logic        | ALF chairman     |  |

|-------------------------|--------------------------------|------------------|--|

| Amir Zarkesh, PhD       | TDT, formerly Viewlogic        | ALF co-chairman  |  |

| Mike Andrews            | Mentor Graphics                | ALF co-chairman  |  |

| Tim Ayres               | Viewlogic/Sunrise              |                  |  |

| Victor Berman           | VI / IEEE                      |                  |  |

| Dennis Brophy           | Mentor Graphics / IEEE DP      | С                |  |

| Renlin Chang            | Cadence                        |                  |  |

| Sanjay Churiwala        | Cadworx                        |                  |  |

| Jose De Castro          | Mentor Graphics                |                  |  |

| Timothy Ehrler          | VLSI Technology                |                  |  |

| Paul Foster             | Avant! Corporation             |                  |  |

| Vassilios Gerousis, PhD | Motorola / OVI Board           |                  |  |

| Kevin Grotjohn          | LSI Logic                      |                  |  |

| Johnson Chan Limqueco   | Ambit Design Systems           |                  |  |

| Ta-Yung Liu             | Avant! Corporation             |                  |  |

| Larry Rosenberg         | Cadence/VSI                    |                  |  |

| Hamid Rahmanian         | Mentor Graphics                |                  |  |

| Ambar Sarkar, PhD       | Viewlogic                      |                  |  |

| Itzhak Shapira          | Cadence                        |                  |  |

| Yatin Trivedi           | Seva Technologies              | Technical Editor |  |

| Devadas Varma           | Ambit Design Systems           |                  |  |

| David Wallace           | Mentor Graphics/Exemplar       |                  |  |

| Frank Weiler            | Avant! Corporation / OVI Board |                  |  |

|                         |                                |                  |  |

### Focus of Work Groups ALF work group Target audience: design & modeling engineers (software background useful) Explore ALF as modeling language for existing and new applications datapath compiler signal integrity formal verification Propose extensions to ALF for new applications Promote migration from internal ASIC library formats to ALF **OLA** work group Target audience: software engineers (design & modeling background useful) help developping the OLA framework help testing the OLA framework promote migration of tool-specific interface to OLA promote development of OLA-based applications

Our work groups are open - please join us!

| Contact People  |                                                                                                                |                     |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| ALF work group: | Wolfgang Roethig<br>NEC Electronics, Santa Clara CA<br>Tel. 408 588 5349<br>Email: Wolfgang_Roethig@el.nec.com | chairman            |  |  |  |  |

|                 | Mike Andrews<br>Mentor Graphics Corp., Wilsonville OR<br>Tel. 503 685 4879<br>Email: mike_andrews@mentorg.com  | co-chairman         |  |  |  |  |

| OLA work group: | Jay Abraham<br>Si2 Inc., Austin TX<br>Tel. 512 342 2244 x 52<br>Email:jabraham@si2.org                         | project coordinator |  |  |  |  |

| websites:       | http://www.ovi.org<br>http://www.si2.org                                                                       |                     |  |  |  |  |