# A standard for an Advanced Library Format (ALF) describing Integrated Circuit (IC) technology, cells, and blocks

This is an unapproved draft for an IEEE standard and subject to change

IEEE P1603 Draft 4

**April 17, 2002**

Copyright  $^{\circledR}$  2001, 2002, 2003 by IEEE. All rights reserved.

put in IEEE verbage

The following individuals contributed to the creation, editing, and review of this document

Wolfgang Roethig, Ph.D. wroethig@eda.org Official Reporter and WG Chair

Joe Daniels chippewea@aol.com Technical Editor

# Revision history:

| IEEE P1596 Draft 0 | August 19, 2001    |

|--------------------|--------------------|

| IEEE P1603 Draft 1 | September 17, 2001 |

| IEEE P1603 Draft 2 | November 12, 2001  |

| IEEE P1603 Draft 3 | January 4, 2002    |

# **Table of Contents**

| 1. | Intr | oduction   |                                                 | 1  |

|----|------|------------|-------------------------------------------------|----|

|    | 1 1  | Motiva     | tion                                            | 1  |

|    |      |            |                                                 |    |

|    |      |            | applications                                    |    |

|    |      | _          | applications                                    |    |

|    |      |            | ts of this standard                             |    |

|    | 1.5  | Conten     | ts of this standard                             |    |

| 2. | Ref  | erences    |                                                 | 7  |

| 3. | Def  | initions . |                                                 | 9  |

| 4. | Acr  | onyms a    | nd abbreviations                                | 11 |

| 5. | ALI  | F langua   | ge construction principles and overview         | 13 |

|    | 5 1  | AI.F m     | eta-language                                    | 13 |

|    |      |            | ries of ALF statements                          |    |

|    |      |            | c objects and library-specific objects          |    |

|    |      |            | ar statements and plural statements             |    |

|    |      |            | iation statement and assignment statement       |    |

|    |      |            | ation, arithmetic model, and related statements |    |

|    |      |            | ents for parser control                         |    |

|    |      |            | space and visibility of statements              |    |

| 6. | Lex  | ical rule: | S                                               | 25 |

|    | 6.1  | Charac     | ter set                                         | 25 |

|    |      |            | ent                                             |    |

|    |      |            | ter                                             |    |

|    |      |            | or                                              |    |

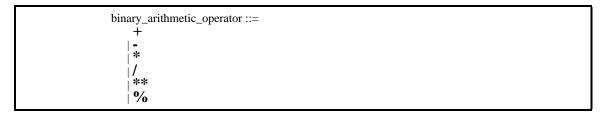

|    | 0.4  | 6.4.1      | Arithmetic operator                             |    |

|    |      |            | Boolean operator                                |    |

|    |      |            | Relational operator                             |    |

|    |      | 6.4.4      | Shift operator                                  |    |

|    |      |            | Event sequence operator                         |    |

|    |      |            | Meta operator                                   |    |

|    | 6.5  | Numbe      | ÷                                               | 31 |

|    | 0.5  | 1 valilioc | mbol                                            |    |

|    |      | -          | ral                                             |    |

|    |      |            | literal                                         |    |

|    |      |            | teral                                           |    |

|    |      | _          | string                                          |    |

|    |      | -          | er                                              |    |

|    | 0.11 |            | Non-escaped identifier                          |    |

|    |      |            | •                                               |    |

|    |      |            | Escaped identifier                              |    |

|    |      |            | Hierarchical identifier                         |    |

|    |      | 0.11.4     | THOTAL CHICAL INCHILITICI                       |    |

|    | 6.12 Keyword                                    |    |

|----|-------------------------------------------------|----|

|    | 6.13 Rules for whitespace usage                 |    |

|    | 6.14 Rules against parser ambiguity             | 37 |

| 7. | Auxiliary Syntax Rules                          | 39 |

|    | 7.1 All-purpose value                           | 39 |

|    | 7.2 Unit value                                  | 39 |

|    | 7.3 String                                      |    |

|    | 7.4 Arithmetic value                            |    |

|    | 7.5 Boolean value                               |    |

|    | 7.6 Edge value                                  |    |

|    | 7.7 Index value                                 |    |

|    | 7.8 Index                                       |    |

|    | 7.9 Pin variable and pin value                  |    |

|    | 7.10 Pin assignment                             |    |

|    | 7.11 Annotation                                 |    |

|    | 7.12 Annotation container                       |    |

|    | 7.13 ATTRIBUTE statement                        |    |

|    | 7.14 PROPERTY statement 7.15 INCLUDE statement  |    |

|    | 7.16 REVISION statement                         |    |

|    | 7.17 Generic object                             |    |

|    | 7.17 Generic object                             |    |

|    | 7.19 All purpose item                           |    |

| 8. | Generic objects and related statements          | 47 |

|    | 8.1 ALIAS declaration                           | 47 |

|    | 8.2 CONSTANT declaration                        |    |

|    | 8.3 CLASS declaration                           |    |

|    | 8.4 KEYWORD declaration                         | 48 |

|    | 8.5 Annotations for a KEYWORD                   | 49 |

|    | 8.5.1 VALUETYPE annotation                      | 49 |

|    | 8.5.2 VALUES annotation                         | 49 |

|    | 8.5.3 DEFAULT annotation                        |    |

|    | 8.5.4 CONTEXT annotation                        |    |

|    | 8.5.5 SI_MODEL annotation                       |    |

|    | 8.6 GROUP declaration                           |    |

|    | 8.7 TEMPLATE declaration                        |    |

|    | 8.8 TEMPLATE instantiation                      | 53 |

| 9. | Library-specific objects and related statements | 57 |

|    | 9.1 LIBRARY and SUBLIBRARY declaration          | 57 |

|    | 9.2 Annotations for LIBRARY and SUBLIBRARY      | 57 |

|    | 9.2.1 INFORMATION annotation container          |    |

|    | 9.3 CELL declaration                            | 59 |

|    | 9.4 CELL instantiation                          |    |

|    | 9.5 Annotations for a CELL                      |    |

|    | 9.5.1 CELLTYPE annotation                       |    |

|    | 9.5.2 SWAP_CLASS annotation                     |    |

|    | 9.5.3 RESTRICT_CLASS annotation                 |    |

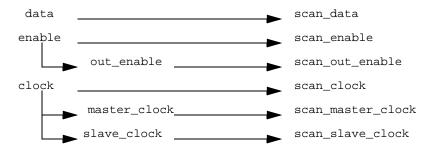

|    | 9.5.4 SCAN_TYPE annotation                      | 61 |

|      | 9.5.5  | SCAN_USAGE annotation                 |    |

|------|--------|---------------------------------------|----|

|      | 9.5.6  | BUFFERTYPE annotation                 | 62 |

|      | 9.5.7  | DRIVERTYPE annotation                 | 63 |

|      | 9.5.8  | PARALLEL_DRIVE annotation             | 64 |

|      | 9.5.9  | PLACEMENT_TYPE annotation             | 64 |

|      | 9.5.10 | SITE reference annotation             | 64 |

| 9.6  | ATTR   | IBUTE values for a CELL               | 64 |

| 9.7  | PIN de | eclaration                            | 66 |

| 9.8  | PINGI  | ROUP declaration                      | 68 |

| 9.9  | Annota | ations for a PIN and a PINGROUP       | 68 |

|      |        | VIEW annotation                       |    |

|      | 9.9.2  | PINTYPE annotation.                   | 69 |

|      | 9.9.3  | DIRECTION annotation                  | 69 |

|      | 9.9.4  | SIGNALTYPE annotation                 |    |

|      | 9.9.5  | ACTION annotation                     |    |

|      | 9.9.6  | POLARITY annotation                   |    |

|      | 9.9.7  | DATATYPE annotation                   |    |

|      | 9.9.8  | INITIAL_VALUE annotation              |    |

|      | 9.9.9  | SCAN_POSITION annotation              |    |

|      | 9.9.10 | STUCK annotation                      |    |

|      | 9.9.11 |                                       |    |

|      | 9.9.12 | SIGNAL CLASS                          |    |

|      |        | SUPPLY CLASS                          |    |

|      |        | DRIVETYPE annotation                  |    |

|      |        | SCOPE annotation.                     |    |

|      |        | CONNECT CLASS annotation.             |    |

|      |        | SIDE annotation                       |    |

|      |        | ROW and COLUMN annotation             |    |

|      |        | ROUTING TYPE annotation               |    |

|      |        | PULL annotation                       |    |

| 9.10 |        | IBUTE values for a PIN and a PINGROUP |    |

|      |        | ITIVE declaration                     |    |

|      |        | declaration                           |    |

|      |        | Annotations for a WIRE                |    |

|      |        | SELECT CLASS annotation               |    |

| 9.1  |        | E declaration.                        |    |

| ,    |        | NODETYPE annotation                   |    |

|      |        | NODE_CLASS annotation.                |    |

| 9.14 |        | OR declaration                        |    |

|      |        | ations for VECTOR                     |    |

| ···· |        | PURPOSE annotation                    |    |

|      |        | OPERATION annotation                  |    |

|      |        | LABEL annotation                      |    |

|      |        | EXISTENCE_CONDITION annotation        |    |

|      |        | EXISTENCE_CLASS annotation            |    |

|      |        | CHARACTERIZATION CONDITION annotation |    |

|      |        | CHARACTERIZATION_VECTOR annotation    |    |

|      |        | CHARACTERIZATION_CLASS annotation     |    |

| 9 1  |        | ER declaration                        |    |

|      |        | ations for LAYER                      |    |

| J.1  |        | LAYERTYPE annotation                  |    |

|      |        | PITCH annotation                      |    |

|      |        | PREFERENCE annotation                 |    |

| 0.1  |        | enderation                            |    |

|     | 9.19 VIA ir | nstantiation                           | 91  |

|-----|-------------|----------------------------------------|-----|

|     | 9.20 Annota | ations for a VIA                       | 91  |

|     | 9.20.1      | VIATYPE annotation                     | 91  |

|     | 9.21 RULE   | declaration                            | 92  |

|     | 9.22 ANTE   | ENNA declaration                       | 92  |

|     | 9.23 BLOC   | KAGE declaration                       | 93  |

|     | 9.24 PORT   | declaration                            | 93  |

|     | 9.25 Annota | ations for PORT                        | 93  |

|     | 9.25.1      | PORT_VIEW annotation                   | 93  |

|     |             | declaration                            |     |

|     | 9.27 Annota | ations for SITE                        | 94  |

|     | 9.27.1      | ORIENTATION_CLASS                      | 94  |

|     |             | SYMMETRY_CLASS                         |     |

|     |             | Y declaration                          |     |

|     |             | ations for ARRAY                       |     |

|     |             | ARRAYTYPE annotation                   |     |

|     |             | ERN declaration                        |     |

|     |             | ations for PATTERN                     |     |

|     |             | SHAPE annotation                       |     |

|     |             | VERTEX annotation                      |     |

|     |             | LAYER reference annotation.            |     |

|     |             | etric model                            |     |

|     |             | ined geometric models using TEMPLATE   |     |

|     |             | etric transformation                   |     |

|     |             | VORK statement                         |     |

|     |             | TION statement                         |     |

|     |             | statement                              |     |

|     |             | VIOR statement                         |     |

|     |             |                                        |     |

|     |             | CTURE statement                        |     |

|     |             | ETABLE statement                       |     |

|     |             | SCAN_CELL statement                    |     |

|     | 9.42 RANC   | GE statement                           | 110 |

| 10. | Constructs  | for modeling of digital behavior       | 111 |

|     | 10 1 Variah | ole declarations                       | 111 |

|     |             | an value system                        |     |

|     |             | inational functions                    |     |

|     |             | Combinational logic                    |     |

|     |             | Boolean operators on scalars           |     |

|     |             | Boolean operators on words             |     |

|     |             | Operator priorities                    |     |

|     |             | Datatype mapping                       |     |

|     |             | Rules for combinational functions      |     |

|     |             | Concurrency in combinational functions |     |

|     |             | ntial functions                        |     |

|     |             | Level-sensitive sequential logic       |     |

|     |             | Edge-sensitive sequential logic        |     |

|     |             | Unary operators for vector expressions |     |

|     |             | Basic rules for sequential functions   |     |

|     |             |                                        |     |

|     |             | Concurrency in sequential functions    |     |

|     |             | Initial values for logic variables     |     |

|     |             | r-order sequential functions           |     |

|     | 10.3.1      | Vector-sensitive sequential logic      | 128 |

|     |             | Canonical binary operators for vector expressions    |     |

|-----|-------------|------------------------------------------------------|-----|

|     | 10.5.3      | Complex binary operators for vector expressions      | 130 |

|     | 10.5.4      | Extension to N operands                              | 131 |

|     | 10.5.5      | Operators for conditional vector expressions         | 133 |

|     | 10.5.6      | Operators for sequential logic                       | 134 |

|     | 10.5.7      | Operator priorities                                  | 134 |

|     | 10.5.8      | Using PINs in VECTORs                                | 135 |

|     | 10.6 Model  | ling with vector expressions                         | 135 |

|     | 10.6.1      | Event reports                                        | 136 |

|     | 10.6.2      | Event sequences                                      | 137 |

|     | 10.6.3      | Scope and content of event sequences                 | 138 |

|     | 10.6.4      | Alternative event sequences                          | 140 |

|     |             | Symbolic edge operators                              |     |

|     |             | Non-events                                           |     |

|     |             | Compact and verbose event sequences                  |     |

|     |             | Unspecified simultaneous events within scope         |     |

|     |             | Simultaneous event sequences                         |     |

|     |             | ) Implicit local variables                           |     |

|     |             | 1 Conditional event sequences                        |     |

|     |             | 2 Alternative conditional event sequences            |     |

|     |             | 3 Change of scope within a vector expression         |     |

|     |             | 4 Sequences of conditional event sequences           |     |

|     |             | 5 Incompletely specified event sequences             |     |

|     |             | 6 How to determine well-specified vector expressions |     |

|     |             | an expression language                               |     |

|     |             | r expression language                                |     |

|     |             | ol expression semantics                              |     |

|     | 10.5 Contro | or expression semantics                              | 100 |

| 11. | Constructs  | for electrical and physical modeling                 | 163 |

|     | Constructs  | Tor erecureur und prij sieur modernig                |     |

|     | 11.1 Arithn | netic expression                                     | 163 |

|     |             | netic model                                          |     |

|     |             | DER, TABLE, and EQUATION                             |     |

|     |             | HEADER statement                                     |     |

|     |             | TABLE statement                                      |     |

|     |             | EQUATION statement                                   |     |

|     |             | nents related to arithmetic model                    |     |

|     |             | Model qualifier                                      |     |

|     |             | Auxiliary arithmetic model                           |     |

|     |             | Arithmetic submodel                                  |     |

|     |             | MIN-MAX statement                                    |     |

|     |             | MIN-TYP-MAX statement                                |     |

|     |             | Trivial MIN-MAX statement                            |     |

|     |             | Arithmetic model container                           |     |

|     |             | LIMIT statement                                      |     |

|     |             | Event reference statement                            |     |

|     |             |                                                      |     |

|     |             | FROM and TO statements                               |     |

|     |             | 1 EARLY and LATE statements                          |     |

|     |             | 2 VIOLATION statement                                |     |

|     |             | ations for arithmetic models                         |     |

|     |             | UNIT annotation.                                     |     |

|     |             | CALCULATION annotation.                              |     |

|     |             | INTERPOLATION annotation                             |     |

|     | 11.5.4      | DEFAULT annotation                                   |     |

| 11.6 TIME                                                              |     |

|------------------------------------------------------------------------|-----|

| 11.6.1 TIME in context of a VECTOR declaration                         |     |

| 11.6.2 TIME in context of a HEADER statement                           |     |

| 11.6.3 TIME as auxiliary arithmetic model                              |     |

| 11.7 FREQUENCY                                                         |     |

| 11.7.1 FREQUENCY in context of a VECTOR declaration                    |     |

| 11.7.2 FREQUENCY in context of a HEADER statement                      |     |

| 11.7.3 FREQUENCY as auxiliary arithmetic model                         |     |

| 11.8 DELAY                                                             |     |

| 11.8.1 DELAY in context of a VECTOR declaration                        |     |

| 11.8.2 DELAY in context of a library-specific object declaration       |     |

| 11.9 RETAIN                                                            |     |

| 11.10SLEWRATE                                                          |     |

| 11.10.1 SLEWRATE in context of a VECTOR declaration                    |     |

| 11.10.2 SLEWRATE in context of a PIN declaration                       |     |

| 11.10.3 SLEWRATE in context of a library-specific object declaration   |     |

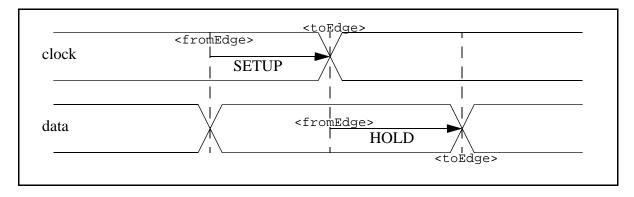

| 11.11SETUP and HOLD                                                    |     |

| 11.11.1 SETUP in context of a VECTOR declaration                       |     |

| 11.11.2 HOLD in context of a VECTOR declaration                        |     |

| 11.11.3 SETUP and HOLD in context of the same VECTOR declaration       |     |

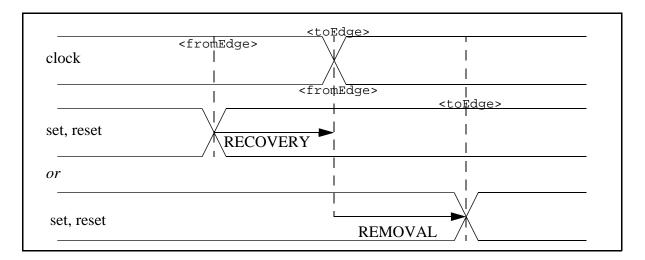

| 11.12RECOVERY and REMOVAL                                              |     |

| 11.12.1 RECOVERY in context of a VECTOR declaration                    |     |

| 11.12.2 REMOVAL in context of a VECTOR declaration                     |     |

| 11.12.3 RECOVERY and REMOVAL in context of the same VECTOR declaration |     |

| 11.13NOCHANGE and ILLEGAL                                              |     |

| 11.13.1 NOCHANGE in context of a VECTOR declaration                    |     |

| 11.13.2 ILLEGAL in context of a VECTOR declaration                     |     |

| 11.14SKEW                                                              |     |

| 11.14.1 SKEW involving two signals                                     |     |

| 11.14.2 SKEW involving multiple signals                                | 183 |

| 11.15PULSEWIDTH                                                        |     |

| 11.15.1 PULSEWIDTH in context of a VECTOR declaration                  |     |

| 11.15.2 PULSEWIDTH in context of a PIN declaration                     |     |

| 11.15.3 PULSEWIDTH in context of a library-specific object declaration |     |

| 11.16PERIOD                                                            |     |

| 11.17JITTER                                                            |     |

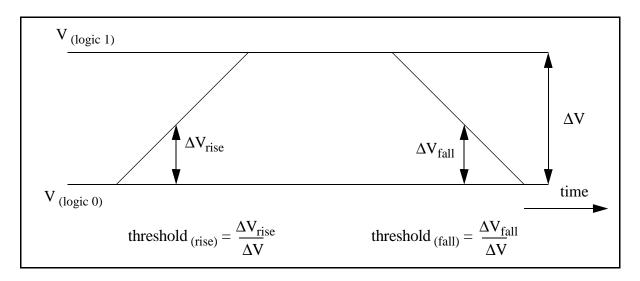

| 11.18THRESHOLD                                                         |     |

| 11.19Annotations related to timing data                                |     |

| 11.19.1 PIN reference annotation                                       |     |

| 11.20PROCESS                                                           |     |

| 11.21DERATE_CASE                                                       |     |

| 11.22TEMPERATURE                                                       |     |

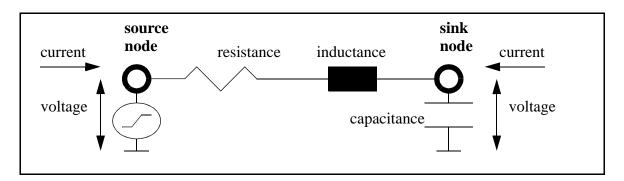

| 11.23PIN-related arithmetic models for electrical data                 |     |

| 11.23.1 CAPACITANCE, RESISTANCE, and INDUCTANCE                        |     |

| 11.23.2 VOLTAGE and CURRENT                                            | 180 |

| 11.23.3 Context-specific semantics                                     |     |

| 11.24POWER and ENERGY                                                  |     |

| 11.25FLUX and FLUENCE                                                  |     |

| 11.26DRIVE_STRENGTH                                                    |     |

| 11.27SWITCHING_BITS                                                    |     |

| 11.28NOISE and NOISE MARGIN                                            |     |

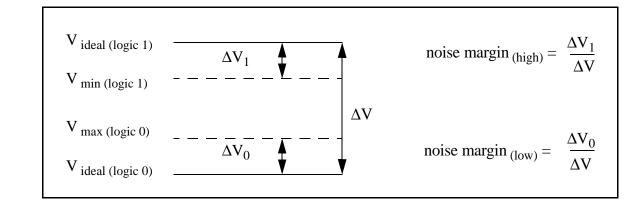

| 11.28.1 NOISE MARGIN                                                   |     |

| 11.28.2 NOISE WARGIN                                                   |     |

| 11.29Annotations and statements related to electrical models | 196   |

|--------------------------------------------------------------|-------|

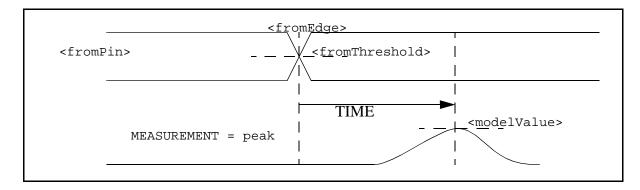

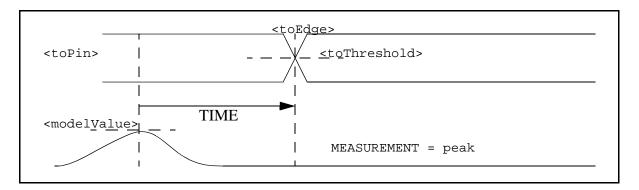

| 11.29.1 MEASUREMENT annotation                               | 196   |

| 11.29.2 TIME to peak measurement                             | 198   |

| 11.30CONNECTIVITY                                            | 199   |

| 11.31SIZE                                                    | 200   |

| 11.32AREA                                                    | 200   |

| 11.33WIDTH                                                   | 201   |

| 11.34HEIGHT                                                  | 201   |

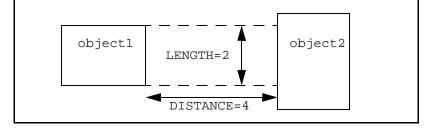

| 11.35LENGTH                                                  | 201   |

| 11.36DISTANCE                                                | 201   |

| 11.37OVERHANG                                                | 202   |

| 11.38PERIMETER                                               | 202   |

| 11.39EXTENSION                                               | 202   |

| 11.40THICKNESS                                               | 202   |

| 11.41Annotations for physical models                         | 203   |

| 11.41.1 CONNECT_RULE annotation                              | 203   |

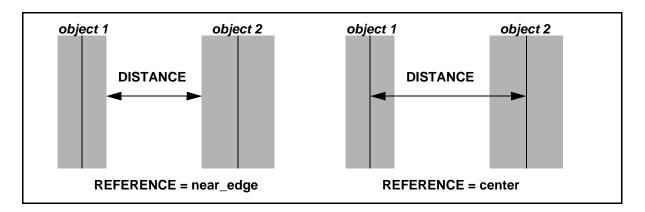

| 11.41.2 BETWEEN annotation                                   | 203   |

| 11.41.3 DISTANCE-MEASUREMENT annotation                      | 204   |

| 11.41.4 REFERENCE annotation container                       | 205   |

| 11.41.5 ANTENNA reference annotation                         | 205   |

| 11.41.6 PATTERN reference annotation                         | 206   |

| 11.42Arithmetic submodels for timing and electrical data     | 207   |

| 11.43Arithmetic submodels for physical data                  | 207   |

| (informative)Syntax rule summary                             | 209   |

| •                                                            |       |

| A.1 Lexical definitions                                      | 209   |

| A.2 Auxiliary definitions                                    | 211   |

| A.3 Generic definitions                                      | 213   |

| A.4 Library definitions                                      | 214   |

| A.5 Control definitions                                      | 221   |

| A.6 Arithmetic definitions                                   | 222   |

| (informative)Pibliography                                    | 225   |

| UNIOTTI UNIO INTO OTTO DIV                                   | 7)7)5 |

# List of Figures

| Figure 1—ALF and its target applications                                               | 4   |

|----------------------------------------------------------------------------------------|-----|

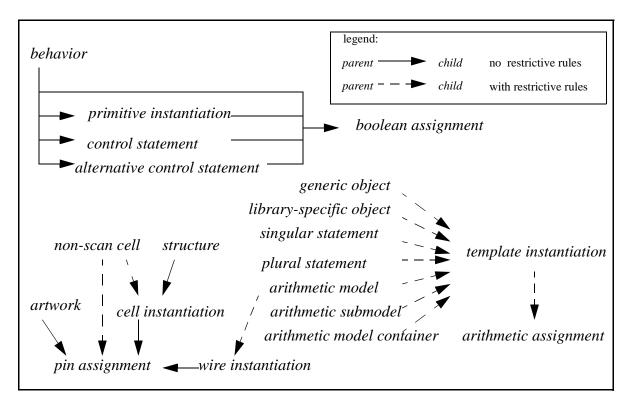

| Figure 2—Parent/child relationship between ALF statements                              | 16  |

| Figure 3—Parent/child relationship amongst library-specific objects                    | 18  |

| Figure 4—Parent/child relationship involving singular statements and plural statements | 20  |

| Figure 5—Parent/child relationship involving instantiation and assignment statements   | 21  |

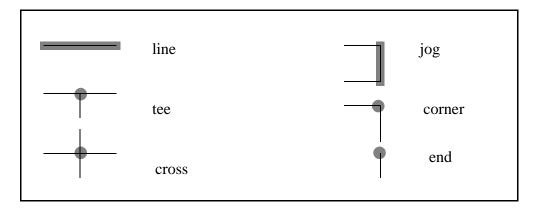

| Figure 6—Routing layer shapes                                                          | 97  |

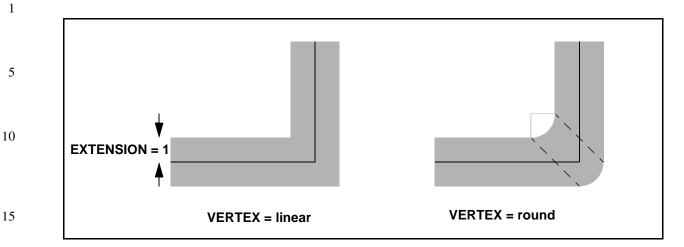

| Figure 7—Illustration of VERTEX annotation                                             | 98  |

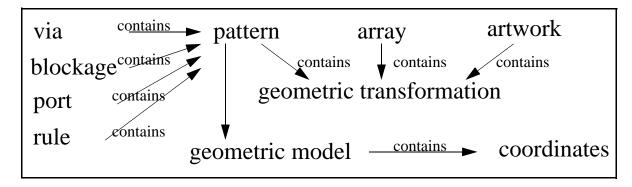

| Figure 8—Geometric model and its context                                               | 98  |

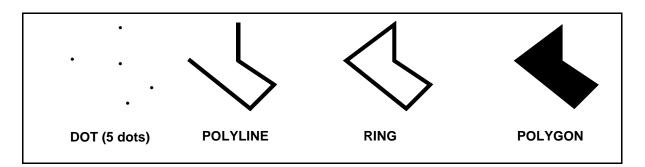

| Figure 9—Illustration of geometric models                                              | 99  |

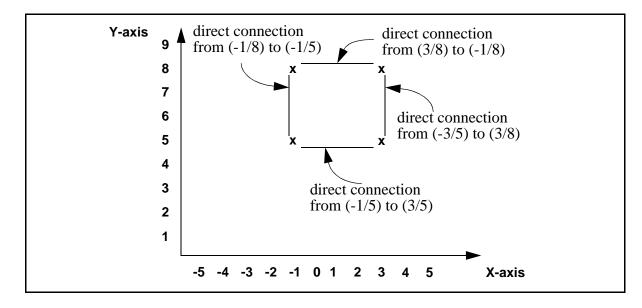

| Figure 10—Illustration of direct point-to-point connection                             | 100 |

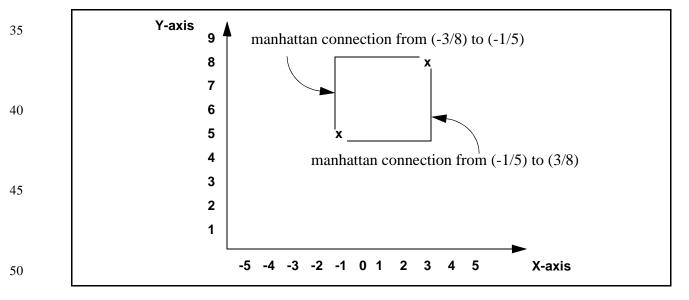

| Figure 11—Illustration of manhattan point-to-point connection                          | 100 |

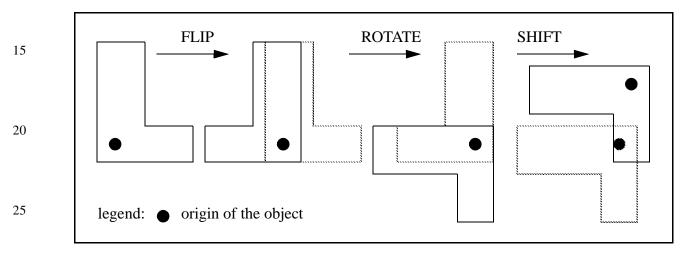

| Figure 12—Illustration of FLIP, ROTATE, and SHIFT                                      | 104 |

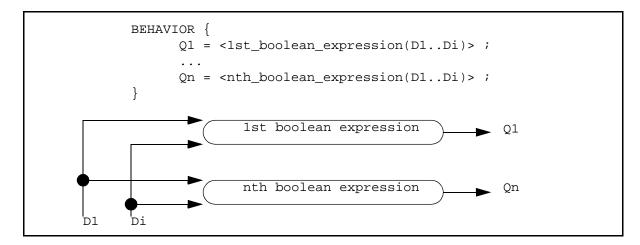

| Figure 13—Concurrency for combinational logic                                          | 119 |

| Figure 14—Model of a flip-flop with asynchronous clear in ALF                          | 121 |

| Figure 15—Model of a flip-flop with asynchronous clear in Verilog                      | 121 |

| Figure 16—Model of a flip-flop with asynchronous clear in VHDL                         | 121 |

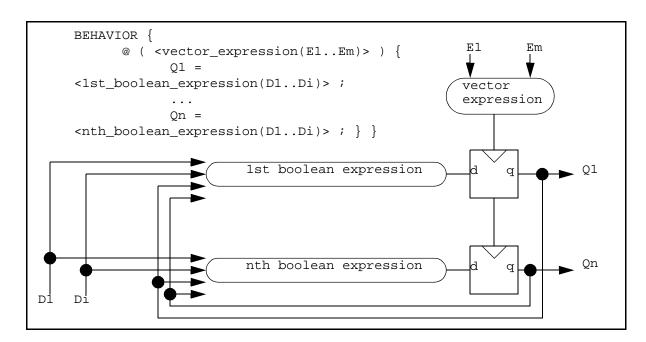

| Figure 17—Concurrency for edge-sensitive sequential logic                              | 126 |

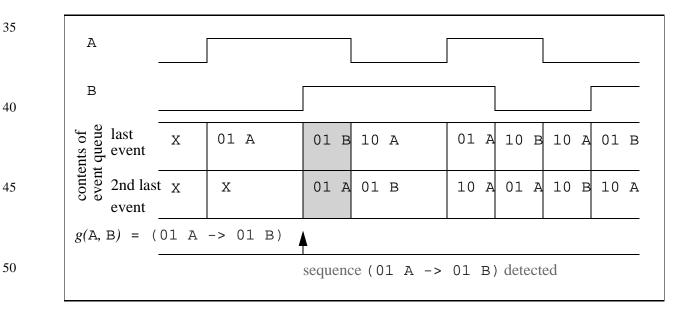

| Figure 18—Example of event sequence detection function                                 | 128 |

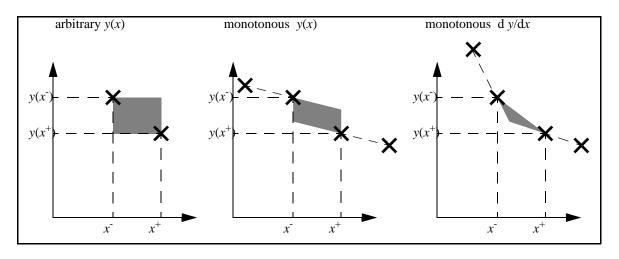

| Figure 19—Bounding regions for y(x) with INTERPOLATION=fit                             |     |

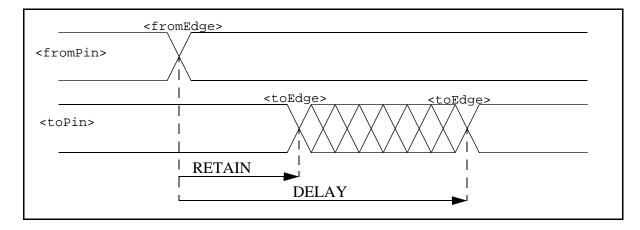

| Figure 20—RETAIN and DELAY                                                             |     |

| Figure 21—SETUP and HOLD                                                               |     |

| Figure 22—RECOVERY and REMOVAL                                                         |     |

| Figure 23—THRESHOLD measurement definition                                             | 185 |

| Figure 24—General representation of electrical models around a pin                     | 189 |

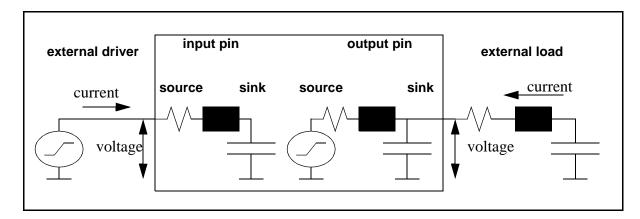

| Figure 25—Electrical models associated with input and output pins                      | 191 |

| Figure 26—Definition of noise margin                                                   |     |

| Figure 27—Mathematical definitions for MEASUREMENT annotations                         | 197 |

| Figure 28—Illustration of time to peak using FROM statement                            |     |

| Figure 29—Illustration of time to peak using TO statement                              |     |

| Figure 30—Illustration of LENGTH and DISTANCE                                          |     |

| Figure 31—Illustration of REFERENCE for DISTANCE                                       | 205 |

# **List of Tables**

| Table 1—Target applications and models supported by ALF                      | 2  |

|------------------------------------------------------------------------------|----|

| Table 2—Categories of ALF statements                                         | 15 |

| Table 3—Generic objects                                                      | 17 |

| Table 4—Library-specific objects                                             | 17 |

| Table 5—Singular statements                                                  | 19 |

| Table 6—Plural statements                                                    | 19 |

| Table 7—Instantiation statements                                             | 20 |

| Table 8—Assignment statements                                                | 21 |

| Table 9—Other categories of ALF statements                                   |    |

| Table 10—Annotations and annotation containers with generic keyword          | 22 |

| Table 11—Keywords related to arithmetic model                                | 22 |

| Table 12—Statements for ALF parser control                                   | 23 |

| Table 13—List of whitespace characters                                       |    |

| Table 14—List of special characters                                          |    |

| Table 15—List arithmetic operators                                           | 28 |

| Table 16—List of boolean operators                                           | 29 |

| Table 17—List of relational operators                                        | 29 |

| Table 18—List of shift operators                                             | 30 |

| Table 19—List of event sequence operators                                    | 30 |

| Table 20—List of meta operators                                              | 30 |

| Table 21—UNIT symbol                                                         | 32 |

| Table 22—Character symbols within a quoted string                            | 34 |

| Table 23—Legal string values within the REVISION statement                   | 44 |

| Table 24—Syntax item identifier                                              |    |

| Table 25—VALUETYPE annotation                                                | 49 |

| Table 26—Annotations within an INFORMATION statement                         | 58 |

| Table 27—CELLTYPE annotation values                                          | 60 |

| Table 28—Predefined values for RESTRICT_CLASS                                | 61 |

| Table 29—SCAN_TYPE annotations for a CELL object                             | 62 |

| Table 30—SCAN_USAGE annotations for a CELL object                            | 62 |

| Table 31—BUFFERTYPE annotations for a CELL object                            | 63 |

| Table 32—DRIVERTYPE annotations for a CELL object                            |    |

| Table 33—Attribute values for a CELL with CELLTYPE=memory                    | 65 |

| Table 34—Attributes within a CELL with CELLTYPE=block                        | 65 |

| Table 35—Attributes within a CELL with CELLTYPE=core                         | 66 |

| Table 36—Attributes within a CELL with CELLTYPE=special                      | 66 |

| Table 37—VIEW annotations for a PIN object                                   | 69 |

| Table 38—PINTYPE annotations for a PIN object                                | 69 |

| Table 39—DIRECTION annotations for a PIN object                              | 70 |

| Table 40—DIRECTION in combination with PINTYPE                               |    |

| Table 41—Fundamental SIGNALTYPE annotations for a PIN object                 | 71 |

| Table 42—Composite SIGNALTYPE annotations for a PIN object                   |    |

| Table 43—ACTION annotations for a PIN object                                 | 73 |

| Table 44—ACTION applicable in conjunction with fundamental SIGNALTYPE values | 73 |

| Table 45– | -POLARITY annotations for a PIN                                        | 74  |

|-----------|------------------------------------------------------------------------|-----|

| Table 46– | -POLARITY applicable in conjunction with fundamental SIGNALTYPE values | 74  |

| Table 47– | DATATYPE annotations for a PIN object                                  | 75  |

|           | STUCK annotations for a PIN object                                     |     |

|           | -DRIVETYPE annotations for a PIN object                                |     |

|           | SCOPE annotations for a PIN object                                     |     |

|           | SIDE annotations for a PIN object                                      |     |

|           | -PULL annotations for a PIN object                                     |     |

|           | -Attributes within a PIN object                                        |     |

|           | -Attributes for pins of a memory                                       |     |

|           | -Attributes for pins representing double-rail signals                  |     |

|           | PIN or PINGROUP attributes for memory BIST                             |     |

|           | NODETYPE annotation values                                             |     |

|           | OPERATION annotation values                                            |     |

|           | -LAYERTYPE annotation values                                           |     |

|           | VIATYPE annotation values                                              |     |

|           | -PORT_VIEW annotation values                                           |     |

|           | -Geometric model identifiers                                           |     |

|           | Single bit constants                                                   |     |

|           | -Single on constants  -Mapping between octal base and binary base      |     |

|           | -Mapping between hexadecimal base, octal base, and binary base         |     |

|           | -Unary boolean operators                                               |     |

|           | -Binary boolean operators                                              |     |

|           | -Binary operator                                                       |     |

|           | Unary reduction operators                                              |     |

|           | -Unary bitwise operators                                               |     |

|           | ·                                                                      |     |

|           | —Binary bitwise operators                                              |     |

|           | Binary reduction operators                                             |     |

|           | -Binary operators                                                      |     |

|           | -Case comparison operators                                             |     |

|           | -Unary vector operators on bits                                        |     |

|           | -Unary vector operators on bits or words                               |     |

|           | -Canonical binary vector operators                                     |     |

|           | -Complex binary vector operators                                       |     |

|           | Operators for conditional vector expressions                           |     |

|           | Operators for sequential logic                                         |     |

|           | -Unary arithmetic operators                                            |     |

|           | -Binary arithmetic operators                                           |     |

|           | -Macro arithmetic operators                                            |     |

|           |                                                                        |     |

|           |                                                                        |     |

|           | Predefined process names                                               |     |

|           | Predefined derating cases                                              |     |

|           | –Direct association of models with a PIN                               |     |

|           | -External association of models with a PIN                             |     |

|           | -MEASUREMENT annotation                                                |     |

|           | Semantic interpretation of MEASUREMENT, TIME, or FREQUENCY             |     |

|           | -Arguments for connectivity                                            |     |

|           | Boolean literals in non-interpolateable tables                         |     |

| Table 94- | -CONNECT RULE annotation                                               | 203 |

| Table 95—Implications between connect rules                      | 203 |

|------------------------------------------------------------------|-----|

| Table 96—Submodels applicable for timing and electrical modeling | 207 |

| Table 97—Submodels applicable for physical modeling              | 207 |

# IEEE Standard for an Advanced Library Format (ALF) describing Integrated Circuit (IC) technology, cells, and blocks

1. Introduction 25

\*\*Add a lead-in OR change this to parallel an IEEE intro section\*\*

#### 1.1 Motivation

Designing digital integrated circuits has become an increasingly complex process. More functions get integrated into a single chip, yet the cycle time of electronic products and technologies has become considerably shorter. It would be impossible to successfully design a chip of today's complexity within the time-to-market constraints without extensive use of EDA tools, which have become an integral part of the complex design flow. The efficiency of the tools and the reliability of the results for simulation, synthesis, timing and power analysis, layout and extraction rely significantly on the quality of available information about the cells in the technology library.

New challenges in the design flow, especially signal integrity, arise as the traditional tools and design flows hit their limits of capability in processing complex designs. As a result, new tools emerge, and libraries are needed in order to make them work properly. Library creation (generation) itself has become a very complex process and the choice or rejection of a particular application (tool) is often constrained or dictated by the availability of a library for that application. The library constraint can prevent designers from choosing an application program that is best suited for meeting specific design challenges. Similar considerations can inhibit the development and productization of such an application program altogether. As a result, competitiveness and innovation of the whole electronic industry can stagnate.

In order to remove these constraints, an industry-wide standard for library formats, the Advanced Library Format (ALF), is proposed. It enables the EDA industry to develop innovative products and ASIC designers to choose the best product without library format constraints. Since ASIC vendors have to support a multitude of libraries according to the preferences of their customers, a common standard library is expected to significantly reduce the library development cycle and facilitate the deployment of new technologies sooner.

1

5

10

15

20

30

35

40

45

#### 1.2 Goals

1

5

10

15

20

25

30

35

40

45

50

55

The basic goals of the proposed library standard are

- simplicity library creation process needs to be easy to understand and not become a cumbersome process only known by a few experts.

- *generality* tools of any level of sophistication need to be able to retrieve necessary information from the library.

- expandability this needs to be done for early adoption and future enhancement possibilities.

- flexibility the choice of keeping information in one library or in separate libraries needs to be in the hand

of the user not the standard.

- efficiency the complexity of the design information requires the process of retrieving information from the library does not become a bottleneck. The right trade-off between compactness and verbosity needs to be established.

- ease of implementation backward compatibility with existing libraries shall be provided and translation to the new library needs to be an easy task.

- *conciseness* unambiguous description and accuracy of contents shall be detailed.

- acceptance there needs to be a preference for the new standard library over existing libraries.

## 1.3 Target applications

The fundamental purpose of ALF is to serve as the primary database for all third-party applications of ASIC cells. In other words, it is an elaborate and formalized version of the *databook*.

In the early days, databooks provided all the information a designer needed for choosing a cell in a particular application: Logic symbols, schematics, and a truth table provided the functional specification for simple cells. For more complex blocks, the name of the cell (e.g., asynchronous ROM, synchronous 2-port RAM, or 4-bit synchronous up-down counters) and timing diagrams conveyed the functional information. The performance characteristics of each cell were provided by the loading characteristics, delay and timing constraints, and some information about DC and AC power consumption. The designers chose the cell type according to the functionality, estimated the performance of the design, and eventually re-implemented it in an optimized way as necessary to meet performance constraints.

Design automation enabled tremendous progress in efficiency, productivity, and the ability to deal with complexity, yet it did not change the fundamental requirements for ASIC design. Therefore, ALF needs to provide models with *functional* information and *performance* information, primarily including timing and power. Signal integrity characteristics, such as noise margin can also be included under performance category. Such information is typically found in any databook for analog cells. At deep sub-micron levels, digital cells behave similar to analog cells as electronic devices bound by physical laws and therefore are not infinitely robust against noise.

Table 1 shows a list of applications used in ASIC design flow and their relationship to ALF.

NOTE — ALF covers *library* data, whereas *design* data needs to be provided in other formats.

Table 1—Target applications and models supported by ALF

| Application     | Functional model | Performance model | Physical model   |

|-----------------|------------------|-------------------|------------------|

| Simulation      | Derived from ALF | N/A               | N/A              |

| Synthesis       | Supported by ALF | Supported by ALF  | Supported by ALF |

| Design for test | Supported by ALF | N/A               | N/A              |

Table 1—Target applications and models supported by ALF (Continued)

| Application      | Functional model | Performance model | Physical model   |

|------------------|------------------|-------------------|------------------|

| Design planning  | Supported by ALF | Supported by ALF  | Supported by ALF |

| Timing analysis  | N/A              | Supported by ALF  | N/A              |

| Power analysis   | N/A              | Supported by ALF  | N/A              |

| Signal integrity | N/A              | Supported by ALF  | N/A              |

| Layout           | N/A              | N/A               | Supported by ALF |

Historically, a functional model was virtually identical to a simulation model. A functional gate-level model was used by the proprietary simulator of the ASIC company and it was easy to lump it together with a rudimentary timing model. Timing analysis was done through dynamic functional simulation. However, with the advanced level of sophistication of both functional simulation and timing analysis, this is no longer the case. The capabilities of the functional simulators have evolved far beyond the gate-level and timing analysis has been decoupled from simulation.

RTL design planning is an emerging application type aiming to produce "virtual prototypes" of complex for system-on-chip (SOC) designs. RTL design planning is thought of as a combination of some or all of RTL floorplanning and global routing, timing budgeting, power estimation, and functional verification, as well as analysis of signal integrity, EMI, and thermal effects. The library components for RTL design planning range from simple logic gates to parameterizeable macro-functions, such as memories, logic building blocks, and cores.

From the point of view of library requirements, applications involved in RTL design planning need functional, performance, and physical data. The functional aspect of design planning includes RTL simulation and formal verification. The performance aspect covers timing and power as primary issues, while signal integrity, EMI, and thermal effects are emerging issues. The physical aspect is floorplanning. As stated previously, the functional and performance models of components can be described in ALF.

ALF also covers the requirements for physical data, including layout. This is important for the new generation of tools, where logical design merges with physical design. Also, all design steps involve optimization for timing, power, signal integrity, i.e. electrical correctness and physical correctness. EDA tools need to be knowledgeable about an increasing number of design aspects. For example, a place and route tool needs to consider congestion as well as timing, crosstalk, electromigration, antenna rules etc. Therefore it is a logical step to combine the functional, electrical and physical models needed by such a tool in a unified library.

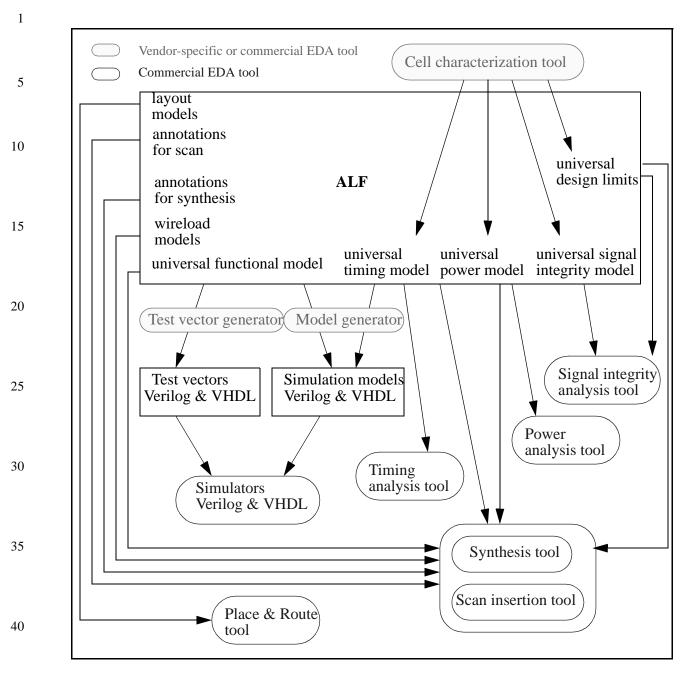

Figure 1 shows how ALF provides information to various design tools.

Figure 1—ALF and its target applications

The worldwide accepted standards for hardware description and simulation are VHDL and Verilog. Both languages have a wide scope of describing the design at various levels of abstraction: behavioral, functional, synthesizable RTL, and gate level. There are many ways to describe gate-level functions. The existing simulators are implemented in such a way that some constructs are more efficient for simulation run time than others. Also, how the simulation model handles timing constraints is a trade-off between efficiency and accuracy. Developing efficient simulation models which are functionally reliable (i.e., pessimistic for detecting timing constraint violation) is a major development effort for ASIC companies.

Hence, the use of a particular VHDL or Verilog simulation model as primary source of functional description of a cell is not very practical. Moreover, the existence of two simulation standards makes it difficult to pick one as a

45

50

reference with respect to the other. The purpose of a generic functional model is to serve as an absolute reference for all applications that require functional information. Applications such as synthesis, which need functional information merely for recognizing and choosing cell types, can use the generic functional model directly. For other applications, such as simulation and test, the generic functional model enables automated simulation model and test vector generation and verification, which has a tremendous benefit for the ASIC industry.

With progress of technology, the set of physical constraints under which the design functions have increased dramatically, along with the cost constraints. Therefore, the requirements for detailed characterization and analysis of those constraints, especially timing and power in deep submicron design, are now much more sophisticated. Only a subset of the increasing amount of characterization data appears in today's databooks.

ALF provides a generic format for all type of characterization data, without restriction to state-of-the art timing models. Power models are the most immediate extension and they have been the starter and primary driver for ALF.

Detailed timing and power characterization needs to take into account the *mode of operation* of the ASIC cell, which is related to the functionality. ALF introduces the concept of *vector-based modeling*, which is a generalization and a superset of today's timing and power modeling approaches. All existing timing and power analysis applications can retrieve the necessary model information from ALF.

#### 1.4 Conventions

The syntax for description of lexical and syntax rules uses the following conventions.

\*\*Consider using the BNF nomenclature from IEEE 1481-1999\*\*

The syntax for explanation of semantics of expressions uses the following conventions.

```

=== left side and right side expressions are equivalent <item> a placeholder for an item in regular syntax

```

#### 1.5 Contents of this standard

The organization of the remainder of this standard is

- Clause 2 (References) provides references to other applicable standards that are assumed or required for ALF.

- Clause 3 (Definitions) defines terms used throughout the different specifications contained in this standard.

- Clause 4 (Acronyms and abbreviations) defines the acronyms used in this standard.

- Clause 6 (Lexical rules) specifies the lexical rules.

- Clause 5 (ALF language construction principles) defines the language construction principles.

- Clause 7 (Auxiliary Syntax Rules) defines syntax and semantics of auxiliary items used in this standard.

55

1

5

10

15

20

25

30

35

40

45

- 1 Clause 8 (Generic objects and related statements) defines syntax and semantics of generic objects used in this standard.

- Clause 9 (Library-specific objects and related statements) defines syntax and semantics of library-specific objects used in this standard.

- Clause 10 (Constructs for modeling of digital behavior) defines syntax and semantics of the control expression language used in this standard

- Clause 11 (Constructs for electrical and physical modeling) defines syntax and semantics of arithmetic models used in this standard.

- Annexes. Following Clause 11 are a series of normative and informative annexes.

5

10

20

25

30

35

40

45

50

2. References \*\*Fill in applicable references, i.e. standards on which the herein proposed standard depends. This standard shall be used in conjunction with the following publication. When the following standard is superseded by an approved revision, the revision shall apply. \*\*The following is only an example. ALF does not depend on C. ISO/IEC 9899:1990, Programming Languages—C.<sup>1</sup> [ISO 8859-1: 1987(E)] ASCII character set

1

5

10

15

20

25

30

35

40

45

50

<sup>&</sup>lt;sup>1</sup>ISO publications are available from the ISO Central Secretariat, Case Postale 56, 1 rue de Varembé, CH-1211, Genève 20, Switzerland/ Suisse (http://www.iso.ch/). IEC publications are available from the Sales Department of the International Electrotechnical Commission, Case Postale 131, 3, rue de Varembé, CH-1211, Genève 20, Switzerland/Suisse (http://www.iec.ch/). ISO/IEC publications are also available in the United States from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

| 3. Definitions                                                                                                                                                                                                                                                                                                                                        | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| For the purposes of this standard, the following terms and definitions apply. The <i>IEEE Standard Dictionary of Electrical and Electronics Terms</i> [B4] should be consulted for terms not defined in this standard.                                                                                                                                | 5  |

| **Fill in definitions of terms which are used in the herein proposed standard.                                                                                                                                                                                                                                                                        | 3  |

| 3.1 <b>advanced library format:</b> The format of any file that can be parsed according to the syntax and semantics defined within this standard.                                                                                                                                                                                                     | 10 |

| 3.2 <b>application</b> , <b>electric design automation (EDA) application</b> : Any software program that uses data represented in the Advanced Library Format (ALF). Examples include RTL (Register Transfer Level) synthesis tools, static timing analyzers, etc. <i>See also:</i> <b>advanced library format</b> ; <b>register transfer level</b> . | 15 |

| 3.3 arc: See: timing arc.                                                                                                                                                                                                                                                                                                                             | 13 |

| 3.4 <b>argument:</b> A data item required for the mathematical evaluation of an artihmetic model. <i>See also:</i> <b>arithmetic model</b> .                                                                                                                                                                                                          | 20 |

| 3.5 <b>arithmetic model:</b> A representation of a library quantity that can be mathematically evaluated.                                                                                                                                                                                                                                             | 20 |

| 3.6                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.7 <b>register transfer level:</b> A behavioral representation of a digital electronic design allowing inference of sequential and combinational logic components.                                                                                                                                                                                   | 25 |

| 3.8                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.9 <b>timing arc:</b> An abstract representation of a measurement between two points in time during operation of a library component.                                                                                                                                                                                                                | 30 |

| 3.10                                                                                                                                                                                                                                                                                                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                       | 35 |

|                                                                                                                                                                                                                                                                                                                                                       |    |

|                                                                                                                                                                                                                                                                                                                                                       | 40 |

|                                                                                                                                                                                                                                                                                                                                                       | 40 |

|                                                                                                                                                                                                                                                                                                                                                       |    |

|                                                                                                                                                                                                                                                                                                                                                       | 45 |

|                                                                                                                                                                                                                                                                                                                                                       |    |

|                                                                                                                                                                                                                                                                                                                                                       | 50 |

# 4. Acronyms and abbreviations

This clause lists the acronyms and abbreviations used in this standard.

| ALF   | advanced library format, title of the herein proposed standard                        | 5  |

|-------|---------------------------------------------------------------------------------------|----|

| ASIC  | application specific integrated circuit                                               |    |

| AWE   | asymptotic waveform evaluation                                                        |    |

| BIST  | built-in self test                                                                    | 10 |

| BNF   | Backus-Naur Form                                                                      | 10 |

| CAE   | computer-aided engineering [the term electronic design automation (EDA) is preferred] |    |

| CAM   | content-addressable memory                                                            |    |

| CLF   | Common Library Format from Avant! Corporation                                         |    |

| CPU   | central processing unit                                                               | 15 |

| DCL   | Delay Calculation Language from IEEE 1481-1999 std                                    |    |

| DEF   | Design Exchange Format from Cadence Design Systems Inc.                               |    |

| DLL   | delay-locked loop                                                                     |    |

| DPCM  | Delay and Power Calculation Module from IEEE 1481-1999 std                            | 20 |

| DPCS  | Delay and Power Calculation System from IEEE 1481-1999 std                            |    |

| DSP   | digital signal processor                                                              |    |

| DSPF  | Detailed Standard Parasitic Format                                                    |    |

| EDA   | electronic design automation                                                          | 25 |

| EDIF  | Electronic Design Interchange Format                                                  |    |

| HDL   | hardware description language                                                         |    |

| IC    | integrated circuit                                                                    |    |

| IP    | intellectual property                                                                 | 20 |

| ILM   | Interface Logic Model from Synopsys Inc.                                              | 30 |

| LEF   | Library Exchange Format from Cadence Design Systems Inc.                              |    |

| LIB   | Library Format from Synopsys Inc.                                                     |    |

| LSSD  | level-sensitive scan design                                                           |    |

| MPU   | micro processor unit                                                                  | 35 |

| OLA   | Open Library Architecture from Silicon Integration Initiative Inc.                    |    |

| PDEF  | Physical Design Exchange Format from IEEE 1481-1999 std                               |    |

| PLL   | Phase-locked loop                                                                     |    |

| PVT   | process/voltage/temperature (denoting a set of environmental conditions)              | 40 |

| QTM   | Quick Timing Model                                                                    |    |

| RAM   | random access memory                                                                  |    |

| RC    | resistance times capacitance                                                          |    |

| RICE  | rapid interconnect circuit evaluator                                                  | 45 |

| ROM   | read-only memory                                                                      |    |

| RSPF  | Reduced Standard Parasitic Format                                                     |    |

| RTL   | Register Transfer Level                                                               |    |

| SDF   | Standard Delay Format from IEEE 1497 std                                              | 50 |

| SDC   | Synopsys Design Constraint format from Synopsys Inc.                                  | 50 |

| SPEF  | Standard Parasitic Exchange Format from IEEE 1481-1999 std                            |    |

| SPF   | Standard Parasitic Format                                                             |    |

| SPICE | Simulation Program with Integrated Circuit Emphasis                                   |    |

| STA   | Static Timing Analysis                                                                | 55 |

|       |                                                                                       |    |

| 1  | STAMP         | (STA Model Parameter ?) format from Synopsys Inc.                                                                |

|----|---------------|------------------------------------------------------------------------------------------------------------------|

|    | TCL<br>TLF    | Tool Command Language (supported by multiple EDA vendors) Timing Library Format from Cadence Design Systems Inc. |

| 5  | VCD           | Value Change Dump format (from IEEE 1364 std ?)                                                                  |

|    | VHDL<br>VHSIC | VHSIC Hardware Description Language very-high-speed integrated circuit                                           |

| 10 | VITAL         | VHDL Initiative Towards ASIC Libraries from IEEE ??? std                                                         |

| 10 | VLSI          | very-large-scale integration                                                                                     |

|    |               |                                                                                                                  |

| 15 |               |                                                                                                                  |

| 13 |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 20 |               |                                                                                                                  |

|    |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 25 |               |                                                                                                                  |

|    |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 30 |               |                                                                                                                  |

|    |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 35 |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 40 |               |                                                                                                                  |

| 40 |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 45 |               |                                                                                                                  |

|    |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 50 |               |                                                                                                                  |

|    |               |                                                                                                                  |

|    |               |                                                                                                                  |

| 55 |               |                                                                                                                  |

### 5. ALF language construction principles and overview

#### \*\*Add lead-in text\*\*

This section presents the ALF language construction principles and gives an overview of the language features. The types of ALF statements and rules for parent/child relationships between types are presented summarily. Most of the types are associated with predefined keywords. The keywords in ALF shall be case-insensitive. However, uppercase is used for keywords throughout this section for clarity.

### 5.1 ALF meta-language

The following Syntax 1— establishes an ALF meta-language.

```

ALF statement ::=

ALF_type [ALF_name] [ = ALF_value] ALF_statement_termination

ALF_statement_termination ::=

{ ALF_value | : | ; } }

| { { ALF_statement } }

ALF_type ::=

non_escaped_identifier [ index ]

(a)

|:

ALF_name ::=

identifier [ index ]

| control_expression

ALF value ::=

identifier

number

arithmetic_expression

| boolean_expression

control_expression

```

Syntax 1—syntax construction for ALF meta-language

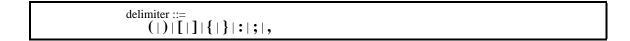

An ALF statement uses the delimiters ";", "{" and "}" to indicate its termination.

The *ALF type* is defined by a *keyword* (see Section 6.12 on page 36) eventually in conjunction with an *index* (see Section 7.8 on page 40) or by the *operator* "@" (Section 6.4 on page 28) or by the *delimiter* ":" (see Section 6.3 on page 27). The usage of keyword, index, operator, or delimiter as ALF type is defined by ALF language rules concerning the particular ALF type.

The *ALF name* is defined by an *identifier* (see Section 6.11 on page 34) eventually in conjunction with an index or by a *control expression* (see Section 10.9 on page 160). Depending on the ALF type, the ALF name is mandatory or optional or not applicable. The usage of identifier, index, or control expression as ALF name is defined by ALF language rules concerning the particular ALF type.

The ALF value is defined by an identifier, a number (see Section 6.5 on page 31), an arithmetic expression (see Section 11.1 on page 163), a boolean expression (see Section 10.7 on page 159), or a control expression. Depending on the type of the ALF statement, the ALF value is mandatory or optional or not applicable. The usage of identifier, number, arithmetic expression, boolean expression or control expression as ALF value is defined by ALF language rules concerning the particular ALF type.

55

1

5

10

15

20

25

30

35

40

45

- An ALF statement can contain one or more other ALF statements. The former is called *parent* of the latter. Conversely, the latter is called *child* of the former. An ALF statement with child is called a *compound* ALF statement.

- An ALF statement containing one or more ALF values, eventually interspersed with the delimiters ";" or ":", is called a *semi-compound* ALF statement. The items between the delimiters "{" and "}" are called *contents* of the ALF statement. The usage of the delimiters ";" or ":" within the contents of an ALF statement is defined by ALF language rules concerning the particular ALF statement.

An ALF statement without child is called an *atomic* ALF statement. An ALF statement which is either compound or semi-compound is called a *non-atomic* ALF statement.

Examples

```

15

```

20

25

30

35

40

10

```

ALF statement describing an unnamed object without value:

ARBITRARY ALF TYPE {

// put children here

ALF statement describing an unnamed object with value:

ARBITRARY ALF TYPE = arbitrary ALF value;

ARBITRARY_ALF_TYPE = arbitrary_ALF_value {

// put children here

ALF statement describing a named object without value:

ARBITRARY ALF TYPE arbitrary ALF name;

ARBITRARY_ALF_TYPE arbitrary_ALF_name {

// put children here

}

d)

ALF statement describing a named object with value:

ARBITRARY_ALF_TYPE arbitrary_ALF_name = arbitrary_ALF_value;

ARBITRARY ALF TYPE arbitrary ALF name = arbitrary ALF value {

// put children here

```

## 5.2 Categories of ALF statements

In this section, the terms *statement*, *type*, *name*, *value* are used for shortness in lieu of *ALF statement*, *ALF name*, *ALF value*, respectively.

45

50

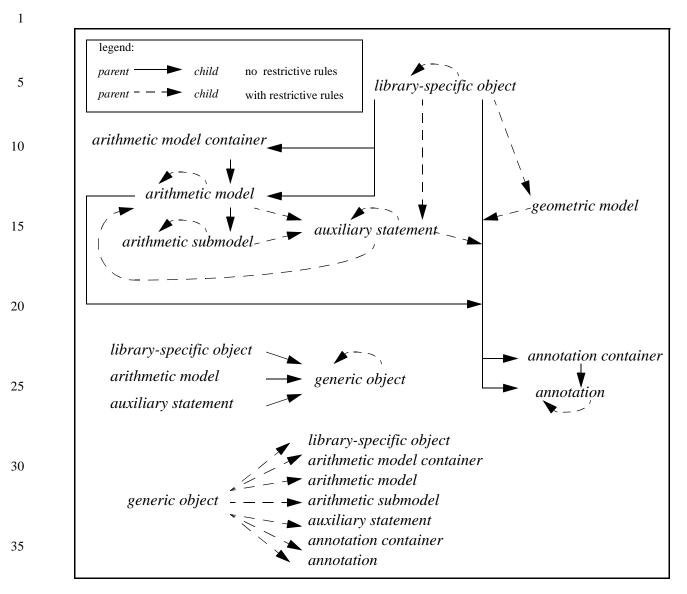

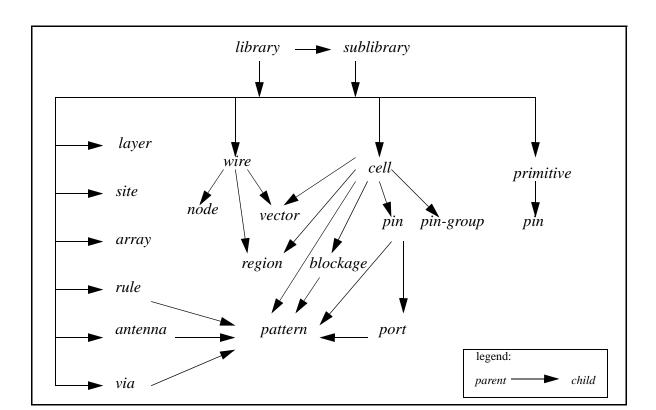

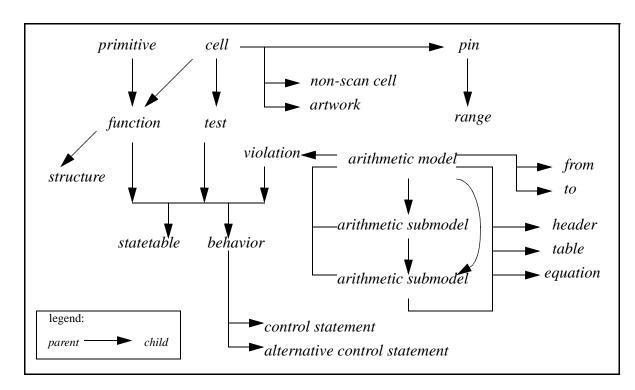

Statements are divided into the following categories: *generic object*, *library-specific object*, *arithmetic model*, *arithmetic submodel*, *arithmetic model container*, *geometric model*, *annotation*, *annotation container*, and *auxiliary statement*, as shown in Table 2—.

Table 2—Categories of ALF statements

| category                   | purpose                                                                                                                                                                                       | syntax particularity                                                                                                                                                                                     |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| generic object             | provide a definition for use within other ALF statements                                                                                                                                      | Statement is atomic, semi-compound or compound.  Name is mandatory.  Value is either mandatory or not applicable.                                                                                        |

| library-specific object    | describe the contents of a IC technology library                                                                                                                                              | Statement is atomic or compound. Name is mandatory. Value does not apply. Category of parent is exclusively library-specific object                                                                      |