# IBIS OPEN FORUM I/O BUFFER MODELING COOKBOOK

Version 4.0

Revision 0.95

Deleted: 9AM1

**Prepared By:** The IBIS Open Forum

Senior Editor: Michael Mirmak

Contributors:

Intel Corp.

John Angulo, Mentor Graphics Corp. Ian Dodd, Mentor Graphics Corp. Lynne Green, Green Streak Programs Syed Huq, Cisco Systems Arpad Muranyi, Intel Corp. Bob Ross, Teraspeed Consulting Group

From an original by Stephen Peters

Copyright © 2005 The IBIS Open Forum. All Rights Reserved.

Formatted: Title, Left

#### **DRAFT REVISION HISTORY**

- Rev 0.0 August 10, 2004

- Rev 0.1 September 9, 2004

- Rev 0.2 October 5, 2004

- Rev 0.3 October 7, 2004

- Rev. 0.4 October 15, 2004 added series/series switch descriptions; incorporated written feedback from Arpad, updated the single-ended totem-pole buffer diagrams, reformatted document with appropriate labels and table of contents; used buffer or component in place of device in many cases; incorporated new SSO language; added new differential type diagrams.

- Rev. 0.5 October 21, 2004 minor editorial changes, including fonts on examples; added captions to all drawings; added a new [Pin Mapping] description, with diagram; added diagrams to the "Series Element" section

- Rev. 0.6a November 19, 2004 added missing table and figure captions, inserted table of figures and table of captions, added A. Muranyi's suggested changes from Nov. 18 Cookbook meeting; added note regarding pin-to-pad bijective mapping; revised differential section to describe systems before buffers; revised most curve figures; added detail on [Ramp] calculation and matching to I-V table data; grammar and spelling check completed.

• Rev. 0.6b – November 23, 2004 – updated clamp analysis and on-die termination text to account for differences between specification and A. Muranyi algorithms. Cookbook now recommends the Muranyi ranges for clamp generation and Muranyi methods of subtraction.

• Rev. 0.7 – December 22, 2004 – made changes suggested by A. Muranyi, including

- o Additional line breaks before and after each section

- o Expanded [Pin Mapping] example

- o Updated differential comments

- Rev. 0.8 May 25, 2005 incorporates three subdrafts from A. Muranyi

- Rev. 0.9 June 13, 2005 updated with cleanup changes by M. Mirmak

Incorporated changes from Bob Ross, including CAE-> EDA tool vendors, standardized

indents of bullets, table changes, use of "tables" in place of "curves," etc. Also added two

previously missing drawings and updated internal document links

- Rev. 0.9AM1 June 23, 2005 Updated split C\_comp section with text from Arpad Muranyi

- Rev. 0.95 June 26, 2005 Significant overhaul of entire document; all changes tracked through <u>Microsoft Word® change tracking option</u>. Table numbering and rearrangement of <u>differential sections</u>, spelling and grammar checked.

Formatted: List Bullet 2, Bulleted + Level: 1 + Aligned at: 0.25" + Tab after: 0.5" + Indent at: 0.5"

Deleted: ¶

Deleted: ¶

Formatted: Indent: Left: 0.25", Hanging: 0.56", Tabs: Not at 0.5" +

Formatted: Bullets and Numbering

Formatted: Indent: Left: 0.25", Hanging: 0.25"

# TABLE OF CONTENTS

| 1.0 INTRODUCTION                                                                    | <u>1</u>  |

|-------------------------------------------------------------------------------------|-----------|

| 1.1 Overview of an IBIS File                                                        | 1         |

| 1.2 STEPS TO CREATING AN IBIS MODEL.                                                | 2         |

| 2.0 PRE-MODELING STEPS                                                              |           |

|                                                                                     |           |

| 2.1 BASIC DECISIONS                                                                 | 3         |

| 2.1.1 Model Version and Complexity                                                  | <u>3</u>  |

| 2.1.2 Specification Model vs. Part Model                                            | 4         |

| 2.1.3 Fast and Slow Corner Model Limits                                             | <u>4</u>  |

| 2.1.4 Inclusion of SSO Effects                                                      |           |

| 2.2 Information Checklist                                                           | <u>4</u>  |

| 2.3 COMPONENT BUFFER GROUPING                                                       |           |

| 3.0 EXTRACTING THE DATA – SINGLE-ENDED BUFFERS                                      | 6         |

| 3.1 EXTRACTING I-V DATA FROM SIMULATIONS                                            | 6         |

| 3.1.2 Sweep Ranges                                                                  | 8         |

| 3.1.3 Making Pullup and Power Clamp Sweeps Vcc-relative                             | 9         |

| 3.1.4 Diode Models                                                                  | 9         |

| 3.2 EXTRACTING RAMP RATE OR V-T WAVEFORM DATA FROM SIMULATIONS                      |           |

| 3.2.1 Extracting Data for the [Ramp] Keyword                                        | 10        |

| 3.2.2 Extracting Data for the Rising and Falling Waveform Keywords                  | 10        |

| 3.2.3 Minimum Time Step                                                             | 12        |

| 3.2.4 Multi-Stage Drivers                                                           | <u>12</u> |

| 3.3 Extracting Buffer Capacitance (C_comp)                                          | <u>12</u> |

| 3.3.1 Splitting C_comp into C_comp_pullup, C_comp_pulldown, C_comp_power_clamp, and | 1.4       |

| C comp gnd clamp                                                                    | 14        |

|                                                                                     |           |

| 4.0 EXTRACTING THE DATA – DIFFERENTIAL BUFFERS                                      | <u>16</u> |

| 4.1 Introduction                                                                    | 16        |

| 4.2 DIFFERENTIAL RECEIVERS                                                          |           |

| 4.3 DIFFERENTIAL DRIVERS                                                            | 21        |

| 4.4 On-die Termination                                                              | 24        |

| 4.5 DIFFERENTIAL BUFFER MODELING WITH IBIS                                          |           |

| 4.6 Data extraction                                                                 | 26        |

| 4.6.1 Extracting Common Mode I-V Tables                                             |           |

| 4.6.2 Extracting the differential mode I-V surfaces                                 | <u>29</u> |

| 4.6.3 Separating the On-die Termination I-V Tables                                  |           |

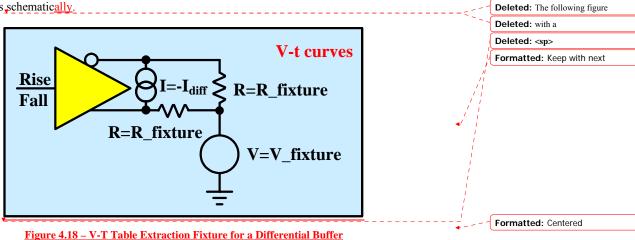

| 4.6.4 Extracting V-T Table Data                                                     | <u>31</u> |

| 4.6.5 Additional Notes on Differential Data Extraction                              | 32        |

| 4.7 C_COMP AND DIFFERENTIAL BUFFER CAPACITANCE (C_DIFF)                             |           |

| 5.0 PUTTING THE DATA INTO AN IBIS FILE                                              | 35        |

| 5.1 BASIC SYNTAX; KEYWORDS AND THEIR DEFINITIONS                                    | 36        |

| 5.1 BASIC SYNTAX: KEYWORDS AND THEIR DEFINITIONS 5.1.1 IBIS File Header Information | 36        |

| 5.1.2 Component and Pin Information                                                 | 37        |

| 5.1.3 The [Model] Keyword                                                           | <i>38</i> |

| 5.2 Data Checking                                                                   | 51        |

|                                                                                     |           |

| 5.2.1 Data Completeness                                                             | 51        |

Formatted: Title Char, No underline

Formatted: Centered

Deleted: Page Break

| <u>5</u>   | .3 I         | DATA LIMITING50                     | 1         |

|------------|--------------|-------------------------------------|-----------|

| <u>5</u>   |              | ADDITIONAL RECOMMENDATIONS          | 5         |

|            | <i>5.4.1</i> | Internal Terminations 50            | 5         |

|            | 5.4.2        | V-T Table Windowing 60              | <u>)</u>  |

| <u>5</u>   | .5 A         | ADVANCED KEYWORDS AND CONSTRUCTS 60 | <u>)</u>  |

|            | 5.5.1        | [Model Selector]6                   | 1         |

|            | 5.5.2        | [Submodel]6                         | 2         |

|            | 5.5.3        | [Model Spec]6.                      | 3         |

|            | 5.5.4        | [Diff Pin]6.                        | 3         |

|            | <u>5.5.5</u> | [Driver Schedule] 6-                | <u> 1</u> |

|            | 5.5.6        | [Pin Mapping]66                     | 8         |

|            | 5.5.7        | Series Elements                     | <u>)</u>  |

|            | 5.5.8        | Series Elements                     | 5         |

| <u>6.0</u> |              | LIDATING THE MODEL75                | 5         |

| <b>7.0</b> | co           | RRELATING THE DATA70                | <u>5</u>  |

| <u>8.0</u> | RE           | SOURCES                             | <u>7</u>  |

Formatted: Title

# **INDEX OF FIGURES**

| Figure 3.1 – Standard 3-state Buffer                                                        | <u>7</u> |

|---------------------------------------------------------------------------------------------|----------|

| Figure 3.2 – Simulation Setup for Extracting Ramp Rate Information (Rising Edge Shown)      | 10       |

| Figure 3.3 – Fixture for Extraction of C_comp Information                                   | 12       |

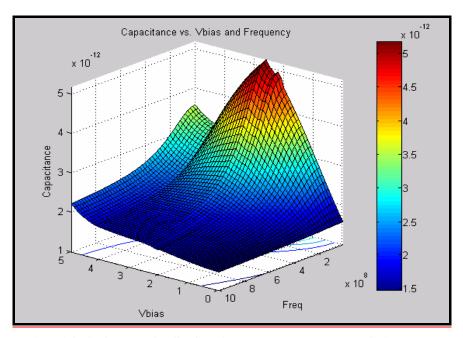

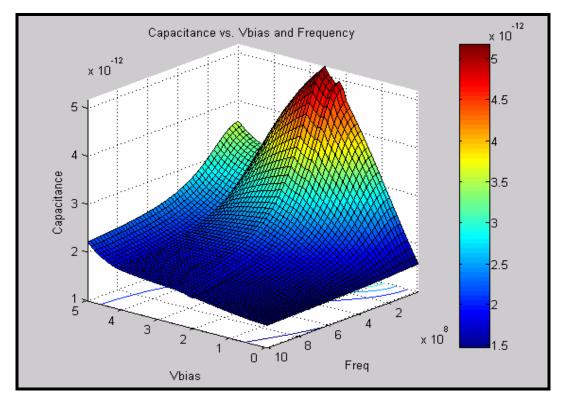

| Figure 3.4 – Surface Plot of Buffer Capacitance versus Frequency and DC Bias Voltage        | 14       |

| Figure 3.5 – Fixture for Extraction of C_comp Information                                   | 15       |

| Figure 4.1 – Device with Independent Input, Output and Power Supply Ports                   | 17       |

| Figure 4.2 – Device with Ports Using Common Ground                                          | 17       |

| Figure 4.3 – Input Port with Locally Generated Reference                                    | 18       |

| Figure 4.4 – Single-ended Receiver.                                                         | 19       |

| Figure 4.5 – True Differential Receiver                                                     | 19       |

| Figure 4.6 – Half-differential Receiver.                                                    | 20       |

| Figure 4.7 – Pseudo-differential Receiver                                                   | 21       |

| Figure 4.8 – Single-ended Driver.                                                           | 21       |

| Figure 4.9 – True Differential Driver with External Load.                                   | 22       |

| Figure 4.10 – Half-differential Driver with External Load                                   | 23       |

| Figure 4.11 – Pseudo-differential Driver Example                                            | 24       |

| Figure 4.12 – Block Diagram of a True Differential Model using IBIS v3.2 Constructs         |          |

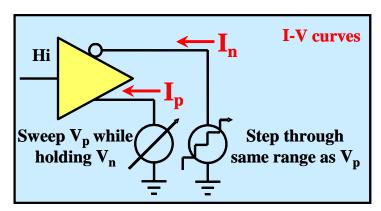

| Figure 4.13 – I-V Table Extraction Fixture for a Differential Buffer                        |          |

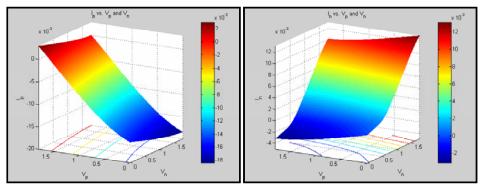

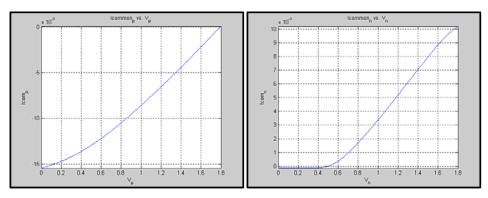

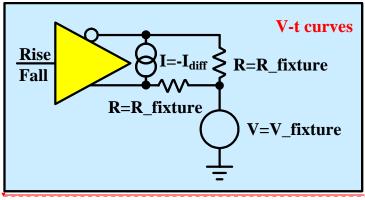

| Figure 4.14 – Surface Plots of Raw Data from I-V Sweep of Differential Buffer               | 28       |

| Figure 4.15 – I-V Curves of Common Mode Characteristics of Differential Buffer              | 29       |

| Figure 4.16 – Differential Current Plot of Output Current versus P and N Voltage            | 29       |

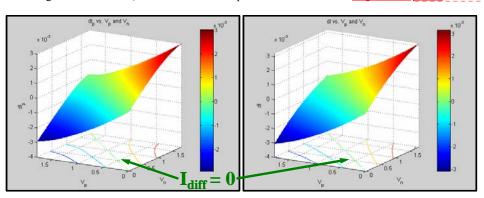

| Figure 4.17 – Plots of Various Vds Values for a [Series MOSFET] Buffer                      | 30       |

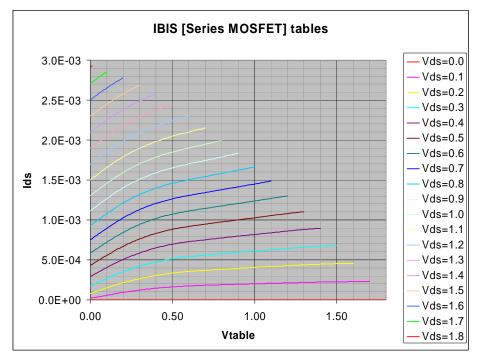

| Figure 4.18 – V-T Table Extraction Fixture for a Differential Buffer                        | 32       |

| Figure 4.19 – Fixture for Extraction of Differential Buffer C_comp                          | 34       |

| Figure 4.20 – Surface Plot of Differential Capacitance versus Frequency and DC Bias Voltage | 35       |

| <u>Figure 5.1 – Conceptual Diagram of Model Keyword Structure</u>                    | 39 |

|--------------------------------------------------------------------------------------|----|

| Figure 5.2 – Model Keyword Structure with Added Diode Detail                         | 40 |

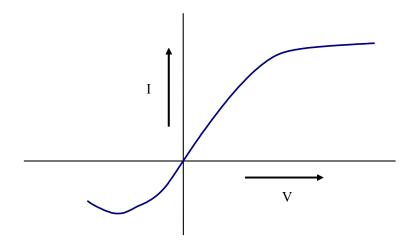

| Figure 5.3 – Graph of [GND Clamp] I-V Table Data                                     | 42 |

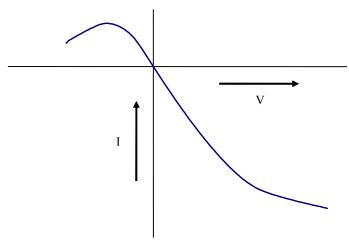

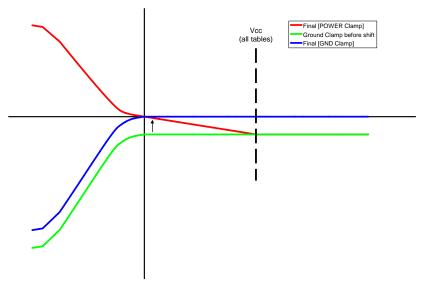

| Figure 5.4 – Graph of [POWER Clamp] I-V Table Data after Clamp Subtraction           | 43 |

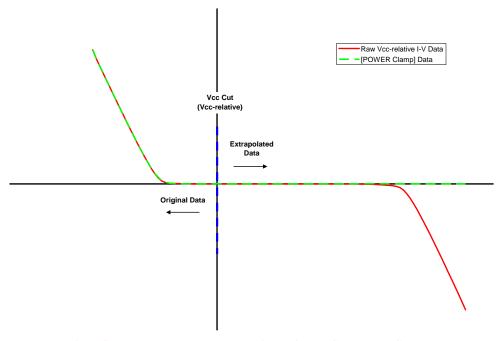

| Figure 5.5 – Raw I-V and Extrapolated Final [GND Clamp] Data Graphs                  | 43 |

| Figure 5.6 – Raw I-V and Extrapolated Final [POWER Clamp] Data Graphs                | 44 |

| Figure 5.7 – Graph of [Pulldown] I-V Table Data, after Clamp Subtraction             | 45 |

| Figure 5.8 – Graph of [Pullup] I-V Table Data after Clamp Subtraction                | 46 |

| Figure 5.9 – Diagram of Resistive Load for Rising Waveform                           | 52 |

| Figure 5.10 – V-T Table Loading Example                                              | 52 |

| Figure 5.11 – V-T Table Loading Example, Simplified                                  | 53 |

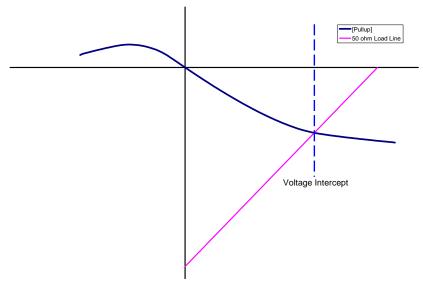

| Figure 5.12 – [Pullup] I-V Table Data with Load Line Intercept                       | 54 |

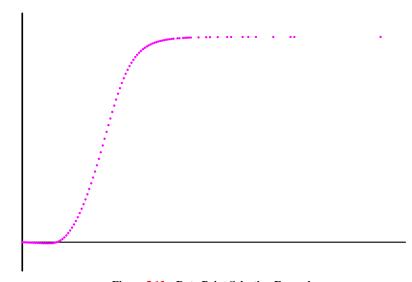

| Figure 5.13 – Data Point Selection Example                                           | 55 |

| Figure 5.14 – Diagram of I/O Buffer with Internal Termination                        | 56 |

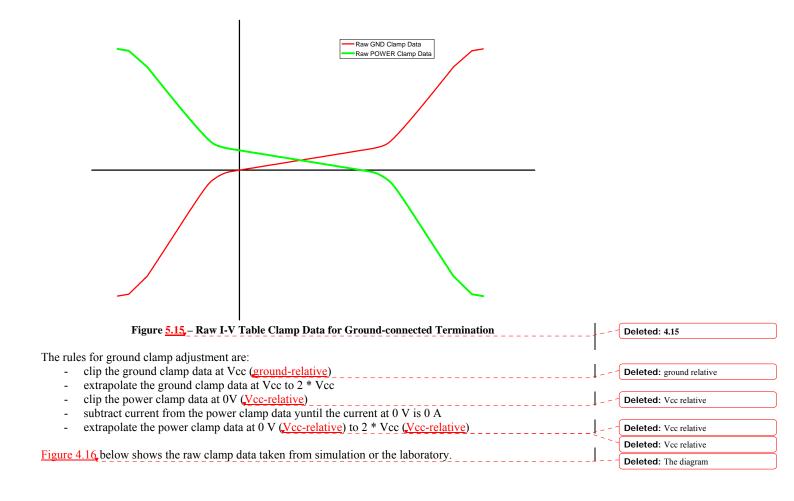

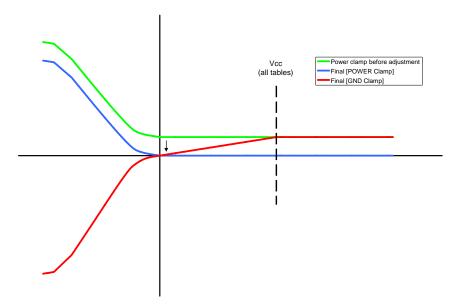

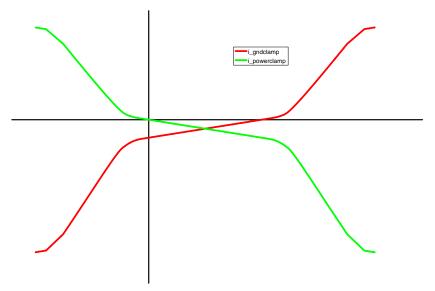

| Figure 5.15 – Raw I-V Table Clamp Data for Ground-connected Termination              | 57 |

| Figure 5.16 – Graph of I-V Data for Ground Terminated Buffer in High-Impedance State | 58 |

| Figure 5.17 – Graph of Power and Ground Clamp I-V Data for Vcc-connected Termination | 59 |

| Figure 5.18 – Graph of I-V Data for Vcc Terminated Buffer in High-Impedance State    | 60 |

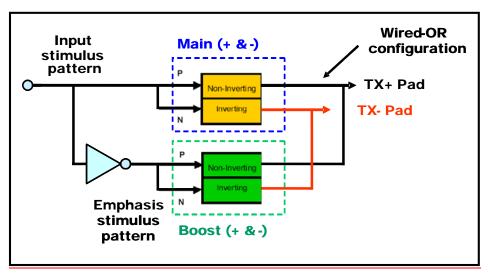

| Figure 5.19 – Block Diagram of a Two-Tap Differential Buffer Featuring Pre-Emphasis  | 66 |

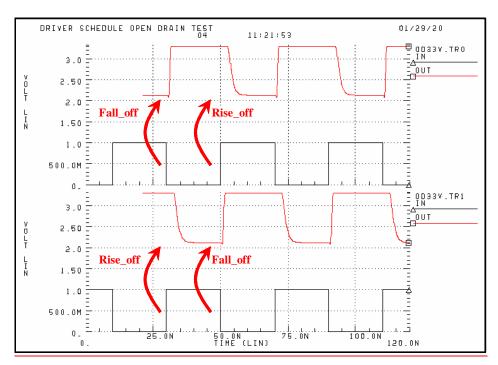

| Figure 5.20 – Output of a Scheduled Driver Configured as an Inverter.                | 67 |

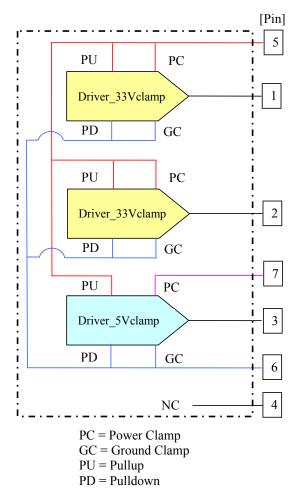

| Figure 5.21 – Component Diagram Showing Buffer and Supply Buses                      | 69 |

| Figure 5.22 – Connection of Single-ended and Series [Model]s                         | 71 |

Deleted: Figure 3.1 - Standard 3-state Buffer 7¶ Figure 3.2 - Simulation Setup for Extracting Ramp Rate Information (Rising Edge Shown) 10¶ Figure 3.3 – Device with Independent Input, Output and Power Supply Ports 13¶ Figure 3.4 – Device with Ports Using Common Ground 13¶ Figure 3.5 - Input Port with Locally Generated Reference 14¶ Figure 3.6 – Single Ended Receiver 15¶ Figure 3.7 – True Differential Receiver 15¶ Figure 3.8 – Half Differential Receiver 16¶ Figure 3.9 – Pseudo Differential Receiver 17¶ Figure 3.10 – Single Ended Driver 17¶ Figure 3.11 – True Differential Driver with External Load 18¶ Figure 3.12 – Half Differential Driver with External Load 199 Figure 3.13 – Pseudo Differential Driver Example 20¶ Figure 3.14 – Block Diagram of a True Differential Model using IBIS v3.2 Constructs 22¶ Figure 3.15 - I-V Table Extraction Fixture for a Differential Buffer 23¶ Figure 3.16 - Surface Plots of Raw Data from I-V Sweep of Differential Buffer 24¶ Figure 3.17 - I-V Curves of Common Mode Characteristics of Differential Buffer 25¶ Figure 3.18 – Differential Current Plot of Output Current versus P and N Voltage 25¶ Figure 3.19 - Plots of Various Vds Values for a [Series MOSFET] Buffer 26¶ Figure 3.21 – Block Diagram of a Two-Tap Differential Buffer Featuring Pre-Emphasis 30¶ Figure 3.22 - Output of a Scheduled Driver Configured as an Inverter 31¶ Figure 3.23 - Fixture for Extraction of C\_comp Information 33¶ Figure 3.24 - Surface Plot of Buffer Capacitance versus Frequency and DC Bias Voltage 34¶ Figure 3.25 - Fixture for Extraction of Differential Buffer C comp 34¶ Figure 3.26 - Surface Plot of Differential Capacitance versus Frequency and DC Bias Voltage 35¶ Figure 3.27 - Fixture for Extraction of C comp Information 36¶ Figure 4.1 – Conceptual Diagram of Model Keyword Structure 42¶ Figure 4.2 – Model Keyword Structure with Added Diode Detail 43¶ Figure 4.3 – Graph of [GND Clamp] I-V Table Data 45¶ Figure 4.4 – Graph of [POWER Clamp] I-V Table Data after Clamp Subtraction 46¶ [2]

Formatted: Title

### **INDEX OF TABLES**

| Table 3.1 – Recommended Load Circuits and Waveforms for V-T Data Extraction | <u>11</u> |

|-----------------------------------------------------------------------------|-----------|

| Table 5.1 – IBIS File Header Keywords                                       | 36        |

| Table 5.2 – IBIS Component and Pin Information                              | 37        |

| Table 5.3 – IBIS [Model] Subparameters                                      | 38        |

| Table 5.4 – IBIS [Model] Temperature and Voltage Keywords                   | 39        |

| Table 5.5 – [Model] I-V Table Keywords                                      | 40        |

| Table 5.6 – Pulldown I-V Table (Typical Only)                               | 45        |

| Table 5.7 – Summary of Recommended I-V Table Sweep Ranges                   | 46        |

| Table 5.8 – Poorly Extrapolated [GND Clamp] Table, Typical Corner           | 47        |

| Table 5.9 – [GND Clamp] Table, Typical Corner, with Improved Extrapolation  | 47        |

| Table 5.10 – [Ramp] and Waveform Table Keywords                             | 47        |

| Table 5.11 – I-V Table Keywords and Buffer Types                            | 49        |

| Table 5.12 – V-T Fixtures and Buffer Types                                  | 50        |

| Table 5.13 – Example V-T Table Data for Rising Waveform                     | 52        |

| Table 5.14 – V-T Table Loading Recommendations.                             | 54        |

Table 1 – Recommended Load Circuits and Waveforms for V-T Data Extraction . 11¶

Table 2 – IBIS File Header Keywords 39¶

Table 3 – IBIS Component and Pin Table 3 – IBIS Component and Pin Information . 39¶

Table 4 – IBIS [Model]

Subparameters 40¶

Table 5 – IBIS [Model] Temperature and Voltage Keywords .41¶

Table 6 – [Model] I-V Table Keywords .43¶

Table 7 – Pulldown I-V Table (Typical Only) 48¶ Only) 48¶

Table 8 – [Ramp] and Waveform Table Keywords 50¶

Table 9 – I-V Table Keywords and Buffer Types 52¶

Table 10 – V-T Fixtures and Buffer Types . 52¶

Table 11 – Example V-T Table Data for Rising Waveform . 54¶

Table 12 – V-T Table Loading Recommendations 56¶

#### 1.0 Introduction

This cookbook describes the recommended steps for producing IBIS models for digital integrated circuits (ICs). IBIS (officially, EIA standard 656-A-1999, IEC 62014-1) stands for I/O Buffer Information Specification. IBIS models provide a standardized way of representing the electrical characteristics of a digital IC's pins (input, output, I/O buffers and the like) behaviorally, i.e., without revealing the underlying circuit's structure or process information.

Note that the basic behavioral information in an IBIS model can be obtained either by direct measurement of the component or transistor level simulation of the component's buffers. This cookbook describes both methods, though with a strong emphasis on data extraction through simulation. The cookbook is targeted towards generating models of CMOS, GTL, and bipolar parts, and applies to models generated for IBIS version, 4.0 and earlier. For the most recent version of the specification and other IBIS documents visit the IBIS web page, (see the *Resources*, section later in this cookbook).

The intended audience of this cookbook is those responsible for performing the measurements or simulations that gather I/O buffer data, as well as those responsible for actual IBIS model creation. Persons involved in SI or system level PC board simulations may also benefit by reading this document. Some familiarity with behavioral modeling of I/O buffers and analog simulation is assumed.

#### 1.1 Overview of an IBIS File

An IBIS file contains, in a human readable ASCII format, the data required to model behaviorally a component's input, output and I/O buffers. Specifically, the data in an IBIS file is used to construct a model useful for performing signal integrity (SI) simulations and timing analysis of printed circuit (PC) boards. The fundamental information needed to perform these simulations is a buffer's I-V (current vs. voltage) and switching (output voltage vs. time) characteristics. Please note that the IBIS specification does NOT define an executable simulation model – it is a standard for the formatting and transfer of data. As such, the specification defines what the information included in an IBIS file represents and how it is to be gathered. It does not specify what an analog simulation application does with the data.

IBIS models are component-centric. That is, an IBIS file allows one to model an entire component, not just a particular input, output or I/O buffer. Therefore, in addition to the electrical characteristics of a component's buffers an IBIS file includes a component's pin-to-buffer mapping, and the electrical parameters of the component's package.

In general, an output or I/O buffer is characterized behaviorally using the following information:

- The buffer's output I-V characteristics when the output is in the logic low state

- The buffer's output I-V characteristics when the output is in the logic high state

- The buffer's output I-V characteristics when the output is forced below ground and above the power supply rail (referred to as its 'beyond the rail' characteristics)

- The time it takes a buffer's output to switch logic states (i.e. from low to high and high to low)

- The buffer's capacitance

For an input buffer the required information is reduced to:

- The buffer's I-V characteristics (including its 'beyond the rail' characteristics)

- The buffer's capacitance

IBIS Open Forum

I/O Buffer Modeling Cookbook

Page 1

Deleted: required to produce

Deleted: an

Deleted:

Deleted: or

**Deleted:** The purpose of this document is to describe how to gather the information required to produce an IBIS model, as well as some of the common pitfalls to avoid when creating the IBIS file itself

Deleted: s

Deleted: 3.2 and

Formatted: Not Strikethrough

Deleted:

Deleted: . For access information,

Formatted: Font: 11 pt, Italic

Deleted: Resources

**Deleted:** It is assumed that the reader

has s

**Deleted:** behaviorally

Deleted: a component's

Deleted: needed to

Deleted: a component's

Deleted: general

The above information is included in an IBIS file using 'keywords'. A keyword is a word or phrase surrounded by square brackets. Keywords are followed by either specific parameters or tables of data. For instance, the Model] keyword would be used to encapsulate the I-V and V-T tables, plus other data, for individual single-ended I/O buffer. Some keywords are required, but most are optional. At a minimum, a valid IBIS file contains the following data and keywords:

1. Information regarding the file itself and name of the component being modeled. This information is contained under the keywords [IBIS Ver], [File Name], [File Rev], [Component] and [Manufacturer].

- 2. Information about the package's electrical characteristics and the pin to buffer model mapping (i.e. which pins are connected to which buffer models). This information is included under the [Package] and [Pin] keywords.

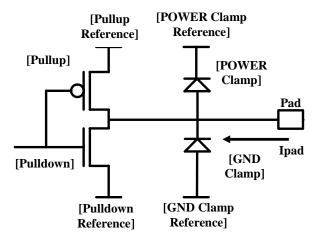

- 3. The data required to model each unique input, output and I/O buffer design on the component. The [Model] keyword introduces the data set for each unique buffer. As described above, buffers are characterized by their I-V behaviors and switching characteristics. This information is included using the keywords [Pullup], [Pulldown], [GND clamp], [POWER Clamp] and [Ramp]. In addition, the required parameters to the [Model] keyword specify a model's type (Input, Output, I/O, Open\_drain, etc.) and its input or output capacitance.

The details of constructing an IBIS model from data are included in <u>Putting the Data Into an IBIS File later in</u> this document.

#### 1.2 Steps to creating an IBIS Model

There are five basic steps to creating an IBIS model of a component:

- Perform the pre-modeling activities. These include deciding on the model's complexity, determining

the voltage, temperature and process limits over which the IC operates and the buffer model will be

characterized, and obtaining the component related (electrical characteristics and pin-out) and use

information about the component. See the chapter titled Pre-Modeling Steps.

- Obtain the electrical (I-V and switching response) data for output or I/O buffers either by direct

measurement or by simulation. See the chapter titled Extracting the Data. This chapter may also be

used by those who are doing the simulations required to gather the data but not actually creating the

IBIS file.

- 3. Format the data into an IBIS file. See the chapter titled <u>Putting the Data Into an IBIS File</u>.

- 4. Run the file through the Golden Parser. If the model is generated from simulation data, validate the model by comparing the results from the original analog (transistor level) model against the results of a behavioral simulator that uses the IBIS file as input data. See the chapter titled Validating the Model.

- When the actual silicon is available (or if the model is from measured data), compare the IBIS model data to the measured data. See the chapter titled <u>Correlating the Data</u>.

The rest of this cookbook documents these steps in detail.

**Deleted:** either by specific parameters

Deleted: the

Deleted: Putting the Data Into an IBIS

File

Deleted: chapter

Formatted: Font: Italic

Deleted: titled

Deleted: Pre-Modeling Steps

Formatted: Font: 11 pt, Italic

Deleted: tables

Deleted: rise/fall

Deleted: titled

Formatted: Font: 11 pt, Italic

Deleted: Extracting the Data

**Deleted:** and run the file through the Golden Parser

Golden Parser

**Deleted:** Putting the Data Into an IBIS

Formatted: Font: Italia

Deleted: titled

Formatted: Font: 11 pt, Italic

**Deleted:** Validating the Model

Formatted: Font: 11 pt, Italic

Deleted: Correlating the Data

#### 2.0 Pre-Modeling Steps

#### 2.1 Basic Decisions

Before one creates an I/O buffer model there are several basic questions that must be answered regarding the model's complexity, operational limits, and use requirements. Answering these questions requires not only knowledge of the buffer's physical construction, but also knowledge of the final application in which the IC will be used, and any specific requirement the model users may place on the model. These questions cannot be answered by the model creator alone; they generally require the involvement of both the buffer designer and members of the team responsible for insuring that the I/O buffers are useable in a system environment. This team is referred to as the interconnect simulation team. Together, the model creator and interconnect simulation team must determine the following:

- Model Version and Complexity

- Specification Model vs. Part Model

- Fast and Slow Corner Model Limits

- Inclusion of SSO Effects

#### 2.1.1 Model Version and Complexity

Based on the characteristics and construction of the I/O buffer itself, and the model user's simulator capability, you must decide what IBIS version of the model is most appropriate. Different IBIS versions, as denoted by the [IBIS Ver] keyword, support different features. Additionally, the checking rules used by the IBIS Golden Parser change slightly with each version. In general, models should use the highest [IBIS Ver] version number supported by the Golden Parser and by their simulation tools (see *Validating the Model*). Similarly, following good engineering practice, use the simplest model that will suffice.

For standard CMOS buffers with a single stage push-pull or open drain outputs, a version 1.1 model is the starting point. A version 1.1 model describes a buffer using a low state and high state I-V table, along with a linear ramp that describes how fast the buffer switches between states. IBIS version 2.1 adds support for tables of V-T data, in addition to support for ECL and dual-supply buffers, ground bounce from shared power rails, differential I/O buffers, termination components, and controlled rise-time buffers. A version 2.1 or above model will be required if the I/O buffer has any of the following characteristics:

- Multiple Supply Rails A version 2.1 (or higher) model is required if the buffer contains diode effects from parasitic diodes or electrostatic discharge (ESD) diodes which are referenced to a different power rail than the pullup or pulldown transistors, or if the I/O uses more than one supply (for example, a buffer whose output swings from below ground or above Vcc).

- Non-Linear Output Switching Waveform A version 2.1 (or higher) model is required if the I/O buffer's output voltage vs. time waveform (its V-T waveform) when switching low-to-high or high-to-low cannot be accurately described using a linear ramp rate value. This is the case for GTL technology, or for any buffer that uses "graduated turn on" type technology.

- In addition, a version 2.1 model description is required if the model maker wishes to enable the user to perform ground bounce simulations by connecting several buffers together on a common supply rail. See the [Pin Mapping] keyword description below.

IBIS version 3.2 adds support for an electrical board description format, multi-staged buffers or buffers that may use multiple I-V tables and diode transient times, among other features. IBIS 4.0 extends the maximum length of V-T table data, supports the inclusion of independent validation data tables and adds more parameters for expressing "databook" criteria for evaluating buffer performance.

mum length

neters for

IBIS Open Forum

I/O Buffer Modeling Cookbook

Page 3

Deleted: model users

Deleted: ¶

Formatted: Bullets and Numbering

Deleted: a knowledge

Deleted: a knowledge

Formatted: Font: Italic

Deleted: -- A

Deleted: Discharge

Deleted: E

Deleted: and above

#### 2.1.2 Specification Model vs. Part Model

A model can be made to represent a particular existing component or can be made as a representative encapsulation of the limits of the specification for a class of components. Specification vs. Part is a major factor in determining if and how much guard-banding or de-rating a model requires. Generally, a "spec model" is based on an existing part, then the strength and edge rate of the model is adjusted to meet the best and worst case parameters of a particular specification. For example, an GTL buffer model for a particular processor may give a worst case Vol of 0.4 V at 36 mA. However, if the GTL specification allows for a worst case Vol of 0.6 V at 36 mA the model's pulldown table may be adjusted (or de-rated) to describe the specification and not just

#### 2.1.3 Fast and Slow Corner Model Limits

The IBIS format provides for slow (weakest drive, slowest edge), typical and fast (strongest drive, fastest edge) corner models. These corners are generally determined by the environmental (temperature and power supply) conditions under which the silicon is expected to operate, the silicon process limits, and the number of simultaneous switching outputs. The interconnect team or project must supply the model developer with the environmental, silicon process, and operational (number of SSOs) conditions that define the slow, typical and fast corners of the model. *Please note that for an output buffer model to be useful for flight time simulations these conditions MUST match those used for specifying the buffer's Tco parameter.*

#### 2.1.4 Inclusion of SSO Effects

the behavior of an individual part.

Closely related to the discussion on model limits is the decision on how to include simultaneous switching output (SSO) effects (sometimes called simultaneous switching noise). SSO effects can be included explicitly in a model by measuring the I-V and edge rate characteristics under SSO conditions. For example, a buffer's I-V characteristic can be measured with all the adjacent buffers turned on and sinking current, or the buffer's edge rate may be measured while adjacent buffers are also switching. Alternatively, a model that represents a single buffer in isolation may be created, then several buffers may be connected to a common power or ground rail via the [Pin Mapping] keyword. The former method (including SSO effects in the I-V and V-T tables) has the advantage that the resulting model is straightforward to verify and less dependent on any particular simulator's capability. Note however, the [Pin Mapping] keyword method also adds data to enable explicit ground bounce simulations and devise specific 'what if' scenarios.

Note that the information provided under IBIS 4.0 and earlier versions only describes the output behavior of buffers under loaded conditions. Therefore, SSO simulations will only be based on the behavior at the pad and not upon information extracted about the current profile of the supplies as the buffer switches. Different distributions of internal buffer current may result in the same behavior at the pad. Different simulation tools may therefore make radically different assumptions regarding SSO behavior for the same IBIS data. Check with your simulation tool vendor for details on their specific assumptions and IBIS SSO simulation algorithms.

#### 2.2 Information Checklist

Once the above decisions have been made, the model maker can begin acquiring the specific information needed to generate the IBIS model for the component. Some of this information is specific to the component as a whole

Deleted: the process of

Deleted: S

Deleted:

Deleted: does

Deleted: give

Deleted: the user the ability to perform

Deleted: Switching

Deleted: Output

ge 4 I/O Buffer Modeling Cookbook

IBIS Open Forum

Deleted: Model vs

Page 4

and goes directly into the IBIS file itself, while some items are needed to perform the required simulations. In general, the model maker will need the following:

IBIS Specification Acquire, read and become familiar with the IBIS specification.

Buffer Schematics Acquire a schematic of each of the different types of input, output, I/O<sub>2</sub>

etc. buffers on the component. If at all possible, use the same schematic that the silicon designers use for simulating Tco. Make sure that the schematic includes ESD diodes (if present in the design) and a representation of the power distribution network of the package. From these schematics determine the types of each buffer structure (standard

Deleted: and

Deleted: output

output or I/O buffer

Deleted: a

Deleted: that

Deleted: for each different type of

CMOS totem-pole, open-drain, etc.) on the IC.

Clamp Diode and Pullup References Determine if the buffer uses different voltage references (power and/or

ground supply rails) for the clamp diodes than those used for the pullup or pulldown transistors. This may be the case when dealing with components that are designed to be used in mixed 3.3 V/5 V systems.

Packaging Information Find out in what packages the component is offered. A separate IBIS

model is required for each package type. Acquire a pinout list of the component (pin name to signal name mapping) and determine the pin

name to buffer type mapping.

Packaging Electricals Acquire the electrical characteristics (inductance, capacitance and

resistance) of the component's package for each pin to buffer connection (package stub). This becomes the R\_pin, L\_pin and C\_pin parameters of the [Pin] keyword or the R\_pkg, L\_pkg and C\_pkg of the

[Package] keyword.

Signal Information Determine which signals can be ignored for digital IC modeling

purposes. For example, <u>purely analog pins</u>, test pads or static control signals may not need a model. These may be listed as NC in the [Pin]

list.

Die Capacitance Obtain the capacitance of each pad (the C comp parameter). This is

the capacitance seen when looking from the **pad** back into the buffer for a fully placed and routed buffer design, **exclusive of package effects** (note that the phrases "Cdie" or "die capacitance" may be used in other industry contexts to refer to the capacitance of the entire component, in some cases including package capacitance, as measured

between the power and ground supply rails).

Vinl and Vinh Parameters A complete IBIS model of an input or I/O buffer includes the Vinl and

Vinh parameters. Vinl is the maximum pad or pin voltage at which the receiving buffer's logical state would still be a logical "low" or "0." Vinh is the minimum pad or pin voltage at which the receiving buffer's logical state would still be a logical "high" or "1." Note that IBIS 4.0 permits advanced threshold descriptions, including different AC and

DC switching voltages plus hysteresis effects.

IBIS Open Forum

I/O Buffer Modeling Cookbook

Page 5

Tco Measurement Conditions

Find out under what loading conditions an output or I/O buffer's Tco (propagation delay, clock to output) parameter is measured. This includes the load capacitance, resistance and/or voltage (Cref, Rref and Vref parameters) as well as the output voltage crossing point at which Tco is measured (the Vmeas parameter).

#### 2.3 Component Buffer Grouping

One of the first tasks when building an IBIS representation of a component is to determine how many individual buffer models have to be created. Separate buffer models are required for each different buffer design or structure (number and connection of the transistor elements) the component uses. Begin by first separating a component's pins into buffer types: inputs, outputs, I/Os and the like. Then for each group of pins determine how many unique buffer designs are present. For example, a clock input may have a different input design or diode structure than the rest of the component's inputs. Also, be aware that even if all the output or I/O pins are driven by buffers of the same design, separate output or I/O models may be required if a group of signals have different C\_comp parameters or Tco measurement conditions. Once the number of separate buffer models has been determined, the actual buffer model creation process can begin.

Deleted: Tips For

Deleted: model

Deleted: determining

Deleted: and

Deleted: signals

Deleted: buffer

#### 3.0 Extracting the Data – Single-ended Buffers

Once the pre-modeling steps have been performed, the process of gathering the required I-V and switching information can begin. Output and I/O buffers demand both I-V tables and rise/fall data, while input buffers in most cases only demand I-V tables. There are two ways to get this information:

- For pre-silicon models use circuit simulation tools to obtain the information over the worst cases of

process and temperature variations, then correlate the model against the actual silicon.

- When the actual silicon is available, use the data from physical measurements to build the model.

However, obtaining worst case min and max data over process and temperature may be difficult using physical data.

The first sections of this chapter explain how to obtain the I-V and switching information from a transistor-level model of the buffer, either by use of an automated simulation template or extraction tool (such as S2IBIS3) or by doing your own simulations. Obtaining I-V and Switching Information via Lab Measurement later in this chapter explains how to gather this information via measurement. The reader is assumed to have some background in doing transistor level simulations and/or the use of lab equipment.

Totem pole CMOS structures are assumed for most of the text below. Some adjustments will be necessary for designs such as open source, open sink and the like.

Deleted: need

Deleted: require

Deleted: only

Deleted: it is difficult to get

Deleted: this way

Deleted: s

Deleted: V-T

Formatted: Font: Italic

Deleted: It is assumed that t

Deleted: has

#### 3.1 Extracting I-V Data from Simulations

The first step to extracting the required I-V tables is understanding the buffer's operation. Analyze the buffer schematic and determine how to put the buffer's output into a logic low, logic high and (if applicable) high impedance (3-state) state. As mentioned above, the schematic should include the R, L and C parameters associated with the on-die power supply distribution and ground return paths as well as any ESD or protection diodes. The schematic should also indicate if the power clamp and/or ground clamp diode structures are tied to voltage rails (voltage references) different than those used by the pullup and/or pulldown transistors.

Deleted: a

Deleted: that

Page 6

I/O Buffer Modeling Cookbook

IBIS Open Forum

#### 3.1.1.1 Simulation Setup

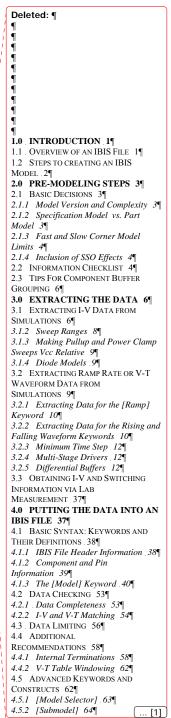

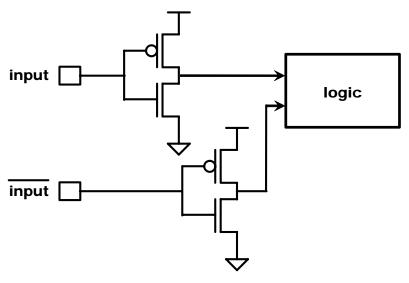

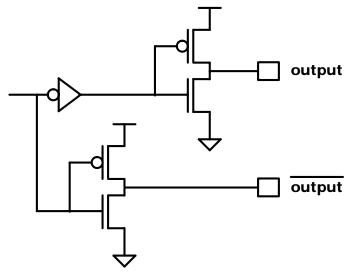

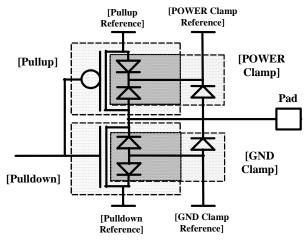

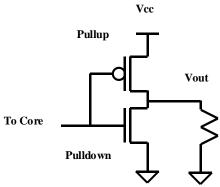

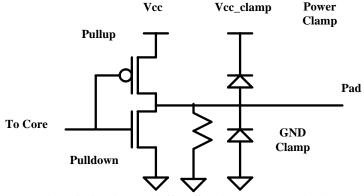

A typical I-V table simulation setup for an output or I/O buffer is shown in Figure 3.1 below. For this example the buffer being analyzed is a standard 3-state buffer with a single push-pull output stage. The buffer uses electrostatic discharge protection devices in addition to its parasitic driver diodes. The buffer's clamp supplies are assumed to be identical to its driver supply.

Deleted: diode clamps

Deleted: supply

Deleted: is

Figure 3.1. Standard 3-state Buffer

All measurements are made at the output node (pad) as shown above. Remove all package lead (R\_pin, L\_pin, C\_pin) parasitics. However, any series resistances present between the pad and the pullup/pulldown\_transistors are included.

The output buffer is connected to an independent voltage source. Set the buffer's input(s) so that the desired output state (low, high, off) is obtained, then using a DC or 'transfer function' analysis sweep the voltage source over the sweep range vcc to Vcc \* 2 while recording the current into the buffer. An alternative method is to perform a 'transient analysis'. The voltage source in this case should be linear ramp function driving the output node, slow enough that the current measurement at each time point is effectively DC, without reactive aspects of the design affecting the result. The current flow into the pad is measured (by IBIS convention, current flow into the pad positive), as is the voltage at the node with respect to a lab reference, then the resulting I-T and V-T data is combined into a single I-V table. Note that a transient function analysis may require post simulation data manipulation.

Deleted: 3.1 Deleted: -

Deleted: resistors

Deleted: -

Deleted: at the output node

Deleted: out

Deleted: would be neg

Deleted: a

#### 3.1.1.2 3-state Buffers

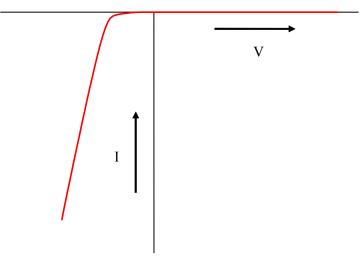

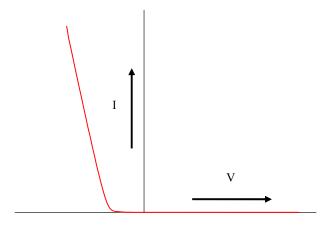

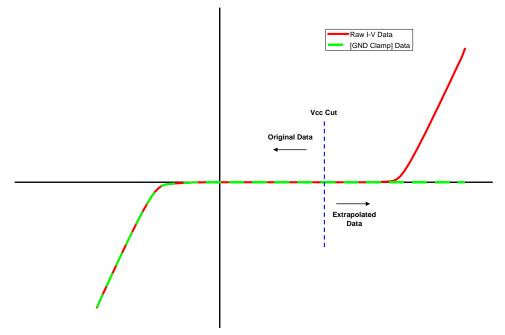

For an I/O (3-stateable) buffer, four sets of I-V tables are generally included; one with the pulldown transistor turned on (output in the low state), one with the pullup transistor turned on (output in the high state), and two with the output in a high impedance state. The data gathered while the output is in the low state is used to construct the [Pulldown] table. Data gathered when the output is in the high state is used to construct the [Pullup] table. Pulldown I-V data is referenced to ground while pullup I-V data is referenced to Vcc. (referencing pullup data to Vcc means that the endpoints of the sweep range are adjusted as Vcc is adjusted; refer to Making Pullup and Power Clamp Sweeps Vcc-relative for more details). Data for the [GND Clamp] keyword is taken with the output in the high impedance state and is ground-relative, while data for the [POWER]

Deleted: though

Deleted:

Deleted: Referencing

**Deleted:** the Making Pullup and Power Clamp Sweeps Vcc Relative

Deleted: section

Deleted: ground relative

IBIS Open Forum

I/O Buffer Modeling Cookbook

Page 7

Clamp] keyword is also taken with the output in a high impedance state but with the data <u>Vcc-relative</u>. For each keyword, a typical set of tables must be included; data for minimum and maximum corner conditions may be included. If corner data is present, it must cover the entire sweep range.

Deleted: Vcc relative

Thus, a buffer with 3-state capabilities would require the following 12 I-V data sets:

- Pulldown I-V under minimum, typical and maximum conditions, data ground-relative

- Pullup I-V under minimum, typical and maximum conditions, data <u>Vcc-relative</u>

- High impedance state I-V under minimum, typical and maximum conditions, data ground-relative

- High impedance state I-V under minimum, typical and maximum conditions, data Vcc-relative

#### Deleted: ground relative

Deleted: Vcc relative

Deleted: I

Deleted: ground relative

Deleted: g

Deleted: Vcc relative

Deleted: output

#### 3.1.1.3 Output Only Buffers

For an output only (non 3-state) buffer, only two sets of tables are needed; one with the pulldown transistor turned on (output in the low state), and one with the pullup transistor turned on (output in the high state). As before, pulldown I-V data is referenced to ground while pullup I-V data is referenced to Vcc. Because an output only buffer does not have a 3-state mode the power and ground clamp diode tables cannot be isolated from the transistor tables; the beyond the rail data is simply included in the final IBIS [Pullup] and [Pulldown] I-V tables. The [GND Clamp] and [POWER Clamp] keywords are not required for an output only buffer.

Deleted: p

Deleted: pulldown

Deleted: data

#### 3.1.1.4 Open Drain Buffers

Open-drain (open-sink) or open-collector (open-source) type buffers generally contain three sets of I-V data: [Pulldown], [GND Clamp] and [POWER Clamp] (technically, clamp data is never required by the IBIS specification). Data for the [Pulldown] table is gathered as described previously. [POWER Clamp] and [GND Clamp] data is gathered by turning off the pulldown transistor then doing the two I-V sweeps as described above for an I/O buffer in the high impedance state. Note that an open drain buffer may not require the full vcc to Vcc \* 2 sweep range; refer to the section below entitled Sweep Ranges.

Deleted:

Formatted: Font: Italic

Deleted: Sweep Ranges

#### 3.1.1.5 Input Buffers

When gathering I-V data for input buffers the same general setup is used, only the variable voltage source is placed on the input node. Input buffers generally contain only [POWER Clamp] and [GND Clamp] I-V data, though [POWER Clamp] only or [GND Clamp] only designs are possible (technically, clamp data is never required by the IBIS specification). As with the output buffer, [GND Clamp] data is gathered via a voltage sweep with the voltage source referenced to ground and the [POWER Clamp] data is gathered by a voltage sweep with the voltage source Vcc-relative. If an input buffer includes internal resistive terminations to power and/or ground, the effects of these terminations on the I-V tables are included into the respective ground clamp or power clamp I-V data and additional post-processing is required before the data can be included in the IBIS model. See Internal Terminations, for more information.

Deleted: buffers have been seen

Deleted: Vcc relative

Formatted: Font: Italic

Deleted: Internal Terminations

#### 3.1.2 Sweep Ranges

As per the IBIS specification I-V data must be supplied over the range of voltages the output could possible see in a transmission line environment. Assuming that a buffer's output swings from ground to Vcc (where Vcc is the voltage given by the [Voltage Range] or [Pullup Reference] keywords) this range is Vcc (the maximum negative reflection from a shorted transmission line) to Vcc \*2 (the maximum positive reflection from an open circuited transmission line). However, be aware that if a buffer is operating in an environment where its output

Deleted: -

could be actively driven beyond these limits the I-V table must be extended further. Consider, for example, a 3.3 V I/O buffer operating in a mixed 3.3 V/5 V system. While the buffer's output may only drive from 0 to 3.3 V, a five volt buffer connected to this output may drive the output node beyond 3.3 V volts. In this case I-V data should be supplied over a full -5 V to +10 V range. Likewise, an open collector or open drain buffer may be terminated in a voltage (Vpulllup) different than that given by the [Voltage Range] keyword. In this case it is recommended to supply the pullup and pulldown data over the range Vpullup to Vpullup \*2.

Semiconductor buffer models may not be well behaved over these ranges, so one may reduce the actual sweep

range and use linear extrapolation to get to the required endpoints. For example, suppose one were attempting

V range. The model maker may choose to limit the simulation sweep to -2 V to +7 V, and then extrapolate to the final -5 V to +10 V range. Be aware however, that the simulation sweep range must be enough to forward

to gather the I-V data for a typical 5 V buffer. The IBIS specification requires I-V data over the full -5 V to ±10

Deleted: -

**Deleted:** It is recognized that s

Deleted: it is acceptable to lessen

Deleted: then

Deleted:

**Deleted:** the diodes intrinsic to the

Deleted: Vcc Relative

#### 3.1.3 Making Pullup and Power Clamp Sweeps Vcc-relative

bias any ESD protection diodes or parasitic diode structures.

As stated earlier the pullup and power clamp data is relative to Vcc. In order to make the pullup and power clamp data Vcc-relative (and to enter this I-V data into IBIS's table format properly) adjust the starting and ending endpoints of these sweep to follow the variations in Vcc. For example, suppose one were gathering the pullup data for a standard 3.3 V buffer whose Vcc specification was 3.3 V +/- 10% (i.e. the operating Vcc ranged from 3.0 V minimum to 3.6 V maximum). The sweep voltage under typical conditions would range from -3.3 V to +6.6 V. For minimum conditions, where the Vcc was adjusted to 3.0 V, the sweep voltage should also be adjusted negative 0.3 V, to sweep from -3.6 V to +6.3 V. Likewise, for maximum conditions, adjust the sweep endpoint positive 0.3 V so the sweep covers -3.0 V to 6.9 V. By gathering the data in this manner the corresponding voltage data point in all three data sets represent the same 'distance' from Vcc. Note that the 9.9 V sweep RANGE remains the same for all three simulations.

**Deleted:** Vcc relative

Deleted: h

#### 3.1.4 Diode Models

When designing digital I/O buffers most of the analysis is focused on the buffer's Tco parameter and output impedance. Very little attention is paid to a buffer's 'beyond the rail' operation. Thus, the diode models included in buffer's schematic may be included for layout or completeness only, and are most likely ideal diode models with no intrinsic resistance or other parasitics. Likewise, if the design relies on the intrinsic diode structure of the output transistors to provide output protection the transistor models may not properly model operation beyond the rails. Therefore, when simulating in these voltage regions one may get unrealistically large (e.g., kiloamp) power and ground clamp currents. If this is a problem several options are available. Working with the buffer designer the diode or transistor models can be enhanced to include the proper junction or bulk resistance. Note that with large ESD structures the metal resistance can be relatively large—on the order of a few ohms – an this should be included in the design. If a physical silicon sample is available the model creator can measure the power and ground clamp I-V data directly.

Deleted: doing

Deleted: design

Deleted: concerned with

Deleted: 'perfect'

Deleted: this mode of

Deleted: doing

Deleted: o

**Deleted:** the model creator has a couple

Deleted: n actual buffer

#### 3.2 Extracting Ramp Rate or V-T Waveform Data from Simulations

Simulations to obtain the ramp rate and/or V-T (output voltage vs. time) tables are relatively straight forward. When modeling a CMOS or TTL buffer, for each simulation corner (minimum, typical, maximum), four V-T data sets are recommended; one rising and one falling set for the buffer output switching low to high and one

Deleted: For

Deleted: required

IBIS Open Forum

I/O Buffer Modeling Cookbook

Page 9

rising and one falling set for the buffer output switching high to low. This data can then be reported as a rising and falling dV/dt ratios (the 'ramp rate') or the actual V-T data may be reported directly.

#### 3.2.1 Extracting Data for the [Ramp] Keyword

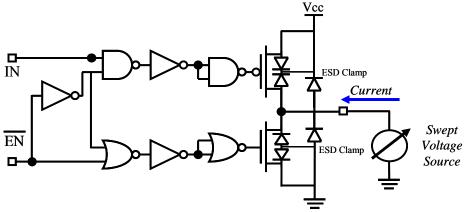

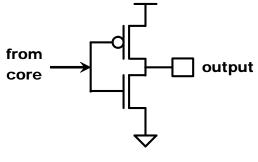

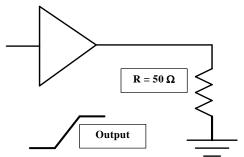

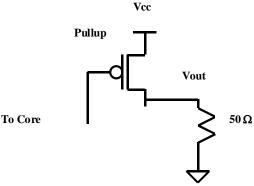

If the output switching (V-T) waveform of a buffer can be approximated by a linear ramp (i.e. the V-T waveform has no abrupt changes in shape, there are no 'pedestals' in the waveform, etc.) then the V-T data may be reported as a rising and falling ramp rate (dV/dt) by using the [Ramp] keyword. Data for the [Ramp] keyword may be extracted using a simulation setup similar to that shown in Figure 3.2 below. Switching information can only be represented in IBIS 1.1 through the [Ramp] keyword.

Figure 3.2 Simulation Setup for Extracting Ramp Rate Information (Rising Edge Shown)

Obtain rise and fall time data by setting the simulator for a transient analysis simulation. The control inputs of the buffer are set to enable the buffer outputs and a driving waveform is applied to the buffer input. The slew rate of the input stimulus driving waveform should match the internal slew rate of the technology (i.e. the slew rate of the pre-driver that would normally drive the final output stage). Rising edge ramp rate data is obtained by placing a load resistance from the output to ground then stimulating the buffer so that the output switches from low to high. Falling edge ramp data is captured with the load resistor tied to Vcc. Use a load resistance of 50 ohms. If the buffer does not have enough drive capability to make a significant output transition then a higher value of load resistance may be used, but this must be noted in the IBIS file (see the description of the [Ramp] keyword in the IBIS specification for details). For an open-drain or ECL/PECL buffer, measure the rise and fall times into the load resistor and voltage used by the manufacturer when specifying propagation delays. As with the I-V simulations the package lead (L\_pin, R\_pin, C\_pin) parasitics must be removed. However, simulations are performed with C comp effects included in the circuit.

#### 3.2.2 Extracting Data for the Rising and Falling Waveform Keywords

In IBIS versions 2.1 and above V-T data may be reported directly by using the [Rising Waveform] and [Falling Waveform] keywords. These two keywords are strongly recommended if the output switching waveform of the buffer is significantly non-linear (this is the case with most 'controlled rise time' or 'graduated turn on' buffer designs). The use of these keywords is also indicated if the buffer incorporates a delay between the turning off of one output transistor and the turning on of the other (i.e. the V-T waveform contains a ledge).

Deleted: the

Deleted: This setup is the one described in IBIS versions 1.1 and 2.1, and is applicable for extracting rise and fall data for a standard single stage, push-pull TTL or CMOS buffer.¶

Deleted: 3.2

Deleted: -

Deleted: specific

Deleted:

Deleted: type

Deleted:

**Deleted:** Note that to avoid errors when trying to correlate later simulations with those used to extract rise/fall time information, use the same "time step" throughout the simulation and correlation procedure.

**Deleted:** generally required

Deleted: style

Deleted: pedestal

**Deleted:** Finally, the model creator may wish to include the V-T data directly so that the model itself includes it own verification feature. By including this 'golden waveform' the model user may perform a simulation with the buffer driving the same load as was used to generate the V-T tables. The results of this simulation should match the V-T waveform as given in the IBIS file, thereby verifying that the users simulator is producing the proper results.

When performing simulations to extract V-T data for the [Rising Waveform] and [Falling Waveform] keywords a variety of load circuits may be used, depending on the technology of the buffer. By selecting the proper load(s) and termination voltage(s), the turn-on time, turn-off time (and overlap between the two) of the pullup and pulldown stages of the buffer can be isolated and a more accurate behavioral model constructed.

A few recommended loads and waveforms are listed in Table 3.1 below.

| Technology                                 | # of<br>Waveforms | Notes   | Load Circuit and Waveform                                                                            |

|--------------------------------------------|-------------------|---------|------------------------------------------------------------------------------------------------------|

| Standard Push/Pull – CMOS                  | 4                 | (1)     | 1R + 1F driving 50 Ω to Vcc<br>1R + 1F driving 50 Ω to GND                                           |

| Standard Push/Pull – TTL                   | 8                 | (1)     | 1R + 1F driving 50 $\Omega$ to 3.5 $V$<br>1R + 1F driving 50 $\Omega$ to GND                         |

| Open Drain/Collector- CMOS,<br>TTL and GTL | 2                 | (1) (2) | 1R + 1F into manufacture <u>r</u> 's suggested<br>Vterm and Rterm (pullup resistor and<br>voltage)   |

| Open Source/Emitter – CMOS and TTL         | 2                 | (1)(2)  | 1R + 1F into manufacture <u>r</u> 's suggested<br>Vterm and Rterm (pulldown resistor and<br>voltage) |

| ECL                                        | 2                 | (1) (2) | 1R + 1F into manufacture <u>r</u> 's suggested<br>Vterm and Rterm (pulldown resistor and<br>voltage) |

*Note:*

(1)  $IR = one \ rising \ waveform, \ IF = one \ falling \ waveform$

(2) if recommended termination resistor is >100 ohms, include 1R +1F driving 50 ohms to Vterm

Table 3.1 - Recommended Load Circuits and Waveforms for V-T Data Extraction

#### Note:

Be aware that not all EDA tool vendors' simulation software will use all the V-T tables provided in the model. If in doubt, check with your EDA tool vendor.

In many cases, particularly for buffers with fast output transitions, the most appropriate load is a resistive value corresponding to the impedance of the system transmission lines the buffer will drive. For example, a buffer intended for use in a  $60~\Omega$  system may best be modeled using a  $60~\Omega$  V-T fixture load.

While supported by the IBIS specification, the use of reactive elements as V-T table loads is not recommended. A resistive load should be used wherever possible.

As with the simulations for ramp rate the slew rate of the <u>internal</u> driving waveform should match the internal slew rate of the technology. For meaningful results, all of the above rising and falling waveforms should be taken with the package lead parameters (R\_pin, L\_pin and C\_pin or R\_pkg, L\_pkg and C\_pkg) and fixture reactive elements (L\_fixture and C\_fixture) set to zero. As noted in the IBIS specification itself, all rising and falling waveforms <u>should</u> be time correlated. In other words, the rising (falling) edge data in each of the rising (falling) edge waveform tables must be entered with respect to a common reference <u>time</u> point on the input waveform used to stimulate the buffer,

Finally, some buffers may show slightly different rising and falling edge characteristics depending on how much time the buffer has had to settle from a previous output transition. Some projects may ask that the model creator extract ramp or V-T data from the second or third output transition in a series. Note, however, that all V-T table

Deleted: The intent is that by picking

**Deleted:** Following are the recommended loads and waveforms to collect, as specified by the various EDA tool vendors that support IBIS models.

Formatted Table

Deleted: ohms

Deleted: ohms

Deleted: v

Deleted: ohms

#### Formatted: Centered

Deleted: Table 1 – Recommended Load Circuits and Waveforms for V-T Data Extraction¶

Note:

(1)  $1R = one \ rising \ waveform, \ 1F = one \ falling \ waveform$

(2) if recommended termination resistor is >100 ohms, include 1R +1F driving 50 ohms to Vterm¶

**Deleted:** (The L\_fixture and C\_fixture parameters are included as parameters of the [Rising Waveform] and [Falling Waveform] keywords only for use in documenting a measurement setup or creating complex loads for simulator comparison and validation via a golden waveform.)

Deleted: it is critical that

#### Deleted: ¶

Deleted: In addition to the above recommended V-T tables, additional waveforms may be included for simulator validation purposes. These waveforms are referred to as 'golden waveforms' because their intent is to supply a reference waveform that the simulator attempts to match, not raw V-T data that the simulator uses to construct the behavioral model. Unlike the recommend loads above, the load circuits used to generate golden waveforms can include reactive elements. Two popular golden waveform loads are 50 ohms to (Vcc -GND) / 2, and a 50 pF load to ground. The model maker may also wish to include a waveform of the buffer driving a load that represents the typical load found in the buffer's intended application.¶

data should be extracted over a duration long enough to ensure steady-state DC behavior at the start and at the end of the data set.

Deleted:

#### 3.2.3 Minimum Time Step

As a rule of thumb, set the minimum time step so that there are between 30 to 50 data points in a rising or falling V-T table. If the V-T waveform is especially complex more points may be required (note however that the V-T waveform tables can contain no more than 100 points under IBIS 3.2; IBIS 4.0 permits up to 1000 points per V-

T\_table)\_

#### 3.2.4 Multi-Stage Drivers

Some buffer designs involve staged or graduated activation of the buffer as a function of time. For these buffers, a single set of V-T and I-V tables may only correctly describe one of the stages through which the buffer passes in any one transition. In this case, the [Driver Schedule] keyword may be used to combine several sets of V-T and I-V tables as a function of time. See <u>Advanced Keywords and Constructs</u> below.

# Deleted: [Driver Schedule] Deleted:

Field Code Changed

Deleted: waveform

required

Deleted:

**Deleted:** If the data is going to be reduced to dV/dt under the [Ramp] keyword then fewer points may be

Formatted: Font: Italic

Formatted: Heading 2

Formatted: Bullets and Numbering

#### 3.3 Extracting Buffer Capacitance (C\_comp)

The C\_comp parameter specifies the buffer's capacitance and can have a typical, minimum and maximum value.

C\_comp represents only the capacitance of the transistors, die pad and on-die interconnect for an individual buffer. It does not include package capacitance.

C comp is best generated using one of three methods:

- performing an AC or frequency sweep analysis of the buffer

- placing a resistive load at the output and calculating the RC charging or discharging time in a transient analysis

- driving the pad using a voltage source and dividing the source current by the dV/dt

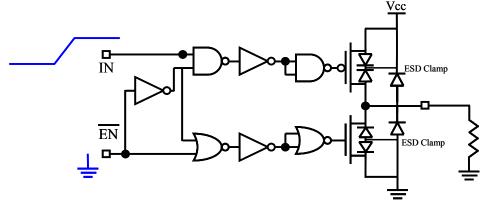

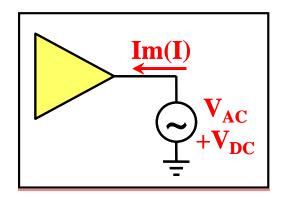

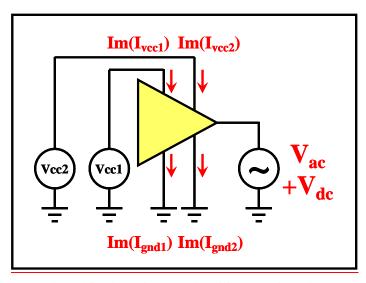

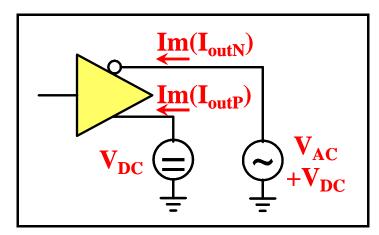

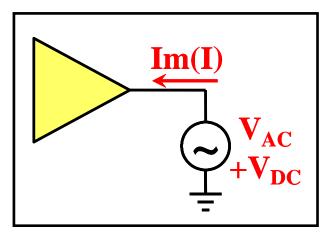

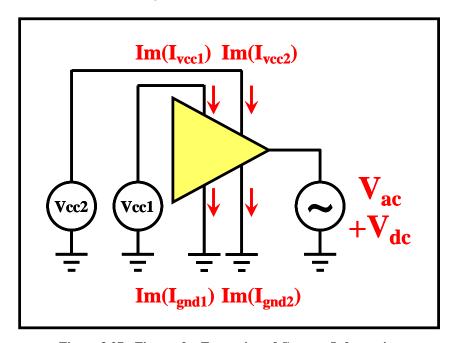

One way C\_comp can be measured for a single-ended buffer is by connecting an AC voltage source to its I/O pad and reading the imaginary part of the current in that AC source, as shown in the figure below.

Figure 3.3 – Fixture for Extraction of C\_comp Information

Formatted: Caption, Don't keep with next

Page 12 I/O Buffer Modeling Cookbook

IBIS Open Forum

The capacitance can be calculated using the following formula:

$$C_{comp} = -Im(I_{AC}) / (2 * \pi * f * V_{AC}),$$

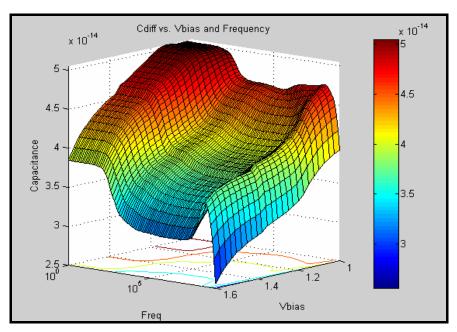

where Im(I<sub>AC</sub>) is the imaginary part of the current measured through the AC voltage source, f is the frequency of the AC source, V<sub>AC</sub> is the AC amplitude of the AC source. Please note that, for IBIS, the polarity is positive when the current flows into the part. Since we are interested in the current flowing into the buffer while measuring it in the AC source, the polarity of the current reading will have to be inverted. Therefore a negative sign is used in the above equation. If the capacitance of the buffer is affected by the DC voltage on the output pad (bias), one must also set the DC offset in the AC source to an appropriate value. Since the capacitance of most buffers usually varies with frequency as well as voltage, it is advisable to run a series of simulations in which both of these parameters are swept over a certain range. The results of such simulations can be displayed on a surface plot, as shown in Figure 4.20 below.

The C comp value used in the IBIS model should correspond to the most likely operating frequency and bias voltage of the buffer.

Figure 3.4 - Surface Plot of Buffer Capacitance versus Frequency and DC Bias Voltage

# Formatted: Caption, Centered Formatted: Normal Formatted: Heading 3 Formatted: Bullets and Numbering

# 3.3.1 Splitting C comp into C comp pullup, C comp pulldown, C comp power clamp, and C comp gnd clamp

The IBIS 4.0 specification introduced four additional C\_comp subparameters, C\_comp\_pullup, C\_comp\_pulldown, C\_comp\_power\_clamp, and C\_comp\_gnd\_clamp. These subparameters define the capacitance which can be measured between the I/O pad and any of the four supply references, [Pullup Reference], [Pulldown Reference], [Power Clamp Reference], and [GND Clamp Reference]. Breaking up the single C\_comp into these fractions is very important for power delivery network, and/or power/GND bounce simulations. This sections will describe how the values for these parameters can be obtained.

The circuit for measuring the split C\_comp values is very similar to the basic C\_comp simulation setup, except the current will be measured at the supply connections, instead of the I/O pad of the device under test, as shown in the figure below.

Figure 3.5 - Fixture for Extraction of C\_comp Information

The four capacitance values can be calculated with the same formula as before using the four current measurements shown above.

Please note that the four supply connections will not necessarily be available for all buffer designs. For this reason, the IBIS specification does not require any of these split (partial) C\_comp parameters, and the model maker should only use as many of them as necessary.

#### 3.4 Obtaining I-V and Switching Information via Lab Measurement

You can obtain I-V tables and rise/fall time information from the actual buffer, using the following lab setup:

- A programmable power supply with an output capable of sinking and sourcing current while maintaining the required output voltage. The output must be floating.

- A curve tracer

- A digital sampling oscilloscope with an appropriate bandwidth

- A low capacitance probe, e.g. FET

- A test fixture used for DC measurements

- A motherboard or specific test fixture used for transient measurements

- If available, a thermoelectronic hot/cold plate (a peltier device), to control die temperature

To obtain I-V table measurements, mount the component to be tested in the DC test fixture and connect the power and ground pins of the DUT to the programmable power supply. Attach the hot/cold plate to the component with a very thin layer of thermal grease and adjust the temperature as desired. Wait for the die to stabilize at the desired temperature. Select an output on the DUT in the desired state (high or low) and use the curve tracer to obtain the I-V characteristics of the output.

#### Notes

During curve tracing of a tri-statable output, the table contains both the transistor and the diode output characteristics. To obtain tables for the diodes alone, select and curve

Page 15

IBIS Open Forum I/O Buffer Modeling Cookbook

Formatted: Bullets and Numbering

Formatted: Bullets and Numbering

trace the output in its high impedance state. Buffers containing time-delayed feedback can produce bad results.

Reference the pullup and power clamp data to Vcc, as described in the IBIS specification. You can obtain this data directly by connecting the curve tracer's negative (reference) lead to the Vcc supply of the DUT, then setting the curve tracer for a negative sweep. Make sure no ground path connects back through the AC line between the component ground and power supply ground. For standard pulldown and clamp diode tables, attach the negative lead to the DUT's GND supply and use a positive sweep direction. Ensure the supply is floating.

Note that package and on-die parasitics, particularly resistive effects, can distort the I-V measurement data taken at pins relative to the behavior at the die pads expressed in IBIS models. Ensure that any voltage sweeps are performed as slowly as possible to avoid distortions from reactive elements. Obtain an estimate of the package resistivity and take this into consideration when obtaining the I-V data.

Similarly, thermal measurement at the package surface may not be reflective of at-die conditions.

The curve tracer may not be able to sweep the entire range required by the IBIS specification. In this case the model creator must extrapolate the tables to the required range.

Capturing rise/fall time data requires either a specific test fixture or a motherboard to which the DUT can be attached. Depending on the driver's edge rate, rise/fall time measurements may require an oscilloscope with a wide bandwidth. As with the I-V measurements, V-T data must not include package information when eventually included in the final IBIS file. Take into account the effect on the rise/fall times of the packaging, interconnect and any loading by the fixture. Use a probe with extremely low loading, such as a FET probe. The probe grounding should be as short as possible.

Capture data using the oscilloscope of the buffer driving a known load. Then, using the known packaging parameters and measured I-V tables, construct a simulation model of the buffer using an initial estimate of the rise/fall time. With an IBIS simulator, adjust the rise/fall times in the model until the simulation results match the oscilloscope waveforms. For greater control, lift the pin under test from any load other than the scope probe and simulate with a package and probe model.

#### 4.0 Extracting the Data - Differential Buffers

#### 4.1 Introduction

Today's high-speed designs make increasing use of various kinds of differential buffers and signaling techniques. Unfortunately the related terminology is not always defined unambiguously. Therefore this chapter will begin with a short overview of the fundamental concepts of differential and single-ended signaling, and the basic operation of differential drivers and receivers. These principles are essential to understanding the process for extracting data from differential buffer designs for IBIS.

The main difference between differential and <u>single-ended</u> signaling is very closely related to how voltages and/or currents are observed by the receiver and/or generated by the driver. <u>From basic physics a voltage can</u> only be measured between two points <u>(there is no such thing as a voltage of a single point)</u>. Similarly, current makes only sense when we talk about a path (or branch), through which current can flow. Since a current path is basically an electrical connection between two points, a relationship between voltage and current can be easily

Deleted: ¶

Formatted: Heading 1

Formatted: Bullets and Numbering

Formatted: Heading 2

Formatted: Bullets and Numbering

Deleted: single ended

Deleted: In order to

Deleted: IBIS model making

Deleted: of Deleted: s

**Deleted:** it is very important to understand these basic principles.

Deleted: single ended

**Deleted:** We should all remember f

**Deleted:** electronics or **Deleted:** courses that

Deleted:

Deleted: There

established. From this perspective, all voltage and current measurements or observations are differential in nature, because they involve <u>a relationship between</u> two distinct points in space. These principles are valid regardless of whether the voltages and currents we are observing represent signals or power.

Deleted: c

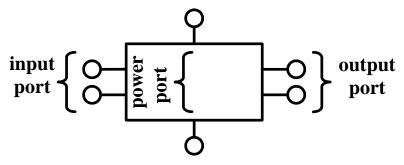

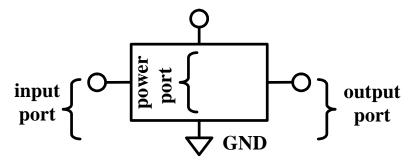

The simplest circuit, having an input, output and power supply port, will need a total of six terminals if each of these ports are to be kept independent (or isolated) from each other for analysis purposes. However, the usage of a common reference can reduce the total number of terminals to just four. In practical designs, such simplifications can provide significant cost savings and reduction of complexity, especially on large designs. Whether or not such simplifications can be done depends on many different requirements, such as safety, cost, and performance, just to name a few.

**Deleted:** Most electronic circuits are designed to amplify and/or process signals. To do this, they consume power.

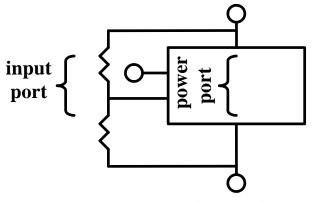

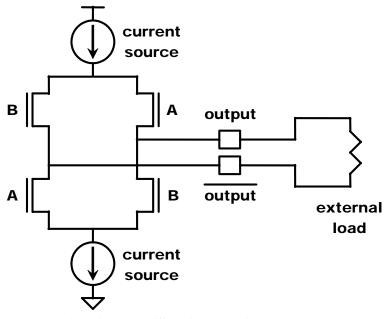

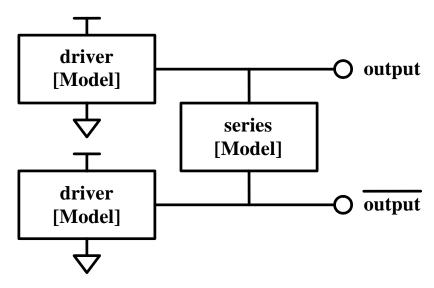

Figure 4.1 – Device with Independent Input, Output and Power Supply Ports

Deleted: 3.3

Figure 4.2 - Device with Ports Using Common Ground

Deleted: 3.4

The determining factor between differential and single-ended systems is the referencing scheme. When studying a transmission line, we need to find out whether its reference is a power or ground plane, or another "signal" trace. A single-ended transmission line has only one signal trace whose reference is some sort of a power or ground plane that is common to the entire design. A differential transmission line has "two signal traces", either one of which can be considered as the reference of the other. When studying a buffer, we need to ask: "What are the two terminals of the input or output port?" A differential buffer's input or output port consists of two dedicated terminals. Neither of these terminals is common with the power or ground terminals. On the other hand, a single-ended buffer's input or output port consists of only one dedicated terminal. The other terminal is shared with either the power or ground terminal.

Deleted: vs.

Deleted: single ended

Deleted: basically

Deleted: single ended

Deleted: '

Deleted: single ended

Deleted: ot

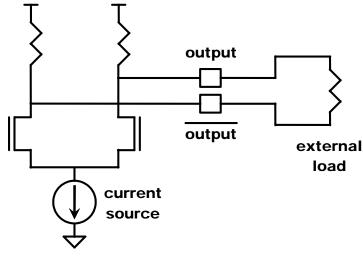

In summary, we can think of a differential signal as information <u>sent with</u> its own reference. A <u>single-ended</u> signal, on the other hand, does not include a reference because it is assumed to be available either as a common power or ground connection, or as a locally generated reference which is derived from a common power or ground connection. The following figure illustrates an input port with a locally generated reference.

Deleted: that carries

Deleted: single ended

Figure 4.3 – Input Port with Locally Generated Reference

Deleted: 3.5

Using the above criteria of referencing, there are two major categories for signaling schemes: differential and single-ended. However, from a buffer designer's perspective we can actually define three categories. In this document we will refer to these as true differential, half-differential, and single-ended drivers and receivers.

Each of these is reviewed below.

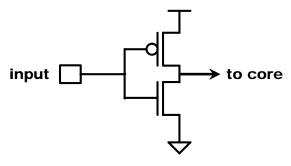

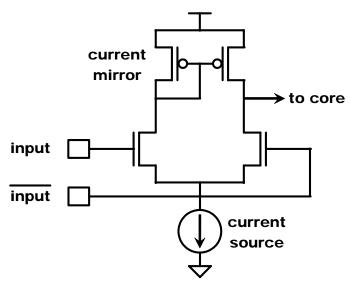

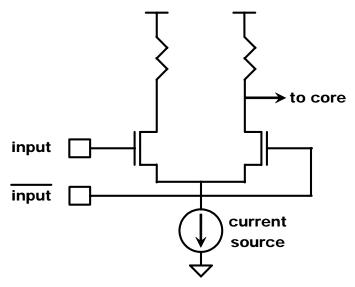

#### 4.2 Differential Receivers

In order to appreciate the operation of differential receivers, single-ended receivers must be understood. A single-ended receiver is usually implemented as transistors connected between the input and ground and/or between the input and power supply terminals. If the receiver is built using field effect transistors (FET), the transistor will usually detect the signal as a voltage that is observed between the input terminal and the power and/or ground supply rails. If the receiver is built with bipolar junction transistors (BJT), the transistor will usually detect the signal as a current flow between the input terminal and the ground and/or power supply rails. In short, the input signal is evaluated with respect to one or both of the supply rails. Figure 4.4 below illustrates a simple receiver using CMOS technology.

Please be aware, that the schematics used as illustrations <u>below</u> are provided only to give a better understanding of the discussion at hand. <u>The examples are not intended as exhaustive in covering the vast abundance of possible circuit designs and configurations.</u>

Deleted: single ended

Deleted: half differential

Deleted: single ended

**Deleted:** Let's review each of these, starting with the discussion of receivers.

Formatted: Heading 2

Formatted: Bullets and Numbering

**Deleted:** it is useful to understand how single ended

Deleted: work

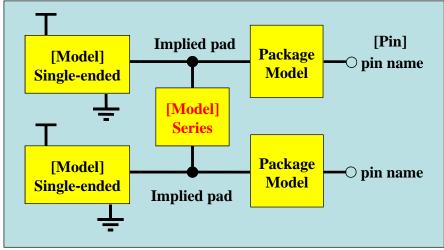

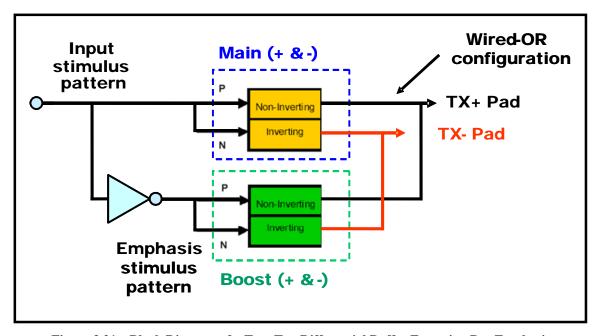

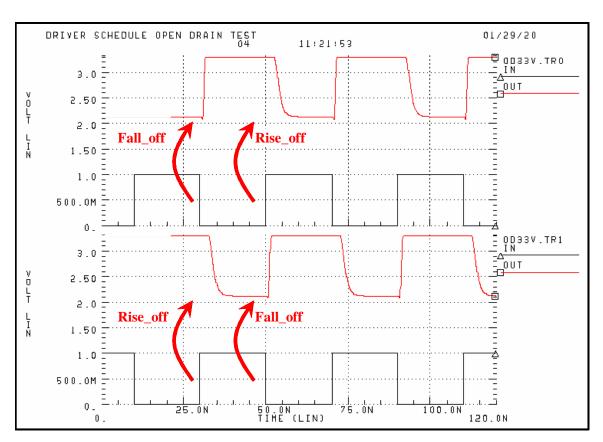

Deleted: single ended