# SystemVerilog 3.1 C/C++ Interface API Reference Manual DRAFT

**Version 0.7**

March 25, 2003

Copyright<sup>©</sup> 2003 by Accellera. All rights reserved.

No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means — graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems — without the prior approval of Accellera.

Additional copies of this manual may be purchased by contacting Accellera at the address shown below.

Notices

The information contained in this manual represents the definition of the SystemVerilog 3.1 C/C++ API as reviewed and released by Accellera in March 2003.

Accellera reserves the right to make changes to the SystemVerilog 3.1 C/C++ API and this manual in subsequent revisions and makes no warranties whatsoever with respect to the completeness, accuracy, or applicability of the information in this manual, when used for production design and/or development.

Accellera does not endorse any particular simulator or other CAE tool that is based on the SystemVerilog 3.1 C/C++ API.

Suggestions for improvements to the SystemVerilog 3.1 C/C++ API and/or to this manual are welcome. They should be sent to the SystemVerilog 3.1 C/C++ API email reflector

sv-cc@server.eda.org

or to the address below.

The current Working Group's website address is

www.eda.org/sv-cc

Information about Accellera and membership enrollment can be obtained by inquiring at the address below.

Published as: SCE-MI Reference Manual

Version 0.7, March 25, 2003.

Published by: Accellera

1370 Trancas Street, #163

Napa, CA 94558

Phone: (707) 251-9977 Fax: (707) 251-9877

Printed in the United States of America.

Verilog<sup>®</sup> is a registered trademark of Cadence Design Systems, Inc.

Mentor Graphics

| I | SystemVerilog 3.1/draft 4 |

|---|---------------------------|

|   | SystemVerilog 3.1/draft 4 |

\*\*Revise this\*\*

Revision history:

Version 0.3, 1st draft 02/26/03

Version 0.5 03/20/2003

# **Table of Contents**

| Section 1<br>DirectC in | nterface1                                         |      |

|-------------------------|---------------------------------------------------|------|

| 1.1                     | Introduction                                      | 1    |

| 1.2                     | Two layers of the DirectC interface               |      |

| 1.3                     | Required properties of external functions         |      |

| 1.4                     | External declarations.                            |      |

| 1.5                     | External function calls                           |      |

| 1.6                     | Argument passing                                  |      |

| 1.7                     | Exported functions                                |      |

| Section 2               |                                                   |      |

|                         | erilog Assertion API11                            |      |

| 2.1                     | Requirements                                      | 11   |

| 2.2                     | Extensions to VPI enumerations                    | 11   |

| 2.3                     | Static information                                | 13   |

| 2.4                     | Dynamic information                               | 15   |

| 2.5                     | Control functions                                 | 18   |

| Section 3               |                                                   |      |

|                         | erilog Coverage API21                             |      |

| 3.1                     | Requirements                                      | 2.1  |

| 3.2                     | SystemVerilog real-time coverage access           |      |

| 3.3                     | FSM recognition                                   |      |

| 3.4                     | VPI coverage extensions                           |      |

| Annex A                 |                                                   |      |

| DirectC C               | C-layer31                                         |      |

| A.1                     | Overview                                          | . 31 |

| A.2                     | Naming conventions                                |      |

| A.3                     | . <del>.</del> .                                  |      |

|                         | Include files.                                    |      |

| A.5                     | Semantic constraints                              | . 33 |

| A.6                     | Data types                                        | . 35 |

| A.7                     | Argument passing modes                            | . 38 |

| A.8                     | Context functions                                 |      |

| A.9                     | Include files                                     | . 42 |

| A.10                    | Arrays                                            | . 46 |

| A.11                    | Open arrays                                       | . 47 |

| Annex B                 |                                                   |      |

| Include fi              | les55                                             |      |

| B.1                     | Binary-level compatibility include file svc.h     | 55   |

| B.2                     | Source-level compatibility include file svc_src.h |      |

| Annex C                 |                                                   |      |

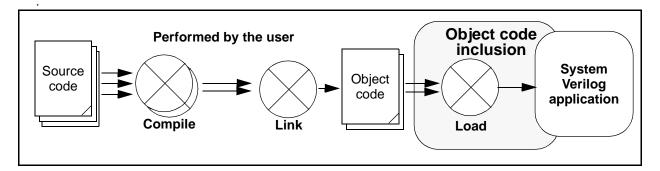

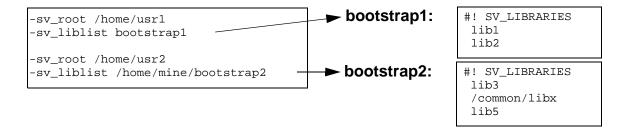

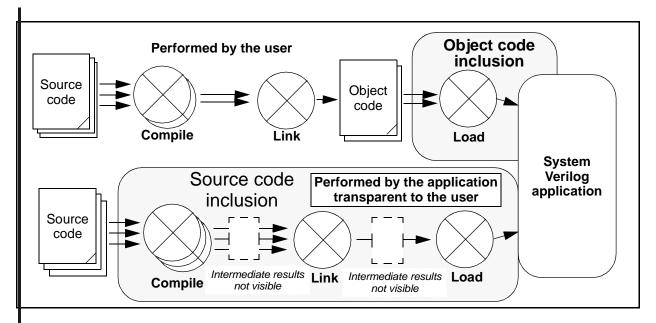

| Inclusion               | of Foreign Language Code59                        |      |

| C.1 | Overview              | 59 |

|-----|-----------------------|----|

|     | Location independence |    |

| C.3 | Object code inclusion | 60 |

|     |                       | 62 |

# Section 1 Direct Programming Interface (DPI)

This chapter highlights the Direct Programming Interface and provides a detailed description of the System-Verilog-la pf the interface. The C-layer is defined in Annex A.

# 1.1 Overview

DPI is an interface between SystemVerilog and a foreign programming language. It consists of two separated layers: the SystemVerilog-layer and a foreign language layer. Both sides of DPI are fully isolated. Which programming language is actually used as the foreign language is transparent and irrelevant for the SystemVerilog side of this interface. Neither SystemVerilog compiler nor the foreign language compiler is required to analyze the source code in the other's language. Different programming languages can be used and supported with the same intact SystemVerilog-layer. For now, however, SystemVerilog 3.1 defines a foreign language layer only for the C programming language. See Annex A for more details.

The motivation for this interface is two-fold. The methodological requirement is that the interface should allow to build a heterogeneous system (a design or a testbench) in which some components may be written in a language; (or more languages) other than SystemVerilog, hereinafter called the foreign language. On the other hand, there is also a practical need for an easy and efficient way to connect the property of the context of the co

DPI follows the principle of a black box: the specification and the implementation of a component is clearly separated and the actual implementation is transparent to the rest of the system. Therefore, the actual programming language of the implementation is also transparent, with the stipulation that it must have C linkage semantics. The separation between SystemVerilog code and the foreign language is based on using functions as the natural encapsulation unit in SystemVerilog. By and large, any function can be treated as a black box and implemented either in SystemVerilog or in the foreign language in a transparent way, without changing its calls.

#### 1.1.1 Functions

DPI allows direct function inter-language function calls (ILFC's) between the languages either side of the interface. Specifically, functions implemented in a foreign language can be called from Specifically, functions implemented in a foreign language can be called from Specifically, functions are referred to as *imported functions*. System Verilog functions that are to be called from a foreign code shall be specified in export declarations (see section 1.6 for more details). DPI allows for passing System Verilog data between the two domains through function arguments and results. There is no intrinsic overhead in this interface.

All functions used in DPI are assumed to complete their execution instantly and consume 0 (zero) simulation time, just as normal SV functions. DPI provides no means of synchronization other than by data exchange and explicit transfer of control.

Every imported function needs to be declared. A declaration of an imported function is referred to as an *import declaration*. Import declarations are very similar to SystemVerilog function declarations. External declarations shall occur in any location that is legal for a native SystemVerilog function declaration. Specifically, this means in module, interface, program, or generate scope. Multiple declarations of the same nal function are not allowed in the same scope. However, it is allowable to declare several extension that are all mapped to the same cname. (This can be a useful way of providing different description are not allowed in the same scope. However, it is allowable to declare several extension that are all mapped to the same cname. (This can be a useful way of providing different descriptions or more formal input, output, and inout arguments, and they can return a lit or be defined as void functions.

DPI is entirely based entirely upon SystemVerilog constructs. The usage of imported functions is identical as for native temVerilog functions. With few exceptions imported functions and native functions are mutually exchange acre. Calls sites of imported functions are indistinguishable from calls of SystemVerilog functions. This facilitates eas \_\_\_\_\_\_ use and minimizes the learning curve.

# 1.1.2 Data types

SystemVerilog data types are the sole data types that can cross the boundary between SystemVerilog and a foreign language in either direction (i.e., when a gign function is called from SystemVerilog code or an exported SystemVerilog function is called from a beign code). It is not possible to import the data types or directly use the type syntax from another language. With with some restrictions and with some notational extensions, most SystemVerilog data types are allowed in the DPI interface. Function result types are restricted to small values, however (see section 1.4.5).

Formal arguments of an imported function can be specified as open arrays. A formal argument is an *open array* when a range of one or more of its dimensions, packed or unpacked, is unspecified (denoted by using empty square brackets ([])). This is solely a relaxation of the argument-matching rules. An actual argument shall match the formal one regardless of the range(s) for its corresponding dimension(s), which facilitates writing regeneral code that can handle SystemVerilog arrays of different sizes. See section 1.4.6.1.

# 1.1.2.1 Data representation

DPI does not add any constraints on how SystemVerilog-specific data types are actually implemented. Optimal representation can be platform dependent. The layout of 2- or 4-state packed structures and arrays is implementation- and platform-dependent.

The implementation (representation and layout) of 4-state values, structures, and arrays is irrelevant for SystemVerilog semantics, and can only impact the foreign side of the interface.

# 1.2 Two layers of the DPI interface

DPI consists of two separate layers: the SystemVerilog-layer does not depend on which programming language actually used as the foreign language. Although different programming languages can be supported and used with the intact SystemVerilog-layer, SystemVerilog 3.1 defines a foreign language layer only for the C programming language. Nevertheless, SystemVerilog code shall look identical and its semantics shall be unchanged for any foreign language layer.

#### 1.2.1 DPI SystemVerilog-layer

The SystemVerilog side of DPI does not depend on the foreign programming language. In particular, the actual function call protocol and argument passing mechanisms used in the foreign language are transparent and irrelevant to SystemVerilog. SystemVerilog code shall look identical regardless of what code the foreign side of the interface is using. The semantics of the SystemVerilog side of the interface is independent from the foreign side of the interface.

This chapter does not constitute a complete interface specification. It only describes the functionality, semantics and syntax of the SystemVerilog-layer of the interface. The other half of the interface, the foreign language layer, defines the actual argument passing mechanism and the methods to access (read/write) formal arguments from the foreign code. See Annex A for more details.

#### 1.2.2 DPI foreign language layer

The foreign language layer of the interface (which is transparent to SystemVerilog) shall specify how actual arguments are passed, how they can be accessed from the foreign code, how SystemVerilog-specific data types (such as logic and packed) are represented, and how to translate them to and from some predefined C-like types.

The data types allowed for formal arguments and results of imported functions or exported functions are generally SystemVerilog types (with some restrictions and with notational extensions for open arrays). The user is responsible for specifying in their foreign code the native types equivalent to the SystemVerilog types used in imported declarations or export declarations. EDA Software tools, like a SystemVerilog compiler, can facilitate the mapping of SystemVerilog types onto foreign native types by generating the appropriate function headers.

The SystemVerilog compiler or simulator shall generate and/or use the function call protocol and argument passing mechanisms required for the intended foreign language layer. The same SystemVerilog code (compiled accordingly) shall be usable with different foreign language layers, regardless of the data access method assumed in a specific layer. Annex A defines DPI foreign language layer for the C programming language.

# 1.3 Global name space of imported and exported functions

Every function imported to SystemVerilog must eventually resolve to a global symbol. Similarly, every function exported from SystemVerilog defines a global symbol. Thus the functions imported to and exported from SystemVerilog have their own global name space, different from \$root name space. Global names of imported and exported functions must be unique (no overloading is allowed) and shall follow C conventions for naming. Exported and imported functions, however, may be declared with local SystemVerilog names. Import and export declarations allow to space a global name for a function in a global name is not explicitly give will be the same as the SystemVerilog name. Example:

```

export "DPI" foo_plus = function \foo+ ; // "foo+" exported as "foo_plus"

export "DPI" function foo; // "foo" exported under its own name

import "DPI" init_1 = function void \init[1] (); // "init_1" is a global name

```

# [Syntactical/levical rules for cname should allow arbitrary C identifier, including those clashing with SV keywords.]

The same global function may be referred to in multiple import declarations in different scopes or/and with different SystemVerilog names, see section 1.4.4. Each exported function must have a unique global name.

# 1.4 Imported functions

The usage of imported functions is similar as for native System Verilog functions.

# 1.4.1 Required properties of imported functions - semantica nstraints

This section defines the semantic constraints imposed on imported functions. Some semantic restrictions are shared by all the ported functions. Other restrictions depend on whether the special properties pure (see section 1.4.2) or ported functions. Other restrictions depend on whether the special properties pure (see section 1.4.2) are specified an imported function. A System Verilog compiler is not able to verify that those restrictions are observed and if those restrictions are not satisfied, the

specified as pure. This will usually allow for more optimizations and thus may result in improved simulation performance. Section section 1.4.2 details the rules that must be obeyed by pure functions.

An imported function that is intended to call exported functions or to access SystemVerilog data objects other then its actual arguments (e.g. via VPI or PLI calls) must be specified as context. Calls of context functions are specially instrumented and may impair SystemVerilog compiler optimizations; therefore simulation performance may decrease in the property is used when not necessary. A function not specified as context shall not read or any data objects from SystemVerilog other then its actual arguments. For functions not specified as context, the effects of calling PLI, VPI, or exported SystemVerilog functions can be unpredictable and can lead to unexpected behavior; such calls can even crash. Section section 1.4.3 details the restrictions that must be obeyed by non-context functions.

# 1.4.1.4 Memory management

The memory spaces owned and allocated by the foreign code and SystemVerilog code are disjoined. Each side is responsible for its own allocated memory. Specifically, an imported function shall not free the memory allocated by SystemVerilog code (or the SystemVerilog compiler) nor expect SystemVerilog code to free the memory allocated by the foreign code (or the foreign compiler). This does not exclude scenarios where foreign code allocates a block of memory, then passes a handle (i.e., a pointer) to that block to SystemVerilog code, which in turn calls an imported function (e.g. C standard function free) which directly or indirectly frees that block.

NOTE—In this last scenario, a block of memory is allocated and freed in the foreign code, even when the standard functions malloc and free are called directly from SystemVerilog code.

#### 1.4.2 Pure functions

A pure function call can be safely eliminated if its result is not needed or if the previous result for the same values of input arguments is available somehow and can be reused without needing to recalculate. Only non-void functions with no output or input arguments can be specified as pure. Functions specified as pure shall have no side effects whatsoever; their results need to depend solely on the values of their input arguments. Calls to such functions can be removed by SystemVerilog compiler optimizations or replaced with the values previously computed for the same values of the input arguments.

Specifically, a pure function is assumed not to directly or indirectly (i.e., by calling other functions):

- perform any file operations

- read or write anything in the broadest possible meaning, includes i/o, environment variables, objects from the operating system or from the program or other processes, shared memory, sockets, etc.

- access any persistent data, like global or static variables.

If a pure function does not obey the above restrictions, SystemVerilog compiler optimizations can lead to unexpected behavior, due to eliminated calls or incorrect results being used.

#### 1.4.3 Context functions

Some DPI external functions require that the context of their call is known. It takes special instrumentation of their call instances to provide such context; for example, an internal variable referring to the "current instance" might need to be set. To avoid any unnecessary overhead, external function calls in SystemVerilog code are not instrumented unless the external function is specified as context in its SystemVerilog declaration.

All DPI export functions require that the context of their call is known. This occurs since SystemVerilog function declarations always occur in instantiable scopes, hence allowing a multiplicity of unique function instances in the simulator's elaborated database. Thus, there is no such thing as a non-context export function.

For the sake of simulation performance, an external function call shall not block SystemVerilog compiler optimizations. An external function not specified as context shall not access any data objects from SystemVerilog other than its actual arguments. Only the actual arguments can be affected (read or written) by its call. Therefore, a call of non-context function is not a barrier for optimizations. A context external function,

however, can access (read or write) any SystemVerilog data objects by calling PLI/VPI, or by calling an embedded export function. Therefore, a call to a context function is a barrier for SystemVerilog compiler optimizations.

Only calls of context external functions are properly instrumented and cause conservative optimizations; therefore, only those functions can safely call all functions from other APIs, including PLI and VPI functions or exported SystemVerilog functions. For external functions not specified as context, the effects of calling PLI, VPI, or SystemVerilog functions can be unpredictable and such calls can crash if the callee requires a context that has not been properly set. However note that declaring an import context function does not automatically make any other simulator interface automatically available. For VPI access (or any other interface access) to be possible, the appropriate implementation defined mechanism must still be used to enable these interface(s). Note also that DPI calls do not automatically create or provide any handles or any special environment that may be needed by those other interfaces. It is the user's responsibility to create, manage or otherwise manipulate the required handles/environment(s) needed by the other interfaces.

Special DPI utility functions exist that allow external functions to retrieve and operate on their context. See Annex A for more details.

# 1.4.4 Import declarations

# Also cross-reference to section 10.6, import and export functions

Each imported function shall be declared. Such declaration are referred to as *import declarations*. The syntax of an import declaration is similar to the syntax of SystemVerilog function prototypes.

Imported functions are similar to SystemVerilog functions. Imported functions can have zero or more formal input, output, and input arguments. Imported functions can return a result or be defined as void functions.

#### **Syntax:**

import\_dpi\_decl ::= import "DPI" [pure/context] [cname=] <named\_function\_proto>;

where named\_function\_proto is as defined in section A.2.6 of SV 3.1 BNF

#### /\* EDITOR: UPDATE ABOVE CROSS-REFERENCE AS NECESSARY \*/

An import declaration specifies the function name, function result type, and types and directions of formal arguments. It can also provide optional default values for formal arguments. Formal argument names are optional unless argument passing by name is needed. An external declaration can also specify an optional function property: context or pure.

Note that an import declaration is equivalent to defining a function of that name in the SV scope in which the import declaration occurs, and thus multiple imports of the same function name into the same scope are forbidden.

cname provides the linkage name for this function in the foreign language. If not provided, this defaults to the same identifier as the SV function name. In either case, this linkage name must conform to C identifier syntax, specifically, must start with a letter or underscore, and may be followed by alphanumeric characters or underscores. An error will occur if the cname, either directly or indirectly, does not conform to these rules.

For any given cname (whether explicitly defined with cname=, or automatically determined from the function name), all declarations, regardless of scope, **must** have exactly the same type signature. The type signature includes the return type, the number, order and types of each and every argument. Type includes dimensions and bounds of any arrays or array dimensions. Signature also includes the pure/context qualifiers that may be associated with an extension.

Note that multiple declarations of the same external language function in different scopes may vary argument names and default values, provided the type con bility constraints are met.

A formal argument name is required to separate the packed and the unpacked dimensions of an array.

The qualifier ref can not be used in external declarations. The actual implementation of argument passing depends solely on the foreign language layer and its implementation and shall be transparent to the SystemVerilog side of the interface.

The following are examples of external declarations.

#### 1.4.5 Function result

Function result types are restricted to small values. The following SystemVerilog data types are allowed for imported function results:

- void, byte, shortint, int, longint, real, shortreal, handle, and string

- packed bit arrays up to 32 bits and all types that are eventually equivalent to packed bit arrays up to 32 bits.

The same restrictions apply for the result types of exported functions.

# 1.4.6 Types of formal arguments

With some restrictions and with notational extensions, all SystemVerilog data types are allowed for formal arguments of imported functions.

- Enumerated data types are not supported directly. Instead, an enumerated data type is interpreted as the type associated with that enumerated type.

- SystemVerilog does not specify the actual memory representation of packed structures or any arrays, packed or unpacked. Unpacked structures have an implementation-dependent packing, normally matching the C compiler.

- The actual memory representation of SystemVerilog data types is transparent for SystemVerilog semantics and irrelevant for SystemVerilog code. It can be relevant for the foreign language code on the other side of the interface, however; a particular representation of the SystemVerilog data types can be assumed. This shall not restrict the types of formal arguments of imported functions, with the exception of unpacked arrays. SystemVerilog implementation can restrict which SystemVerilog unpacked arrays are passed as actual arguments for a formal argument which is a sized array, although they can be always passed for an unsized (i.e., open) array. Therefore, the correctness of an actual argument might be implementation-dependent. Nevertheless, an open array provides an implementation-independent solution.

# 1.4.6.1 Open arrays

The size of the packed dimension, the unpacked dimension, or both dimensions can remain unspecified; such

cases are referred to as *open arrays* (or unsized arrays). These arrays allow the use of generic code to handle different sizes.

Formal arguments of imported functions can be specified as open arrays. (Exported SystemVerilog functions cannot have formal arguments specified as open arrays.) A formal argument is an *open array* when a range of one or more of its dimensions is unspecified (denoted by using square brackets ([])). This is solely a relaxation of the argument-matching rules. An actual argument shall match the formal one regardless of the range(s) for its corresponding dimension(s), which facilitates writing a mentage general code that can handle SystemVerilog arrays of different sizes.

Although the packed part of an array can have an arbitrary number of dimensions, in the case of open arrays only a single dimension is allowed for the packed part. This is not very restrictive, however, since any packed type is eventually equivalent to one-dimensional packed array. The number of unpacked dimensions is not restricted.

If a formal argument is specified as an open array with a range of its packed or one or more of its unpacked dimensions unspecified, then the actual argument shall match the formal one — regardless of its dimensions and sizes of its linearized packed or unpacked dimensions corresponding to an unspecified range of the formal argument, respectively.

Here are examples of types of formal arguments (empty square brackets [] denote open array):

```

logic

bit [8:1]

bit[]

bit[7:0] b8x10 [1:10] // b8x10 is a formal arg name

logic [31:0] 132x [] // 132x is a formal arg name

logic [] lx3 [3:1] // lx3 is a formal arg name

bit [] an_unsized_array [] // an_unsized_array is a formal arg name

```

Example of complete import declarations:

```

import "DPI" function void foo(input logic [127:0]);

import "DPI" function void boo(logic [127:0] i []); // open array of 128-bit

```

The following example shows the use of open arrays for different sizes of actual arguments:

#### 1.5 Imported function calls

The usage of imported functions is identical as for native SystemVerilog functions. The usage and syntax for calling imported functions is identical as for native SystemVerilog functions. Specifically, arguments with default values can be omitted from the call; arguments can be passed by name, if all fomal arguments are

# 1.5.1 Argument passing

Arguments passing for imported functions is ruled by SIWYG principle: What You Specify Is What You Get,

see section 1.5.1.1. The evaluation order of formal arguments follows general SystemVerilog rules. Directions and types of formal arguments of imported functions are never coerced, regardless of the actual argument.

Argument compatibility and coercion rules are the same as for native SystemVerilog functions. If a coercion is needed, a temporary variable is created and passed as the actual argument. For input and inout arguments, the temporary variable is initialized with the value of actual argument with the appropriate coercion; for output or inout arguments, the value of the temporary variable is assigned to the actual argument with the appropriate conversion. The assignments between a temporary and the actual argument follow general System-Verilog rules for assignments and automatic coercion.

On the SystemVerilog side of the interface, the values of actual arguments for formal input arguments of imported functions shall not be affected by the callee; the initial values of formal output arguments of imported functions are unspecified (and can be implementation-dependent), and the necessary coercions, if any, are applied as for assignments. imported functions shall not modify the values of their input arguments.

For the SystemVerilog side of the interface, the semantics of arguments passing is as if input arguments are passed by *copy-in*, output arguments are passed by *copy-out*, and inout arguments were passed by *copy-in*, *copy-out*. The terms *copy-in* and *copy-out* do not impose the actual implementation, they refer only to "hypothetical assignment".

The actual implementation of argument passing is transparent to the SystemVerilog side of the interface. In particular, it is transparent to SystemVerilog whether an argument is actually passed *by value* or *by reference*. The actual argument passing mechanism is defined in the foreign language layer. See Annex A for more details.

# 1.5.1.1 "What You Specify Is What You Get" principle

The principle "What You Specify Is What You Get" guarantees the types of formal arguments of imported functions — an actual argument is guaranteed to be of the type specified for the formal argument, with the exception of open arrays (for which unspecified ranges are statically unknown). Formal arguments, other than open arrays, are fully defined by extended arrays exactly as specified in the external defined action. Only the declaration site of the imported function is relevant for such formal arguments.

The mal arguments defined as open arrays have the size and ranges of the all argument, i.e., have the range of packed or unpacked arrays exactly as that of the actual argument. The lized ranges of open arrays are determined at a call site; the rest of type information is specified at the external declaration.

So, if a formal argument is declared as bit [15:8] b [], then it is the external declaration which specifies the formal argument is an unpacked array of packed bit array with bounds 15 to 8, while the actual argument used at a particular call site defines the bounds for the unpacked part for that call.

# 1.5.2 Value changes for output and inout arguments

The SystemVerilog simulator is responsible for handling value changes for output and inout arguments. Such changes shall be detected and handled after control returns from imported functions to SystemVerilog code.

For output and inout arguments, the value propagation (i.e., value change events) happens as if an actual argument was assigned a formal argument immediately after control returns from imported functions. If there is more than one argument, the order of such assignments and the related value change propagation follows general SystemVerilog rules.

#### 1.6 Exported functions

DPI allows calling SystemVerilog functions from another language. However, such functions must adhere to the same restrictions as are imposed on imported functions.

SystemVerilog functions that can be called from a fewer need to be specified in export declarations. Export declarations are allowed to occur only in the open in which the function being exported is defined. Only one export declaration per function is allowed in a given scope.

Note that class member functions may not be exported, but all other SystemVerilog functions may be exported.

Similar to import declarations, export declarations can define an optional cname to be used in the foreign language when calling an exported function.

#### Syntax:

```

export_dpi_decl ::= export "DPI" [cname=] function fname;

```

cname is optional here, it defaults to fname. Note that all export functions are always *context* functions; thus there is no need to attribute them as such with special syntax. Export functions may not be attributed as *pure*, either.

# Section 2 SystemVerilog Assertion API

This chapter defines the Assertion Application Programming Interface (API) in SystemVerilog 3.1/draft 2.

# 2.1 Requirements

SystemVerilog 3.1/draft 2 provides assertion capabilities to enable:

— a user's C code to react to assertion events,

# 2.2.2 Object properties

This section lists the object property VPI calls. The VPI reserved range for these call is 700 - 729.

```

/* Directives as properties */

#define vpiSequenceAssertion 701

#define vpiAssertAssertion 702

#define vpiAssumeAssertion 703

#define vpiRestrictAssertion 704

#define vpiCoverAssertion 705

#define vpiCheckAssertion 705 /* inlined behavior assertion */

#define vpiOtherDirectiveAssertion 706 /* placeholder for other assertion directive */

```

#### 2.2.3 Callbacks

This section lists the system callbacks. The VPI reserved range for these call is 700 - 719.

#### 1) Assertion

```

#define cbAssertionStart

700

#define cbAssertionSuccess

701

#define cbAssertionFailure

702

#define cbAssertionStepSuccess 703

#define cbAssertionStepFailure 704

#define cbAssertionDisable

705

#define cbAssertionEnable

706

#define cbAssertionReset

707

#define cbAssertionKill

708

```

#### 2) "Assertion system"

```

#define cbAssertionSysInitialized709

#define cbAssertionSysStart 710

#define cbAssertionSysStop 711

#define cbAssertionSysEnd 712

#define cbAssertionSysReset 713

```

#### 2.2.4 Control constants

This section lists the system control constant callbacks. The VPI reserved range for these call is 730 - 759.

# 1) Assertion

```

#define vpiAssertionDisable 730

#define vpiAssertionEnable 731

#define vpiAssertionReset 732

#define vpiAssertionKill 733

#define vpiAssertionEnableStep 734

#define vpiAssertionDisableStep 735

```

#### 2) Assertion stepping

```

#define vpiAssertionClockSteps 736

```

# 3) "Assertion system"

```

#define vpiAssertionSysStart 737

#define vpiAssertionSysStop 738

#define vpiAssertionSysEnd 739

```

```

#define vpiAssertionSysReset 740

```

#### 2.3 Static information

This section defines how to obtain assertion handles and other static assertion information.

## 2.3.1 Obtaining assertion handles

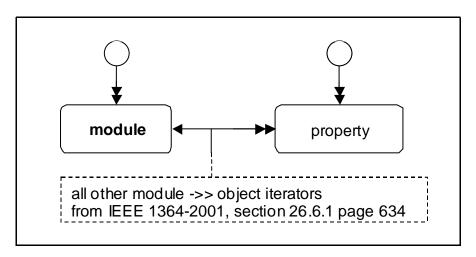

SystemVerilog 3.1/draft 2 extends the VPI module iterator model (i.e., the instance) to encompass assertions, as shown in Figure 2-1—. \*\*Revise this xref w/ Stu; also check/revise variable settings, etc.\*\*

The following steps highlight how to obtain the assertion handles for named assertions.

Figure 2-1—Encompassing assertions

1) Iterate all assertions in the design: use a NULL reference handle (ref) to vpi\_iterate(), e.g.,

```

itr = vpi_iterate(vpiAssertion, NULL);

while (assertion = vpi_scan(itr)) {

/* process assertion */

}

```

2) Iterate all assertions in an instance: pass the appropriate instance handle as a reference handle to vpi\_iterate(), e.g.,

```

itr = vpi_iterate(vpiAssertion, instanceHandle);

while (assertion = vpi_scan(itr)) {

/* process assertion */

}

```

3) Obtain the assertion by name: extend vpi\_handle\_by\_name to also search for assertion names in the appropriate scope(s), e.g.,

```

vpiHandle = vpi_handle_by_name(assertName, scope)

```

4) /\* room for expanding iteration later, filtering based on "object property" e.g.

```

itr = vpi_iterate_property(vpiAssertion, /* property_here: e.g.

vpiCheckAssertion*/, NULL);

while (assertion = vpi_scan(itr)) {

/* process assertion *

```

}

#### **NOTES**

- 1—As with all VPI handles, assertion handles are handles to a specific instance of a specific assertion.

- 2—These iterators return both assertions and immediate non-temporal checks.

- 3—Unnamed assertions cannot be found by name.

# 2.3.2 Obtaining static assertion information

The following information about an assertion is considered to be "static".

- Assertion name

- Instance in which the assertion occurs

- Module definition containing the assertion

- Assertion directive

- 1) assert

- 2) check

- 3) assume

- 4) cover

- 5) sequence

- 6) Any assertion updates from the SV-AC.

- Assertion source information: the file, line, and column where the assertion is defined.

- Assertion clocking domain/expression2

# **2.3.2.1 Using** vpi\_get\_assertion\_info

Static information can be obtained directly from an assertion handle by using vpi\_get\_assertion\_info, as shown below.

```

typedef struct t_vpi_source_info {

PLI_BYTE* *fileName;

PLI_INT32 startLine;

PLI_INT32 startColumn;

PLI_INT32 endLine;

PLI_INT32 endColumn;

} s_vpi_source_info, *p_vpi_source_info;

typedef struct t_vpi_assertion_info {

PLI_BYTE8 *name;

/* name of assertion */

vpiHandle instance; /* instance containing assertion */

/* name of module/interface containing

PLI_BYTE8 modname;

assertion */

vpiHandle clock; /* clocking expression */

PLI_INT32 directive; /* vpiAssume, ... */

s_vpi_source_info sourceInfo;

s_vpi_assertion_info, *p_vpi_assertion_info;

int vpi_get_assertion_info (assert_handle, p_vpi_assertion_info);

```

This call obtains all the static information associated with an assertion.

The inputs are a valid handle to an assertion and a pointer to an existing <code>s\_vpi\_assertion\_info</code> data structure. On success, the function returns <code>TRUE</code> and the <code>s\_vpi\_assertion\_info</code> data structure is filled in as appropriate. On failure, the function returns <code>FALSE</code> and the contents of the assertion data structure are unpredictable.

Assertions can occur in modules and interfaces: assertions defined in modules (by using VPI) shall have instance information; assertions in interfaces shall have a NULL instance handle. In either case, modname is the definition name.

#### **NOTES**

- 1—The assertion clock is an event expression supplied as the clocking expression to the assertion declaration, i.e., this is a handle to an arbitrary Verilog event expression.

- 2—A single call returns all the information for efficiency reasons.

```

2.3.2.2 Extending vpi_get() and vpi_get_str()

```

In addition to vpi\_get\_assertion\_info, the following existing VPI functions are also extended:

```

vpi_get(), vpi_get_str()

```

vpi\_get() can be used to query the following VPI properties from a handle to an assertion.

```

vpiAssertionDirective

```

returns one of vpiAssertProperty or vpiCheckProperty.

vpiLineNo

returns the line number where the assertion is declared.

vpi\_get\_str() can be used to obtain the following VPI properties from an assertion handle.

vpiFileName

returns the filename of the source file where the assertion was declared.

vpiName

returns the name of the assertion.

vpiFullName

returns the fully qualified name of the assertion.

# 2.4 Dynamic information

This section defines how to place assertion system and assertion callbacks.

# 2.4.1 Placing assertion "system" callbacks

Use vpi\_register\_cb(), setting the cb\_rtn element to the function to be invoked and the reason element of the s\_cb\_data structure to one of the following values, to place an assertion system callback.

```

cbAssertionSysInitialized

```

occurs after the system has initialized. No assertion-specific actions can be performed until this callback completes. The assertion system can initialize before cbStartOfSimulation does or afterwards.

```

cbAssertionSysStart

```

the assertion system has become active and starts processing assertion attempts. This always occur after cbAssertionSysInitialized. By default, the assertion system is "started" on simulation startup, but the user can delay this by using assertion system control actions.

```

cbAssertionSysStop

```

the assertion system has been temporarily suspended. While stopped no assertion attempts are processed and no assertion-related callbacks occur. The assertion system can be stopped and resumed an arbitrary number of times during a single simulation run.

```

cbAssertionSysEnd

```

occurs when all assertions have completed and no new attempts will start. Once this callback occurs no more assertion-related callbacks shall occur and assertion-related actions shall have no further effect. This typically occurs after the end of simulation.

```

cbAssertionSysReset

```

occurs when the assertion system is reset, e.g., due to a system control action.

The callback routine invoked follows the normal VPI callback prototype and is passed an s\_cb\_data containing the callback reason and any user data provided to the vpi\_register\_cb() call.

# 2.4.2 Placing assertions callbacks

Use vpi\_register\_assertion\_cb() to place an assertion callback; the prototype is:

```

vpiHandle vpi_register_assertion_cb(

vpiHandle, /* handle to assertion */

PLI_INT32 event,/* event for which callbacks needed */

PLI_INT32 (*cb_rtn)( /* callback function */

PLI_INT32 event,

vpiHandle assertion,

p_vpi_attempt_info info,

PLI_BYTE8 *userData),

PLI_BYTE8 *user_data/* user data to be supplied to cb */

);

typedef struct t_vpi_assertion_step_info {

PLI_INT32 matched_expression_count;

vpiHandle *matched_exprs; /* array of expressions */

p_vpi_source_info *exprs_source_info; /* array of source info */

PLI_INT32 stateFrom, stateTo;/* identify transition */

} s_vpi_assertion_step_info, *p_vpi_assertion_step_info;

typedef struct t_vpi_attempt_info {

union {

vpiHandle failExpr;

p_vpi_assertion_step_info step;

} detail;

s_vpi_time attemptTime,

} s_vpi_attempt_info, *p_vpi_attempt_info;

```

where event is any of the following.

```

cbAssertionStart

```

an assertion attempt has started. For most assertions one attempt starts each and every clock tick.

```

cbAssertionSuccess

```

when an assertion attempt reaches a success state.

```

cbAssertionFailure

```

when an assertion attempt fails to reach a success state.

```

cbAssertionStepSucess

```

the progress of one "thread" along an attempt. By default, step callbacks are not enabled on any assertions; they are enabled on a per-assertion/per-attempt basis, rather than on a per-assertion basis.

```

cbAssertionStepFailure

```

failure to progress along one "thread" along an attempt. By default, step callbacks are not enabled on any assertions; they are enabled on a per-assertion/per-attempt basis, rather than on a per-assertion basis.

cbAssertionDisable

whenever the assertion is disabled (e.g., as a result of a control action).

cbAssertionEnable

whenever the assertion is enabled.

cbAssertionReset

whenever the assertion is reset.

cbAssertionKill

when an attempt is killed (e.g., as a result of a control action).

These callbacks are specific to a given assertion; placing such a callback on one assertion does not cause the callback to trigger on an event occurring on a different assertion. If the callback is successfully placed, a handle to the callback is returned. This handle can be used to remove the callback via <code>vpi\_remove\_cb()</code>. If there were errors on placing the callback, a <code>NULL</code> handle is returned. As with all other calls, invoking this function with invalid arguments has unpredictable effects.

Once the callback is placed, the user-supplied function shall be called each time the specified event occurs on the given assertion. The callback shall continue to be called whenever the event occurs until the callback is removed.

The callback function shall be supplied the following arguments:

- 1) the event that caused the callback

- 2) the handle for the assertion

- 3) a pointer to an attempt information structure

- 4) a reference to the user data supplied when the callback was placed.

The attempt information structure contains details relevant to the specific event that occurred.

- On disable, enable, reset and kill events, the info field is absent (a NULL pointer is given as the value of info).

- On start and success events, only the *attempt time* field is valid.

- On a failure event, the *attempt time* and detail.failExpr are valid.

- On a step callback, the *attempt time* and detail.step elements are valid.

On a step callback, the detail describes the set of expressions matched in satisfying a step along the assertion, along with the corresponding source references. In addition, the step also identifies the source and destination "states" needed to uniquely identify the path being taken through the assertion. State ids are just integers, with 0 identifying the origin state, 1 identifying an accepting state, and any other number representing some intermediate point in the assertion. It is possible for the number of expressions in a step to be 0 (zero), which represents an unconditional transition. In the case of a failing transition, the information provided is just as that for a successful one, but the last expression in the array represents the expression where the transition failed.

#### NOTES

- 1—In a failing transition, there shall always be at least one element in the expression array.

- 2—Placing a step callback results in the same callback function being invoked for both success and failure steps.

#### 2.5 Control functions

This section defines how to obtain assertion system control and assertion control information.

# 2.5.1 Assertion system control

Use vpi\_control(), with one of the following operators and no other arguments, to obtain assertion system control information.

Usage example: vpi\_control(vpiAssertionSysReset)

vpiAssertionSysReset

discards all attempts in progress for all assertions and restore the entire assertion system to its initial state.

Usage example: vpi\_control(vpiAssertionSysStop)

vpiAssertionSysStop

considers all attempts in progress as unterminated and disable any further assertions from being started.

Usage example: vpi\_control(vpiAssertionSysStart)

vpiAssertionSysStart

restarts the assertion system after it was stopped (e.g., due to vpiAssertionSysStop). Once started, attempts shall resume on all assertions.

Usage example: vpi\_control(vpiAssertionSysEnd)

vpiAssertionSysEnd

discard all attempts in progress and disable any further assertions from starting.

#### 2.5.2 Assertion control

Use vpi\_control(), with one of the following operators, to obtain assertion control information.

— For the following operators, the second argument shall be a valid assertion handle.

Usage example: vpi\_control(vpiAssertionReset, assertionHandle)

vpiAssertionReset

discards all current attempts in progress for this assertion and resets this assertion to its initial state.

Usage example: vpi\_control(vpiAssertionDisable, assertionHandle)

vpiAssertionDisable

disables the starting of any new attempts for this assertion. This has no effect on any existing attempts. or if the assertion already disabled. By default, all assertions are enabled.

Usage example: vpi control(vpiAssertionEnable, assertionHandle)

vpiAssertionEnable

enables starting new attempts for this assertion. This has no effect if assertion already enabled or on any existing attempts.

— For the following operators, the second argument shall be a valid assertion handle and the third argument shall be an attempt start-time (as a pointer to a correctly initialized s\_vpi\_time structure).

Usage example: vpi\_control(vpiAssertionKill, assertionHandle, attempt)

vpiAssertionKill

discards the given attempts, but leaves the assertion enabled and does not reset any state used by this assertion (e.g., past() sampling).

Usage example: vpi\_control(vpiAssertionDisableStep, assertionHandle, attempt)

vpiAssertionDisableStep

disables step callbacks for this assertion. This has no effect if stepping not enabled or it is already disabled.

— For the following operator, the second argument shall be a valid assertion handle, the third argument shall be an attempt start-time (as a pointer to a correctly initialized s\_vpi\_time structure) and the fourth argument shall be a "step control" constant.

vpiAssertionEnableStep

enables step callbacks to occur for this assertion attempt. By default, stepping is disabled for all assertions. This call has no effect if stepping is already enabled for this assertion and attempt, other than possibly changing the stepping mode for the attempt if the attempt has not occurred yet. The stepping mode of any particular attempt cannot be modified after the assertion attempt in question has started.

NOTE—In this release, the only step control constant available is <code>vpiAssertionClockSteps</code>, indicating callbacks on a per assertion/clock-tick basis. The assertion clock is the event expression supplied as the clocking expression to the assertion declaration. The assertion shall "advance" whenever this event occurs and, when stepping is enabled, such events shall also cause step callbacks to occur.

# Section 3 SystemVerilog Coverage API

# 3.1 Requirements

This chapter defines the Coverage Application Programming Interface (API) in SystemVerilog 3.1/draft 4.

# 3.1.1 SystemVerilog API

- The following criteria are used within this API.

- This API shall be similar for all coverages There are a wide number of coverage types available, with possibly different sets offered by different vendors. Maintaining a common interface across all the different types enhances portability and ease of use

- 2) At a minimum, the following types of coverage shall be supported:

- a) statement coverage

- b) toggle coverage

- c) fsm coverage

- i) fsm states

- ii) fsm transitions

- d) assertion coverage

- 3) Coverage APIs shall be extensible in a transparent manner, i.e., adding a new coverage type shall not break any existing coverage usage.

- 4) This API shall provide means to obtain coverage information from specific sub-hierarchies of the design without requiring the user to enumerate all instances in those hierarchies.

#### 3.1.2 Naming conventions

All elements added by this interface shall conform to the Verilog Procedural Interface (VPI) interface naming conventions.

- All names are prefixed by vpi.

- All *type names* shall start with vpi, followed by initially capitalized words with no separators, e.g., vpiCoverageStmt.

- All callback names shall start with cb, followed by initially capitalized words with no separators, e.g., cbAssertionStart.

- All *function names* shall start with vpi\_, followed by all lowercase words separated by underscores (\_), e.g., vpi\_control().

#### 3.1.3 Nomenclature

The following terms are used in this standard.

Statement coverage — whether a statement has been executed or not, where statement is anything defined as a statement in the LRM. Covered means it executed at least once. Some implementations also permit

querying the execution count. The granularity of statement coverage can be per-statement or per-statement block (however defined).

FSM coverage — the number of states in a finite state machine (FSM) that this simulation reached. This standard does not require FSM automatic extraction, but a standard mechanism to force specific extraction is available via pragmas.

Toggle coverage — for each bit of every signal (wire and register), whether that bit has both a 0 value and a 1 value. Full coverage means both are seen; otherwise, some implementations can query for partial coverage. Some implementations also permit querying the toggle count of each bit.

Assertion coverage — for each assertion, whether it has had at least one success. Implementations permit querying for further details, such as attempt counts, success counts, failure counts and failure coverage.

These terms define the "primitives" for each coverage type. Over instances or blocks, the coverage number is merely the sum of all contained primitives in that instance or block.

# 3.2 SystemVerilog real-time coverage access

This section ...

# 3.2.1 Predefined coverage constants in SystemVerilog

The following predefine 'defines represent basic real-time coverage capabilities accessible directly from SystemVerilog.

Coverage control

```

'define SV_COV_START 0

'define SV_COV_STOP 1

'define SV_COV_RESET 2

'define SV_COV_QUERY 3

```

Scope definition (hierarchy traversal/accumulation type)

```

'define SV_COV_MODULE 10

'define SV_COV_HIER 11

```

— Coverage type identification

```

'define SV_COV_ASSERTION 20

'define SV_COV_FSM_STATE 21

'define SV_COV_STATEMENT 22

'define SV_COV_TOGGLE 23

```

Status results

```

'define SV_COV_OVERFLOW -2

'define SV_COV_ERROR -1

'define SV_COV_NOCOV 0

'define SV_COV_OK 1

'define SV_COV_PARTIAL 2

```

# 3.2.2 Built-in coverage access system functions

This section ...

#### **3.2.2.1** \$coverage\_control

This function enables, disables, resets or queries the availability of coverage information for the specified portion of the hierarchy. The return value is a 'defined name, with the value indicating the success of the action.

```

'SV COV OK

```

the request is successful. When querying, if starting, stopping, or resetting this means the desired effect occurred, coverage is available. A successful reset clears all coverage (i.e., using a ...get() == 0 after a successful ...reset()).

```

'SV COV ERROR

```

the call failed with no action, typically due to errors in the arguments, such as a non-existing module or instance specifications.

```

'SV_COV_NOCOV

```

coverage is not available for the requested portion of the hierarchy.

```

'SV COV PARTIAL

```

coverage is only partially available in the requested portion of the hierarchy (i.e., some instances have the requested coverage information, some don't).

Starting, stopping, or resetting coverage multiple times in succession for the same instance(s) has no further effect if coverage has already been started, stopped, or reset for that/those instance(s).

The hierarchy(ies) being controlled or queried are specified as follows.

```

'SV_MODULE_COV, "unique module def name"

```

provides coverage of all instances of the given module (the unique module name is a string), excluding any child instances in the instances of the given module. The module definition name can use special notation to describe nested module definitions.

```

`SV_COV_HIER, "module name"

```

provides coverage of all instances of the given module, including all the hierarchy below.

```

'SV_MODULE_COV, instance_name

```

provides coverage of the one named instance. The instance is specified as a normal Verilog hierarchical path.

```

'SV_COV_HIER, instance_name

```

provides coverage of the named instance, plus all the hierarchy below it.

All the permutations are summarized in Table 3-1 on page 23.

\*\*Revise this xref w/ Stu; also check/revise variable settings, etc.\*\*

Table 3-1: Instance coverage permutations

| Control/query  | "Definition name"                                                                                         | instance.name                                                                                   |

|----------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 'SV_COV_MODULE | The sum of coverage for all instances of the named module, excluding any hierarchy below those instances. | Coverage for just the named instance, excluding any hierarchy in instances below that instance. |

Table 3-1: Instance coverage permutations (continued)

| Control/query | "Definition name"                                                                                                          | instance.name                                               |

|---------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 'SV_COV_HIER  | The sum of coverage for all instances of the named module, including all coverage for all hierarchy below those instances. | Coverage for the named instance and any hierarchy below it. |

NOTE—Definition names are represented as strings, whereas instance names are referenced by hierarchical paths. A hierarchical path need not include any . if the path refers to an instance in the current context (i.e., normal Verilog hierarchical path rules apply).

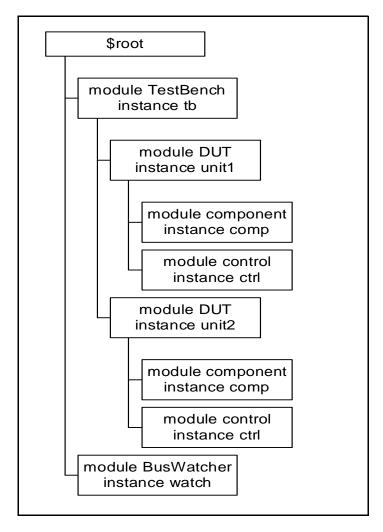

Example 3-1Hierarchical instance example

If coverage is enabled on all instances shown in Example 3-1, then:

resets coverage collection on both instances of the DUT, specifically, \$root.tb.unit1 and \$root.tb.unit2, but leaves coverage unaffected in all other instances.

resets coverage of only the instance \$root.tb.unit1, leaving all other instances unaffected.

resets coverage of the instance \$root.tb.unit1 and also reset coverage for all instances below it, specifically \$root.tb.unit1.comp and \$root.tb.unit1.ctrl.

\$coverage\_control(`SV\_COV\_START, `SV\_COV\_TOGGLE, `SV\_COV\_HIER, "DUT")

starts coverage on all instances of the module DUT and of all hierarchy(ies) below those instances. In this

design, coverage is started for the instances \$root.tb.unit1, \$root.tb.unit1.comp,

\$root.tb.unit1.ctrl, \$root.tb.unit2, \$root.tb.unit2.comp, and

\$root.tb.unit2.ctrl.

#### 3.2.2.2 \$coverage\_get\_max

```

$coverage_get_max(coverage_type, scope_def, modules_or_instance)

```

This function obtains the value representing 100% coverage for the specified coverage type over the specified portion of the hierarchy. This value shall remain constant across the duration of the simulation.

NOTE—This value is proportional to the design size and structure, so it also needs to be constant through multiple independent simulations and compilations of the same design, assuming any compilation options do not modify the coverage support or design structure.

The return value is an integer, with the following meanings.

```

-2 ('SV COV OVERFLOW)

```

the value exceeds a number that can be represented as an integer.

```

-1 ('SV_COV_ERROR)

```

an error occurred (typically due to using incorrect arguments).

```

0 ('SV_COV_NOCOV)

```

no coverage is available for that coverage type on that/those hierarchy(ies).

```

+pos_num

```

the maximum coverage number (where  $pos\_num > 0$ ), which is the sum of all coverable items of that type over the given hierarchy(ies).

The scope of this function is specified as per \$coverage control (see section 3.2.2.1).

#### 3.2.2.3 \$coverage\_get

```

$coverage_get(coverage_type, scope_def, modules_or_instance)

```

This function obtains the current coverage value for the given coverage type over the given portion of the hierarchy. This number can be converted to a coverage percentage by use of the equation:

$$cov erage\% = \frac{cov erage \_ get()}{cov erage \_ get \_ max()} *100$$

The return value follows the same pattern as \$coverage\_get\_max (see section 3.2.2.2), but with the pos\_num number representing the current coverage level, i.e., the number of the coverable items that have been covered in this/these hierarchy(ies).

The scope of this function is specified as per \$coverage\_control (see section 3.2.2.1).

The return value is an integer, with the following meanings.

```

-2 ('SV COV OVERFLOW)

```

the value exceeds a number that can be represented as an integer.

```

-1 ('SV_COV_ERROR)

```

an error occurred (typically due to using incorrect arguments).

```

0 ('SV_COV_NOCOV)

```

no coverage is available for that coverage type on that/those hierarchy(ies).

```

+pos num

```

the maximum coverage number (where  $pos\_num > 0$ ), which is the sum of all coverable items of that type over the given hierarchy(ies).

#### 3.2.2.4 \$coverage merge

```

$coverage_merge(coverage_type, "name")

```

This function loads and merges coverage data for the specified coverage into the simulator. name is an arbitrary string used by the tool, in an *implementation-specific* way, to locate the appropriate coverage database, i.e., tools are allowed to store coverage files any place they want with any extension they want *as long* as the user can retrieve the information by asking for a specific saved name from that coverage database. If *name* does not exist or does not correspond to a coverage database from the same design, an error shall occur. If an error occurs during loading, the coverage numbers generated by this simulation might not be meaningful.

The return values from this function are:

```

'SV COV OK

```

the coverage data has been found and merged.

```

'SV COV NOCOV

```

the coverage data has been found, but did not contain the coverage type requested.

```

'SV_COV_ERROR

```

the coverage data was not found or it did not correspond to this design, or another error.

#### **3.2.2.5** \$coverage\_save

```

$coverage_save(coverage_type, "name")

```

This function saves the current state of coverage to the tool's coverage database and associates it with the file named name. This file name shall not contain any directory specification or extensions. Data saved to the database shall be retrieved later by using \$coverage\_merge and supplying the same name. Saving coverage shall not have any effect on the state of coverage in this simulation.

The return values from this function are:

```

'SV_COV_OK

```

the coverage data was successfully saved.

```

'SV COV NOCOV

```

no such coverage is available in this design (nothing was saved).

```

'SV_COV_ERROR

```

some error occurred during the save. If an error occurs, the tool shall automatically remove the coverage database entry for *name* to preserve the coverage database integrity. It is *not* an error to overwrite a previously existing *name*.

# NOTES

1—The coverage database format is implementation-dependent.

2—Mapping of names to actual directories/files is implementation-dependent. There is no requirement that a coverage name map to any specific set of files or directories.

# 3.3 FSM recognition

Coverage tools need to have automatic recognition of many of the common FSM coding idioms in Verilog/SystemVerilog. This standard does not attempt to describe or require any specific automatic FSM recognition mechanisms. However, the standard does prescribe a means by which non-automatic FSM extraction occurs. The presence of any of these standard FSM description additions shall override the tool's default extraction mechanism.

Identification of an FSM consists of identifying the following items:

- 1) the state register (or expression)

- 2) the next state register (this is optional)

- 3) the legal states.

# 3.3.1 Specifying the signal that holds the current state

```

**This section reads a bit like a user's guide; convert this into an annex??

```

Use the following pragma to identify the vector signal that holds the current state of the FSM:

```

/* tool state_vector signal_name */

**let's define these terms (in the next draft)**

```

where tool and state\_vector are required keywords. This pragma needs to be specified inside the module definition where the signal is declared.

Another pragma is also required, to specify an enumeration name for the FSM. This enumeration name is also specified for the next state and any possible states, associating them with each other as part of the same FSM. There are two ways to do this:

— Use the same pragma:

```

/* tool state_vector signal_name enum enumeration_name */

```

— Use a separate pragma in the signal's declaration:

```

/* tool state_vector signal_name */

reg [7:0] /* tool enum enumeration_name */ signal_name;

```

In either case, enum is a required keyword; if using a separate pragma, tool is also a required keyword and the pragma needs to be specified immediately after the bit-range of the signal.

#### 3.3.2 Specifying the part-select that holds the current state

- A part-select of a vector signal can be used to hold the current state of the FSM. When cmView displays or reports FSM coverage data, it names the FSM after the signal that holds the current state. If a part-select holds the current state in the user's FSM, the user needs to also specify a name for the FSM that cmView can use. The FSM name is not the same as the enumeration name.

- Specify the part-select by using the following pragma:

```

/* tool state_vector signal_name[n:n] FSM_name enum enumeration_name */

```

# 3.3.3 Specifying the concatenation that holds the current state

Like specifying a part-select, a concatenation of signals can be specified to hold the current state (when including an FSM name and an enumeration name):

```

/* tool state_vector {signal_name , signal_name, ...} FSM_name enum

enumeration_name */

```

The concatenation is composed of all the signals specified. Bit-selects or part-selects of signals cannot be used in the concatenation.

# 3.3.4 Specifying the signal that holds the next state

The signal that holds the next state of the FSM can also be specified with the pragma that specifies the enumeration name:

```

reg [7:0] /* tool enum enumeration_name */

signal name

```

This pragma can be omitted if, and only if, the FSM does not have a signal for the next state.

# 3.3.5 Specifying the current and next state signals in the same declaration

The tool assumes the first signal following the pragma holds the current state and the next signal holds the next state when a pragma is used for specifying the enumeration name in a declaration of multiple signals, e.g.,

```

/* tool state_vector cs */

reg [1:0] /* tool enum myFSM */ cs, ns, nonstate;

```

In this example, the tool assumes signal cs holds the current state and signal ns holds the next state. It assumes nothing about signal nonstate.

#### 3.3.6 Specifying the possible states of the FSM

The possible states of the FSM can also be specified with a pragma that includes the enumeration name:

```

parameter /* tool enum enumeration_name */

S0 = 0,

s1 = 1,

s2 = 2,

s3 = 3;

```

Put this pragma immediately after the keyword parameter, unless a bit-width for the parameters is used, in which case, specify the pragma immediately after the bit-width:

```

parameter [1:0] /* tool enum enumeration_name */

S0 = 0,

s1 = 1,

s2 = 2,

s3 = 3;

```

# 3.3.7 Pragmas in one-line comments

These pragmas work in both block comments, between the /\* and \*/ character strings, and one-line comments, following the // character string, e.g.,

```

parameter [1:0] // tool enum enumeration_name

S0 = 0,

s1 = 1,

```

```

s2 = 2,

s3 = 3;

```

# 3.3.8 Example

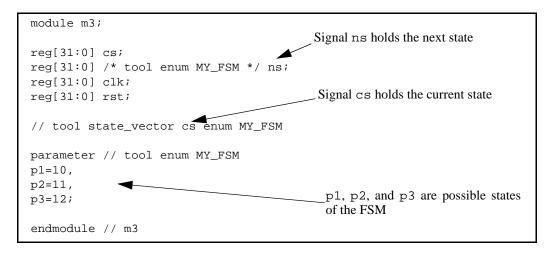

Example 3-2FSM specified with pragmas

# 3.4 VPI coverage extensions

This section ...

# 3.4.1 VPI entity/relation diagrams related to coverage

This section ...

# 3.4.2 Extensions to VPI enumerations

Coverage control

```

#define vpiCoverageStart

#define vpiCoverageStop

#define vpiCoverageReset

#define vpiCoverageCheck

#define vpiCoverageMerge

#define vpiCoverageSave

```

#### VPI properties

1) Coverage type properties

```

#define vpiAssertCoverage

#define vpiFsmStateCoverage

#define vpiStatementCoverage

#define vpiToggleCoverage

```

2) Coverage status properties

```

#define vpiCovered

#define vpiCoverMax

#define vpiCoveredCount

```

3) Assertion-specific coverage status properties

```

#define vpiAssertAttemptCovered

#define vpiAssertSuccessCovered

#define vpiAssertFailureCovered

```

4) FSM-specific methods

```

#define vpiFsmStates

#define vpiFsmStateExpression

```

— FSM handle types (vpi types)

```

#define vpiFsm

#define vpiFsmHandle

```

# 3.4.3 Obtaining coverage information

All \*\*what?? use vpi\_get() along with the appropriate properties and object handles.

```

coverage type, instance

```

the number of covered items in the given instance.

```

vpiCovered, handle

```

the number of items of the handle type is covered. This is only applicable to: statement handles, signal (wire/reg) handles, assertion handles, and FSM handles.

```

vpiCoveredCount, handle

```

the number of times each item of the handle type is covered. This is only easily interpretable when *handle* points to a unique coverable item (otherwise this is the sum of counts of all contained items).

```

vpiCoveredMax, handle

```

the total possible coverable items in the given handle. Handle types limited as per above. vpiCovered-Max is only really useful when *handle* is a handle to an object potentially containing more than one coverable item.

- Use vpi\_iterate(vpiFsm, instance-handle) to get the iterator to all FSMs in an instance.

- Use vpi\_handle(vpiFsmStateExpression, fsm-handle) to get the handle to the signal or expression encoding the FSM state.

- Use vpi\_iterate(vpiFsmStates, fsm-handle) to get the iterator to all states of an FSM.

- Use vpi\_get\_value(fsm\_state\_handle, state-handle) to get the value of a state.

# 3.4.4 Controlling coverage

\*\*Revise similar to Assertions\*\*

```

vpi_control()

```

has three arguments: coverage control (start, stop, reset, query), coverage type, and the handle to the appropriate instance or assertion. Statement, toggle, and FSM coverage are not individually controllable (i.e., they are controllable only at the instance level, not on a per statement/signal/FSM). The semantics and behavior are specified as per the equivalent system function \$coverage\_control (see section 3.2.2.1).

```

vpi_control()

```

has three arguments: coverage control (merge, save), coverage type, and name. This merges coverage into the current simulation. The semantics and behavior are specified as per the equivalent system functions \$coverage\_merge (see section 3.2.2.4) and \$coverage\_save (see section 3.2.2.5).

# Annex A

# **DPI C-laver**

#### A.1 Overview

The SystemVerilog Direct Programming Interface (DPI) allows direct inter-language function calls (ILFC's) between SystemVerilog and any foreign programming language with a C function call protocol and linking model:

- Functions implemented in C and given import declarations in SystemVerilog can be called from System-Verilog; such functions are referred to as *mported functions*.

- Functions implemented in SystemVerilog and specified in export declarations can be called from C; such functions are referred to as *exported functions*.

The SystemVerilog DPI supports only SystemVerilog data types, which are the sole data types that can cross the boundary between SystemVerilog and a foreign language in either direction. On the other hand, the data types used in C code shall be C types; hence, the duality of types.

A value that is passed through the Direct Programming Interface is specified in SystemVerilog code as a value of SystemVerilog type, while the same value shall be specified in C code as a value of C type. Therefore, a pair of matching type definitions is required to pass a value through DPI: the SystemVerilog definition and the C definition.

It is the user's responsibility to provide these matching definitions. A tool (such as the a System Verilog compiler) can facilitate this by generating C type definitions for the System Verilog definitions used in <u>DPI</u> for imported and exported functions.

Some SystemVerilog types are directly compatible with C types; defining a matching C type for them is straightforward. There are, however, SystemVerilog-specific types, namely packed types (arrays, structures, and unions), 2-state or 4-state, which have no natural correspondence in C. DPI does not require any particular representation of such types and does not impose any restrictions on SystemVerilog implementation. This allows implementors to choose the layout and representation of packed types that best suits their simulation performance.

While not specifying the actual representation of packed types, this C-layer interface defines a canonical representation of packed 2-state and 4-state arrays. This canonical representation is actually based on Verilog legacy Programming Language Interface's (PLI's) avalue/bvalue representation of 4-state vectors. Library functions provide the translation between the representation used in a simulator and the canonical representation of packed arrays. There are also functions for bit selects and limited part selects for packed arrays, which do not require the use of the canonical representation.

Formal arguments in SystemVerilog can be specified as open arrays solely in <a href="import\_declarations">import\_declarations</a>; exported SystemVerilog functions can not have formal arguments specified as open arrays. A formal argument is an *open array* when a range of one or more of its dimensions is unspecified (denoted in SystemVerilog by using empty square brackets ([])). This corresponds to a relaxation of the argument-matching rules. An actual argument shall match the formal one regardless of the range(s) for its corresponding dimension(s), which facilitates writing more general C code that can handle SystemVerilog arrays of different sizes.

The C-layer of DPI basically uses normalized ranges. Normalized ranges mean [n-1:0] indexing for the packed part (packed arrays are restricted to one dimension) and [0:n-1] indexing for a dimension in the unpacked part of an array. Normalized ranges are used for the canoni 12.944 resetration of pnackel ar

fwante

ry( ay944[d th9846(ets)-5.2(a)16(e1