#### Functional Coverage Arturo Salz

# Agenda

- Definitions and features

- Coverage definition

- Coverage group

- Coverage point

- Values and Transitions

- User defined bins

- Cross coverage

- Cross product selection and exclusion

- Coverage options

SystemVerilog

Procedural control and access to coverage

# What is Functional coverage

- Measure of how much of the design specification has been exercised

- % test plan features

- User-specified

- Not automatically inferred from the design

- Based on design specification

- Captures intent

- Independent of design code or structure

### **Functional coverage features**

- Coverage of variables and expressions

Cross coverage

- Automatic and user-defined coverage bins

Values, transitions, or cross products

- Filtering conditions at multiple levels

- Flexible coverage sampling

Events, Sequences, Procedural

SystemVerilog

Directives to control and query coverage

## **Coverage model : covergroup**

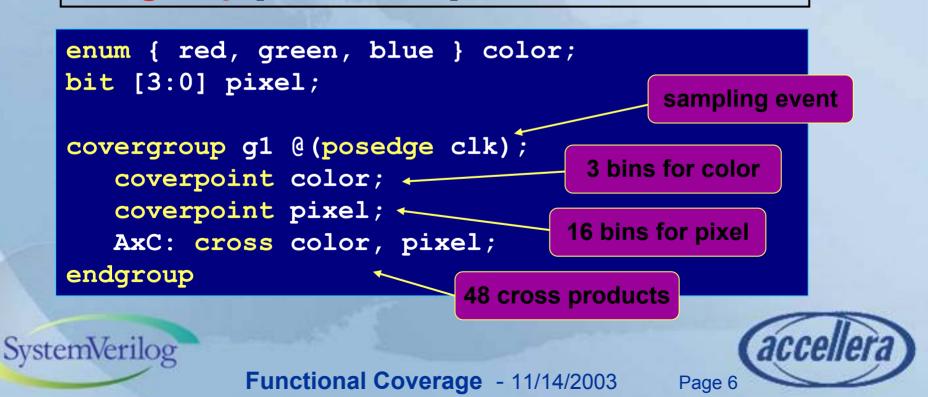

#### New container covergroup : coverage model

- Coverage points

- variables

- expressions

- transitions

SystemVerilog

- Cross coverage

- Sampling expression : clocking event

- Filtering expressions

- Specify once (like class), use many times

Cumulative or per-instance coverage

#### **Declaration of a covergroup**

covergroup identifier [ ( argument\_list ) ]

[ clocking\_event ] ;

{ coverage\_spec\_or\_option ; }

endgroup [ : identifier ]

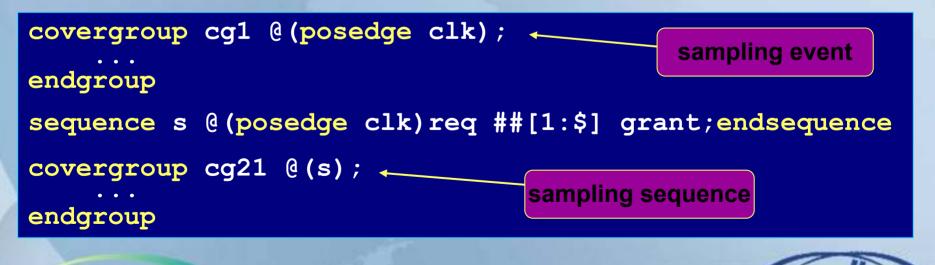

#### **Coverage sampling event**

#### Sampling can be

SystemVerilog

- Any event expression edge, variable

- End-point of a sequence

- Event can be omitted

- Procedural sampling under user control

ACCE

Page 7

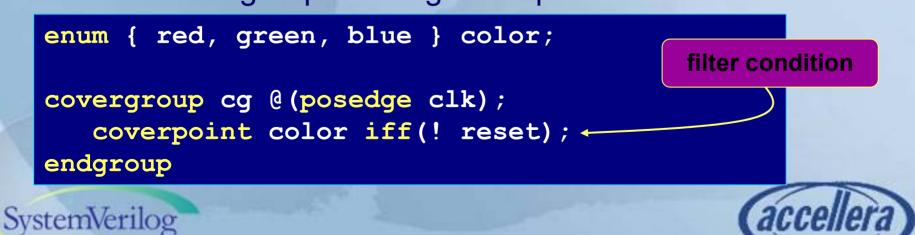

# **Defining Coverage Points**

[label :] coverpoint expression [ iff (expression) ]

{ bins\_or\_options }

#### **Specifies expression (or variable) to sample**

- Expression is sampled and accounted in bin(s)

- Number of values/bins can be controlled

- bins specification

- Optionally filtering expression iff

- Bins can be grouped using bins specification

Page 8

#### **Defining Bins for Coverage Points**

- If no state or transition bins explicitly defined, then bins are automatically created

- Easy-to-use, no effort in defining bins

- Or, user can define state and/or transition bins for each coverage point.

- Too many values

- Not all values are interesting or relevant

- Each bin groups a set of values or a set of value transitions associated with a sampled variable or expression

- Group equivalent values

- Cover bins, not values

SystemVerilog

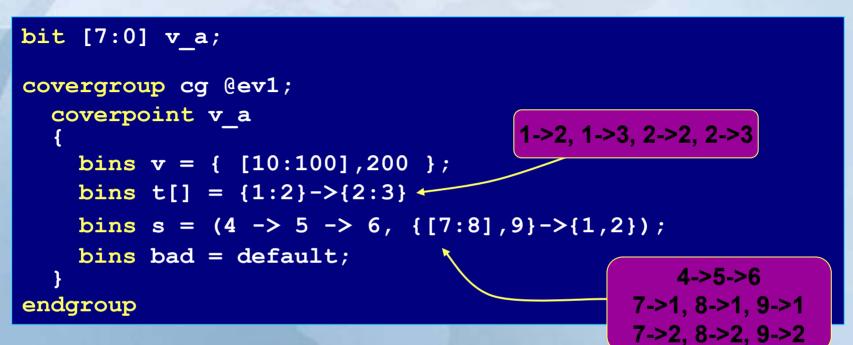

# **Defining coverage-point bins**

bins name [[]] = { value set } [ iff (expression) ] bins name [[]] = (transitions) [iff (expression)] bins name [ [ ] ] = default [sequence] iff (expression)]

- Group specific cover-points under a name

- Set of values

SystemVerilog

- Set of transitions (4->5, 6->7, 10->1)

{ 1, 5, [7:14], 25 }

- · default catches undefined values / transitions

- [] specifies creation of multiple bins per value

- iff specifies conditional coverage •

## **Defining value coverage bins**

```

bit [7:0] v_a, v_b;

covergroup cg @ev1;

coverpoint v_a + v_b

{

bins a = { [64:127],200 }; // user-defined bins

bins b[] = { 0,10,100,220 } iff( !reset );

bins bad = default; // all other values

}

```

endgroup

- a creates one bin, covered if in the range

- b creates one bin per value: b[0], b[10], b[100], b[220]

only covered when reset == 0

- bad catches all other (in one bin)

- [1:9], [11:63], [128:199], [201:219], [221:255]

SystemVerilog

Functional Coverage - 11/14/2003

Page 1<sup>°</sup>

#### **Transition coverage bins**

trans\_range\_list-> trans\_range\_list {-> tras\_range\_list}

trans\_range\_list ::=

trans\_item

[ trans\_item [\* repeat\_range ] // consecutive

[ trans\_item [\*-> repeat\_range ] // goto-repetition

[ trans\_item [\*= repeat\_range ] // nonconsecutive rept

#### Subset of property syntax

- {1:8} -> 2 expands to 1->2, 2->2, 3->2,... 8->2

- 3->5->{1:2} expands to 3->5->1, 3->5->2

- 2->3[\*2:3] expands to 2->3, 2->3->3, 2->3->3

- 2->3[\*->2] expands to 2->3->...->3

- 2->4[\*=2] expands to 2->4->...->4 (excluded)

SystemVerilog

Functional Coverage - 11/14/2003

Page 12

## **Defining transition bins**

- s creates one bin for all 7 transitions

- bad catches all undefined values

- [0:9], [101:199], [201:255]

SystemVerilog

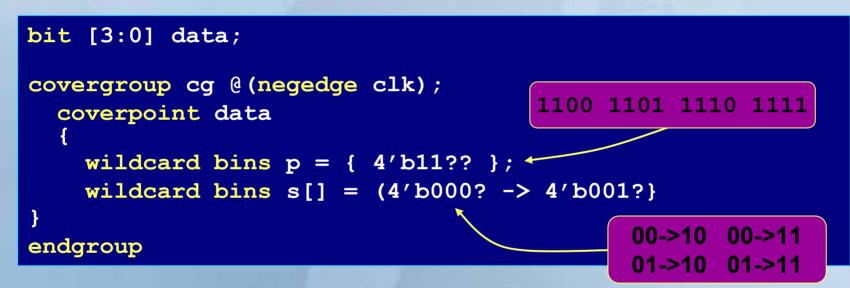

### Wildcard bins specification

The wildcard specification treats ?, X, Z as a wildcard for 0 or 1

- p creates one bin for the 4 values

12, 13, 14, 15

- s creates one bin for each of the transitions

- 0->2, 0->3, 1->2, 1->3

SystemVerilog

### **Automatic bin creation**

- If omitted, N bins are automatically created

- *N* is determined:

- For an enum : N is the cardinality of the enum

- All others: N is min( 2<sup>M</sup>, auto\_bin\_max )

- M => # bits needed to represent the cover-point

- If  $N < 2^{M}$

SystemVerilog

- Values are uniformly distributed into the N bins

- Every bin will include 2<sup>M</sup>/N values

- Last bin accommodates any slack

- Automatic bins exclude X and Z (2-state only)

- Coverage space is tractable

#### **Excluding values or transitions**

Any set of values or transitions can be explicitly excluded from coverage

the ignore bins specification

```

covergroup g1 @(posedge clk);

coverpoint a

{

...

ignore_bins ivals = {7,8};

ignore_bins itrans = (1->3->5);

}

endgroup

```

ivals excludes values 7 and 8

SystemVerilog

itrans excludes the transition 1->3->5

#### **Illegal values or transitions**

Any set of values or transitions can be marked illegal using illegal\_bins

```

covergroup g1 @(posedge clk);

coverpoint a

{

...

illegal_bins evals = {1,2,3};

illegal_bins etrans = (4->3->2, 5->2);

}

endgroup

```

An Illegal bin hit triggers a run-time error

Even if it is part of another bin

**Functional Coverage** - 11/14/2003

SystemVerilog

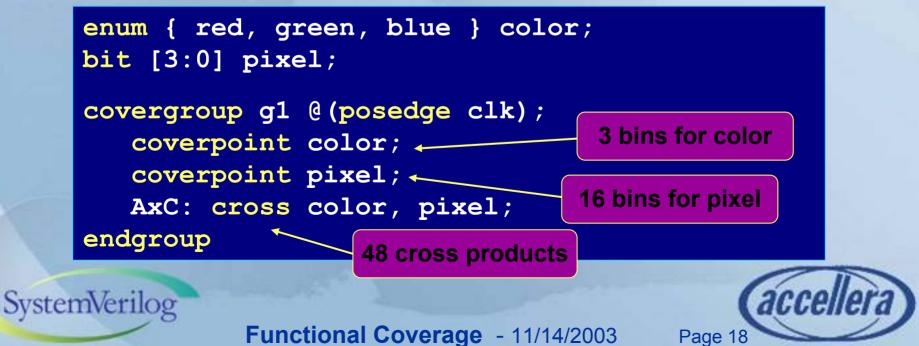

#### **Defining cross coverage**

[label :] cross coverpoint\_list [ iff (expression) ]

{ select\_bins\_or\_options }

- Covers two or more coverage points simultaneously

- Coverage of all combinations of all bins associated with the specified cover-points

- The Cartesian product of all the sets of coverage-point bins

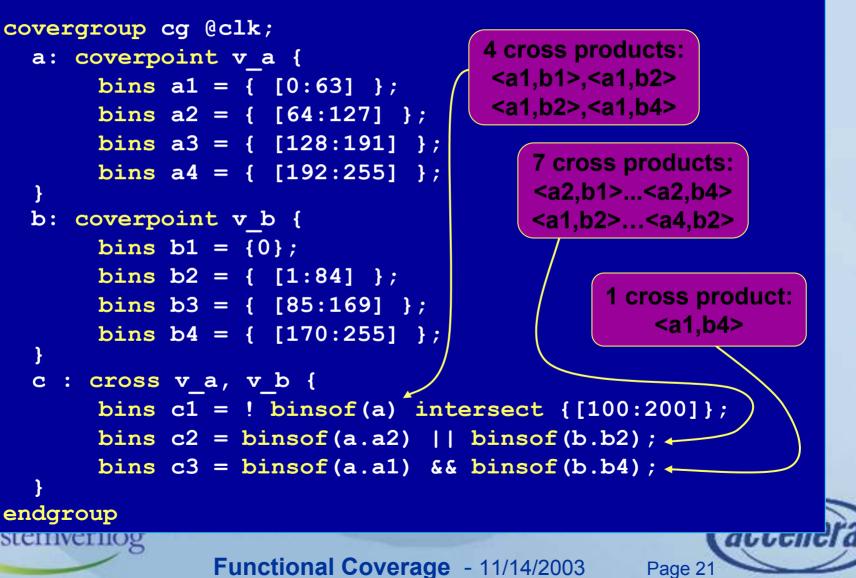

## **Defining cross coverage bins**

- A cross coverage bin associates a name and a count with a set of cross products

- Cross bins group together sets of cross products

```

bins selection ::= bins name = select expression

select expression ::=

select condition

select condition

select expression && select expression

select expression || select expression

(select expression)

select condition ::=

binsof ( bins) [ intersect open_range_list ]

SystemVerilog

accel

```

Functional Coverage - 11/14/2003

Page 19

#### **Cross coverage bins**

#### bit [7:0] v\_a, v\_b;

endgroup

```

covergroup cg @clk;

a: coverpoint v a {

bins a1 = { [0:63] };

bins a2 = { [64:127] };

bins a3 = { [128:191] };

bins a4 = { [192:255] };

b: coverpoint v b {

16 cross products:

bins b1 = \{0\};

<a1,b1>...<a1,b4>

bins b2 = \{ [1:84] \};

<a4,b1>...<a4,b4>

bins b3 = { [85:169] };

bins b4 = { [170:255] };

c : cross v a, v b ;

```

Functional Coverage - 11/14/2003

*auuci*

Page 20

#### **Cross coverage bins**

#### bit [7:0] v\_a, v\_b;

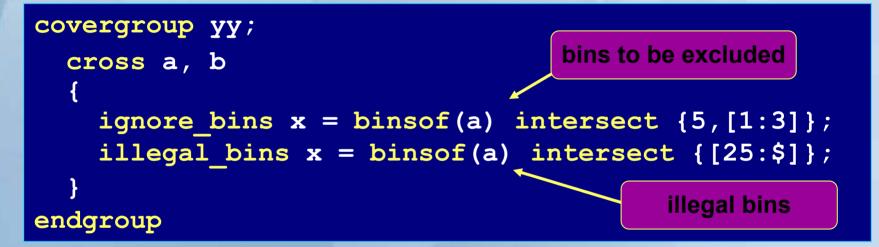

#### **Exclusion cross products**

Select expressions can be used to exclude or specify cross products as illegal

- Illegal bins take precedence over all others

- Excluded bins are never included

### **Generic Coverage groups**

Generic coverage groups can be written by passing their traits as arguments to the constructor.

```

covergroup rg (ref int ra, int low, int high ) @(clk);

coverpoint ra // sample variable passed by reference

bins good = { [low : high] };

bins bad[] = default;

endgroup

```

- good creates one bin, for the range [low : high]

- bad creates one bin per value outside that range

```

int A, B;

rg c1 = new(A, 0, 50); // cover A in range 0 to 50

// cover B in range 120 to 600

rg c2 = new(B, 120, 600);

SystemVerilog

```

### **Coverage Group in classes**

- Coverage groups may be embedded in class

- Integrated with object oriented paradigm

- Intuitive and simple to cover data members

- Including private data members

- Other class members can be seamlessly used in coverage specification

#### **Embedded Coverage Group**

class xyz; bit [3:0] m\_x; int m\_y; bit m\_z;

> covergroup cov1 @m\_z; coverpoint m\_x; coverpoint m\_y; endgroup

covergroup cov1 @m\_z; // embedded covergroup

function new(); cov1 = new; endfunction

endclass

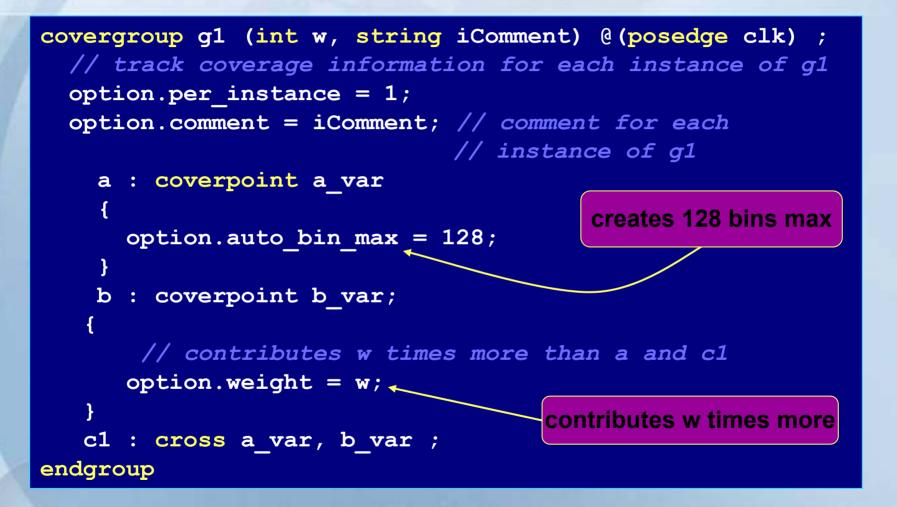

#### **Coverage Options**

SystemVerilog

# **Options for control**

- weight

- for computing weighted mean

- goal

- target goal for group/point/cross

- name

SystemVerilog

- name for the covergroup instance

- at\_least

- minimum number of hits for a bin

- per\_instance

- keep per instance data in addition to the cumulative coverage

## **Coverage Control**

- Covergroup and covergroup instance methods allow control and access to the coverage data

- void sample()

SystemVerilog

- Procedurally control sampling

- real get\_coverage()

obtains cumulative coverage

- real get\_inst\_coverage()

- obtains instance coverage

### **Procedural sampling**

```

enum { red, green, blue } color;

bit [3:0] pixel adr,

covergroup g1;

c: coverpoint color;

a: coverpoint pixel adr iff (xfer > n);

endgroup

g1 tc1 = new;

task transaction();

Sample for coverage at this point

tc1.sample();

• • •

endtask

```

SystemVerilog

## **Coverage Control**

- Methods to start and stop collection

- start()

- stop()

- System function to retrieve overall coverage

- \$get\_coverage()

- System tasks to name, load and save coverage database

- \$set\_coverage\_db\_name()

- \$load\_coverage\_db()

SystemVerilog

#### Thank you