# The IBIS Specification and Verilog-AMS

Michael Mirmak Intel Corp. Chair, EIA IBIS Open Forum

Accellera Verilog-AMS WG February 14, 2005

02/14/05 http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners IBIS

# Agenda

- What is IBIS?

- IBIS Organization

- The IBIS Open Forum

- Open Forum members

- IBIS and Accellera Verilog-AMS WG

- Timeline

- Backup

02/14/05

- IBIS Model Format

- IBIS Link to \*-AMS Models

- Technical Vision of IBIS<->AMS relationship

- A Related Specification: ICM

some material from Arpad Muranyi, Intel Corp.

# What Is IBIS?

I/O

- **B Buffer**

- Information

# **S** Specification

IBIS, common name for any of about 30 species of long-legged, long-necked wading birds.

http://www.eigroup.org/ibis/ http://www.eda.org/ibis/

IBIS is a universal standard for describing the analog behavior of digital device buffers using data in ASCII text format

IBIS files are not really models, they just contain the data that will be

used by the simulation tool's behavioral models and algorithms

- Started in the early 90s to promote tool-independent I/O models for system-level signal integrity work

- IBIS 3.2 is an official standard: ANSI/EIA-656-A (1999), IEC 62014-1

intel

02/14/05

**IBIS 4.1 incorporates links to VHDL-AMS and Verilog-AMS**

http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners

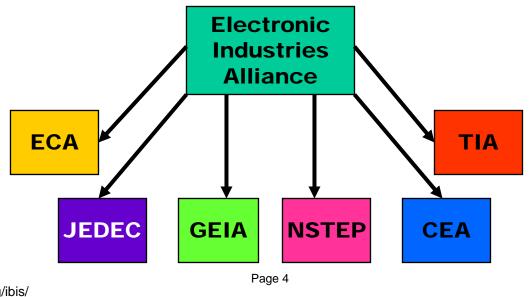

### **IBIS Organization**

- "IBIS Specification Committee"

- Informally, the IBIS Open Forum

- Manages IBIS, ICM (IBIS Interconnect Modeling) specifications

- Part of the GEIA SSTC

- **GEIA = Government Electronics & IT Association**

- SSTC = Systems, Standards and Technology Council

http://www.eigroup.org/ibis/

02/14/05

\*Other brands and names are the property of their respective owners

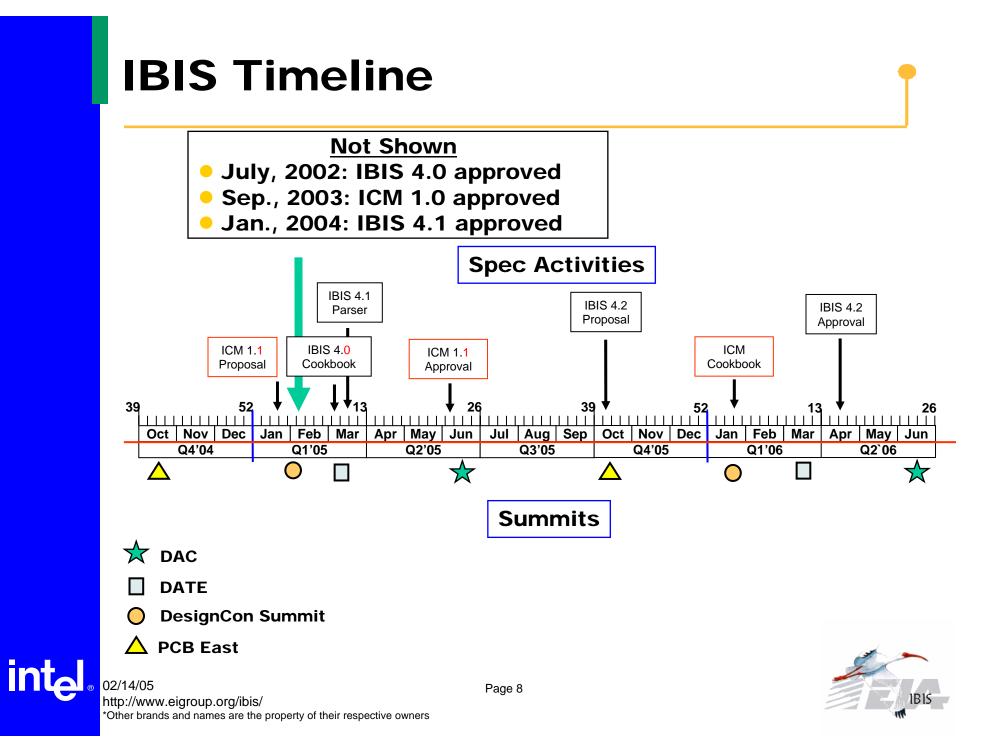

# **IBIS Open Forum**

- Primary Responsibilities

- Manage changes to the ICM and IBIS specifications

- Latest IBIS revision is 4.1, approved January 2004

- IBIS 3.2 in wide use, with IBIS 4.0 ramping up

- Maintain IBIS "Golden Syntax Parser" (closed source software)

- IBIS 4.1 parser expected Q1'05

- Maintain ICM "Golden Syntax Parser" (open source)

- ICM 1.0 with parser released Q4'03

- Foster technical advances and support user base

- Working Practices

- Meets every three weeks via teleconference

- Members may vote on specification changes

- Hold several annual summits in US and Europe

- Annual elections held during DAC in June

- Four Committees: Cookbook, Futures, Model Review, Quality

02/14/05 http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners

# **IBIS Open Forum Members**

- Twenty-three members in 2004

- Ansoft

- Applied Simulation Technology

- Cadence Design Systems

- Cisco

- Freescale

- Hitachi ULSI Systems

- Huawei

- IBM

- Intel

- LSI Logic

- Mentor Graphics

- Micron

- NEC

- Panasonic

- Samtec

- Siemens

- Sigrity

- Signal Integrity Software

- Synopsys

- TDA Systems

- Teraspeed Consulting Group

- Texas Instruments

- Zuken

- Trending to over 30 members in 2005

- New: Actel, Agere, AMD, Silicon Image, Xilinx...

02/14/05 http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners

# **IBIS Now Links to AMS**

#### IBIS 4.1 incorporates multi-lingual extensions

- Verilog-AMS

- VHDL-AMS

- Berkeley SPICE 3F5

- New IBIS keywords link to external code

- IBIS port structure with \*-AMS content

- IBIS Open Forum interested in WG liaison

- Buffer and SI analysis are growing applications for \*-AMS

- Interest in cross-domain (electrical, thermal) analysis

- Work together to support user-education efforts

**Relationship would have mutual benefits:**

- IBIS can provide feedback on \*-AMS language features

- Drive adoption by buffer design, SI communities

- Keep IBIS "in touch" with latest \*-AMS revisions, trends

intel

#### BACKUP

02/14/05 http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners IB15

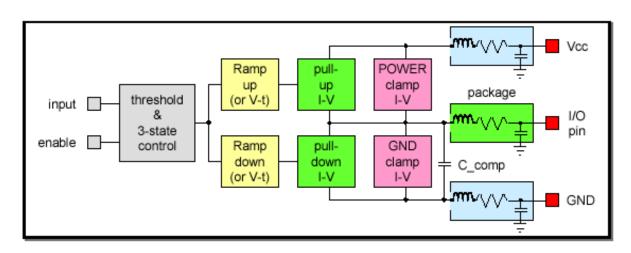

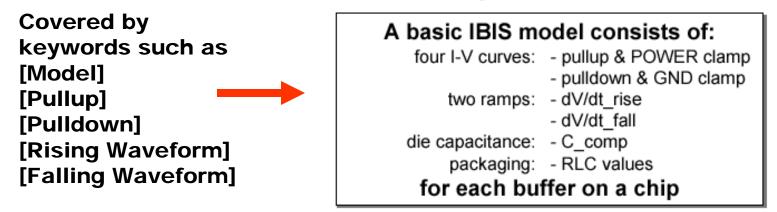

# **IBIS Model Format**

#### **Block diagram of CMOS buffer**

02/14/05 http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners

# **Example IBIS Model**

| *****          | *****                                                 | *****        | ******            | **** |  |

|----------------|-------------------------------------------------------|--------------|-------------------|------|--|

| [IBIS Ver]     | 3.2                                                   |              |                   |      |  |

| [File Name]    | example.ibs                                           |              |                   |      |  |

| [File Rev]     | 0.00                                                  |              |                   |      |  |

| [Date]         | 11/12/2004                                            |              |                   |      |  |

| [Source]       | From silicon level SPICE model at Intel Corporation.  |              |                   |      |  |

| [Notes]        | The following information is an example only          |              |                   |      |  |

| [Disclaimer]   | This information is for modeling purposes only.       |              |                   |      |  |

| [Copyright]    | Copyright 2004, IBIS Open Forum, All Rights Reserved. |              |                   |      |  |

| ********       | *****                                                 | *****        | ******            | **** |  |

| [Component]    | EXAMPLE                                               |              |                   |      |  |

| [Manufacturer] | Them Corporation                                      |              |                   |      |  |

| [Package]      |                                                       |              |                   |      |  |

|                | typ                                                   | min          | max               |      |  |

| R_pkg          | 0.0000hm                                              | 0.0000hm     | 0.0000hm          |      |  |

| L_pkg          | 0.00н                                                 | 0.00H        | 0.00H             |      |  |

| C_pkg          | 0.00F                                                 | 0.00F        | 0.00F             |      |  |

| *********      | ****                                                  | ******       | ******            | **** |  |

| [Pin] signal_n | ame model_nam                                         | ne           | R_pin L_pin C_pin |      |  |

| 1 Data         | EMP_B0I0                                              | P1F1F4P55890 |                   |      |  |

| 2 Reset        | EMP_B010                                              | P1F1F4P55890 |                   |      |  |

| ********       | ****                                                  | *****        | ******            | **** |  |

02/14/05

http://www.eigroup.org/ibis/

\*Other brands and names are the property of their respective owners

int

# Example IBIS Model (cont.)

| *****                                    | *****            | *****               | ******                 |

|------------------------------------------|------------------|---------------------|------------------------|

| [Model] ]                                | MP_B0I0P1F1F4P5  | 55890               |                        |

| Model_type                               | :/0              |                     |                        |

| vinl = 800.000m                          | 7                |                     |                        |

| 7 = 2.000                                |                  |                     |                        |

| meas = 1.500V                            |                  |                     |                        |

| Cref = 0.000F                            |                  |                     |                        |

|                                          |                  |                     |                        |

|                                          | ty               | /p mi               | .n max                 |

| C_comp                                   | 2.5              | 500pF 2.0           | 00pF 3.000pF           |

| [Voltage Range]                          | 3.3              | 300V 3.1            | .35V 3.465V            |

| [Power Clamp Re:                         | erence] 5.0      | )00V 4.7            | 50V 5.250V             |

| [Temperature Rai                         | nge] 50.0        | 0 100.0             | 0.0                    |

| <br> ****************<br> <br>[Pulldown] | *******          | ******              | ******                 |

|                                          |                  |                     |                        |

| Voltage                                  | I(t <sub>j</sub> | yp) I(min           | h) I(max)              |

|                                          | E+0 -256.260     | 00000E-6 -212.20000 | 000E-6 -300.6000000E-6 |

| -3.3000000                               |                  |                     |                        |

Page 12

http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners

int

02/14/05

### **IBIS Example – Pointing to AMS**

```

*************************

[External Circuit] BUFF-Verilog

Verilog-AMS

Language

Corner

file name

circuit name (module)

corner name

buffer typ.vams buffer io typ

Corner

Typ

buffer min.vams buffer io min

Corner

Min

buffer max.vams buffer io max

Corner

Max

Parameters List of parameters

Parameters delay rate preemphasis

Ports

List of port names (in same order as in VHDL-AMS)

A signal A puref A pdref A pcref A gcref A control

Ports

D drive D enable D receive

Ports

[End External Circuit]

```

Page 13

IBIS

# The long-term future of IBIS

- IBIS originally consisted of two aspects

- Device model behavioral data: V-t, I-V tables, etc.

- Behavior is a "snapshot" at certain conditions (Temp, etc.)

- Interface specs, for user automation: Vinh, Vmeas, etc.

- Power supply information fits in both categories

- As industry goes to AMS, some of IBIS redundant

- Behavioral modeling concepts in IBIS expanded in AMS

- AMS much more flexible, includes non-electrical areas

- Second aspect of IBIS still very useful

- AMS primarily describes device design behavior

- Evaluation criteria may or may not be included with AMS data

- Still exists a need for standard SI "wrapper" around AMS

- Should include evaluation criteria with AMS model

- Would help user judge device performance in system

- IBIS serves this need user-defined spec parameters coming...

02/14/05 http://www.eigroup.org/ibis/ \*Other brands and names are the property of their respective owners

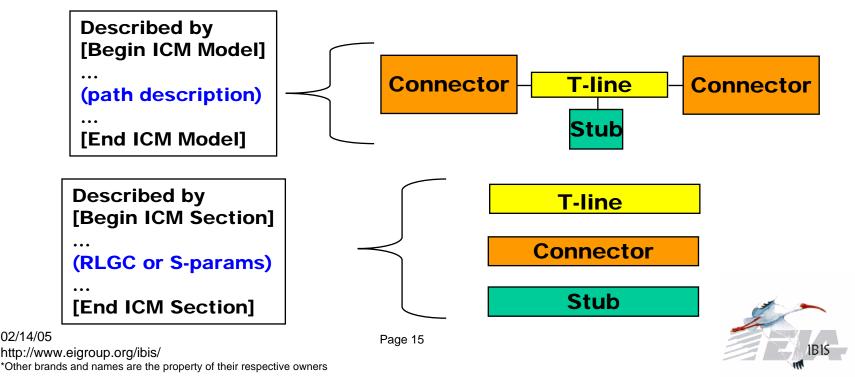

# **A Related Specification: ICM**

- ICM = IBIS Interconnect Modeling Specification

- Standard text format for interconnect modeling data

- "Interconnect" can be connector, cable, PCB traces or even an IC package

- Defines structure as path between "sections"

- Defines the electrical data for each section