# CS49300 Family DSP

# Multi-Standard Audio Decoder Family

#### Features

- CS4930X: DVD Audio Sub-family

- PES Layer decode for A/V sync

- DVD Audio Pack Layer Support

- Meridian Lossless Packing Specification (MLP)™

- Dolby Digital<sup>™</sup>, Dolby Pro Logic II<sup>™</sup> MPEG-2, Advanced Audio Coding Algorithm (AAC)

- MPEG Multichannel

- DTS Digital Surround<sup>™</sup>, DTS-ES Extended Surround<sup>™</sup>

- CS4931X: Broadcast Sub-family

- PES Layer decode for A/V sync

- Dolby Digital

- MPEG-2, Advanced Audio Coding Algorithm (AAC)

- MPEG-1 (Layers 1, 2, 3) Stereo

MPEG-2 (Layers 2, 3) Stereo

- CS4932X: AVR Sub-family

- Dolby Digital, Dolby Pro Logic II DTS & DTS-ES decoding with integrated DTS tables Crystal Original Surround (C.O.S.)

- MPEG-2, Advanced Audio Coding Algorithm (AAC)

- MPEG Multichannel

- MP3 (MPEG-1, Layer 3)

- CS49330: General Purpose Audio DSP

- THX<sup>®</sup> Surround EX<sup>™</sup> and THX<sup>®</sup> Ultra2 Cinema General Purpose AVR and Broadcast Audio Decoder (MPEG Multichannel, MPEG Stereo, MP3, C.O.S.) Car Audio

- Features are a super-set of the CS4923/4/5/6/7/8/9

- 8 channel output, including dual zone output capability

- Dynamic Channel Remapability Supports up to 192 kHz Fs @ 24-bit throughput

- Increased memory/MIPs

- SRAM Interface for increased delay and buffer capability

- **Dual-Precision Bass Manager**

- Enhance your system functionality via firmware upgrades through the Crystal Ware<sup>TM</sup> Software Licensing Program

#### Description

The CS493XX is a family of multichannel audio decoders intended to supersede the CS4923/4/5/6/7/8/9 family as the leader of audio decoding in both the DVD, broadcast and receiver markets. The family will be split into parts tailored for each of these distinct market segments.

For the DVD market, parts will be offered which support Meridian Lossless Packing (MLP), Dolby Digital, Dolby Pro Logic II, MPEG Multichannel, DTS Digital Surround, DTS-ES, AAC, and subsets thereof. For the receiver market, parts will be offered which support Dolby Digital, Dolby Pro Logic II, MPEG Multichannel, DTS Digital Surround, DTS-ES, AAC, and various virtualizers and PCM enhancement algorithms such as HDCD<sup>®</sup>, DTS Neo:6<sup>TM</sup>, Logic 7<sup>®</sup>, and SRS Circle Surround II<sup>®</sup>. For the broadcast market, parts will be offered which support Dolby Digital, AAC, MPEG-1, Layers 1,2 and 3, MPEG-2, Layers 2 and 3.

Under the Crystal brand, Cirrus Logic is the only single supplier of high-performance 24-bit multi-standard audio DSP decoders, DSP firmware, and high-resolution data converters. This combination of DSPs, system firmware, and data converters simplify rapid creation of world-class high-fidelity digital audio products for the Internet age.

#### Ordering Information: See page 82

|         | -               |                                          |

|---------|-----------------|------------------------------------------|

|         | APPLICATION     | CORE DECODER FUNCTIONALITY               |

| CS49300 | DVD Audio       | MLP, AC-3, AAC, DTS, MPEG 5.1, MP3, etc. |

| CS49310 | Broadcast       | AAC, AC-3, MPEG Stereo, MP3, etc.        |

| CS49311 | Broadcast       | AAC, MPEG Stereo, MP3, etc.              |

| CS49312 | Broadcast       | AC-3, MPEG Stereo, MP3, etc.             |

| CS49325 | AVR             | AC-3, COS, MPEG 5.1, MP3, etc.           |

| CS49326 | AVR             | AC-3, DTS, COS, MPEG 5.1, MP3, etc.      |

| CS49329 | AVR             | AC-3, AAC, DTS, MPEG 5.1, MP3, etc.      |

| CS49330 | Car Audio DSP   | Car Audio Code                           |

| CS49330 | General Purpose | MPEG 5.1, MPEG Stereo, MP3, C.O.S., etc  |

| CS49330 | Post-Processor  | DPP, THX Surround EX, THX Ultra2 Cinema  |

Preliminary Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

#### CIRRUS LOGIC®

P.O. Box 17847, Austin, Texas 78760 (512) 445 7222 FAX: (512) 445 7581 http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2001 (All Rights Reserved)

#### TABLE OF CONTENTS

| 1.1 Absolute Maximum Ratings       6         1.2 Recommended Operating Conditions       6         1.3 Digital D.C. Characteristics       6         1.4 Power Supply Characteristics       6         1.5 Switching Characteristics       7         1.6 Switching Characteristics       7         1.7 Switching Characteristics       11         1.8 Switching Characteristics       10 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3 Digital D.C. Characteristics       6         1.4 Power Supply Characteristics       6         1.5 Switching Characteristics       7         1.6 Switching Characteristics       CLKIN         7       7         1.7 Switching Characteristics       Intel <sup>®</sup> Host Mode         8       8         1.8 Switching Characteristics       Motorola <sup>®</sup> Host Mode    |

| 1.3 Digital D.C. Characteristics       6         1.4 Power Supply Characteristics       6         1.5 Switching Characteristics       7         1.6 Switching Characteristics       CLKIN         7       7         1.7 Switching Characteristics       Intel <sup>®</sup> Host Mode         8       8         1.8 Switching Characteristics       Motorola <sup>®</sup> Host Mode    |

| 1.5 Switching Characteristics       — RESET       7         1.6 Switching Characteristics       — CLKIN       7         1.7 Switching Characteristics       — Intel <sup>®</sup> Host Mode       8         1.8 Switching Characteristics       — Motorola <sup>®</sup> Host Mode       10                                                                                             |

| 1.5 Switching Characteristics       — RESET       7         1.6 Switching Characteristics       — CLKIN       7         1.7 Switching Characteristics       — Intel <sup>®</sup> Host Mode       8         1.8 Switching Characteristics       — Motorola <sup>®</sup> Host Mode       10                                                                                             |

| 1.6 Switching Characteristics — CLKIN                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>1.7 Switching Characteristics — Intel<sup>®</sup> Host Mode</li></ul>                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.9 Switching Characteristics — SP <sup>I</sup> Control Port                                                                                                                                                                                                                                                                                                                          |

| 1.10 Switching Characteristics — I <sup>2</sup> C <sup>®</sup> Control Port                                                                                                                                                                                                                                                                                                           |

| 1.11 Switching Characteristics — Digital Audio Input16                                                                                                                                                                                                                                                                                                                                |

| 1.12 Switching Characteristics — CMPDAT, CMPCLK                                                                                                                                                                                                                                                                                                                                       |

| 1.13 Switching Characteristics — Parallel Data Input                                                                                                                                                                                                                                                                                                                                  |

| 1.14 Switching Characteristics — Digital Audio Output19                                                                                                                                                                                                                                                                                                                               |

| 2. FAMILY OVERVIEW                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1 Multichannel Decoder Family of Parts21                                                                                                                                                                                                                                                                                                                                            |

| 3. TYPICAL CONNECTION DIAGRAMS                                                                                                                                                                                                                                                                                                                                                        |

| 3.1 Multiplexed Pins                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2 Termination Requirements                                                                                                                                                                                                                                                                                                                                                          |

| 3.3 Phase Locked Loop Filter                                                                                                                                                                                                                                                                                                                                                          |

| 4. POWER                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1 Decoupling                                                                                                                                                                                                                                                                                                                                                                        |

| 4.2 Analog Power Conditioning                                                                                                                                                                                                                                                                                                                                                         |

#### **Contacting Cirrus Logic Support**

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts

Dolby Digital, AC-3, Dolby Pro Logic, Dolby Pro Logic II, Dolby Surround, Surround EX, Virtual Dolby Digital, MLP and the "AAC" logo are trademarks and the "Dolby Digital" logo, "Dolby Digital with Pro Logic II" logo, "Dolby" and the double-"D" symbol are registered trademarks of Dolby Laboratories Licensing Corporation. DTS, DTS Digital Surround, DTS-ES Extended Surround, DTS Neo:6, and DTS Virtual 5.1 are trademarks and the "DTS", "DTS-ES", "DTS Virtual 5.1" logos are registered trademarks of the Digital Theater Systems Corporation. The "MPEG Logo" is a registered trademark of Philips Electronics N.V. Home THX Cinema and THX are registered trademarks of Lucasfilm Ltd. Surround EX is a jointly developed technology of THX and Dolby Labs, Inc. AAC (Advanced Audio Coding) is an "MPEG-2-standard-based" digital audio compression algorithm (offering up 5.1 discrete decoded channels for this implementation) collaboratively developed by AT&T, the Fraunhofer Institute, Dolby Laboratories, and the Sony Corporation noregards to the MP3 capable functionality of the CS49300 Family DSP (via downloading of mp3\_493xx\_v.v.ld and mp3e\_493xx\_v.v.ld application codes) the following statements are applicable: "Supply of this product conveys a license for personal, private and non-commercial use. MPEG Layer-3 audio decoding technology licensed from Fraunhofer IIS and THOMSON Multimedia." MLP and Meridian Lossless Packing are registered trademarks of Lexicon. SRS CircleSurround, and SRS TruSurround are trademarks of SRS Labs, Inc. The HDCD logo, HDCD, High Definition Compatible Digital and Pacific Microsonics are either registered trademarks of Pacific Microsonics, Inc. in the United States 3,638,074; 5,638,074; 5,640,161; 5,872,531; 5,808,574; 5,838,274; 5,854,600; 5,864,311; and in Auştralia: 669114; with other patents pending. Intel is a registered trademark of Intel Corporation. Motorola is a registered trademark of Philips PC Patent Rights to use those components in a standard <sup>12</sup>C system. The "Crystal Logo" and the "Crystal D

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without to relectronic files may be opied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without to relectronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

# CS49300 Family DSP

|    | 4.3 Ground                                            |    |

|----|-------------------------------------------------------|----|

|    | 4.4 Pads                                              | 32 |

| 5. | CLOCKING                                              | 32 |

| 6. | CONTROL                                               | 32 |

|    | 6.1 Serial Communication                              |    |

|    | 6.1.1 SPI Communication                               |    |

|    | 6.1.2 I <sup>2</sup> C Communication                  | 35 |

|    | 6.1.3 INTREQ Behavior: A Special Case                 |    |

|    | 6.2 Parallel Host Communication                       |    |

|    | 6.2.1 Intel Parallel Host Communication Mode          |    |

|    | 6.2.2 Motorola Parallel Host Communication Mode       |    |

|    | 6.2.3 Procedures for Parallel Host Mode Communication | 46 |

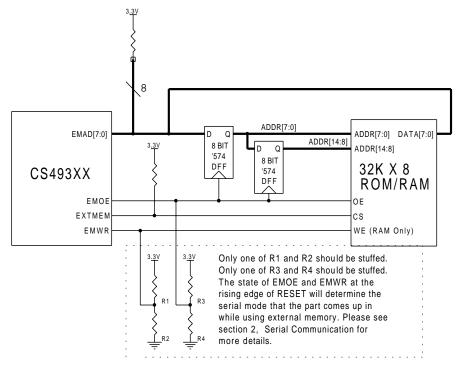

| 7. | EXTERNAL MEMORY                                       | 48 |

|    | 7.1 Non-Paged Memory                                  | 49 |

|    | 7.2 Paged Memory                                      | 49 |

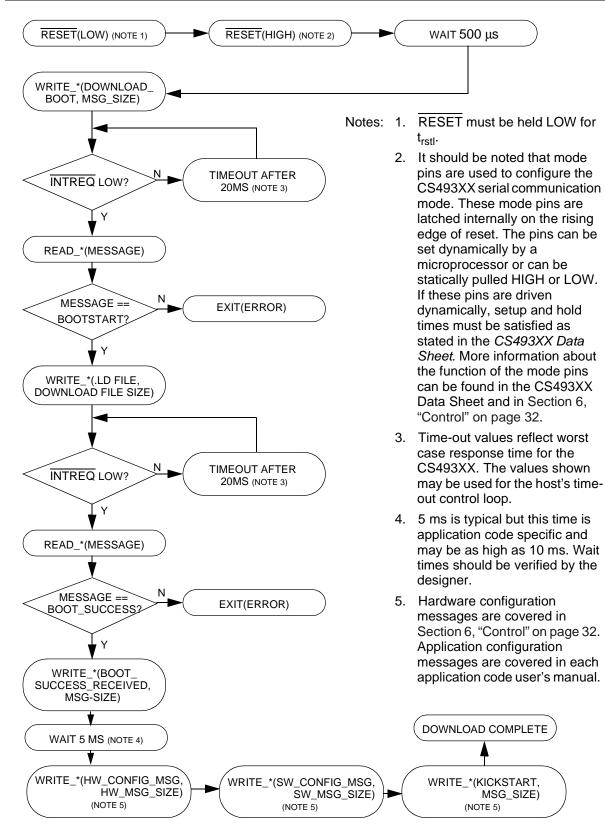

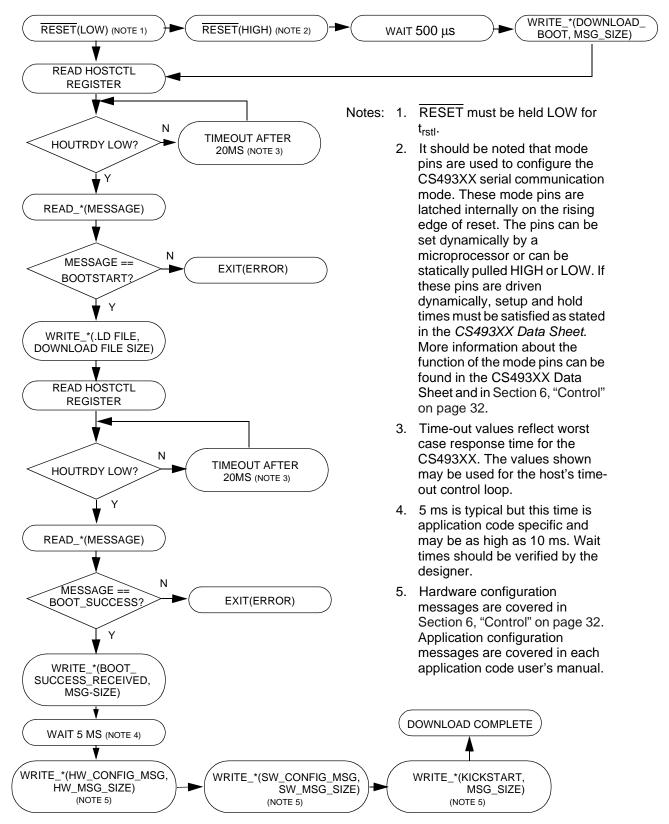

| 8. | BOOT PROCEDURE & RESET                                | 52 |

|    | 8.1 Host Boot                                         |    |

|    | 8.2 Autoboot                                          |    |

|    | 8.2.1 Autoboot INTREQ Behavior                        | 55 |

|    | 8.3 Internal Boot                                     | 57 |

|    | 8.4 Application Failure Boot Message                  | 57 |

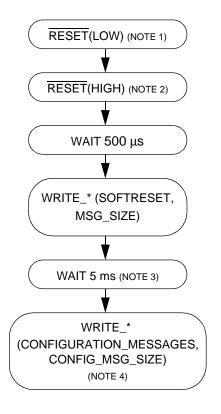

|    | 8.5 Resetting the CS493XX                             |    |

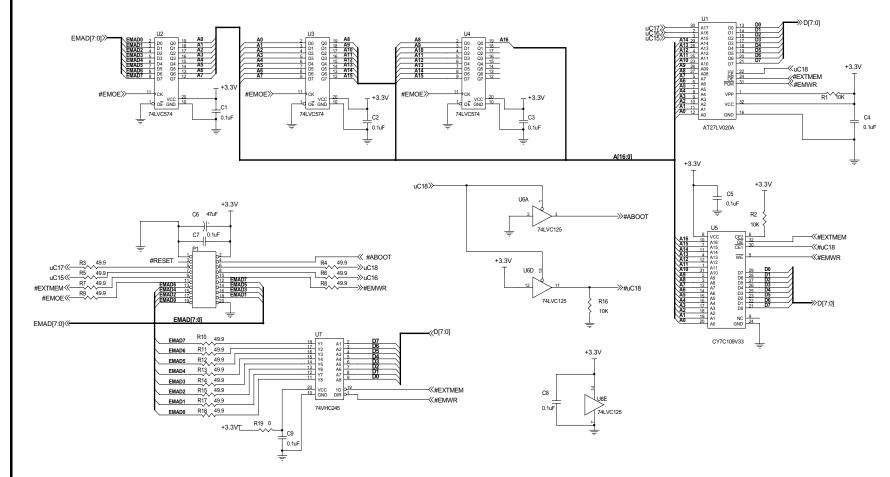

|    | 8.6 External Memory Examples                          |    |

|    | 8.6.1 Non-Paged Autoboot Memory                       |    |

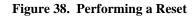

|    | 8.6.2 32 Kilobyte Paged Autoboot Memory               |    |

|    | 8.7 CDB49300-MEMA.0                                   |    |

| 9. | HARDWARE CONFIGURATION                                | 63 |

| 10 | .DIGITAL INPUT & OUTPUT                               | 63 |

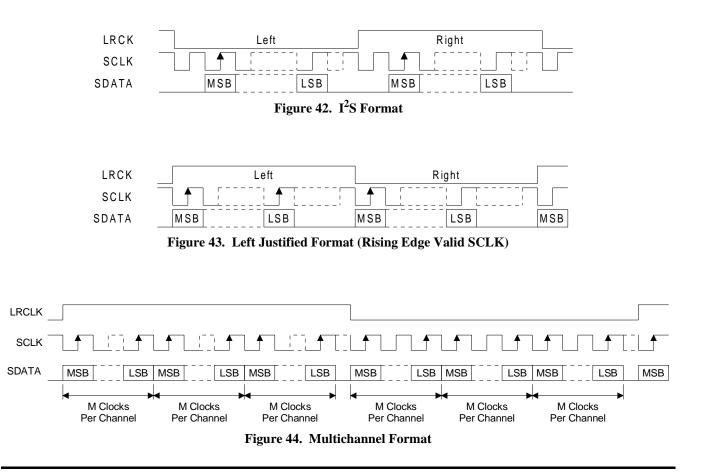

|    | 10.1 Digital Audio Formats                            |    |

|    | 10.1.1 I <sup>2</sup> S                               | 63 |

|    | 10.1.2 Left Justified                                 | 63 |

|    | 10.1.3 Multichannel                                   | 63 |

|    | 10.2 Digital Audio Input Port                         |    |

|    | 10.3 Compressed Data Input Port                       |    |

|    | 10.4 Byte Wide Digital Audio Data Input               |    |

|    | 10.4.1 Parallel Delivery with Parallel Control        |    |

|    | 10.4.2 Parallel Delivery with Serial Control          | 66 |

|    | 10.5 Digital Audio Output Port                        | 66 |

|    | 10.5.1 IEC60958 Output                                |    |

| 11 | HARDWARE CONFIGURATION                                |    |

|    | 11.1 Address Checking                                 |    |

|    | 11.2 Input Data Hardware Configuration                |    |

|    | 11.2.1 Input Configuration Considerations             |    |

|    | 11.3 Output Data Hardware Configuration               |    |

|    | 11.3.1 Output Configuration Considerations            |    |

|    | 11.4 Creating Hardware Configuration Messages         |    |

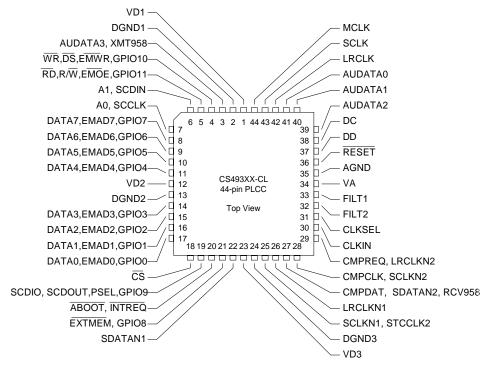

|    | .PIN DESCRIPTIONS                                     |    |

| 13 | ORDERING INFORMATION                                  | 81 |

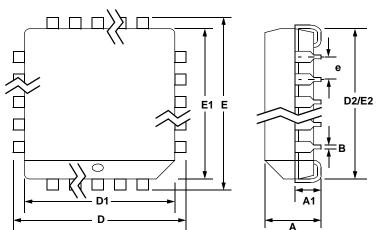

| 14 | .PACKAGE DIMENSIONS                                   | 81 |

# LIST OF FIGURES

| Figure 1. RESET Timing                                                                    | 7  |

|-------------------------------------------------------------------------------------------|----|

| Figure 2. CLKIN with CLKSEL = VSS = PLL Enable                                            | 7  |

| Figure 3. Intel <sup>®</sup> Parallel Host Mode Read Cycle                                | 9  |

| Figure 4. Intel <sup>®</sup> Parallel Host Mode Write Cycle                               | 9  |

| Figure 5. Motorola <sup>®</sup> Parallel Host Mode Read Cycle                             | 11 |

| Figure 6. Motorola <sup>®</sup> Parallel Host Mode Write Cycle                            | 11 |

| Figure 7. SPI Control Port Timing                                                         | 13 |

| Figure 8. I <sup>2</sup> C <sup>®</sup> Control Port Timing                               | 15 |

| Figure 9. Digital Audio Input Data, Master and Slave Clock Timing                         | 17 |

| Figure 10. Serial Compressed Data Timing                                                  | 18 |

| Figure 11. Parallel Data Timing (when not in a parallel control mode)                     | 18 |

| Figure 12. Digital Audio Output Data, Input and Output Clock Timing                       | 20 |

| Figure 13. I <sup>2</sup> C <sup>®</sup> Control                                          | 26 |

| Figure 14. I <sup>2</sup> C <sup>®</sup> Control with External Memory                     | 27 |

| Figure 15. SPI Control                                                                    | 28 |

| Figure 16. SPI Control with External Memory                                               | 29 |

| Figure 17. Intel <sup>®</sup> Parallel Control Mode                                       | 30 |

| Figure 18. Motorola <sup>®</sup> Parallel Control Mode                                    | 31 |

| Figure 19. SPI Write Flow Diagram                                                         | 33 |

| Figure 20. SPI Read Flow Diagram                                                          | 34 |

| Figure 21. SPI Timing                                                                     | 36 |

| Figure 22. I <sup>2</sup> C <sup>®</sup> Write Flow Diagram                               | 37 |

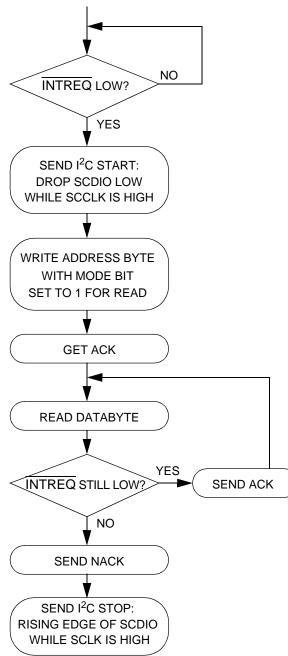

| Figure 23. I <sup>2</sup> C <sup>®</sup> Read Flow Diagram                                | 38 |

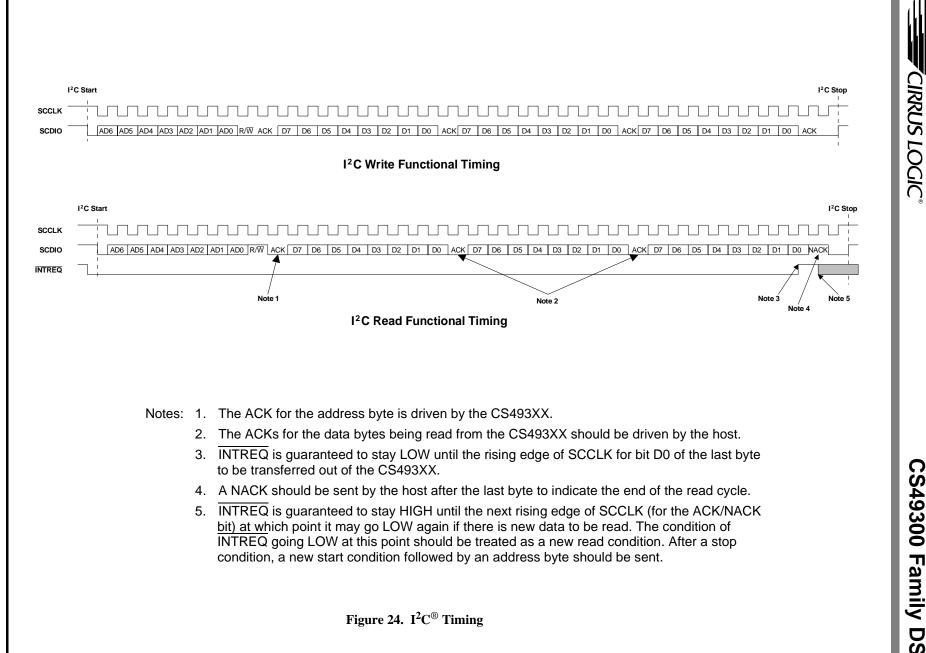

| Figure 24. I <sup>2</sup> C <sup>®</sup> Timing                                           | 40 |

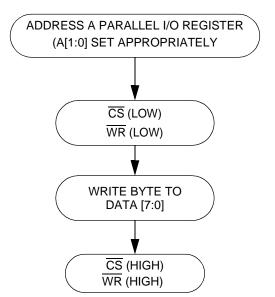

| Figure 24. Intel Mode, One-Byte Write Flow Diagram                                        | 44 |

| Figure 25. Intel Mode, One-Byte Read Flow Diagram                                         | 44 |

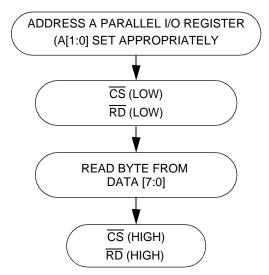

| Figure 26. Motorola Mode, One-Byte Write Flow Diagram                                     | 45 |

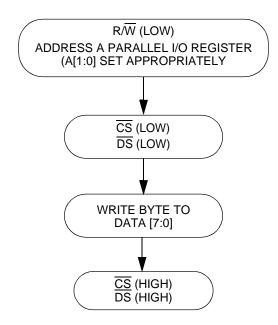

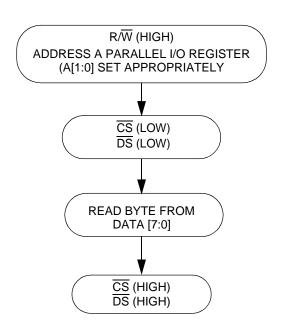

| Figure 27. Motorola Mode, One-Byte Read Flow Diagram                                      | 46 |

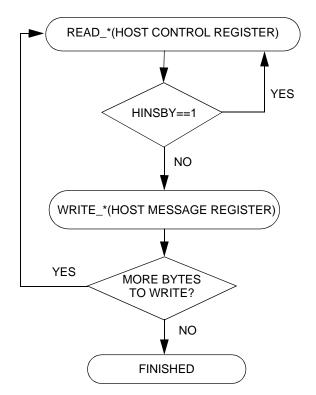

| Figure 28. Typical Parallel Host Mode Control Write Sequence Flow Diagram                 | 47 |

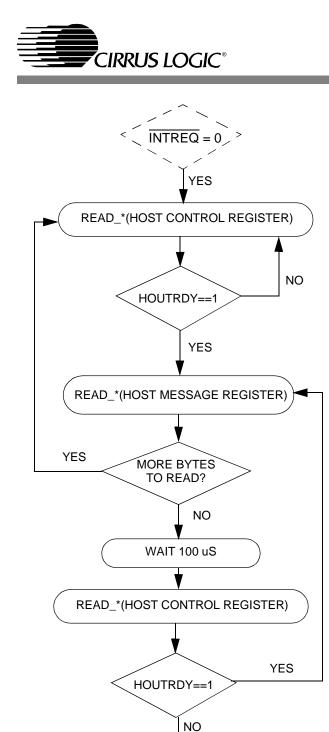

| Figure 29. Typical Parallel Host Mode Control Read Sequence Flow Diagram                  | 48 |

| Figure 30. External Memory Interface                                                      | 51 |

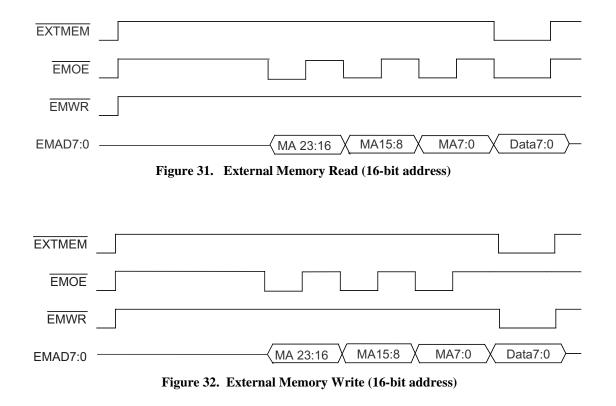

| Figure 31. External Memory Read (16-bit address)                                          | 51 |

| Figure 32. External Memory Write (16-bit address)                                         | 51 |

| Figure 33. Typical Serial Boot and Download Procedure                                     | 53 |

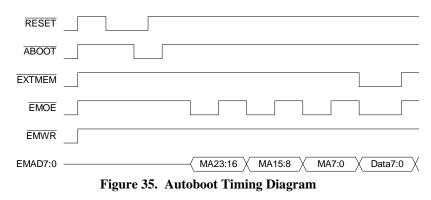

| Figure 34. Autoboot Timing Diagram                                                        | 54 |

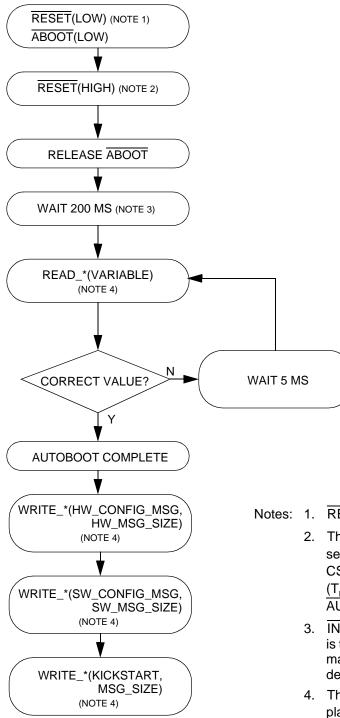

| Figure 35. Autoboot Sequence                                                              | 56 |

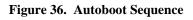

| Figure 36. Autoboot INTREQ Behavior                                                       | 57 |

| Figure 37. Performing a Reset                                                             | 58 |

| Figure 38. Non-Paged Memory                                                               | 59 |

| Figure 39. Example Contents of a Paged 32 Kilobytes External Memory (Total 256 Kilobytes) | 60 |

| Figure 40. CDB49300-MEMA.0 Daughter Card for the CDB4923/30-REV-A.0                       | 62 |

| Figure 41. I <sup>2</sup> S Format                                          | 64 |

|-----------------------------------------------------------------------------|----|

| Figure 42. Left Justified Format (Rising Edge Valid SCLK)                   | 64 |

| Figure 43. Multichannel Format                                              | 64 |

| LIST OF TABLES                                                              |    |

| Table 1. PLL Filter Component Values                                        | 25 |

| Table 2. Host Modes                                                         |    |

| Table 3. SPI Communication Signals                                          | 33 |

| Table 4. I <sup>2</sup> C® Communication Signals                            | 35 |

| Table 5. Parallel Input/Output Registers                                    | 42 |

| Table 6. Intel Mode Communication Signals                                   | 43 |

| Table 7. Motorola Mode Communication Signals                                | 45 |

| Table 8. Memory Interface Pins                                              |    |

| Table 9. Boot Write Messages                                                | 52 |

| Table 10. Boot Read Messages                                                | 52 |

| Table 11. Memory Requirements for Example 5.1, 6.1 and 7.1 Channel Systems  | 61 |

| Table 12. Digital Audio Input Port                                          | 65 |

| Table 13. Compressed Data Input Port                                        | 66 |

| Table 14. Digital Audio Output Port                                         | 67 |

| Table 15. MCLK/SCLK Master Mode Ratios                                      | 68 |

| Table 16. Output Channel Mapping                                            | 68 |

| Table 17. Input Data Type Configuration (Input Parameter A)                 | 70 |

| Table 18. Input Data Format Configuration (Input Parameter B)               | 70 |

| Table 19. Input SCLK Polarity Configuration (Input Parameter C)             | 72 |

| Table 20. Input FIFO Setup Configuration (Input Parameter D)                | 72 |

| Table 21. Output Clock Configuration (Parameter A)                          |    |

| Table 22. Output Data Format Configuration (Parameter B)                    | 73 |

| Table 23. Output MCLK Configuration (Parameter C)                           | 74 |

| Table 24. Output SCLK Configuration (Parameter D)                           | 74 |

| Table 25. Output SCLK Polarity Configuration (Parmeter E)                   | 74 |

| Table 26. Example Values to be Sent to CS493XX After Download or Soft Reset | 76 |

## 1. CHARACTERISTICS AND SPECIFICATIONS

#### 1.1. Absolute Maximum Ratings

(AGND, DGND = 0 V; all voltages with respect to 0 V)

| Parameter                              |                                                    | Symbol           | Min               | Max                 | Unit        |

|----------------------------------------|----------------------------------------------------|------------------|-------------------|---------------------|-------------|

| DC power supplies:                     | Positive digital<br>Positive analog<br>  VA  –  VD | VD<br>VA         | -0.3<br>-0.3<br>- | 2.75<br>2.75<br>0.3 | V<br>V<br>V |

| Input current, any pin except supplies |                                                    | I <sub>in</sub>  | -                 | ±10                 | mA          |

| Digital input voltage                  |                                                    | V <sub>IND</sub> | -0.3              | 3.63                | V           |

| Storage temperature                    |                                                    | T <sub>stg</sub> | -65               | 150                 | °C          |

**CAUTION:** Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# 1.2. Recommended Operating Conditions

| (AGND, DGND = 0 V; all voltages with respect to 0 V) |  |

|------------------------------------------------------|--|

|                                                      |  |

| Parameter                        | Symbol         | Min  | Тур | Мах  | Unit |

|----------------------------------|----------------|------|-----|------|------|

| DC power supplies: Positive digi | al VD          | 2.37 | 2.5 | 2.63 | V    |

| Positive anal                    | og VA          | 2.37 | 2.5 | 2.63 | V    |

| VA  –  V                         | <b>P</b>       | -    | -   | 0.3  | V    |

| Ambient operating temperature    | T <sub>A</sub> | 0    | -   | 70   | °C   |

#### 1.3. Digital D.C. Characteristics

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; measurements performed under static conditions.)

| Parameter                                            | Symbol          | Min             | Тур | Max       | Unit |

|------------------------------------------------------|-----------------|-----------------|-----|-----------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2.0             | -   | -         | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -               | -   | 0.8       | V    |

| High-level output voltage at $I_O = -2.0 \text{ mA}$ | V <sub>OH</sub> | $VD \times 0.9$ | -   | -         | V    |

| Low-level output voltage at $I_0 = 2.0 \text{ mA}$   | V <sub>OL</sub> | -               | -   | VD × 0.11 | V    |

| Input leakage current                                | l <sub>in</sub> | -               | -   | 1.0       | μA   |

# 1.4. Power Supply Characteristics

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; measurements performed under operating conditions)

|                       | Parameter                  | Symbol | Min | Тур | Max | Unit |

|-----------------------|----------------------------|--------|-----|-----|-----|------|

| Power supply current: | Digital operating: VD[3:1] |        | -   | 200 | 310 | mA   |

|                       | Analog operating: VA       |        | -   | 1.7 | 4   | mA   |

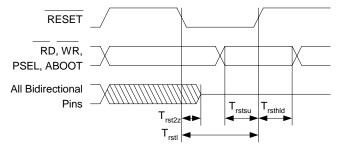

# 1.5. Switching Characteristics — RESET

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                     |          | Symbol              | Min | Max | Unit |

|-----------------------------------------------|----------|---------------------|-----|-----|------|

| RESET minimum pulse width low (-CL)           | (Note 1) | T <sub>rstl</sub>   | 100 | -   | μs   |

| RESET minimum pulse width low (-IL)           | (Note 1) | T <sub>rstl</sub>   | 530 | -   | μs   |

| All bidirectional pins high-Z after RESET low | (Note 2) | T <sub>rst2z</sub>  | -   | 50  | ns   |

| Configuration bits setup before RESET high    |          | T <sub>rstsu</sub>  | 50  | -   | ns   |

| Configuration bits hold after RESET high      |          | T <sub>rsthld</sub> | 15  | -   | ns   |

- Notes: 1. The minimum RESET pulse listed above is valid only when using the recommended pull-up/pull-down resistors on the RD, WR and PSEL mode pins. For Rev. D and older parts, pull-up/pull-down resistors should be 4.7 k. For Rev. E and newer parts, pull-up/pull-down resistors should be 3.3 k.

- 2. This specification is characterized but not production tested.

Figure 1. RESET Timing

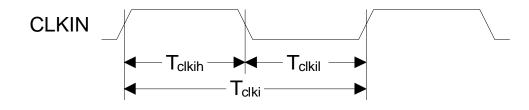

#### 1.6. Switching Characteristics — CLKIN

$(T_A = 25 \degree C; VA, VD[3:1] = 2.5 V \pm 5\%; Inputs: Logic 0 = DGND, Logic 1 = VD, C_L = 20 \text{ pF})$

| Parameter                                   | Symbol             | Min | Max  | Unit |

|---------------------------------------------|--------------------|-----|------|------|

| CLKIN period for internal DSP clock mode    | T <sub>clki</sub>  | 35  | 3800 | ns   |

| CLKIN high time for internal DSP clock mode | T <sub>clkih</sub> | 18  |      | ns   |

| CLKIN low time for internal DSP clock mode  | T <sub>clkil</sub> | 18  |      | ns   |

Figure 2. CLKIN with CLKSEL = VSS = PLL Enable

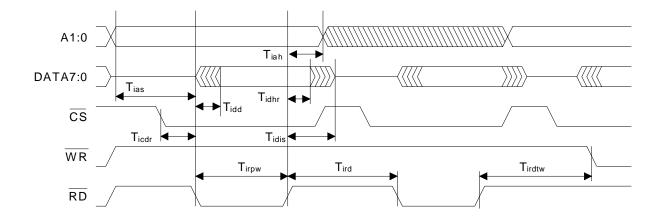

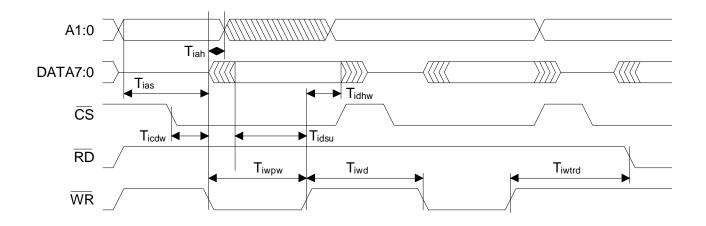

# **1.7.** Switching Characteristics — Intel<sup>®</sup> Host Mode

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                                                                                                     |          | Symbol             | Min          | Max      | Unit |

|-------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|--------------|----------|------|

| Address setup before $\overline{CS}$ and $\overline{RD}$ low or $\overline{CS}$ and $\overline{RD}$                           | WR low   | T <sub>ias</sub>   | 5            | -        | ns   |

| Address hold time after $\overline{CS}$ and $\overline{RD}$ low or $\overline{CS}$ and                                        | d WR low | T <sub>iah</sub>   | 5            | -        | ns   |

| Delay between $\overline{RD}$ then $\overline{CS}$ low or $\overline{CS}$ then $\overline{RD}$ lo                             | w        | T <sub>icdr</sub>  | 0            | $\infty$ | ns   |

| Data valid after $\overline{CS}$ and $\overline{RD}$ low                                                                      | (Note 3) | T <sub>idd</sub>   | -            | 21       | ns   |

| CS and RD low for read                                                                                                        | (Note 1) | T <sub>irpw</sub>  | DCLKP + 10   | -        | ns   |

| Data hold time after $\overline{CS}$ or $\overline{RD}$ high                                                                  |          | T <sub>idhr</sub>  | 5            | -        | ns   |

| Data high-Z after $\overline{CS}$ or $\overline{RD}$ high                                                                     | (Note 2) | T <sub>idis</sub>  | -            | 22       | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{RD}}$ high to $\overline{\text{CS}}$ and $\overline{\text{RD}}$ low for next read  | (Note 1) | T <sub>ird</sub>   | 2*DCLKP + 10 | -        | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{RD}}$ high to $\overline{\text{CS}}$ and $\overline{\text{WR}}$ low for next write | (Note 1) | T <sub>irdtw</sub> | 2*DCLKP + 10 | -        | ns   |

| Delay between $\overline{WR}$ then $\overline{CS}$ low or $\overline{CS}$ then $\overline{WR}$ is                             | wo       | T <sub>icdw</sub>  | 0            | $\infty$ | ns   |

| Data setup before CS or WR high                                                                                               |          | T <sub>idsu</sub>  | 20           | -        | ns   |

| $\overline{\text{CS}}$ and $\overline{\text{WR}}$ low for write                                                               | (Note 1) | T <sub>iwpw</sub>  | DCLKP + 10   | -        | ns   |

| Data hold after $\overline{CS}$ or $\overline{WR}$ high                                                                       |          | T <sub>idhw</sub>  | 5            | -        | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{WR}}$ high to $\overline{\text{CS}}$ and $\overline{\text{RD}}$ low for next read  | (Note 1) | T <sub>iwtrd</sub> | 2*DCLKP + 10 | -        | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{WR}}$ high to $\overline{\text{CS}}$ and $\overline{\text{WR}}$ low for next write | (Note 1) | T <sub>iwd</sub>   | 2*DCLKP + 10 | -        | ns   |

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP = 1/DCLK. The DSP clock can be defined as follows:

External CLKIN Mode: DCLK == CLKIN/4 before and during boot DCLK == CLKIN after boot

Internal Clock Mode: DCLK == 10MHz before and during boot, i.e. DCLKP == 100ns DCLK == 65 MHz after boot, i.e. DCLKP == 15.4ns

It should be noted that DCLK for the internal clock mode is application specific. The application code users guide should be checked to confirm DCLK for the particular application.

- 2. This specification is characterized but not production tested.

- 3. See T<sub>idd</sub> from Intel Host Mode in Table 6 on page 43

# CS49300 Family DSP

Figure 3. Intel<sup>®</sup> Parallel Host Mode Read Cycle

Figure 4. Intel<sup>®</sup> Parallel Host Mode Write Cycle

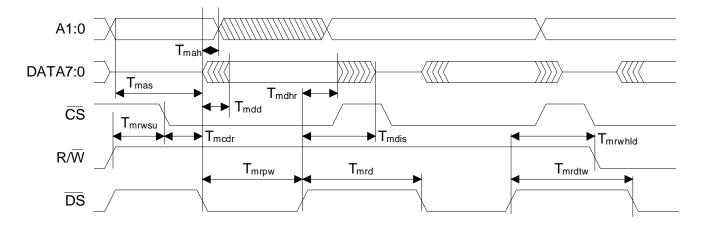

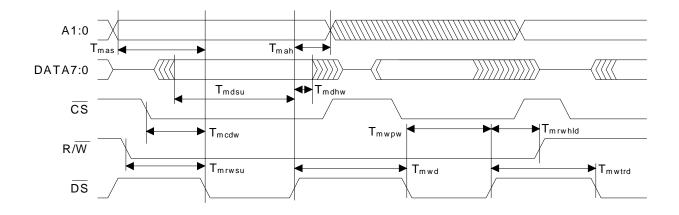

# 1.8. Switching Characteristics — Motorola<sup>®</sup> Host Mode

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                                                                                                      |                       | Symbol              | Min          | Мах | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|--------------|-----|------|

| Address setup before CS and DS low                                                                                             |                       | T <sub>mas</sub>    | 5            | -   | ns   |

| Address hold time after $\overline{CS}$ and $\overline{DS}$ low                                                                |                       | T <sub>mah</sub>    | 5            | -   | ns   |

| Delay between $\overline{\text{DS}}$ then $\overline{\text{CS}}$ low or $\overline{\text{CS}}$ then $\overline{\text{DS}}$ low |                       | T <sub>mcdr</sub>   | 0            | ~   | ns   |

| Data valid after $\overline{CS}$ and $\overline{RD}$ low with $R/\overline{W}$ high                                            | (Note 3)              | T <sub>mdd</sub>    | -            | 21  | ns   |

| CS and DS low for read                                                                                                         | (Note 1)              | T <sub>mrpw</sub>   | DCLKP + 10   | -   | ns   |

| Data hold time after $\overline{CS}$ or $\overline{DS}$ high after read                                                        |                       | T <sub>mdhr</sub>   | 5            | -   | ns   |

| Data high-Z after CS or DS high low after read                                                                                 | (Note 2)              | T <sub>mdis</sub>   | -            | 22  | ns   |

| $\overline{\text{CS}}$ or $\overline{\text{DS}}$ high to $\overline{\text{CS}}$ and $\overline{\text{DS}}$ low for next read   | (Note 1)              | T <sub>mrd</sub>    | 2*DCLKP + 10 | -   | ns   |

| CS or DS high to CS and DS low for next write                                                                                  | (Note 1)              | T <sub>mrdtw</sub>  | 2*DCLKP + 10 | -   | ns   |

| Delay between $\overline{\text{DS}}$ then $\overline{\text{CS}}$ low or $\overline{\text{CS}}$ then $\overline{\text{DS}}$ low |                       | T <sub>mcdw</sub>   | 0            | 8   | ns   |

| Data setup before CS or DS high                                                                                                |                       | T <sub>mdsu</sub>   | 20           | -   | ns   |

| CS and DS low for write                                                                                                        | (Note 1)              | T <sub>mwpw</sub>   | DCLKP + 10   | -   | ns   |

| $R/\overline{W}$ setup before $\overline{CS}$ AND $\overline{DS}$ low                                                          |                       | T <sub>mrwsu</sub>  | 5            | -   | ns   |

| $R/\overline{W}$ hold time after $\overline{CS}$ or $\overline{DS}$ high                                                       |                       | T <sub>mrwhld</sub> | 5            | -   | ns   |

| Data hold after CS or DS high                                                                                                  |                       | T <sub>mdhw</sub>   | 5            | -   | ns   |

| $\overline{CS}$ or $\overline{DS}$ high to $\overline{CS}$ and $\overline{DS}$ low with R/W high for                           | next read<br>(Note 1) | T <sub>mwtrd</sub>  | 2*DCLKP + 10 | -   | ns   |

| $\overline{CS}$ or $\overline{DS}$ high to $\overline{CS}$ and $\overline{DS}$ low for next write                              | (Note 1)              | T <sub>mwd</sub>    | 2*DCLKP + 10 | -   | ns   |

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP = 1/DCLK. The DSP clock can be defined as follows:

External CLKIN Mode: DCLK == CLKIN/4 before and during boot DCLK == CLKIN after boot

Internal Clock Mode: DCLK == 10MHz before and during boot, i.e. DCLKP == 100ns DCLK == 65 MHz after boot, i.e. DCLKP == 15.4ns

It should be noted that DCLK for the internal clock mode is application specific. The application code users guide should be checked to confirm DCLK for the particular application.

- 2. This specification is characterized but not production tested.

- 3. See  $T_{mdd}$  from Motorola Host Mode in Table 7 on page 45

Figure 5. Motorola<sup>®</sup> Parallel Host Mode Read Cycle

Figure 6. Motorola<sup>®</sup> Parallel Host Mode Write Cycle

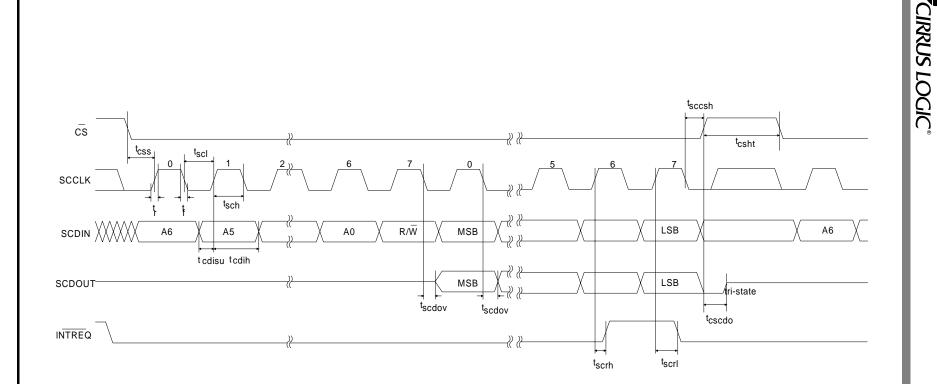

# 1.9. Switching Characteristics — SPI Control Port

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                         |             | Symbol             | Min | Max      | Units |

|---------------------------------------------------|-------------|--------------------|-----|----------|-------|

| SCCLK clock frequency                             | (Note 1)    | f <sub>sck</sub>   | -   | 2000     | kHz   |

| CS falling to SCCLK rising                        |             | t <sub>css</sub>   | 20  | -        | ns    |

| Rise time of SCCLK line                           | (Note 7)    | t <sub>r</sub>     | -   | 50       | ns    |

| Fall time of SCCLK lines                          | (Note 7)    | t <sub>f</sub>     | -   | 50       | ns    |

| SCCLK low time                                    |             | t <sub>scl</sub>   | 150 | -        | ns    |

| SCCLK high time                                   |             | t <sub>sch</sub>   | 150 | -        | ns    |

| Setup time SCDIN to SCCLK rising                  |             | t <sub>cdisu</sub> | 50  | -        | ns    |

| Hold time SCCLK rising to SCDIN                   | (Note 2)    | t <sub>cdih</sub>  | 50  | -        | ns    |

| Transition time from SCCLK to SCDOUT valid        | (Note 3)    | t <sub>scdov</sub> | -   | 40       | ns    |

| Time from SCCLK rising to INTREQ rising           | (Note 4)    | t <sub>scrh</sub>  | -   | 200      | ns    |

| Rise time for INTREQ                              | (Note 4)    | t <sub>rr</sub>    | -   | (Note 6) | ns    |

| Hold time for INTREQ from SCCLK rising            | (Note 5, 7) | t <sub>scrl</sub>  | 0   | -        | ns    |

| Time from SCCLK falling to $\overline{CS}$ rising |             | t <sub>sccsh</sub> | 20  | -        | ns    |

| High time between active CS                       |             | t <sub>csht</sub>  | 200 | -        | ns    |

| Time from $\overline{CS}$ rising to SCDOUT high-Z | (Note 7)    | t <sub>cscdo</sub> |     | 20       | ns    |

Notes: 1. The specification f<sub>sck</sub> indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. The relevant application code user's manual should be consulted for the software speed limitations.

- 2. Data must be held for sufficient time to bridge the 50 ns transition time of SCCLK.

- 3. SCDOUT should *not* be sampled during this time period.

- 4. INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for the second-to-last bit of the last byte of data during a read operation as shown.

- 5. If INTREQ goes high as indicated in (Note 4), then INTREQ is guaranteed to remain high until the next rising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treat this condition as a new read transaction. Raise chip select to end the current read transaction and then drop it, followed by the 7-bit address and the R/W bit (set to 1 for a read) to start a new read transaction.

- 6. With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pull up value will affect the rise time.

- 7. This time is by design and not tested.

DS339PP3

Figure 7. SPI Control Port Timing

CS49300 Family DSP

13

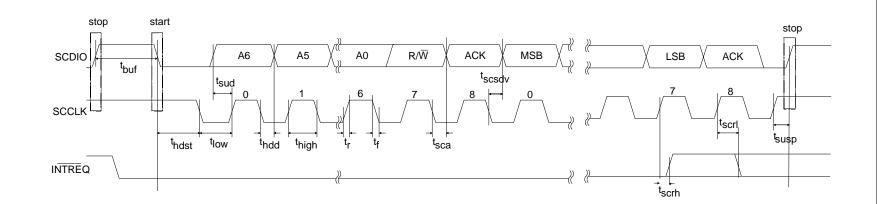

# 1.10. Switching Characteristics — I<sup>2</sup>C<sup>®</sup> Control Port

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                              |                    | Symbol             | Min | Мах | Units |

|--------------------------------------------------------|--------------------|--------------------|-----|-----|-------|

| SCCLK clock frequency                                  | (Note 1)           | f <sub>scl</sub>   |     | 400 | kHz   |

| Bus free time between transmissions                    |                    | t <sub>buf</sub>   | 4.7 |     | μs    |

| Start-condition hold time (prior to first clock pulse) |                    | t <sub>hdst</sub>  | 4.0 |     | μs    |

| Clock low time                                         |                    | t <sub>low</sub>   | 1.2 |     | μs    |

| Clock high time                                        |                    | t <sub>high</sub>  | 1.0 |     | μs    |

| SCDIO setup time to SCCLK rising                       |                    | t <sub>sud</sub>   | 250 |     | ns    |

| SCDIO hold time from SCCLK falling                     | (Note 2)           | t <sub>hdd</sub>   | 0   |     | μs    |

| Rise time of SCCLK                                     | (Note 3), (Note 7) | t <sub>r</sub>     |     | 50  | ns    |

| Fall time of SCCLK                                     | (Note 7)           | t <sub>f</sub>     |     | 300 | ns    |

| Time from SCCLK falling to CS493XX ACK                 |                    | t <sub>sca</sub>   |     | 40  | ns    |

| Time from SCCLK falling to SCDIO valid during read of  | peration           | t <sub>scsdv</sub> |     | 40  | ns    |

| Time from SCCLK rising to INTREQ rising                | (Note 4)           | t <sub>scrh</sub>  |     | 200 | ns    |

| Hold time for INTREQ from SCCLK rising                 | (Note 5)           | t <sub>scrl</sub>  | 0   |     | ns    |

| Rise time for INTREQ                                   | (Note 6)           | t <sub>rr</sub>    |     | **  | ns    |

| Setup time for stop condition                          |                    | t <sub>susp</sub>  | 4.7 |     | μs    |

Notes:. 1. The specification f<sub>scl</sub> indicates the maximum speed of the hardware. The system designer should be aware that the actual maximum speed of the communication port may be limited by the software. The relevant application code user's manual should be consulted for the software speed limitations.

- 2. Data must be held for sufficient time to bridge the 300-ns transition time of SCCLK. This hold time is by design and not tested.

- 3. This rise time is *shorter* than that recommended by the I<sup>2</sup>C specifications. For more information, see Section 6.1, "Serial Communication" on page 33.

- 4. INTREQ goes high only if there is no data to be read from the DSP at the rising edge of SCCLK for the last data bit of the last byte of data during a read operation as shown.

- 5. If INTREQ goes high as indicated in Note 8, then INTREQ is guaranteed to remain high until the next rising edge of SCCLK. If there is more data to be read at this time, INTREQ goes active low again. Treat this condition as a new read transaction. Send a new start condition followed by the 7-bit address and the R/W bit (set to 1 for a read). This time is by design and is not tested.

- 6. With a 4.7k Ohm pull-up resistor this value is typically 215ns. As this pin is open drain adjusting the pull up value will affect the rise time.

- 7. This time is by design and not tested.

DS339PP3

CS49300 Family DSP

CIRRUS LOGIC®

15

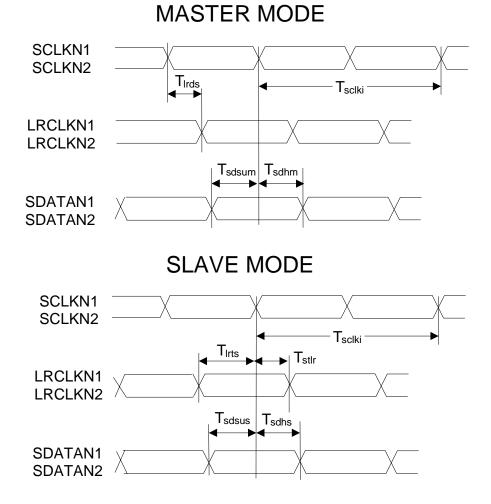

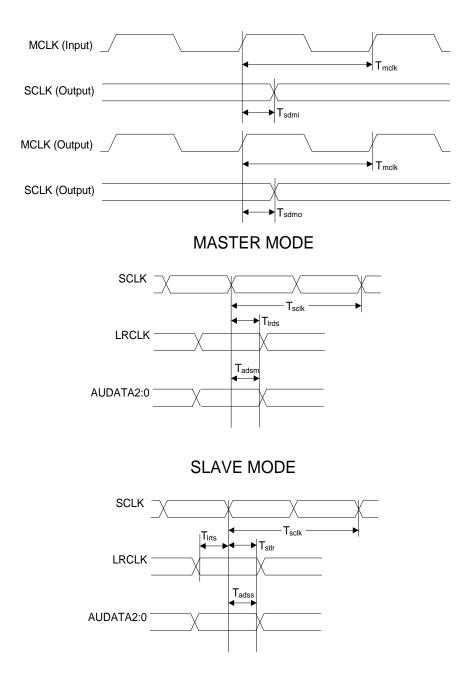

#### 1.11. Switching Characteristics — Digital Audio Input

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                               |             | Symbol             | Min | Max | Unit |

|---------------------------------------------------------|-------------|--------------------|-----|-----|------|

| SCLKN1(2) period for both Master and Slave mode         | (Note 1)    | T <sub>sclki</sub> | 40  | -   | ns   |

| SCLKN1(2) duty cycle for Master and Slave mode          | (Note 1)    |                    | 45  | 55  | %    |

| Master Mode                                             | (Note 1, 2) |                    |     |     |      |

| LRCLKN1(2) delay after SCLKN1(2) transition             | (Note 3)    | T <sub>Irds</sub>  | -   | 10  | ns   |

| SDATAN1(2) setup to SCLKN1(2) transition                | (Note 4)    | T <sub>sdsum</sub> | 10  | -   | ns   |

| SDATAN1(2) hold time after SCLKN1(2) transition         | (Note 4)    | T <sub>sdhm</sub>  | 5   | -   | ns   |

| Slave Mode                                              | (Note 5)    |                    |     |     |      |

| Time from active edge of SCLKN1(2) to LRCLKN1(2) trans  | ition       | T <sub>stlr</sub>  | 10  | -   | ns   |

| Time from LRCLKN1(2) transition to SCLKN1(2) active edg | je          | T <sub>Irts</sub>  | 10  | -   | ns   |

| SDATAN1(2) setup to SCLKN1(2) transition                | (Note 4)    | T <sub>sdsus</sub> | 5   | -   | ns   |

| SDATAN1(2) hold time after SCLKN1(2) transition         | (Note 4)    | T <sub>sdhs</sub>  | 5   | -   | ns   |

Notes: 1. Master mode timing specifications are characterized, not production tested.

- 2. Master mode is defined as the CS493XX driving LRCLKN1(2) and SCLKN1(2). Master or Slave mode can be programmed.

- 3. This timing parameter is defined from the non-active edge of SCLKN1(2). The active edge of SCLKN1(2) is the point at which the data is valid.

- 4. This timing parameter is defined from the active edge of SCLKN1(2). The active edge of SCLKN1(2) is the point at which the data is valid.

- 5. Slave mode is defined as SCLKN1(2) and LRCLKN1(2) being driven by an external source.

Figure 9. Digital Audio Input Data, Master and Slave Clock Timing

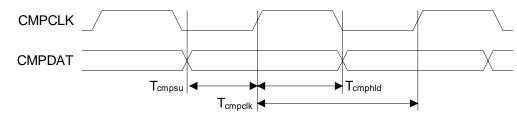

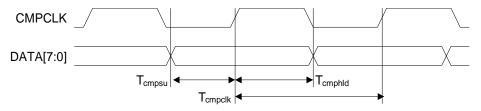

#### 1.12. Switching Characteristics — CMPDAT, CMPCLK

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V  $\pm$ 5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                  | Symbol              | Min | Max | Unit |

|--------------------------------------------|---------------------|-----|-----|------|

| Serial compressed data clock CMPCLK period | T <sub>cmpclk</sub> | -   | 27  | MHz  |

| CMPDAT setup before CMPCLK high            | T <sub>cmpsu</sub>  | 5   | -   | ns   |

| CMPDAT hold after CMPCLK high              | T <sub>cmphld</sub> | 3   | -   | ns   |

Figure 10. Serial Compressed Data Timing

#### **1.13. Switching Characteristics — Parallel Data Input**

$(T_A = 25 \degree C; VA, VD[3:1] = 2.5 V \pm 5\%; Inputs: Logic 0 = DGND, Logic 1 = VD, C_L = 20 \text{ pF})$

| Parameter                          | Symbol              | Min         | Max | Unit |

|------------------------------------|---------------------|-------------|-----|------|

| CMPCLK Period                      | T <sub>cmpclk</sub> | 4*DCLK + 10 |     | ns   |

| DATA[7:0] setup before CMPCLK high | T <sub>cmpsu</sub>  | 10          |     | ns   |

| DATA[7:0] hold after CMPCLK high   | T <sub>cmphld</sub> | 10          |     | ns   |

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLK, in nanoseconds. The DSP clock can be defined as follows:

External CLKIN Mode: DCLK == CLKIN/4 before and during boot DCLK == CLKIN after boot

Internal Clock Mode: DCLK == 10MHz before and during boot, i.e. DCLK == 100ns DCLK == 65 MHz after boot, i.e. DCLK == 15.4ns

It should be noted that DCLK for the internal clock mode is application specific. The application code users guide should be checked to confirm DCLK for the particular application.

Figure 11. Parallel Data Timing (when not in a parallel control mode)

#### 1.14. Switching Characteristics — Digital Audio Output

(T<sub>A</sub> = 25 °C; VA, VD[3:1] = 2.5 V ±5%; Inputs: Logic 0 = DGND, Logic 1 = VD, C<sub>L</sub> = 20 pF)

| Parameter                                    |                  | Symbol            | Min | Мах | Unit |

|----------------------------------------------|------------------|-------------------|-----|-----|------|

| MCLK period                                  | (Note 1)         | T <sub>mclk</sub> | 40  | -   | ns   |

| MCLK duty cycle                              | (Note 1)         |                   | 40  | 60  | %    |

| SCLK period for Master or Slave mode         | (Note 2)         | T <sub>sclk</sub> | 40  | -   | ns   |

| SCLK duty cycle for Master or Slave mode     | (Note 2)         |                   | 45  | 55  | %    |

| Master Mode                                  | (Note 2, 3)      |                   |     |     |      |

| SCLK delay from MCLK rising edge, MCLK as ar | n input          | T <sub>sdmi</sub> |     | 15  | ns   |

| SCLK delay from MCLK rising edge, MCLK as ar | n output         | T <sub>sdmo</sub> | -5  | 10  | ns   |

| LRCLK delay from SCLK transition             | (Note 4)         | T <sub>Irds</sub> |     | 10  | ns   |

| AUDATA2–0 delay from SCLK transition         | (Note 4)         | T <sub>adsm</sub> |     | 10  | ns   |

| Slave Mode                                   | (Note 5)         |                   |     |     |      |

| Time from active edge of SCLKN1(2) to LRCLKN | 11(2) transition | T <sub>stlr</sub> | 10  | -   | ns   |

| Time from LRCLKN1(2) transition to SCLKN1(2) | active edge      | T <sub>Irts</sub> | 10  | -   | ns   |

| AUDATA2–0 delay from SCLK transition         | (Note 4, 6)      | T <sub>adss</sub> |     | 15  | ns   |

Notes: 1. MCLK can be an input or an output. These specifications apply for both cases.

- 2. Master mode timing specifications are characterized, not production tested.

- 3. Master mode is defined as the CS493XX driving both SCLK and LRCLK. When MCLK is an input, it is divided to produce SCLK and LRCLK.

- 4. This timing parameter is defined from the non-active edge of SCLK. The active edge of SCLK is the point at which the data is valid.

- 5. Slave mode is defined as SCLK and LRCLK being driven by an external source.

- 6. This specification is characterized, not production tested.

Figure 12. Digital Audio Output Data, Input and Output Clock Timing

### 2. FAMILY OVERVIEW

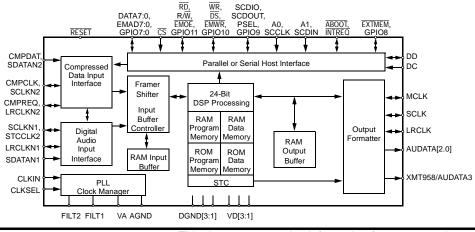

The CS49300 family contains system on a chip solutions for multichannel audio decompression and digital signal processing. The CS49300 family is split into 4 sub-families targeted at the DVD, broadcast and audio/video receiver (AVR), and effects and post processing markets.

This document focuses on the electrical features and characteristics of these parts. Different features are described from a hardware design perspective. It should be understood that not all of the features portrayed in this document are supported by all of the versions of application code available. The application code user's guides should be consulted to confirm which hardware features are supported by the software.

The parts use a combination of internal ROM and RAM. Depending on the application being used, a download of application software may be required each time the part is powered up. This document uses "download" and "code load" interchangeably. These terms should be interpreted as meaning the transfer of application code into the internal memory of the part from either an external microcontroller or through the autoboot procedure.

# 2.1. Multichannel Decoder Family of Parts

*CS49300 - DVD Audio Decoder*. The CS49300 device is targeted at audio decoding in the DVD via ES or PES in a serial or parallel bursty fashion for MLP or for DVD Audio Pack Layer Support. (All the other decoding/processing algorithms listed below require delivery of PCM or IEC61937-packed compressed data via I<sup>2</sup>S or LJ formatted digital audio to the CS49300). Specifically the CS49300 will support all of the following decoding/processing standards:

- Meridian Lossless Packing<sup>TM</sup> (MLP<sup>TM</sup>)\* (for ES and PES data delivery only)

- DVD Audio Pack Layer Support\* (for ES and PES data delivery only)

- Dolby Digital<sup>TM</sup> (AC-3<sup>TM</sup>) with Dolby Pro Logic<sup>TM</sup>

- Dolby Digital<sup>TM</sup> with Dolby Pro Logic<sup>TM</sup> plus Crystal Extra Surround<sup>TM</sup>

- Dolby  $\text{Digital}^{\text{TM}}$  with Dolby Pro Logic  $\text{II}^{\text{TM}}$

- Dolby Digital<sup>™</sup> with Dolby Pro Logic II<sup>™</sup> plus Crystal Extra Surround<sup>™</sup>

- Virtual Dolby Digital<sup>TM</sup>

- MPEG-2, Advanced Audio Coding Algorithm (AAC)

- MPEG Multichannel

- MPEG Multichannel with Dolby Pro Logic  $II^{TM}$

- MPEG Multichannel plus Crystal Extra Surround  $^{TM}$

- MPEG-1, Layer 3 (MP3)

- DTS Digital Surround<sup>TM</sup>

- DTS Digital Surround<sup>™</sup> with Dolby Pro Logic II<sup>™</sup>

- DTS Digital Surround<sup>™</sup> plus Crystal Extra Surround<sup>™</sup>

- DTS-ES Extended Surround<sup>™</sup> (DTS-ES Discrete 6.1 & Matrix 6.1)

- DTS Neo: $6^{TM}$

- Logic 5<sup>®</sup> (5.1 Channel, Max Fs=48kHz and Logic 7<sup>®</sup> (7.1 Channel, Max Fs=96kHz)

- VMAx VirtualTheater<sup>®</sup> (Virtual Dolby Digital)

- SRS TruSurround<sup>™</sup> (Virtual Dolby Digital and DTS Virtual 5.1<sup>™</sup> Versions)

- SRS Circle Surround  $^{TM}$  I/II

- HDCD<sup>®</sup>

- Crystal P.D.F. (Dolby Pro Logic 2Fs Decoder and PCM Upsampler)

- Crystal PL2\_2FS (Dolby Pro Logic II 2Fs Decoder and PCM Upsampler)

Please refer to the CS4932x/CS49330 Part Matrix vs. Code Matrix (PDF) document available from the CS49300 Web Site Page for the latest listing of audio decoding/processing algorithms. The part

will also support PES layer decode for audio/video synchronization and DVD Audio Pack layer support. The CS49300 will support all of the above decoding and PCM processing standards.

*CS4931X - Broadcast Sub-family*. The CS4931X sub-family is targeted at audio decoding in the broadcast markets in systems such as digital TV, HDTV, set-top boxes and digital audio broadcast units (digital radios). Specifically the CS4931X sub-family will support the following decode standards:

- Dolby Digital<sup>TM</sup> (AC-3<sup>TM</sup>) with Dolby Pro

- MPEG-2, Advanced Audio Coding Algorithm (AAC)

- MPEG-1, Layers 1, 2 Stereo

- MPEG-1, Layers 3 (MP3) Stereo

- MPEG-2, Layer 2 Stereo

- MPEG-2, Layer 3 (MP3) Stereo

The part will also support PES layer decode for audio/video synchronization. The CS49310 will support all of the above decode standards while other parts in the CS4931X sub-family will decode subsets of the above audio decoding standards.

*CS4932X* - *Audio/Video Receiver (AVR) Subfamily*. The CS4932X sub-family is targeted at audio decoding in the audio/video receiver markets. Typical applications will include amplifiers with integrated decoding capability, outboard decoder pre-amplifiers, car radios and any system where the compressed audio is received in an IEC61937 format. Specifically the CS4932X sub-family will support the following decode standards:

- Dolby Digital<sup>TM</sup> (AC-3<sup>TM</sup>) with Dolby Pro Logic<sup>TM</sup>

- Dolby Digital<sup>™</sup> with Dolby Pro Logic<sup>™</sup> plus Crystal Extra Surround<sup>™</sup>

- Dolby  $\text{Digital}^{\text{TM}}$  with Dolby Pro Logic  $\text{II}^{\text{TM}}$

- Dolby Digital<sup>TM</sup> with Dolby Pro Logic II<sup>TM</sup> plus Crystal Extra Surround<sup>TM</sup>

- Virtual Dolby Digital<sup>™</sup>

- MPEG-2, Advanced Audio Coding Algorithm (AAC)

- MPEG Multichannel

- MPEG Multichannel with Dolby Pro Logic  $II^{TM}$

- MPEG Multichannel plus Crystal Extra Surround  $^{TM}$

- MPEG-1, Layer 3 (MP3)

- DTS Digital Surround<sup>TM</sup>

- DTS Digital Surround<sup>TM</sup> with Dolby Pro Logic II<sup>TM</sup>

- DTS Digital Surround<sup>™</sup> plus Crystal Extra Surround<sup>™</sup>

- DTS-ES Extended Surround<sup>™</sup> (DTS-ES Discrete 6.1 & Matrix 6.1)

- DTS Neo: $6^{TM}$

- Logic 5<sup>®</sup> (5.1 Channel, Max Fs=48kHz and Logic 7<sup>®</sup> (7.1 Channel, Max Fs=96kHz)

- VMAx VirtualTheater<sup>®</sup> (Virtual Dolby Digital)

- SRS TruSurround<sup>™</sup> (Virtual Dolby Digital and DTS Virtual 5.1<sup>™</sup> Versions)

- SRS Circle Surround  $^{\text{TM}}$  I/II

- HDCD<sup>®</sup>

- Crystal P.D.F. (Dolby Pro Logic 2Fs Decoder and PCM Upsampler)

- Crystal PL2\_2FS (Dolby Pro Logic II 2Fs Decoder and PCM Upsampler)

The CS49326 will support all of the above decode standards while other parts in the CS4932X sub-family will decode subsets of the above audio decoding standards.

Except for the CS49329 which offers AAC support this subfamily will offer integrated ROM support for the AC-3 code, DTS code, Crystal Original Surround code and DTS tables. The CS49329 will

require an external download for all applications but will still support the DTS tables on chip.

CS49330 - General Purpose, Car Audio Processor, PCM Effects & Multichannel Post-Processing Device. The CS49330 sub-family is targeted at any system that may require post processing or multichannel effects processing, a general purpose MPEG Stereo, MPEG Multichannel, MP3, decoder or PCM effects processor or mixer, or for car audio applications. Typical applications will include multichannel amplifiers, outboard pre-amplifiers, HDTVs and car radios. Specifically the CS49330 sub-family will support the following:

- Crystal Digital Post-Processor, Home THX Cinema<sup>®</sup> and THX Surround EX<sup>™</sup> 5.1 and 7.1 Channel Post-Processors

- Any general purpose application which only requires MPEG Multichannel; MPEG-1, Layer 3; MPEG-2, Layer 3\*, or C.O.S. PCM Effects Processor. (MPEG-1, Layer 3 and MPEG-2, Layer 3 are only available for applications where serial or parallel bursty elementary stream data is available. MPEG-1, Layer 3

audio decoding is only available for IEC61937packed MP3 data.)

- Multichannel Effects Processing

- General purpose broadcast application that only requires MPEG-1 Stereo (Layers 1, 2, or 3) and MPEG-2 Stereo (Layers 2 or 3)

- Car Audio Post-Processor

This sub-family will continue to grow as more post processing algorithms are supported.

This data sheet covers the CS49300, CS4931X, CS4932X and CS49330 sub-families and devices. These parts are identical from an external electrical perspective. Internally, each part has been tailored for supporting different decoding standards. For this document individual part numbers have been replaced by CS493XX if the description applies to the entire CS49300 Family DSP. If a description only applies to a particular sub-family, CS49300, CS4931X, CS4932X or CS49330 will be used. When CS49300, CS4931X, CS4931X, CS4932X or CS49330 is used, this should be interpreted as applying to all parts within the particular sub-family or a particular device.

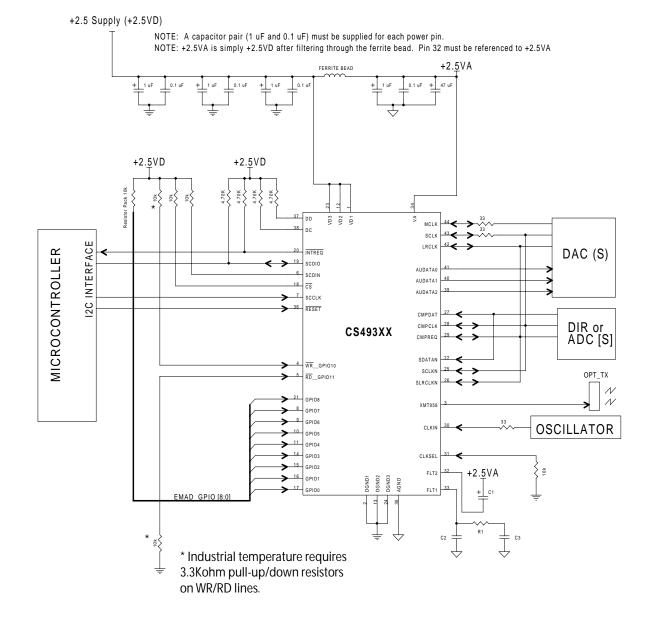

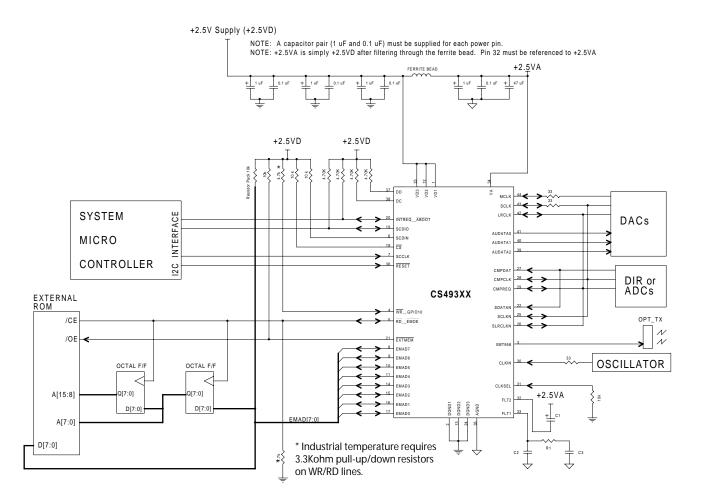

#### 3. TYPICAL CONNECTION DIAGRAMS

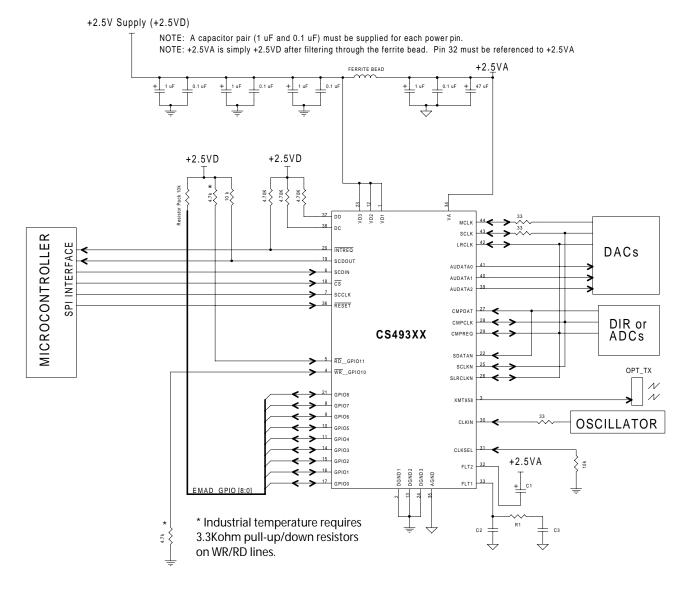

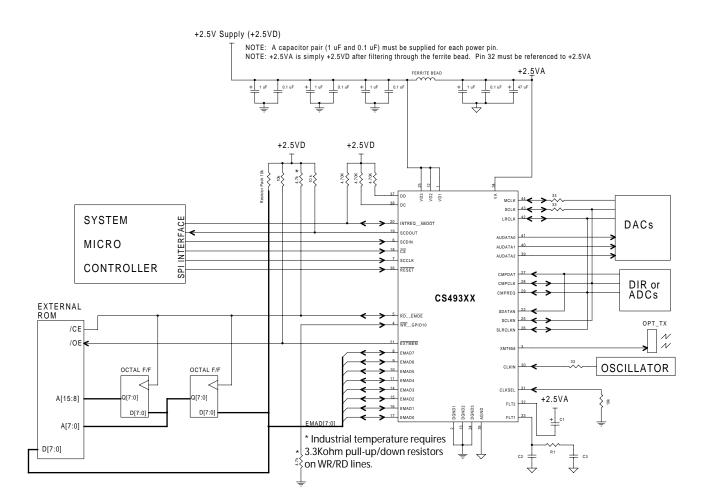

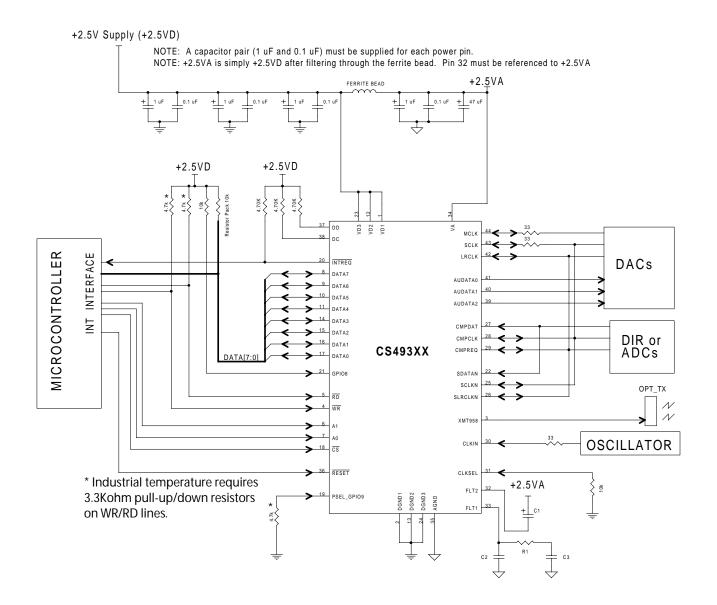

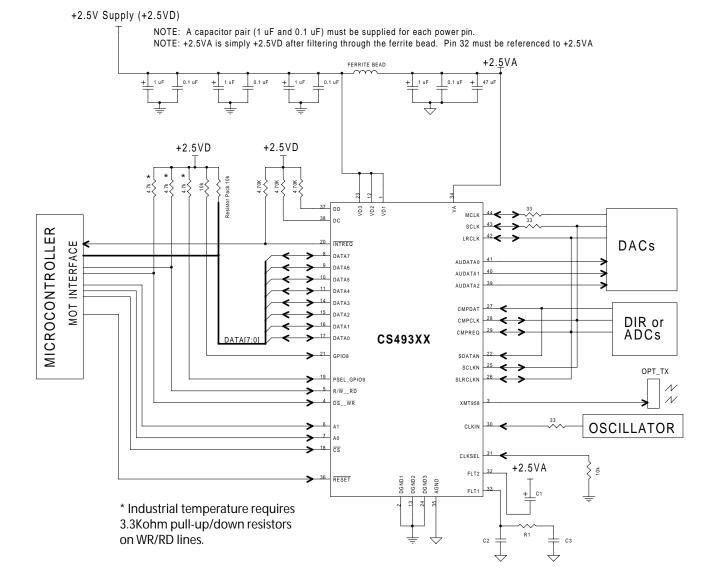

Six typical connection diagrams have been presented to illustrate using the part with the different communication modes available. They are as follows:

Figure 13, "I<sup>2</sup>C<sup>®</sup> Control" on page 26

Figure 14, "I<sup>2</sup>C<sup>®</sup> Control with External Memory" on page 27

Figure 15, "SPI Control" on page 28

Figure 16, "SPI Control with External Memory" on page 29

Figure 17, "Intel<sup>®</sup> Parallel Control Mode" on page 30

Figure 18, "Motorola<sup>®</sup> Parallel Control Mode" on page 31

The following should be noted when viewing the typical connection diagrams:

The pins are grouped functionally in each of the typical connection diagrams. Please be aware that the CS493XX symbol may appear differently in each diagram.

The external memory interface is only supported when a serial communication mode has been chosen.

The typical connection diagrams demonstrate the PLL being used (CLKSEL is pulled low). To use CLKIN as the DSP clock, CLKSEL should be pulled high. The system designer must be aware that certain software features may not be available if external CLKIN is used as the DSP must run slower when external CLKIN is used. The system designer should also be aware of additional duty cycle requirements when using external CLKIN as a DSP clock. It is highly suggested that the system designer use the PLL and pull CLKSEL low.

#### 3.1. Multiplexed Pins

The CS493XX family of digital signal processors (DSPs) incorporate a large amount of flexibility into a 44 pin package. Because of the high degree

of integration, many of these pins are internally multiplexed to serve multiple purposes. Some pins are designed to operate in one mode at power up, and serve a different purpose when the DSP is running. Other pins have functionality which can be controlled by the application running on the DSP. In order to better explain the behavior of the part, the pins which are multiplexed have been given multiple names. Each name is specific to the pin's operation in a particular mode.

An example of this would be the use of pin 20 in one of the serial control modes. During the boot period of the CS493XX, pin 20 is called ABOOT. ABOOT is sampled on the rising edge of RESET. If ABOOT is high the host must download code to the DSP. If ABOOT is low when sampled, the CS493XX goes into autoboot mode and loads itself with code by generating addresses and reading data on EMAD[7:0]. When the part has been loaded with code and is running an application, however, pin 20 is called INTREQ. INTREQ is an open drain output used to inform the host that the DSP has an outgoing message which should be read.

In this document, pins will be referred to by their functionality. Section 12, "Pin Descriptions" on page 77 describes each pin of the CS493XX and lists all of its names. Please refer to this section when exact pin numbers are in question.

The part has 12 general purpose input and output (GPIO[11:0]) pins that all have multiple functionality. While in one of the parallel communication modes (Section 6.2, "Parallel Host Communication" on page 41), these pins are used to implement the parallel host communication interface. While in one of the serial host modes these pins are used to implement an external memory interface. Alternatively while in one of the serial host modes for another general purpose if the application code has been programmed to support the special purpose. In this document the pins are referenced by the

name corresponding to their particular use. Sometimes GPIO[11:0], or some subset thereof, is used when referring to the pins in a general sense.

#### **3.2.** Termination Requirements

The CS493XX incorporates open drain pins which must be pulled high for proper operation.  $\overline{\text{INTREQ}}$ (pin 20) is always an open drain pin which requires a pull-up for proper operation. When in the I<sup>2</sup>C serial communication mode, the SCDIO signal (pin 19) is open drain and thus requires a pull-up for proper operation.

Due to the internal, multiplexed design of the pins, certain signals may or may not require termination depending on the mode being used. If a parallel host communication mode is not being used, GPIO[11:0] must be terminated or driven as these pins will come up as high impedance inputs and will be prone to oscillation if they are left floating. The specific termination requirements may vary since the state of some of the GPIO pins will determine the communication mode at the rising edge of reset (please see Section 6, "Control" on page 32 for more information). For the explicit termination requirements of each communication mode please see the typical connection diagrams.

Generally a 4.7k Ohm resistor is recommended for open drain pins. The communication mode setting pins (please see Section 6, "Control" on page 32 for more information) should also be terminated with a 4.7k resistor. A 10k Ohm resistor is sufficient for the GPIO pins and unused inputs.

# 3.3. Phase Locked Loop Filter

The internal phase locked loop (PLL) of the CS493XX requires an external filter for successful operation. The topology of this filter is shown in the typical connection diagrams. The component values are shown below. Care should be taken when laying out the filter circuitry to minimize trace lengths and to avoid any close routing of high frequency signals. Any noise coupled on to the

filter circuit will be directly coupled into the PLL, which could affect performance.

| Reference Designator | Value    |

|----------------------|----------|

| C1                   | 2.2uF    |

| C2                   | 220pF    |

| C3                   | 10nF     |

| R1                   | 200k Ohm |

Table 1. PLL Filter Component Values

#### 4. POWER

The CS493XX requires a 2.5V digital power supply for the digital logic within the DSP and a 2.5V analog power supply for the internal PLL. There are three digital power pins, VD1, VD2 and VD3, along with three digital grounds, DGND1, DGND2 and DGND3. There is one analog power pin, VA and one analog ground, AGND. The DSP will perform at its best when noise has been eliminated from the power supply. The recommendations given below for decoupling and power conditioning of the CS493XX will help to ensure reliable performance.

#### 4.1. Decoupling

It is good practice to decouple noise from the power supply by placing capacitors directly between the power and ground of the CS493XX. pair of power pins (VD1/DGND, Each VD2/DGND, VD3/DGND, VA/AGND) should have its own decoupling capacitors. The recommended procedure is to place both a 0.1uF and a 1uF capacitor as close as physically possible to each power pin. The 0.1uF capacitor should be closest to the part (typically 5mm or closer).

#### 4.2. Analog Power Conditioning

In order to obtain the best performance from the CS493XX's internal PLL, the analog power supply (VA) must be as clean as possible. A ferrite bead should be used to filter the 2.5V power supply for the analog portion of the CS493XX. This power

Figure 13. I<sup>2</sup>C<sup>®</sup> Control

Figure 14. I<sup>2</sup>C<sup>®</sup> Control with External Memory

Figure 15. SPI Control

Figure 16. SPI Control with External Memory

Figure 17. Intel<sup>®</sup> Parallel Control Mode

Figure 18. Motorola<sup>®</sup> Parallel Control Mode

scheme is shown in the typical connection diagrams.

#### 4.3. Ground

For two layer applications, care should be taken to have sufficient ground between the DSP and parts in which it will be interfacing (DACs, ADCs, DIR, microcontrollers, external memory etc). If there is not sufficient ground, a potential will be seen between the ground reference of the DSP and the interface parts and the noise margin will be significantly reduced potentially causing communication or data integrity problems.

#### 4.4. Pads

The CS493XX incorporate 3.3V tolerant pads. This means that while the CS493XX power supplies require 2.5 volts, 3.3 volt signals can be applied to the inputs without damaging the part.

# 5. CLOCKING

The CS493XX clock manager incorporates a programmable phase locked loop (PLL) clock synthesizer. The PLL takes an input reference clock and produces all the internal clocks required to run the internal DSP and to provide master mode timing to the audio input/output peripherals. The clock manager also includes a 33-bit system time clock (STC) to support audio and video synchronization.

The PLL can be internally bypassed by connecting the CLKSEL pin to VD. This connection multiplexes the CLKIN pin directly to the DSP clock. Care should be taken to note the minimum CLKIN requirements when bypassing the PLL.

The PLL reference clock has three possible sources that are routed through a multiplexer controlled by the DSP: SCLKN2, SCLKN1, and CLKIN. Typically, in audio/video environments like set-top boxes, the CLKIN pin is connected to 27 MHz. In other scenarios such as an A/V receiver design, the PLL can be clocked through the CLKIN pin with even multiples of the desired sampling rate or with an already available clock source. Typically a 12.288 MHz CLKIN is used in this scenario so that the same oscillator can be used for the DSP and ADC.

The clock manager is controlled by the DSP application software. The software user's guide for the application code being used should be referenced for what CLKIN input frequency is supported.

# 6. CONTROL

Control of the CS493XX can be accomplished through one of four methods. The CS493XX supports  $I^2C^{(B)}$  and SPI serial communication. In addition the CS493XX supports both a Motorola and Intel byte wide parallel host control mode. Only one of the four communication modes can be selected for control. The states of the RD, WR, and PSEL pins are sampled at the rising edge of RESET to determine the interface type as shown in Table 2.

| RD<br>(Pin 5) | WR<br>(Pin 4) | PSEL<br>(Pin 19) | Host Interface Mode                  |

|---------------|---------------|------------------|--------------------------------------|

| 1             | 1             | 1                | 8-bit Motorola <sup>®</sup>          |

| 1             | 1             | 0                | 8-bit Intel <sup>®</sup>             |

| 0             | 1             | Х                | Serial I <sup>2</sup> C <sup>®</sup> |

| 1             | 0             | Х                | Serial SPI                           |

Table 2. Host Modes

Whichever host communication mode is used, host control of the CS493XX is handled through the application software running on the DSP. Configuration and control of the CS493XX decoder and its peripherals are indirectly executed through a messaging protocol supported by the downloaded application code. In other words communication successful can only be accomplished by following the low level hardware communication format and high level messaging protocol. The specifications of the messaging protocol can be found in any of the software user's guides.

Only the subsection describing the communication mode being used needs to be read by the system designer.

#### 6.1. Serial Communication

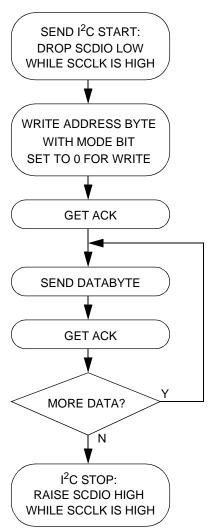

The CS493XX has a serial control port that supports both SPI and  $I^2C^{(R)}$  forms of communication.

The following sections will explain each communication mode in more detail. Flow diagrams will illustrate read and write cycles.

Timing diagrams will be shown to demonstrate relative edge positions of signal transitions for read and write operations.

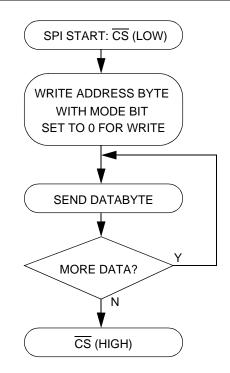

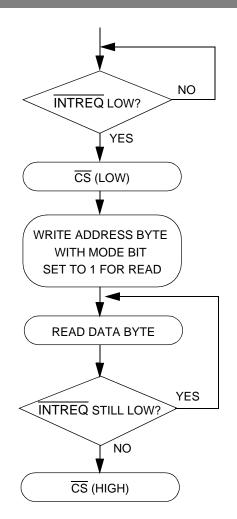

#### 6.1.1. SPI Communication

SPI communication with the CS493XX is accomplished with 5 communication lines: chip select, serial control clock, serial data in, serial data out and an interrupt request line to signal that the DSP has data to transmit to the host. Table 3 shows the mnemonic, pin name, and pin number of each of these signals on the CS493XX.

| Mnemonic          | Pin Name | Pin Number |