# **CL-PS7500FE Development Kit**

## Hardware User's Guide

**Embedded Processors Division**

Copyright © 1999 - Cirrus Logic Inc. All rights reserved.

This document describes the CL-PS7500FE development board provided by Cirrus Logic Inc. No warranty is given for the suitability of this design for any purpose other than demonstrating functional operation of the CL-PS7500FE.

The information contained in this document is subject to change without notice.

Version 1.0 March 1999

# **Table of Contents**

| 1 |       | oduction                                     |     |

|---|-------|----------------------------------------------|-----|

| 2 |       | ns and Definitions                           |     |

| 3 |       | elopment Board                               |     |

|   | 3.1   | Main Feature Set                             | . 6 |

|   | 3.2   | Population Options                           | . 7 |

|   | 3.3   | Board Set-up                                 | . 7 |

|   | 3.4   | Power                                        | . 8 |

|   | 3.5   | Jumpers                                      | . 8 |

| 4 |       | lware Design Details                         |     |

|   |       | DRAM                                         |     |

|   |       | FLASH                                        |     |

|   |       | Boot ROM                                     |     |

|   |       | Clocks                                       |     |

|   |       | Power Management Modes.                      |     |

|   |       | Logic Analyzer Headers                       |     |

|   |       | Keyboard and Mouse                           |     |

|   |       | Sound                                        |     |

|   | 4.8.1 |                                              |     |

|   | 4.8.2 |                                              |     |

|   |       |                                              |     |

|   |       | Event Switches                               |     |

|   |       | ISA Interface                                |     |

|   | 4.10  | J 11 6                                       |     |

|   |       | .2 Exception Support                         |     |

|   |       | SMSC 37C665 PC Combo Chip                    |     |

|   | 4.11  |                                              |     |

|   | 4.11  | , , , , , , , , , , , , , , , , , , , ,      |     |

|   | 4.11  | T F                                          |     |

|   | 4.11  | , , , , , , , , , , , , , , , , , , , ,      |     |

|   |       | CS8900A Ethernet (10BASE-T)                  |     |

|   | 4.12  | TI                                           |     |

|   | 4.12  | J II                                         |     |

|   | 4.12  | - I                                          |     |

|   | 4.12  | .4 Local EEPROM                              | 27  |

|   | 4.13  | Video Subsystem                              | 29  |

|   | 4.13  | .1 Video System Clock Options                | 29  |

|   | 4.13  | .2 VGA                                       | 30  |

|   | 4.    | 13.2.1 Setting the Control Registers         | 30  |

|   | 4.    | 13.2.2 Configuring the Palette               | 31  |

|   | 4.    | 13.2.3 Horizontal and Vertical Configuration | 31  |

|   | 4.    | 13.2.4 Video DMA Configuration               | 32  |

|   | 4.    | 13.2.5 VIDMUX Register                       |     |

|   | 4.13  |                                              |     |

|   |       | OS Porting Aid                               |     |

|   |       | Power                                        |     |

|   | 4.15  |                                              |     |

|   | 4.15  |                                              |     |

|   | 4.15  |                                              |     |

|   | 4.15  |                                              |     |

|   | 4.15  | $\boldsymbol{\varepsilon}$                   |     |

| 5 |       | sical Specification                          |     |

| J | •     | PCB Form Factor                              |     |

|   |       | PCB Construction Materials.                  |     |

|   |       | Connector Details                            |     |

| 6 |       |                                              |     |

| 6 | Opei  | rating and Storage Environments              | 20  |

| 6.1 Temperature                                                         |    |

|-------------------------------------------------------------------------|----|

| 6.2 Humidity                                                            |    |

| 6.3 Air Flow                                                            |    |

| 6.4 Regulatory Compliance (FCC Part 15 Class B, and Part 68)            |    |

| 7 Sources of Additional Information                                     | 37 |

|                                                                         |    |

| X                                                                       |    |

| List of Tables                                                          |    |

| Table 1: Chip Select Usage                                              |    |

| Table 2: Interrupt request usage on the CL-PS7500FE                     |    |

| Table 3: Recommended FLASH SIMMs                                        |    |

| Table 4: Boot ROM Enable/Disable Jumper - JP12                          |    |

| Table 5: Boot ROM Size Selection Jumper – JP11                          |    |

| Table 6: Clock Prescalar Register                                       |    |

| Table 7: Clock Configuration Register                                   |    |

| Table 8: JP1 (1x2) Definition (Control of SnA pin)                      |    |

| Table 9: CPU Clocking Options (if the CH9294G is used for CPU clocking) |    |

| Table 10: JP3 Logic Analyzer Header Definition                          |    |

| Table 11: JP4 Logic Analyzer Header Definition                          |    |

| Table 12: JP5 Logic Analyzer Header Definition                          |    |

| Table 13: JP6 Logic Analyzer Header Definition                          |    |

| Table 14: JP7 Logic Analyzer Header Definition                          |    |

| Table 15: JP8 Logic Analyzer Header Definition                          |    |

| Table 16: JP9 Logic Analyzer Header Definition                          |    |

| Table 17: JP10 Logic Analyzer Header Definition                         |    |

| Table 18: Keyboard and Mouse Registers                                  |    |

| Table 19: PS2 Control Register Write Bit Mapping                        |    |

| Table 20: PS2 Control Register Write Bit Definition                     |    |

| Table 21: PS2 Control Register Read Bit Mapping                         |    |

| Table 22: PS2 Control Register Write Bit Definition                     |    |

| Table 23: Keyboard Interrupt Control                                    |    |

| Table 24: Mouse Interrupt Control                                       |    |

| Table 25: Sound System External Interface                               |    |

| Table 26: Sound Macrocell Configuration Parameters                      |    |

| Table 27: Sound System DMA and Interrupt Registers                      |    |

| Table 28: SDCR – Sound DMA Control Register Configuration (0x0320:01    |    |

| Table 29: SDCR Register Write Bit Definition                            |    |

| Table 30: SDST – Sound DMA Status Register Configuration (0x0320:0190   | ,  |

| Table 31: SDCR Register Write Bit Definition                            |    |

| Table 32: Event Switch Functions                                        |    |

| Table 33: ISA Map to CS-PS7500FE Memory Space                           |    |

| Table 34: ISA Exception Register Bit Definition                         |    |

| Table 35: DMA Acknowledge Memory Space                                  |    |

| Table 36: PC Combo Chip Set-Up Registers                                | 22 |

| Table 37: PC Combo Chip Configuration Register Default Values           |    |

| Table 38: COM1 Address Registers                                        |    |

| Table 39: COM2 Address Registers                                        |    |

| Table 40: JP13 (1x2) Definition (Control of Serial Port #2)             |    |

| Table 41: LPT Register Definitions                                      |    |

| Table 42: CS8900A I/O Mapped Registers                                  |    |

| Table 43: EEPROM Data for Default Ethernet Operation                    |    |

| Table 44: VCLKI Available Frequencies (via JP2)                         |    |

| Table 45: J19 LCD Adapter Module Header Pin-Out                         |    |

| Table 46: –5V Power Source Selection                                    |    |

# **List of Figures**

| Figure 1: Null modem connection                        | ծ |

|--------------------------------------------------------|---|

| Figure 2: Development Board Functional Block Diagram   | ç |

| Figure 3: Physical Memory Map of the CL-PS7500FE       |   |

| Figure 4: JP2 Jumper Pin Numbering                     |   |

| Figure 5: CS8900A Serial EEPROM Configuration Sequence |   |

| Figure 6: Video Data Word Format                       |   |

|                                                        |   |

#### 1 Introduction

**ARM®**

The CL-PS7500FE development board is targeted at system designers who are developing CL-PS7500FE based hardware platforms. This document defines the baseline board-level hardware elements that comprise the Cirrus Logic CL-PS7500FE development board. This document references other documents for more specific details of processors and other devices (ICs) used on the design. Scope is restricted to covering the printed circuit board, connections between components on that board, and between the board and other components intended to connect to the development board.

#### 2 Terms and Definitions

|   |      | core in the CL-PS/500FE.                                                                                                                                       |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | baud | The number of bit transitions per second on a serial line. This is different from bits per                                                                     |

|   |      | second since there are control bits that surround the data bits in a serial transmission stream. It is there always the case that bps < baud on a serial line. |

| • | bps  | bits per second.                                                                                                                                               |

| • | bpp  | bits per pixel.                                                                                                                                                |

Advanced RISC Machines Limited. The company that developed the ARM710 processor

COM1 Serial port #1 on the development board.

COM2 Serial port #2 on the development board.

DAC Digital to Analog Converter.

DAC Digital to Analog Converter.DMA Direct Memory Access.

• EDO Extended Data Output. A more efficient means of DRAM data access than FPM.

• FIFO First In First Out. A memory block where data is read out from a single location in the

exact sequence in which it was written.

• FLASH A type of non-volatile memory.

• FPM Fast Page Mode. Method of DRAM data access.

IrDA Infrared Data Association. This body sets the standard for infrared communication.

• ISA Industry Standard Architecture. This is an older bus common to the IBM® PC and its

compatibles.

• LCD Liquid Crystal Display.

• LPT Parallel port (much like in a PC).

LSB Least Significant Bit.

Mbps Million of bits per second.

MSB Most Significant Bit.

NTSC Television video data broadcast format common to North America. Actually stands for

National Television System Committee.

PAL Television video data broadcast format common to Europe. Actually stands for Phase

Alternation by Line.

SIMM Single In-Line Memory Module. SIMMs are available with either DRAM or FLASH on

them; both used on this design.

Qword Quad Word. Four 32-bit words of data.

• Raster A line of pixels on a display.

UART Universal Asynchronous Receiver Transmitter.

### 3 Development Board

The development board is designed as a prototype with limited debug capabilities, such as test headers for logic analyzer interfacing, option memory and ISA type bus. It is not intended to be a production design.

#### 3.1 Main Feature Set

The development board has the following features:

- Processor

- CL-PS7500FE running at 56MHz

- Memory

- Two 72 PIN SIMM sockets for Fast Page Mode or EDO DRAM, capable of supporting up to 64MBytes per socket.

- User selectable boot ROM

- FLASH SIMM up to 16MBytes in size, configured as 32-bit words (not included in kit)

- Peripherals

- Keyboard interface PS/2

- Mouse interface PS/2

- Two serial ports (16C550A-compatible)

- IrDA compliant serial port (serial port back-end) (shared with COM2)

- Parallel port

- 10BaseT Ethernet interface (CS8900A)

- SVGA port

- LCD module site for supporting custom LCDs

- Two ISA type slot connectors

- Stereo headset port (CS4333)

- User controllable 8-LED bar for OS porting/debugging

### 3.2 Population Options

DRAM

The board has two 72 pin DRAM SIMM sockets supporting from 4MBytes to 128MBytes of memory. Typically most applications will require between 8MBytes to 16MBytes of DRAM. Both Fast Page Mode (FPM) and Extended Data Output (EDO) DRAM are supported. Note: software must be aware of the type of DRAM used.

**FLASH**

The board has a single FLASH SIMM socket on it. This is a standard 80-pin socket and can support up to 16Mbyes of FLASH. The type of FLASH used is critical to application development as FLASH devices do not have common erase/write state machines. The FLASH SIMM option has been selected to permit developers to install modules populated with their own choice of FLASH. A seven bit register is available, connected to the SIMM's information bits. This register is intended to permit interrogation of the SIMM to determine its size. Further information on this standard can be obtained from Global Engineering, by referring to JEDEC standard No. 21-C.

Note: Although JEDEC standard No. 21-C states that SIMMs may be sized from 128KBytes to 32MBytes, this design does not support SIMMs larger than 16MBytes. Note also that EPROM emulators are available that are able to connect 80-pin SIMM sockets. This can be used in place of a SIMM during code development.

ROM

The development board comes with an EPROM that contains the Angel<sup>TM</sup> debug monitor. The boot ROM is enabled via a jumper and when selected, moves FLASH from an initial location of 0x0000:0000 in the CL-PS7500FE's memory to 0x0100:0000, while switching the boot ROM into location 0x0000:0000. When the boot ROM is not selected, it will not be addressable by the CPU.

#### 3.3 Board Set-up

A Null modem cable is supplied to allow communication between the development board and the host PC. Communication is set-up by connecting COM1 of the development board to any available COM port on the host PC.

Note: Null modem cables differ substantially from a straight-through cable. See Figure 1 below:

Version 1.0 7 March 1999

Figure 1: Null modem connection Female Female DB9 DB9 GROUND (5)₹ RI RI(9)DTR DTR (4) CTS CTS TD TD (3) RTS RD RD**(2)**◀ DSR DSR DCD

#### 3.4 Power

A 12V 1500mA AC adapter is provided with the development board. The AC adapter is plugged into J23.

Alternatively, a standard PC/AT power supply can be connected to the development board for supplying power. This may be a more attractive alternative during development if ISA plug-in boards with high power consumption are installed.

#### 3.5 Jumpers

There are five jumpers on the development board. Their functions are summarized below (JP3-JP10 are logic analyzer headers):

- JP1: SnA status select. This line is a processor clock control line used to set the relationship between MCLK and FCLK for the CL-PS7500FE processor. If a jumper is installed on this pin, the memory system clock and the CPU clock run at different rates. If low, the two clocks are driven by the clock signal entering on the MCLK pin. For further details on this jumper, refer to Section 4.4.

- JP2: Video and CPU system clock setting. This is a 2x7 jumper that is used to configure the clock that the video system runs from. Please refer to Sections 4.4 and 4.13 of this document for details on this jumper.

- JP11: Boot ROM size select. This is a 1x3 jumper. When a shunt is put on pins 1-2, 4 MBytes of EPROM is assumed. When a shunt is put on 2-3, 1 MByte of boot ROM is assumed. For further details on this jumper, refer to Section 4.3.

- JP12: Boot mode select. If a shunt is installed on this 1x2 jumper, the system will boot from the Boot ROM. Otherwise, the system will boot from the FLASH SIMM. For further details on this jumper, refer to Section 4.3.

- JP15: -5V power source select. This jumper is used to configure a supply or an external supply of -5V. For further details, refer to Section 4.15.4.

## 4 Hardware Design Details

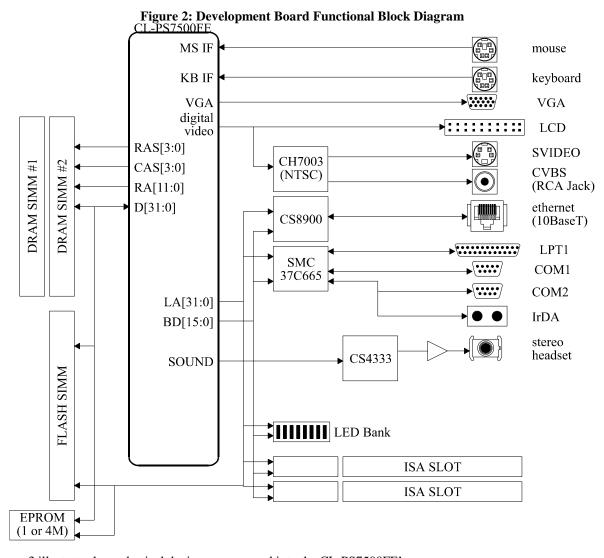

Figure 2 shows a block diagram of the development board. Only a limited number of buses and physical connections are shown as a full illustration here would be prohibitively complex.

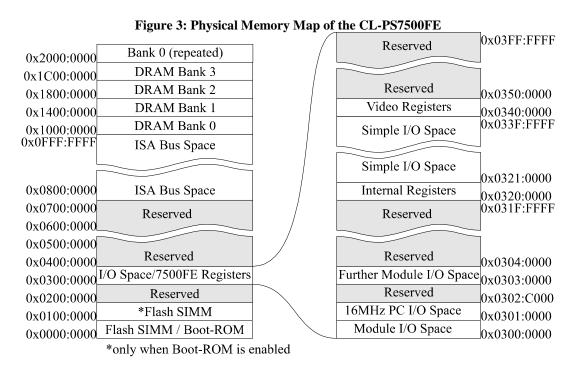

Figure 3 illustrates how physical devices are mapped into the CL-PS7500FE's memory space.

Version 1.0 9 March 1999

Table 1 lists the peripheral chip selects and interrupt request lines to the CL-PS7500FE used by each external device.

Table 1: Chip Select Usage

| Tuble 1. Omp beleet ebuge |                                                                                                   |  |  |  |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Chip Select               | Address Range                                                                                     |  |  |  |  |  |  |

| nEACS                     | 0x0Enn:nn2n0x0Fnn:nn3n                                                                            |  |  |  |  |  |  |

| nEACS                     | 0x0E00:00000x0FFF:FFFF                                                                            |  |  |  |  |  |  |

| nEACS                     | 0x0C00:00000x0DFF:FFFF                                                                            |  |  |  |  |  |  |

| nEACS                     | 0x0800:00000x0BFF:FFFF                                                                            |  |  |  |  |  |  |

| nSIOCS2                   | 0x0334:0C000x0334:8FFF                                                                            |  |  |  |  |  |  |

| nSIOCS2                   | 0x032C:0C000x032C:0CFF                                                                            |  |  |  |  |  |  |

| nSIOCS2                   | 0x0324:0C000x0324:0CFF                                                                            |  |  |  |  |  |  |

| nPCCS1                    | 0x0302:BA000x0302:BAFF                                                                            |  |  |  |  |  |  |

| nPCCS2                    | 0x0302:B0000x0302:B7FF                                                                            |  |  |  |  |  |  |

| nCDACK                    | 0x0301:20000x0302:AFFF                                                                            |  |  |  |  |  |  |

| nCCS                      | 0x301:00000x0301:FFFF                                                                             |  |  |  |  |  |  |

| nCCS                      | 0x0301:00000x0301:1FFF                                                                            |  |  |  |  |  |  |

| nROMCS                    | 0x0100:00000x01FF:FFFF                                                                            |  |  |  |  |  |  |

| nROMCS                    | 0x0000:00000x003F:FFFF                                                                            |  |  |  |  |  |  |

| nROMCS                    | 0x0000:00000x00FF:FFFF                                                                            |  |  |  |  |  |  |

|                           | Chip Select nEACS nEACS nEACS nEACS nSIOCS2 nSIOCS2 nSIOCS2 nPCCS1 nPCCS2 nCDACK nCCS nCCS nROMCS |  |  |  |  |  |  |

Table 2 shows the interrupt number assignment on the CL-PS7500FE development board.

Table 2: Interrupt request usage on the CL-PS7500FE

|      | 1 1 9                                         |

|------|-----------------------------------------------|

| IRQ# | Used by                                       |

| 1    | ISA DMA Requests (all come to this IRQ)       |

| 2    | Parallel Port (LPT1)                          |

| 3    | Unused                                        |

| 4    | CS8900A Interrupt request (Ethernet)          |

| 5    | CS8900A DMA request (Ethernet)                |

| 6    | Serial Port #1 (COM1)                         |

| 7    | ISA Interrupt requests (all come to this IRQ) |

| 8    | General Purpose IRQ (J4)                      |

| 9    | Serial Port #2 (COM2)                         |

|      |                                               |

As can be seen in the above table, interrupts 1 and 7 are used to represent exceptions from multiple sources on the ISA bus. These are discussed in further detail in Section 4.10.2.

#### **4.1 DRAM**

DRAM is mapped to the range of 0x1000:0000 to 0x1FFF:FFFF (maximum DRAM space is 256MBytes) in the CL-PS7500FE's address space.

There are two 72-pin SIMM sockets on the development board. The sockets may be populated with either FPM or EDO SIMMs. The maximum SIMM size is 128MBytes. SIMMs need not be populated in pairs.

If less than a full 128MByte SIMM is used, the memory will likely be fragmented into smaller segments throughout the memory space. Enabling the MMU in the CL-PS7500FE and re-mapping all of the fragments into a contiguous space can solve this problem.

#### 4.2 FLASH

FLASH is mapped to the range of 0x0000:0000 to 0x0100:0000 on the board (16MBytes). The CL-PS7500FE will begin executing at location 0x0000:0000 under normal circumstances.

FLASH is populated using an 80-pin FLASH SIMM. This approach has several advantages. First, the SIMM can be sized according to the requirements of the application. Second, the speed of the SIMM will be dictated by whether the application is to run or load out of FLASH. Perhaps most importantly, FLASH SIMMs can be procured with different manufacturer's parts (i.e. the SIMM may be populated with Intel's FLASH, or AMD's FLASH). If a developer already has experience with one particular device, or a device with a more feature-rich erase/write state-machine becomes available, a SIMM can be procured with that device on it.

Although standard FLASH SIMMs are available up to 32MBytes, this design does not support SIMMs larger than 16MBytes. The reason for this is that although the ROM space of the CL-PS7500FE has a maximum of 32MBytes, when booting from the on-board boot ROM, a FLASH burning utility may be loaded. In this event, the FLASH is re-mapped to the upper 16MBytes of the ROM space.

In order to be compatible with the evaluation software provided in the kit, one of the following Sharp FLASH SIMMs should be purchased:

**Table 3: Recommended FLASH SIMMs**

| Part number    | Size      | Memory Organization |

|----------------|-----------|---------------------|

| LH59F3211SCTAA | 4 MBytes  | 1M X 32             |

| LH59F3212SCTAA | 8 MBytes  | 2 X 1M X 32         |

| LH59F3221S5TAA | 8 MBytes  | 2M X 32             |

| LH59F3222S5TAA | 16 MBytes | 2 X 2M X 32         |

Version 1.0 11 March 1999

These Sharp FLASH SIMMs can be purchased from Marshall Industries (www.marshall.com).

#### 4.3 Boot ROM

The Boot ROM is normally not addressable by the CL-PS7500FE. If JP12 is installed, the FLASH discussed in the preceding section will be re-mapped to 0x0100:0000, and the boot ROM will be addressed at location 0x0000:0000. The boot ROM can be either a 1MByte or 4MByte device.

Table 4: Boot ROM Enable/Disable Jumper - JP12

| Jumper | Description                                                    |

|--------|----------------------------------------------------------------|

|        | FLASH located at 0x0100:0000, Boot ROM located at 0x0000:0000. |

| • •    | FLASH located at 0x0000:0000, Boot ROM not addressable.        |

Due to the possibility of the boot ROM taking on different tasks in-system, the option of changing the size of the device has been included. The ROM may be either 1 MByte or 4 MBytes. Size is determined by JP11 and is set according to the following table. Caution – do not leave the jumper off. The jumper must be in one of these two positions or damage to the EPROM or random read errors could occur.

**Table 5: Boot ROM Size Selection Jumper – JP11**

| Jumper | Description |

|--------|-------------|

| 1 2 3  | 4 MBytes.   |

| 1 2 3  | 1 MByte.    |

#### 4.4 Clocks

The CL-PS7500FE supports different clocks for the memory CPU and I/O subsystems. The simplest means of clocking the CL-PS7500FE is to use the same clock for all three of the above inputs. In the case of the development board, the CPU clock is run from a Chrontel CH9294G clock generator chip whose frequency is determined by JP2, while the MEMORY clock runs from Y1 at 56MHz. The I/O clock is driven by Y2, running at 64MHz. The intent of running Y2 at 64MHz is so that the divide-by-two mode of operation for the I/O subsystem can be used. Clocks are configured by programming the Clock prescalar register, located at 0x0320:003C:

**Table 6: Clock Prescalar Register**

|  | Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--|------|---|---|---|---|---|---|---|---|

|  | Name | X | X | X | X | X | C | M | I |

**Table 7: Clock Configuration Register**

| Bit | Description                                                 |  |  |  |  |

|-----|-------------------------------------------------------------|--|--|--|--|

| X   | Unspecified.                                                |  |  |  |  |

| C   | CPUCLK – If 1, internal CPU clock = CPUCLK input, otherwise |  |  |  |  |

|     | internal CPU clock = ½ CPUCLK input.                        |  |  |  |  |

| M   | MEMCLK - If 1, internal memory clock = MEMCLK input,        |  |  |  |  |

|     | otherwise internal memory clock = ½ MEMCLK input.           |  |  |  |  |

| I   | I_OCLK - If 1, internal I/O clock = I_OCLK input, otherwise |  |  |  |  |

|     | internal I/O clock = ½ I_OCLK input.                        |  |  |  |  |

The SnA pin on the CL-PS7500FE is used to determine the source of the CPU clock. The SnA pin is jumper configurable according to the following:

Table 8: JP1 (1x2) Definition (Control of SnA pin)

|   | Jumper | Description                                          |  |  |  |  |  |

|---|--------|------------------------------------------------------|--|--|--|--|--|

| Ī |        | SnA pulled low. The CL-PS7500FE treats the MEMCLK    |  |  |  |  |  |

|   |        | and CPUCLK as independent clocks and runs the memory |  |  |  |  |  |

|   |        | subsystem asynchronous to the CPU.                   |  |  |  |  |  |

| Ī |        | SnA pulled high. The CL-PS7500FE uses MEMCLK to      |  |  |  |  |  |

|   |        | drive both the internal memory and CPU clocks.       |  |  |  |  |  |

As stated earlier, the Chrontel clock generator Chip (CH9294G) drives the CPU clock. If the developer would prefer not to use this clock, simply remove JP1 and the 56MHz MEMCLK input will drive the CPU. Otherwise, the CPU speed is configured by JP2. JP2 actually configures both the CPUCLK and the VCLKI inputs to the CL-PS7500FE; however, the jumper fields for setting up VCLKI are discussed in Section 4.13.1.

The following figure illustrates the layout of JP2:

Figure 4: JP2 Jumper Pin Numbering

DRAM SIMMs

DRAM SIMMs

CPUCLK

TO BE TO THE SECOND SECON

Table 9: CPU Clocking Options (if the CH9294G is used for CPU clocking)

| (1-6) | Freq. (MHz) |

|-------|-------------|

|       | 55.0        |

|       | 65.0        |

|       | 70.0        |

|       | 80.0        |

|       | 45.0        |

|       | 40.0        |

|       | 60.0        |

|       | 50.0        |

Note that although clock frequencies as high as 80MHz can be specified for the CPU clock, anything above 55MHz is currently not supported.

#### 4.5 Power Management Modes

The CL-PS7500FE supports three different modes of operation: Normal, Suspend, and Stop. The development board has only limited capability in this regard (the Normal mode is the only one fully supported).

The key missing point is that the oscillators on the board cannot be stopped under software control. If the developer's application requires this functionality, please contact Cirrus Logic regarding specific implementation details.

Although the oscillators cannot be stopped, the processor can still enter the Suspend and Stop modes.

In the Suspend mode, barring the fact that the oscillators are still running, the DMA controller still operates within the CL-PS7500FE so things like the display can continue to be refreshed and updated.

Version 1.0 13 March 1999

In the Stop mode, a fully functional system would stop all clocks completely, and consume only leakage current. Caution should be exercised when entering and exiting this mode as the LCD may become damaged if not properly shut down. Consult the documentation that comes with the specific LCD being connected. Specifically, the problem is that if the bias voltage to the display (supplied by the customer) is left on and the pixel clocks to the LCD are stopped, the display will burn up. This is an unfortunate problem with some LCDs.

An active low pulse on either of the nEVENT pins or on the nPOR pin of the CL-PS7500FE will cause the processor to exit the Suspend or Stop mode. One difference between the Stop and Suspend modes is that the Suspend mode may be exited via an IRQ or a FIQ. This means that an interrupt from the serial port, mouse, keyboard, or any other interrupt driven peripheral may cause the processor to transition to the Normal mode.

For full details on entering the alternate modes, please consult the CL-PS7500FE Advance Data Book, V2.0, Chapter 21.

### 4.6 Logic Analyzer Headers

There are eight logic analyzer headers on this design (JP3 to JP10). The headers provide the developer with direct access to many important signals on the board. The pin-outs for the headers are shown on the schematics and listed in the following tables.

Table 10: JP3 Logic Analyzer Header Definition

| Tuble 10: 01 5 Eogle Amaryzer Header Deminion |    |    |                                      |  |  |  |

|-----------------------------------------------|----|----|--------------------------------------|--|--|--|

| Description                                   | #  | #  | Description                          |  |  |  |

| VCC (+5V)                                     | 1  | 2  | VCC (+5V)                            |  |  |  |

| KBCLK (Keyboard shift clock)                  | 3  | 4  | KBDATA (Keyboard serial data)        |  |  |  |

| MSDATA (Mouse port serial data)               | 5  | 6  | MSCLK (Mouse port shift clock)       |  |  |  |

| SDCLK (Sound port data shift clock)           | 7  | 8  | SDO (Sound port data)                |  |  |  |

| SCLK (Sound system clock)                     | 9  | 10 | WS (Sound port channel (left/right)) |  |  |  |

| ECLK (Video data shift clock)                 | 11 | 12 | ED7 (Video data)                     |  |  |  |

| ED6 (Video data)                              | 13 | 14 | ED5 (Video data)                     |  |  |  |

| ED4 (Video data)                              | 15 | 16 | ED3 (Video data)                     |  |  |  |

| ED2 (Video data)                              | 17 | 18 | ED1 (Video data)                     |  |  |  |

| ED0 (Video data)                              | 19 | 20 | Ground                               |  |  |  |

Table 11: JP4 Logic Analyzer Header Definition

| Description                           | #  | #  | Description                           |

|---------------------------------------|----|----|---------------------------------------|

| VCC (+5V)                             | 1  | 2  | VCC (+5V)                             |

| NSIOCS1 (simple I/O chip select)      | 3  | 4  | HCLK (Optional video input clock)     |

| NSIOCS2 (simple I/O chip select)      | 5  | 6  | 16MHz (16MHz IO system clock)         |

| NEASCS (ISA Bus space select)         | 7  | 8  | CPUCLK (CL-PS7500FE processor clock)  |

| OD1 (general purpose open drain I/O)  | 9  | 10 | IOCLK (CL-PS7500FE I/O system clock   |

| OD0 (general purpose open drain I/O)  | 11 | 12 | IOP7 (general purpose open drain I/O) |

| IOP6 (general purpose open drain I/O) | 13 | 14 | IOP5 (general purpose open drain I/O) |

| IOP4 (general purpose open drain I/O) | 15 | 16 | IOP3 (general purpose open drain I/O) |

| IOP2 (general purpose open drain I/O) | 17 | 18 | IOP1 (general purpose open drain I/O) |

| IOP0 (general purpose open drain I/O) | 19 | 20 | Ground                                |

Table 12: JP5 Logic Analyzer Header Definition

| Tubic 12.01 c 20gi      |    | yzer medder benningn |                     |  |  |

|-------------------------|----|----------------------|---------------------|--|--|

| Description             | #  | #                    | Description         |  |  |

| VCC (+5V)               | 1  | 2                    | VCC (+5V)           |  |  |

| D16 (main data bus bit) | 3  | 4                    | D15 (main data bus) |  |  |

| D14 (main data bus)     | 5  | 6                    | D13 (main data bus) |  |  |

| D12 (main data bus)     | 7  | 8                    | D11 (main data bus) |  |  |

| D10 (main data bus)     | 9  | 10                   | D9 (main data bus)  |  |  |

| D8 (main data bus)      | 11 | 12                   | D7 (main data bus)  |  |  |

| D6 (main data bus)      | 13 | 14                   | D5 (main data bus)  |  |  |

| D4 (main data bus)      | 15 | 16                   | D3 (main data bus)  |  |  |

| D2 (main data bus)      | 17 | 18                   | D1 (main data bus)  |  |  |

| D0 (main data bus)      | 19 | 20                   | Ground              |  |  |

Table 13: JP6 Logic Analyzer Header Definition

| Description                    | #  | #  | Description                    |

|--------------------------------|----|----|--------------------------------|

| VCC (+5V)                      | 1  | 2  | VCC (+5V)                      |

| D31 (main data bus)            | 3  | 4  | D30 (main data bus)            |

| D29 (main data bus)            | 5  | 6  | D28 (main data bus)            |

| D27 (main data bus)            | 7  | 8  | D26 (main data bus)            |

| D25 (main data bus)            | 9  | 10 | D24 (main data bus)            |

| D23 (main data bus)            | 11 | 12 | D22 (main data bus)            |

| D21 (main data bus)            | 13 | 14 | D20 (main data bus)            |

| D19 (main data bus)            | 15 | 16 | D18 (main data bus)            |

| D17 (main data bus)            | 17 | 18 | READY (CL-PS7500FE Ready line) |

| nROMCS (FLASH/ROM chip select) | 19 | 20 | Ground                         |

**Table 14: JP7 Logic Analyzer Header Definition**

|    |                                              | aci Deiminon                                     |

|----|----------------------------------------------|--------------------------------------------------|

| #  | #                                            | Description                                      |

| 1  | 2                                            | VCC (+5V)                                        |

| 3  | 4                                            | BD15 (16-bit I/O data)                           |

| 5  | 6                                            | BD13 (16-bit I/O data)                           |

| 7  | 8                                            | BD11 (16-bit I/O data)                           |

| 9  | 10                                           | BD9 (16-bit I/O data)                            |

| 11 | 12                                           | BD7 (16-bit I/O data)                            |

| 13 | 14                                           | BD5 (16-bit I/O data)                            |

| 15 | 16                                           | BD3 (16-bit I/O data)                            |

| 17 | 18                                           | BD1 (16-bit I/O data)                            |

| 19 | 20                                           | Ground                                           |

|    | #<br>1<br>3<br>5<br>7<br>9<br>11<br>13<br>15 | # # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

Table 15: JP8 Logic Analyzer Header Definition

| Table 13. 31 6 Logic Analyzer Header Definition |    |    |                         |  |  |  |

|-------------------------------------------------|----|----|-------------------------|--|--|--|

| Description                                     | #  | #  | Description             |  |  |  |

| VCC (+5V)                                       | 1  | 2  | VCC (+5V)               |  |  |  |

| LA28 (main address bus)                         | 3  | 4  | LA27 (main address bus) |  |  |  |

| LA26 (main address bus)                         | 5  | 6  | LA25 (main address bus) |  |  |  |

| LA24 (main address bus)                         | 7  | 8  | LA23 (main address bus) |  |  |  |

| LA22 (main address bus)                         | 9  | 10 | LA21 (main address bus) |  |  |  |

| LA20 (main address bus)                         | 11 | 12 | LA19 (main address bus) |  |  |  |

| LA18 (main address bus)                         | 13 | 14 | LA17 (main address bus) |  |  |  |

| LA16 (main address bus)                         | 15 | 16 | LA15 (main address bus) |  |  |  |

| LA14 (main address bus)                         | 17 | 18 | LA13 (main address bus) |  |  |  |

| LA12 (main address bus)                         | 19 | 20 | Ground                  |  |  |  |

Version 1.0 15 March 1999

**Table 16: JP9 Logic Analyzer Header Definition**

| Description                       | #  | #  | Description             |

|-----------------------------------|----|----|-------------------------|

| VCC (+5V)                         | 1  | 2  | VCC (+5V)               |

| LA10 (main address bus)           | 3  | 4  | LA11 (main address bus) |

| LA8 (main address bus)            | 5  | 6  | LA9 (main address bus)  |

| LA6 (main address bus)            | 7  | 8  | LA7 (main address bus)  |

| LA4 (main address bus)            | 9  | 10 | LA5 (main address bus)  |

| LA2 (main address bus)            | 11 | 12 | LA3 (main address bus)  |

| LA0 (main address bus)            | 13 | 14 | LA1 (main address bus)  |

| nRAS2 (DRAM Row strobe)           | 15 | 16 | nRAS3 (DRAM Row strobe) |

| nRAS0 (DRAM Row strobe)           | 17 | 18 | nRAS1 (DRAM Row strobe) |

| nIOW (I/O and FLASH write strobe) | 19 | 20 | Ground                  |

Table 17: JP10 Logic Analyzer Header Definition

|                                  |    | •  |                            |

|----------------------------------|----|----|----------------------------|

| Description                      | #  | #  | Description                |

| VCC (+5V)                        | 1  | 2  | VCC (+5V)                  |

| NIOR (I/O and FLASH read strobe) | 3  | 4  | nCAS3 (DRAM Column strobe) |

| NCAS2 (DRAM Column strobe)       | 5  | 6  | nCAS1 (DRAM Column strobe) |

| NCAS0 (DRAM Column strobe)       | 7  | 8  | RA11 (DRAM address bus)    |

| RA10 (DRAM address bus)          | 9  | 10 | RA9 (DRAM address bus)     |

| RA8 (DRAM address bus)           | 11 | 12 | RA7 (DRAM address bus)     |

| RA6 (DRAM address bus)           | 13 | 14 | RA5 (DRAM address bus)     |

| RA4 (DRAM address bus)           | 15 | 16 | RA3 (DRAM address bus)     |

| RA2 (DRAM address bus)           | 17 | 18 | RA1 (DRAM address bus)     |

| RA0 (DRAM address bus)           | 19 | 20 | Ground                     |

### 4.7 Keyboard and Mouse

The keyboard and mouse ports in the CL-PS7500FE are identical. Each is intended for connection to a PS/2 style mouse or keyboard.

The mouse port consists of MSCLK (CL-PS7500FE pin 165) and MSDATA (CL-PS7500FE pin 167), which are brought out to J3. The keyboard port consists of KBCLK (CL-PS7500FE pin 168) and KBDATA (CL-PS7500FE pin 169), which are brought out to J2.

From a programmer's perspective, each interface consists of the following registers:

Table 18: Keyboard and Mouse Registers

|        |             | 9                                  |

|--------|-------------|------------------------------------|

| Name   | Location    | Description                        |

| KBDCR  | 0x0320:0008 | Keyboard control/status register.  |

| KBDAT  | 0x0320:0004 | Keyboard data read/write register. |

| MSECR  | 0x0320:00AC | Mouse control/status register.     |

| MSEDAT | 0x0320:00A8 | Mouse data read/write register.    |

Each data register is used both for reading and writing information to and from each of the two interfaces.

Each of the above control/status registers has a different bit definition for read vs. write. The following tables outline the differences.

Table 19: PS2 Control Register Write Bit Mapping

| Bit  | 7 | 6 | 5 | 4 | 3   | 2 | 1   | 0   |

|------|---|---|---|---|-----|---|-----|-----|

| Name | X | X | X | X | ENA | X | DAT | CLK |

**Table 20: PS2 Control Register Write Bit Definition**

|     | 8                                                                       |

|-----|-------------------------------------------------------------------------|

| Bit | Description                                                             |

| X   | Unspecified.                                                            |

| ENA | Enable line. Set this pin high to enable the PS2 interface being        |

|     | used. Set low to disable.                                               |

| DAT | Data line. Setting this bit to 1 forces the data pin of the specified   |

|     | PS2 interface low. Setting this bit to 0 floats the data pin.           |

|     | Assuming a pull-up is on this open-drain pin, the data pin will float   |

|     | high.                                                                   |

| CLK | Clock line. Setting this bit to 1 forces the clock pin of the specified |

|     | PS2 interface low. Setting this bit to 0 floats the clock pin.          |

|     | Assuming a pull-up is on this open-drain pin, the clock pin will        |

|     | float high.                                                             |

Table 21: PS2 Control Register Read Bit Mapping

| Bit  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name | TXE | TXB | RXF | RXB | ENA | RXP | DAT | CLK |

**Table 22: PS2 Control Register Write Bit Definition**

| Bit | Description                                                            |  |  |  |  |  |  |  |

|-----|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| TXE | Transmit shift register status. If 0, the transmit shift register is   |  |  |  |  |  |  |  |

|     | busy. If 1, the transmit shift register is ready to accept data.       |  |  |  |  |  |  |  |

| TXB | Transmitter busy bit. If 0, the transmitter is NOT busy. If 1, the     |  |  |  |  |  |  |  |

|     | transmitter is busy.                                                   |  |  |  |  |  |  |  |

| RXF | Receive shift register status bit. If 0, the receive shift register is |  |  |  |  |  |  |  |

|     | NOT full. If 1, the receive shift register is full.                    |  |  |  |  |  |  |  |

| RXB | Receiver busy bit. If 0, the receiver is NOT busy. If 1, the           |  |  |  |  |  |  |  |

|     | receiver is busy.                                                      |  |  |  |  |  |  |  |

| ENA | Enable status. If 1, the associated PS2 interface is enabled. If 0,    |  |  |  |  |  |  |  |

|     | the interface is disabled.                                             |  |  |  |  |  |  |  |

| RXP | Received data parity bit. This bit is an odd parity bit associated     |  |  |  |  |  |  |  |

|     | with the last received byte.                                           |  |  |  |  |  |  |  |

| DAT | Status of the data pin of the selected PS2 interface. If the pin is    |  |  |  |  |  |  |  |

|     | high, this bit will be 1, otherwise it will be 0.                      |  |  |  |  |  |  |  |

| CLK | Status of the clock pin of the selected PS2 interface. If the pin is   |  |  |  |  |  |  |  |

|     | high, this bit will be 1, otherwise it will be 0.                      |  |  |  |  |  |  |  |

In addition to the above control and status register definitions, each register has the following data registers:

The keyboard interface may be polled or interrupt driven. Both "transmit register empty" and "receive register full" interrupts are available. These are found in the IRQB register set. The locations and bits associated with IRQB are shown in the following table:

Version 1.0 17 March 1999

**Table 23: Keyboard Interrupt Control**

| Register           | Location    | Description             | Bits used                        |

|--------------------|-------------|-------------------------|----------------------------------|

| IRQSTB             | 0x0320:0020 | IRQB interrupt status   | 7 = keyboard receive interrupt.  |

|                    |             | (enabled/disabled).     | 6 = keyboard transmit interrupt. |

| IRQRQB 0x0320:0024 |             | IRQB interrupt requests | 7 = keyboard receive interrupt.  |

|                    |             |                         | 6 = keyboard transmit interrupt. |

| IRQMSKB            | 0x0320:0028 | IRQB interrupt enable   | 7 = keyboard receive interrupt.  |

|                    |             | mask.                   | 6 = keyboard transmit interrupt. |

The mouse interface may be polled or interrupt driven in exactly the same fashion as the keyboard interface. Both "transmit register empty" and "receive register full" interrupts are available. These are found in the IRQD register set. The locations and bits associated with IRQD are shown in the following table:

**Table 24: Mouse Interrupt Control**

| Register | Location    | Description             | Bits used                     |

|----------|-------------|-------------------------|-------------------------------|

| IRQSTD   | 0x0320:0070 | IRQD interrupt status   | 1 = mouse transmit interrupt. |

|          |             | (enabled/disabled).     | 0 = mouse receive interrupt.  |

| IRQRQD   | 0x0320:0074 | IRQD interrupt requests | 1 = mouse transmit interrupt. |

|          |             |                         | 0 = mouse receive interrupt.  |

| IRQMSKD  | 0x0320:0078 | IRQD interrupt enable   | 1 = mouse transmit interrupt. |

|          |             | mask.                   | 0 = mouse receive interrupt.  |

#### 4.8 Sound

#### 4.8.1 Physical Details

The sound system in the CL-PS7500FE consists of a serial interface intended for driving a 16-bit stereo DAC. In the case of the development board, the sound system pins are connected to a Crystal Semiconductor CS4333 16-bit stereo DAC. This DAC outputs data to the headset port, J1.

The serial arrangement in the sound system consists of four pins, the functions of which are summarized in the table below:

**Table 25: Sound System External Interface**

| Name  | Pin # | Description                                                        |  |  |  |  |  |

|-------|-------|--------------------------------------------------------------------|--|--|--|--|--|

| SDO   | 68    | Serial Data. This line shifts out the serial data in 32-bit words, |  |  |  |  |  |

|       |       | 16-bits for the left and 16-bits for the right channel. Values on  |  |  |  |  |  |

|       |       | the data pin change on the falling edge of SDCLK.                  |  |  |  |  |  |

| SDCLK | 70    | Serial Data Shift Clock. This is the synchronous serial clock for  |  |  |  |  |  |

|       |       | shifting out data. Data is shifted out MSB first.                  |  |  |  |  |  |

| WS    | 71    | Word Select. This pin is high during the transmission of the left  |  |  |  |  |  |

|       |       | channel data, low otherwise. The state of the pin changes on the   |  |  |  |  |  |

|       |       | MSB of the left channel data. This is connected to the LRCK or     |  |  |  |  |  |

|       |       | left/right clock of the CS4333                                     |  |  |  |  |  |

| SCLK  | 69    | This is the master clock used by the DAC.                          |  |  |  |  |  |

In the table above, the "Japanese" mode of operation of the sound macrocell is assumed. If the developer is interested in the alternate mode (Normal) please refer to Chapter 13 of the CL-PS7500FE Advance Data Book V2.0. This mode is not used because the default mode of the CS4333 is not compatible with it.

The sound portion of the video macrocell in the CL-PS7500FE supports operating the sound system clock either off of a clock derived from the I/O clock, or off of an external clock. Since the desired sample rate of the CS4333 is 44.1kHz, an external clock is required. This clock must be either 256, 384 or 512 times the desired sample rate. In

this case, 256x was the chosen value, so the external clock for the sound subsystem is 11.2896MHz. This clock is an input to the SCLK pin of the CL-PS7500FE, as well as the MCLK pin of the CS4333.

In the case of the CS4333, the DAC will be operated in the externally clocked mode. This is the only mode available, as the CL-PS7500FE will not accept a clock on the SDCLK line. The CS4333's de-emphasis filter will also be unavailable, as it is not supported when running the DAC in externally clocked mode.

The CS4333 has a register that is programmed by setting the serial data line high, using the left/right clock as a shift clock, and shifting data in via the serial data clock line. The CL-PS7500FE does not support this type of communication, so the CS4333 must be operated in its default mode. The setting is as follows:

- 16 bits per channel, meaning at least 32 shift clocks per combined left and right sample.

- Right justified. That is, the left/right clock changes on the falling edge of SCLK on the least significant data bit.

- Data is latched into the CS4333 on the rising edge of SDCLK. The CL-PS7500FE changes data on the falling edge of SDCLK, so set-up/hold times are comfortably met.

- The left/right clock (LRCK) is defined as high on the left channel, low on the right channel. The only way to support this is to use the "Japanese" mode of the sound macrocell.

### 4.8.2 Programming Details

Programming the following values into these registers, configures the sound macrocell in the CL-PS7500FE:

**Table 26: Sound Macrocell Configuration Parameters**

| Register | Location    | Value       | Description                       |  |  |  |  |  |  |

|----------|-------------|-------------|-----------------------------------|--|--|--|--|--|--|

| SFR      | 0x0340:0000 | 0xB000:0002 | Sound Frequency Register          |  |  |  |  |  |  |

| SCTL     | 0x0340:0000 | 0xB100:0002 | Sound Control Register            |  |  |  |  |  |  |

| VIDMUX   | 0x0320:006C | VIDMUX[1]=1 | Video LCD and serial sound mux    |  |  |  |  |  |  |

|          |             |             | control. This sets Japanese Mode. |  |  |  |  |  |  |

In addition, there are two sets of DMA pointers to ensure the DAC never runs out of data. This permits software to fill one block of the sound page in memory while the DMA controller is reading data from another. All sound data must be written into a 4Kbyte page in the CL-PS7500FE's memory. DMA data is transferred in blocks of four 32-bit words, or Qwords; the 4Kbyte block of memory must be Qword aligned. To configure the DMA pointer registers, write the following:

Table 27: Sound System DMA and Interrupt Registers

| Register | Location    | Description                                           |

|----------|-------------|-------------------------------------------------------|

| SDCURA   | 0x0320:0180 | Sound DMA Current Address Frequency Register, page A. |

| SDENDA   | 0x0320:0184 | Last Qword location in sound page A.                  |

| SDCURB   | 0x0320:0188 | Sound DMA Current Address Frequency Register, page B. |

| SDENDB   | 0x0320:018C | Last Qword location in sound page B.                  |

Specific values are not listed in the above table, as the location of the sound data pages in memory is entirely up to the programmer. For information on the pointer registers, please consult the CL-PS7500FE Advance Data Book V2.0, pages 99-101.

In addition to the above address pointer configuration, there are control and status registers that must be configured:

**Table 28: SDCR – Sound DMA Control Register Configuration (0x0320:0190)**

| Bit  | 7   | 6 | 5   | 4 | 3 | 2 | 1 | 0 |

|------|-----|---|-----|---|---|---|---|---|

| Name | CLR | X | ENA | 1 | X | X | X | X |

Version 1.0 19 March 1999

**Table 29: SDCR Register Write Bit Definition**

| Bit   | Description                                                             |  |  |  |  |  |  |

|-------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| CLR   | Clear bit. Setting this bit resets the sound state machine. Writing a 0 |  |  |  |  |  |  |

|       | to this bit won't explicitly clear the state machine.                   |  |  |  |  |  |  |

| ENA   | Writing a 0 to this bit shuts down the sound system, writing a 1        |  |  |  |  |  |  |

|       | enables it.                                                             |  |  |  |  |  |  |

| Bit 4 | This bit is not relevant when writing to the control register, but when |  |  |  |  |  |  |

|       | reading, it should be noted that the bit is always 1.                   |  |  |  |  |  |  |

The sound DMA status register is read only, and contains only 3 bits.

Table 30: SDST – Sound DMA Status Register Configuration (0x0320:0190)

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

| Name | X | X | X | X | X | О | I | W |

**Table 31: SDCR Register Write Bit Definition**

| Bit | Description                                                             |

|-----|-------------------------------------------------------------------------|

| О   | Overrun bit. This bit is set if the DMA state machine has been overrun. |

| I   | Interrupt bit. If 1, this bit indicates that a DMA interrupt request is |

|     | pending.                                                                |

| W   | Which buffer? This bit indicates 0 for buffer A, 1 for buffer B as the  |

|     | buffer currently being accessed by the DMA controller.                  |

For further details on the programming the sound system, please consult the CL-PS7500FE Advance Data Book V2.0, sections 9.3.3-4, 10.3.28, 10.3.51-56, 13, 14.1.7, 16.29-30, 21.1.1, and 22.8.

#### 4.9 Event Switches

There are three key-switches on the development board, S1-S3. These switches are connected to the following subsystems on the board:

**Table 32: Event Switch Functions**

|            | Tuble 62. Event Switch I directors                                |  |  |  |  |  |  |

|------------|-------------------------------------------------------------------|--|--|--|--|--|--|

| Switch     | Function(s)                                                       |  |  |  |  |  |  |

| S1         | nEVENT1 on the CL-PS7500FE. Asserts the nEVENT1 interrupt         |  |  |  |  |  |  |

|            | in the CL-PS7500FE. If the CL-PS7500FE is in Stop or Suspend      |  |  |  |  |  |  |

|            | mode, pressing this switch will wake up the processor.            |  |  |  |  |  |  |

| S2         | nEVENT2 on the CL-PS7500FE. Asserts the nEVENT2 interrupt         |  |  |  |  |  |  |

|            | in the CL-PS7500FE. If the CL-PS7500FE is in Stop or Suspend      |  |  |  |  |  |  |

|            | mode, pressing this switch will wake up the processor.            |  |  |  |  |  |  |

| <b>S</b> 3 | nPOR. This switch is connected to the power on reset circuitry of |  |  |  |  |  |  |

|            | the CL-PS7500FE. Pressing this switch will reset the entire       |  |  |  |  |  |  |

|            | system.                                                           |  |  |  |  |  |  |

For details on the event pins and how they are used to exit Stop and Suspend modes, please refer to Section 4.5 of this document, and the CL-PS7500FE Advance Data Book V2.0, Chapter 21.

#### 4.10 ISA Interface

The ISA interface on the board is fully buffered and will support most ISA bus transactions. Key differences between a PC ISA bus and the development board ISA bus are discussed here.

#### 4.10.1 CL-PS7500FE Memory Mapping

Whereas the ISA bus in a PC has I/O mapped registers at the bottom of the x86's memory map, the ISA bus is mapped into a section of memory of the CL-PS7500FE. Although the organization of ISA address space was hinted at in Figure 3, further details on decoding are given here.

Table 33: ISA Map to CS-PS7500FE Memory Space

| Address Range          | Description                                                           |

|------------------------|-----------------------------------------------------------------------|

| 0x0800:00000x0BFF:FFFF | ISA memory mapped device access. Devices requiring memory             |

|                        | read and write strobes are addressed in this range.                   |

| 0x0C00:00000x0DFF:FFFF | ISA I/O devices are addressed in this range. During I/O access to     |

|                        | this range, the AEN line of the ISA bus is asserted.                  |

| 0x0E00:00000x0FFF:FFFF | Addressing this portion of ISA space will produce a DMA               |

|                        | Acknowledge as well as the appropriate I/O strobe. CL-PS7500FE        |

|                        | address bits LA[4:2] decode to the specific DMA channel being         |

|                        | decoded. For an example of how this decoding works, see Table 35.     |

| 0x0Enn:nn2n0x0Fnn:nn3n | Note that this space is a subset of the above space. Accessing        |

|                        | addresses that have $LA[7:5] = [0:0:1]$ will assert the TC pin to the |

|                        | ISA bus as well. This is part of the DMA Acknowledge space. For       |

|                        | an example of how this decoding works, see Table 35.                  |

Note that these address spaces rely on address bits that normally do not decode onto the ISA bus (any address > LA25). Note also that LA25 translates to A23 on the ISA bus. Memory mapped devices should therefore be configured to decode at an address with A23 set to 0.

The ISA data bus is only 16-bits wide and an important point must be observed about communicating with this space. All accesses to this space must be treated as 32-bit, even though only 16-bits of data are being used. This data is read from and written to the lower 16-bits of each 32-bit word.

#### 4.10.2 Exception Support

Exceptions from the ISA bus come in the form of interrupts and DMA requests. Since both types of exception are quite similar, and the CL-PS7500FE does not directly support DMA requests and acknowledges from the ISA bus subsystem, DMA requests and interrupts are treated as a common form of exception. When a DMA request is made, the CL-PS7500FE will receive an interrupt request on IRQ1. When an ISA device asserts an interrupt request, the CL-PS7500FE will receive an interrupt on IRQ7.

Determining which device asserted the DMA/IRQ is a matter of reading a register. The register is located at any address in the range 0x0302:B700...0x0302:B7FF. The register is 16-bits wide and is read only. The definition of each bit is as follows:

Table 34: ISA Exception Register Bit Definition

| Bit #      | D15   | D14   | D13   | D12  | D11  | D10  | D9   | D8    |

|------------|-------|-------|-------|------|------|------|------|-------|

| Exception: | DRQ7  | DRQ6  | DRQ5  | DRQ3 | DRQ2 | DRQ1 | DRQ0 | IRQ15 |

| Bit #      | D7    | D6    | D5    | D4   | D3   | D2   | D1   | D0    |

| Exception: | IRQ14 | IRQ11 | IRQ10 | IRQ9 | IRQ7 | IRQ5 | IRQ4 | IRQ3  |

As noted in the previous section, DMA requests are acknowledged by writing to portions of the address space reserved for this activity. Table 35 below illustrates how the DMA acknowledge "space" is addressed to acknowledge the desired DMA.

Version 1.0 21 March 1999

**Table 35: DMA Acknowledge Memory Space**

| DACK | Address     | Address (w. TC) |

|------|-------------|-----------------|

| 0    | 0x0E00:0000 | 0x0E00:0020     |

| 1    | 0x0E00:0004 | 0x0E00:0024     |

| 2    | 0x0E00:0008 | 0x0E00:0028     |

| 3    | 0x0E00:000C | 0x0E00:002C     |

| 5    | 0x0E00:0010 | 0x0E00:0030     |

| 6    | 0x0E00:0014 | 0x0E00:0034     |

| 7    | 0x0E00:0018 | 0x0E00:0038     |

#### 4.11 SMSC 37C665 PC Combo Chip

The PC Combo chip on this board is an SMSC product model 37C665, and is common to many PC motherboards. Although the Combo chip supports connections to IDE and floppy drives, these have not been implemented on the development board. The only portions of the combo chip that have been implemented are the two serial ports and the one parallel port. Each of these three interfaces is discussed in detail in the following sections.

Prior to attempting to use the ports available, the 37C665 must be configured. The device has two addresses listed in the following table.

Table 36: PC Combo Chip Set-Up Registers

| Name | Address     | Description                                            |

|------|-------------|--------------------------------------------------------|

| CFGA | 0x0301:0FC0 | Chip Configuration register A. Write internal PC combo |

|      |             | chip configuration register addresses here.            |

| CFGB | 0x0301:0FC4 | Chip Configuration register B. Read and write          |

|      |             | configuration register data here.                      |

The 37C665 has an IDE interface and floppy disk interface and both are enabled by default, so some minor programming of the configuration registers is required. Note that the programming of configuration registers as discussed here is not exhaustive. Developers who want to move devices around in the CL-PS7500FE's address space, or enable/disable different devices should consult the 37C665 specification.

When configuring the 37C665, first the device must first be placed in configuration mode. To do this, write the following sequence to CFGA: 0x55 0x55. These two writes must happen in immediate succession and there must not be any bus cycle activity between the writes. For this reason, it is highly recommended that interrupts be disabled prior to writing this sequence.

There are a total of 16 internal configuration registers in the 37C665. Data written to CFGA is the index of the configuration register to be read or written, with the actual register being read or written via CFGB.

The following table outlines the write sequence and what is being set up on the combo chip:

Table 37: PC Combo Chip Configuration Register Default Values

| CFGA | CFGB | Description                                                                             |

|------|------|-----------------------------------------------------------------------------------------|

| 0x00 | 0x20 | This value will disable both the IDE and floppy drive interfaces within the combo       |

|      |      | chip. It will also set the serial port baud rate generator to be active only when the   |

|      |      | PWRGD pin is set high. This is the case in normal operation. If the pin is pulled       |

|      |      | low for any reason, the baud rate generator for the serial ports will be shut down.     |

| 0x01 | 0x9F | This is actually the default value of this register at power-up. The value is           |

|      |      | discussed here to explain what is being set up. This register sets both serial port     |

|      |      | interrupts and the parallel port interrupt to be active high. The register is also used |

|      |      | to configure the decoding addresses of the parallel port and COM 3/4. COM 3 and         |

|      |      | 4 are not implemented in this design, but the corresponding bits for their decode       |

|      |      | should be left at their default values. The following sections of this document list    |

|      |      | addresses where each port may be found. The default decoding is assumed. The            |

|      |      | parallel port is configured for normal mode. For extended modes, please consult         |

|      |      | the 37C665 data sheet. Also, the most significant bit of this register is used to lock  |

|      |      | out accesses to the registers. By default, the bit is high, meaning unlocked. If this   |

|      |      | bit is set low, there will be no way to regain access to any of the configuration       |

|      |      | registers without a hard reset or power down.                                           |

| 0x02 | 0xDC | This register enables and sets the base addresses of the two serial ports on the        |

|      |      | development board. The value listed at left is actually the default, but its meaning    |

|      |      | is discussed here. The value shown puts the serial port addresses at the locations      |

|      |      | shown in the following sections on serial ports. The ports are also enabled and         |

|      |      | powered up under the control of this register. The default is to have both ports on.    |

| 0x03 | 0x78 | This register controls the operation of the floppy drive. Since this part of the chip   |

|      |      | should be powered down, the register should either be programmed with the               |

|      |      | default value at left, or left alone.                                                   |

| 0x04 | 0x00 | This register controls the parallel port mode and the serial port clocking. The         |

|      |      | default is correct for standard operation of the serial ports. Developers have the      |

|      |      | option of setting the serial ports to run at MIDI data rates and to run the parallel    |

|      |      | port in one of its extended modes.                                                      |

Although there are 16 registers, those not listed are either related to the floppy and IDE drive interfaces, or are reserved.

After the configuration registers have been programmed, the 37C665 is taken out of configuration mode by writing 0xAA to the CFGA register. Be sure to do this prior to attempting to communicate with any of the ports.

#### **4.11.1** Serial Port #1 (COM1)

COM1 is a standard 16C550A-compatible UART. The maximum data rate of this port is 115,200 baud. Port registers are addressed in the CL-PS7500FE's memory at the following locations:

**Table 38: COM1 Address Registers**

|            | Table 30. COMI Mudress Registers |                                       |  |  |  |  |

|------------|----------------------------------|---------------------------------------|--|--|--|--|

| Name       | Location                         | Description                           |  |  |  |  |

| DLAB (LSB) | 0x0301:0FE0                      | Baud Rate Divisor Latch LSB           |  |  |  |  |

| DLAB (MSB) | 0x0301:0FE4                      | Baud Rate Divisor Latch MSB           |  |  |  |  |

| RBR/THR    | 0x0301:0FE0                      | Receive Buffer Register / Transmitter |  |  |  |  |

|            |                                  | Holding Register                      |  |  |  |  |

| IER        | 0x0301:0FE4                      | Interrupt Enable Register             |  |  |  |  |

| IIR        | 0x0301:0FE8                      | Interrupt Identification Register     |  |  |  |  |

| LCR        | 0x0301:0FEC                      | Line Control Register                 |  |  |  |  |

| MCR        | 0x0301:0FF0                      | Modem Control Register                |  |  |  |  |

| LSR        | 0x0301:0FF4                      | Line Status Register                  |  |  |  |  |

| MSR        | 0x0301:0FF8                      | Modem Status Register                 |  |  |  |  |

| SR         | 0x0301:0FFC                      | Scratch Register                      |  |  |  |  |

Version 1.0 23 March 1999

COM1 uses Interrupt Request 6 on the CL-PS7500FE.

#### **4.11.2** Serial Port #2 (COM2)

COM2 is also a standard 16C550A-compatible UART. The maximum data rate of this port is 115,200 baud. Port registers are addressed in the CL-PS7500FE's memory at the following locations:

Table 39: COM2 Address Registers

|            | Tuble 59: CONIZ Hadress Registers |                                       |  |  |  |  |

|------------|-----------------------------------|---------------------------------------|--|--|--|--|

| Name       | Location                          | Description                           |  |  |  |  |

| DLAB (LSB) | 0x0301:0BE0                       | Baud Rate Divisor Latch LSB           |  |  |  |  |

| DLAB (MSB) | 0x0301:0BE4                       | Baud Rate Divisor Latch MSB           |  |  |  |  |

| RBR/THR    | 0x0301:0BE0                       | Receive Buffer Register / Transmitter |  |  |  |  |

|            |                                   | Holding Register                      |  |  |  |  |

| IER        | 0x0301:0BE4                       | Interrupt Enable Register             |  |  |  |  |

| IIR        | 0x0301:0BE8                       | Interrupt Identification Register     |  |  |  |  |

| LCR        | 0x0301:0BEC                       | Line Control Register                 |  |  |  |  |

| MCR        | 0x0301:0BF0                       | Modem Control Register                |  |  |  |  |

| LSR        | 0x0301:0BF4                       | Line Status Register                  |  |  |  |  |

| MSR        | 0x0301:0BF8                       | Modem Status Register                 |  |  |  |  |

| SR         | 0x0301:0BFC                       | Scratch Register                      |  |  |  |  |

COM2 uses Interrupt Request 9 on the CL-PS7500FE.

#### 4.11.3 IrDA Support

In addition to being a standard serial port, COM2 can be optionally connected to the on-board IrDA transceiver.

JP13 is used to control whether COM2 is connected to J14 on the development board, or is connected to the IrDA transceiver. The function of JP13 is shown in the following table:

Table 40: JP13 (1x2) Definition (Control of Serial Port #2)

| Jumper | Description                                                             |

|--------|-------------------------------------------------------------------------|

|        | Serial Port #2 is wired to J14 and functions as a standard serial port. |

|        | Serial Port #2 is connected to the IrDA transceiver and is able to      |

|        | interface to IrDA compliant equipment.                                  |

The components used to form the IrDA interface on the development board are the TOIM3232 and the TFDS4500, both manufactured by Temic Semiconductors.

The TFDS4500 is the most recognizable component, as it contains the Ir diodes used for transmitting and receiving data (U26). This device has a theoretical maximum data rate of 4Mbaud. However because the TDFS4500 is connected to COM2, which has a maximum data rate of 115,200 baud, the maximum data rate is thus 115,200 baud.

The TOIM3232 is a device used to adjust outgoing serial port pulses to the correct width for the TFDS4500. The maximum data rate of the TOIM3232 is 115,200 baud. The TOIM3232 expects to receive data from the serial port in 8 data bits, no parity, 1 stop bit format.

Once the jumper above has been set to configure COM2 for infrared communication, the TOIM3232 must be programmed with the baud rate at which the serial port will be operating. To do this, perform the following steps:

1) Reset the TOIM3232 by asserting and then de-asserting the DTR signal. After the signal has been de-asserted, wait for at least  $7\mu$ s.

March 1999 24 Version 1.0

- 2) Put the TOIM3232 into programming mode by asserting the RTS signal. After the signal has been asserted, wait for at least  $7\mu$ s.

- 3) Send the control byte to the TOIM3232. The serial port must be configured for 9600 baud as this is the rate at which the TOIM3232 operates after being reset. Sending 0x1Z will change the baud rate of the TOIM3232 to the desired rate (where Z=0 for 115,200 baud, Z=1 for 57,600 baud, Z=2 for 38,400 baud...see the TOIM3232 data sheet for a complete list). After the control byte has been sent, wait for at least  $1\mu s$ .

- 4) Take the TOIM3232 out of programming mode by de-asserting the RTS signal.

All further data sent to and received from the TOIM3232 will be at the baud rate specified in step 3. The serial port must therefore be reconfigured for the required baud rate.

After the TOIM3232 has been configured with the correct baud rate, from a software perspective the IrDA port can be treated as if it were a standard COM port.

#### 4.11.4 Parallel Port (LPT)

The parallel port used in this design is a standard PC parallel port with its address space mapped as follows:

**Table 41: LPT Register Definitions**

|        |             | 1 110818101 2 011111010118          |

|--------|-------------|-------------------------------------|

| Name   | Address     | Description                         |

| PDOUT  | 0x0301:09E0 | Parallel Data Output/Input Register |

| PSTAT  | 0x0301:09E4 | Parallel Status Register            |

| PCON   | 0x0301:09E8 | Parallel Control Register           |

| PEPPA  | 0x0301:09EC | Parallel EPP address Port           |

| PEPPD0 | 0x0301:09F0 | Parallel EPP mode data port 0       |

| PEPPD1 | 0x0301:09F4 | Parallel EPP mode data port 1       |

| PEPPD2 | 0x0301:09F8 | Parallel EPP mode data port 2       |

| PEPPD3 | 0x0301:09FC | Parallel EPP mode data port 3       |

In addition to the above registers, the LPT port uses interrupt request 2 on the CL-PS7500FE.

This port is capable of supporting normal, ECP, EPP and PS2 type operation.

#### **4.12** CS8900A Ethernet (10BASE-T)

The Ethernet controller on the development board is a Cirrus Logic CS8900A 10BASE-T controller. The device has an ISA compatible interface, and most of the capability of the interface has been implemented on this design. Notably, the device supports an ISA style I/O mapped set of registers and DMA capability. Both of these interfaces are available on the development board.