### **TPS54610**

SLVS598

# FET内蔵 (SWIFT<sup>TM</sup>)、3V~6V入力、6A出力、 同期整流式バックPWMスイッチャ

#### 特 长

- 30mΩ、12AピークのMOSFETスイッチ内蔵により 6A連続ソース/シンク出力電流で高効率を実現

- 1.0%の精度で出力電圧を最低0.9Vまで調整可能

- 広いPWM周波数範囲 固定350kHz、550kHzまたは可変280kHz~700kHz

- ▼ 700kHzまで同期可能

- ピーク電流制限およびサーマル・シャットダウン 機能

- 集積化によるボード面積と部品点数の削減

- SWIFT関連ドキュメント、アプリケーション・ノー ト、設計ソフトウェア:www.ti.com/swift

### アプリケーション

- 低電圧、高密度の分散型電源システム

- 高性能DSP、FPGA、ASIC、マイクロプロセッサ 用ポイント・オブ・ロード (POL) レギュレーション

- ブロードバンド、ネットワーキング、光通信イン フラストラクチャ

- ポータブル・コンピュータ、ノート・パソコン

#### 概 要

TPS54610は、DC/DCレギュレータであるSWIFT<sup>TM</sup>ファミ リーを構成する、低入力電圧、大電流出力の同期整流式バック PWMコンバータで、必要とされる能動部品を全て内蔵してい ます。他の特長としては、出力フィルタのL、C部品を選択す る際に最大の性能と柔軟性を与える高性能な電圧誤差増幅器、 入力電圧が3Vに達するまで起動を抑える低電圧ロックアウト 回路、突入電流を制限する内部または外部で設定されるスロー スタート回路、およびプロセッサ/ロジックのリセットや、電 源シーケンシングに有用なパワーグッド出力などがあります。

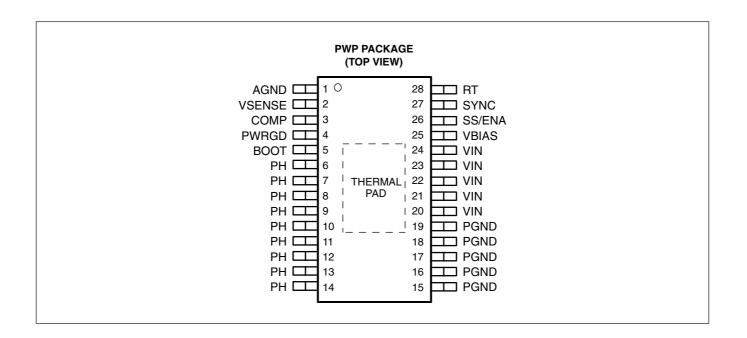

TPS54610は、熱特性を改善した28ピンのTSSOP (PWP) Power PAD<sup>TM</sup>パッケージで供給されており、大型のヒートシン クは不要です。TIは評価モジュールとSWIFT<sup>TM</sup>デザイナー・ソ フトウェア・ツールを提供しており、装置の短期間の開発サイ クルにかなうよう高性能な電源設計が迅速に行われることを支 援しています。

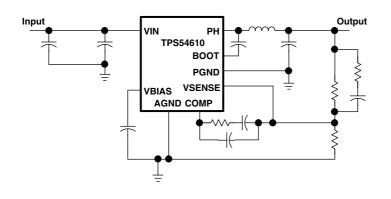

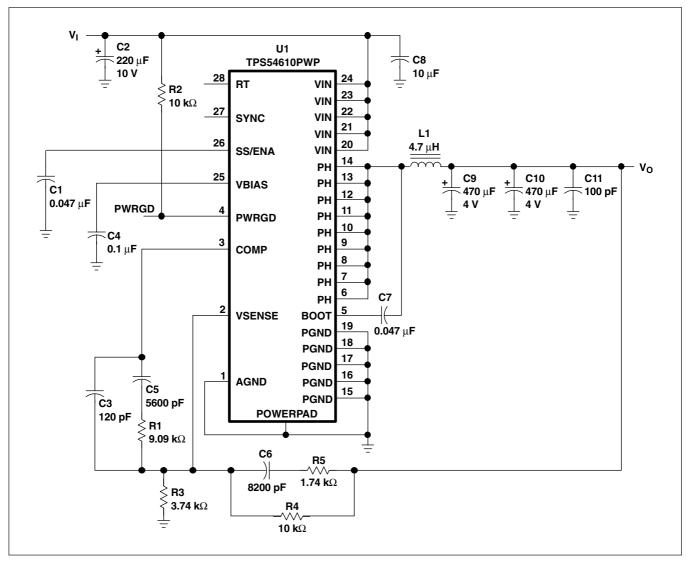

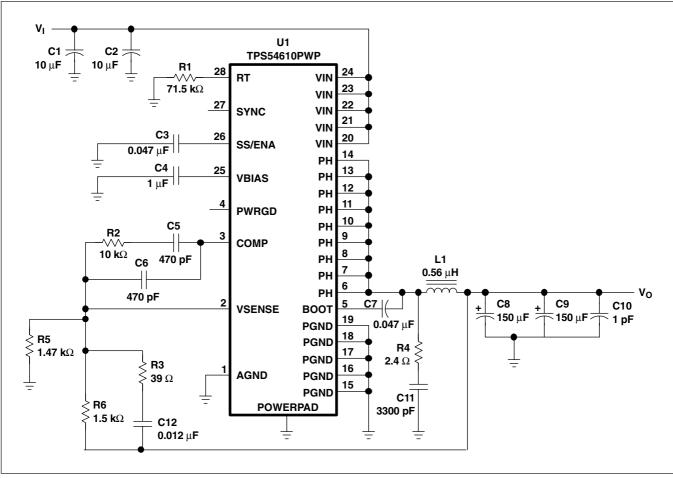

### 回路概略図

SWIFT, PowerPAD, SpActおよびBurr-Brownは、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料 を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわ らず、更新以前の情報に基づいて発生した問題や障害等につきましては如 何なる責任も負いません。

### 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

#### ORDERING INFORMATION

| T <sub>A</sub> | OUTPUT VOLTAGE          | PACKAGE <sup>(1)(2)</sup> | PART NUMBER |  |

|----------------|-------------------------|---------------------------|-------------|--|

| 40°C to 85°C   | Adjustable down to 0.9V | Plastic HTSSOP (PWP)      | TPS54610PWP |  |

- (1) PWPパッケージはテープ/リールでも供給できます。デバイス・タイプの末尾にRを付けてください (すなわち、TPS54610PWPR)。PowerPADの図面およびレイアウト情報についてはこのデータシートの「アプリケーション情報」の節を参照してください。

- (2) 最新のパッケージおよびご発注情報については、このドキュメントの巻末にある「付録:パッケージ・オプション」を参照するか、またはTIのWebサイト (www.ti.com) をご覧ください。

### 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

|                  |                                                             |                    | TPS54610           |

|------------------|-------------------------------------------------------------|--------------------|--------------------|

|                  |                                                             | VIN, SS/ENA, SYNC  | -0.3V to 7V        |

|                  |                                                             | RT                 | -0.3V to 6V        |

| VI               | Input voltage range                                         | VSENSE             | -0.3V to 4V        |

|                  |                                                             | BOOT               | -0.3V to 17V       |

|                  |                                                             | VBIAS, COMP, PWRGD | -0.3V to 7V        |

| V <sub>O</sub>   | Output voltage range                                        | PH                 | -0.6V to 10V       |

|                  | _                                                           | PH                 | Internally Limited |

| Io               | Source current                                              | COMP, VBIAS        | 6mA                |

|                  |                                                             | PH                 | 12A                |

| I <sub>S</sub>   | Sink current                                                | COMP               | 6mA                |

|                  |                                                             | SS/ENA, PWRGD      | 10mA               |

|                  | Voltage differential                                        | AGND to PGND       | ±0.3V              |

| T <sub>J</sub>   | Operating virtual junction temperature range                |                    | -40°C to 125°C     |

| T <sub>stg</sub> | Storage temperature                                         |                    | −65°C to 150°C     |

|                  | Lead temperature 1,6mm (1/16 inch) from case for 10 seconds |                    | 300°C              |

<sup>(1)</sup> 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 推奨動作条件

|                                                | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-----|-----|-----|------|

| Input voltage, V <sub>I</sub>                  | 3   |     | 6   | V    |

| Operating junction temperature, T <sub>J</sub> | -40 |     | 125 | °C   |

### 定格消費電力(1)(2)

| PACKAGE                | THERMAL IMPEDANCE JUNCTION-TO-AMBIENT | T <sub>A</sub> = 25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 28 Pin PWP with solder | 18.2°C/W                              | 5.49W (3)                             | 3.02W                                 | 2.20W                                 |

- (1) PWPパッケージの詳細な情報についてはTIテクニカル・ブリーフ文献番号SLMA002を参照してください。

- (2) テスト・ボードの条件は以下の通りです。

- a. サイズ:3インチ×3インチ、4層、厚さ0.062インチ

- b. PCBの上面に重量1.5オンスの銅配線

- c. PCBの底面に重量1.5オンスの銅のグランド・プレーン

- d. 内部の2層に重量0.5オンスの銅のグランド・プレーン

- e. サーマル・ビアは12個 (このデータシートのアプリケーション情報の"推奨ランド・パターン"を参照してください)

- (3) 最大消費電力は過電流保護により制限されることがあります。

### 定格消費電力 (続き)

| THERMAL IMPEDANCE PACKAGE JUNCTION-TO-AMBIENT |          | T <sub>A</sub> = 25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|-----------------------------------------------|----------|---------------------------------------|---------------------------------------|---------------------------------------|

| 28 Pin PWP without solder                     | 40.5°C/W | 2.48W                                 | 1.36W                                 | 0.99W                                 |

### 電気的特性

動作温度範囲内 (特に記述のない限り)

|                  | PARAMETER                                                     | TEST CONDITIONS                                                                              | MIN                      | TYP   | MAX   | UNIT  |

|------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------|-------|-------|-------|

| SUP              | PLY VOLTAGE, VIN                                              |                                                                                              | •                        |       |       |       |

|                  | Input voltage range, VIN                                      |                                                                                              | 3                        |       | 6     | V     |

|                  |                                                               | $f_{\rm S} = 350 {\rm kHz},  {\rm SYNC} \le 0.8 {\rm V},  {\rm RT}  {\rm open},$ PH pin open | 11                       |       | 15.8  |       |

| $I_{(Q)}$        | Quiescent current                                             | $f_{S}$ = 550kHz, SYNC $\geq$ 2.5V, RT open, PH pin open                                     | 16                       |       | 23.5  | mA    |

|                  |                                                               | Shutdown, SS/ENA = 0V                                                                        |                          | 1     | 1.4   |       |

| UND              | ER VOLTAGE LOCK OUT                                           |                                                                                              |                          |       |       |       |

|                  | Start threshold voltage, UVLO                                 |                                                                                              |                          | 2.95  | 3.0   | V     |

|                  | Stop threshold voltage, UVLO                                  |                                                                                              | 2.70                     | 2.80  |       | V     |

|                  | Hysteresis voltage, UVLO                                      |                                                                                              | 0.14                     | 0.16  |       | V     |

|                  | Rising and falling edge deglitch, UVLO <sup>(1)</sup>         |                                                                                              |                          | 2.5   |       | μs    |

| BIAS             | VOLTAGE                                                       |                                                                                              |                          |       |       |       |

|                  | Output voltage, VBIAS                                         | I <sub>(VBIAS)</sub> = 0                                                                     | 2.70                     | 2.80  | 2.90  | V     |

|                  | Output current, VBIAS <sup>(2)</sup>                          |                                                                                              |                          |       | 100   | μA    |

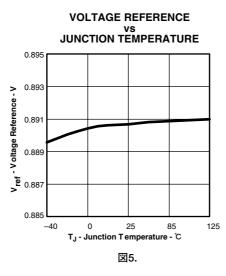

| сим              | ULATIVE REFERENCE                                             |                                                                                              | •                        |       |       |       |

| V <sub>ref</sub> | Accuracy                                                      |                                                                                              | 0.882                    | 0.891 | 0.900 | V     |

|                  | ULATION                                                       |                                                                                              |                          |       |       |       |

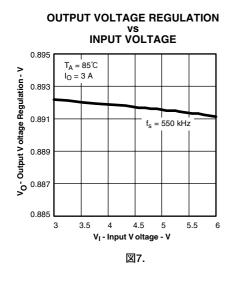

|                  | Line regulation <sup>(2)(3)</sup>                             | $I_L = 3A$ , $f_S = 350$ kHz, $T_J = 85$ °C                                                  |                          | 0.04  |       | 0/ /\ |

|                  |                                                               | I <sub>L</sub> = 3A, f <sub>S</sub> = 550kHz, T <sub>J</sub> = 85°C                          |                          |       | 0.04  | %/V   |

|                  | (1)(2)                                                        | $I_L = 0A \text{ to } 6A, f_S = 350 \text{kHz}, T_J = 85^{\circ}\text{C}$                    |                          |       | 0.03  | 0//4  |

|                  | Load regulation <sup>(1)(3)</sup>                             | I <sub>L</sub> = 0A to 6A, f <sub>s</sub> = 550kHz, T <sub>J</sub> = 85°C                    | $T_{J} = 85^{\circ}C$ 0. |       | 0.03  | %/A   |

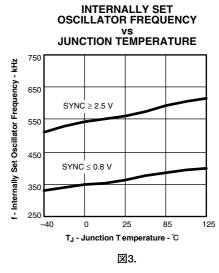

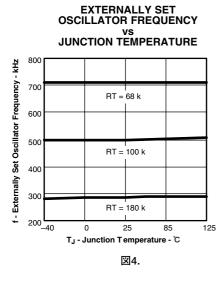

| osci             | ILLATOR                                                       | , , , , ,                                                                                    |                          |       |       |       |

|                  |                                                               | SYNC ≤ 0.8V, RT open                                                                         | 280                      | 350   | 420   |       |

|                  | Internally set-free running frequency                         | SYNC ≥ 2.5V, RT open                                                                         | 440                      | 550   | 660   | kHz   |

|                  |                                                               | RT = $180k\Omega$ (1% resistor to AGND) <sup>(1)</sup>                                       | 252                      | 280   | 308   |       |

|                  | Externally set-free running frequency range                   | RT = 100kΩ (1% resistor to AGND)                                                             | 460                      | 500   | 540   | kHz   |

|                  |                                                               | RT = $68k\Omega$ (1% resistor to AGND) <sup>(1)</sup>                                        | 663 700                  |       | 762   |       |

|                  | High level threshold, SYNC                                    |                                                                                              | 2.5                      |       |       | V     |

|                  | Low level threshold, SYNC                                     |                                                                                              |                          |       | 0.8   | V     |

|                  | Pulse duration, external synchronization, SYNC <sup>(1)</sup> |                                                                                              | 50                       |       |       | ns    |

|                  | Frequency range, SYNC <sup>(1)</sup>                          |                                                                                              | 330                      |       | 700   | kHz   |

|                  | Ramp valley <sup>(1)</sup>                                    |                                                                                              |                          | 0.75  |       | V     |

|                  | Ramp amplitude (peak-to-peak) <sup>(1)</sup>                  |                                                                                              |                          | 1     |       | V     |

|                  | Minimum controllable on time <sup>(1)</sup>                   |                                                                                              |                          |       | 200   | ns    |

|                  | Maximum duty cycle                                            |                                                                                              | 90%                      |       |       |       |

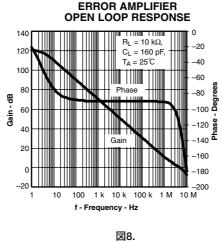

| ERR              | OR AMPLIFIER                                                  |                                                                                              |                          |       |       |       |

|                  | Error amplifier open loop voltage gain                        | 1kΩ COMP to AGND <sup>(1)</sup>                                                              | 90                       | 110   |       | dB    |

|                  | Error amplifier unity gain bandwidth                          | Parallel 10k $\Omega$ , 160pF COMP to AGND <sup>(1)</sup>                                    | 3                        | 5     |       | MHz   |

- (1) 設計で規定されています。 (2) 抵抗性静負荷のみの場合です。 (3) 図10の回路での規定です。

### 電気的特性 (続き)

動作温度範囲内(特に記述のない限り)

| PARAMETER                                       | TEST CONDITIONS                        | MIN | TYP | MAX   | UNIT |

|-------------------------------------------------|----------------------------------------|-----|-----|-------|------|

| Error amplifier common mode input voltage range | Powered by internal LDO <sup>(1)</sup> | 0   |     | VBIAS | ٧    |

| Input bias current, VSENSE                      | VSENSE = V <sub>ref</sub>              |     | 60  | 250   | nA   |

| Output voltage slew rate (symmetric), COMP      |                                        | 1   | 1.4 |       | V/µs |

### 電気的特性 (続き)

動作温度範囲内(特に記述のない限り)

| PARAMETER                                                                                 | TEST CONDITIONS                                   | MIN  | TYP  | MAX  | UNIT              |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|------|-------------------|--|

| PWM COMPARATOR                                                                            |                                                   | •    |      |      |                   |  |

| PWM comparator propagation delay time,PWM comparator input to PH pin (excluding deadtime) | 10-mV overdrive <sup>(4)</sup>                    |      | 70   | 85   | ns                |  |

| SLOW-START/ENABLE                                                                         |                                                   |      |      |      |                   |  |

| Enable threshold voltage, SS/ENA                                                          |                                                   | 0.82 | 1.20 | 1.40 | V                 |  |

| Enable hysteresis voltage, SS/ENA                                                         |                                                   |      | 0.03 |      | V                 |  |

| Falling edge deglitch, SS/ENA <sup>(4)</sup>                                              |                                                   |      | 2.5  |      | μs                |  |

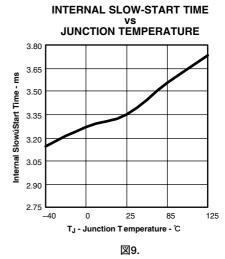

| Internal slow-start time                                                                  |                                                   | 2.6  | 3.35 | 4.1  | ms                |  |

| Charge current, SS/ENA                                                                    | SS/ENA = 0V                                       | 3    | 5    | 8    | μΑ                |  |

| Discharge current, SS/ENA                                                                 | SS/ENA = 1.2V, V <sub>I</sub> = 2.7V              | 2    | 2.3  | 4    | mA                |  |

| POWER GOOD                                                                                |                                                   |      |      |      |                   |  |

| Power good threshold voltage                                                              | VSENSE falling                                    |      | 90   |      | %V <sub>ref</sub> |  |

| Power good hysteresis voltage <sup>(4)</sup>                                              |                                                   |      | 3    |      | %V <sub>ref</sub> |  |

| Power good falling edge deglitch <sup>(4)</sup>                                           |                                                   |      | 35   |      | μs                |  |

| Output saturation voltage, PWRGD                                                          | $I_{(sink)} = 2.5mA$                              |      | 0.18 | 0.3  | V                 |  |

| Leakage current, PWRGD                                                                    | $V_{I} = 5.5V$                                    |      |      | 1    | μΑ                |  |

| CURRENT LIMIT                                                                             |                                                   |      |      |      |                   |  |

| Current limit trip point                                                                  | V <sub>I</sub> = 3V Output shorted <sup>(4)</sup> | 7.2  | 10   |      | A                 |  |

| Ourient with trip point                                                                   | V <sub>I</sub> = 6V Output shorted <sup>(4)</sup> | 10   | 12   |      | ^                 |  |

| Current limit leading edge blanking time <sup>(4)</sup>                                   |                                                   |      | 100  |      | ns                |  |

| Current limit total response time <sup>(4)</sup>                                          |                                                   |      | 200  |      | ns                |  |

| THERMAL SHUTDOWN                                                                          |                                                   |      |      |      |                   |  |

| Thermal shutdown trip point <sup>(4)</sup>                                                |                                                   | 135  | 150  | 165  | °C                |  |

| Thermal shutdown hysteresis <sup>(4)</sup>                                                |                                                   |      | 10   |      | °C                |  |

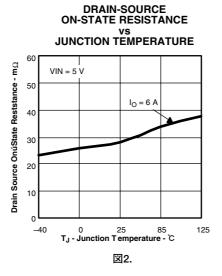

| OUTPUT POWER MOSFETS                                                                      |                                                   |      |      |      |                   |  |

| r <sub>DS(on)</sub> Power MOSFET switches                                                 | $V_I = 6V^{(5)}$                                  |      | 26   | 47   | mΩ                |  |

| 1D2(00) 1 2 10 10 01 E1 3 WIGHOS                                                          | $V_1 = 3V^{(5)}$                                  |      | 36   | 65   | 7 ms2             |  |

<sup>- (4)</sup> 設計で規定されています。 (5) 一対のMOSFETのうちローサイド側のオン抵抗はテストで、ハイサイド側のオン抵抗は設計で規定されています。

### ピン機能

| TERMINAL<br>端子名 番号 |       | 機能                                                                                                                       |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------|

| AGND               | 1     | アナログ・グランド。補償ネットワーク/出力デバイダ、スロースタート・キャパシタ、VBIASキャパシタ、RT抵抗、SYNCピンのリターン。PowerPADは、AGNDと接続してください。                             |

| BOOT               | 5     | ブートストラップ出力。ハイサイドFETのフローティング・ドライバ回路用に、0.022μF~0.1μFのTGESRキャパシタが、BOOT端子からPHに接続されます。                                        |

| COMP               | 3     | 誤差増幅器出力。COMPからVSENSEに対して周波数補償ネットワークが接続されます。                                                                              |

| PGND               | 15-19 | パワー・グランド。ローサイド・ドライバとパワーMOSFETの大電流リターン端子。PGNDは入出力電源リターンに接続されます。<br>AGNDとの接続は一点接続が推奨されます。                                  |

| PH                 | 6-14  | フェーズ出力。ハイサイド/ローサイドFETとインダクタとの接続点。                                                                                        |

| PWRGD              | 4     | パワーグット・オープンドレイン出力。VSENSE電圧がVREFの90%以上の場合に"H"、その範囲外の場合に"L"となります。<br>ただし、SS/ENAが"L"、または内部シャットダウン信号がアクティブのときには、出力は"L"になります。 |

| RT                 | 28    | 周波数設定用抵抗接続入力。RTとAGND間に抵抗を接続することで、発振周波数が設定されます。SYNCピンを使用する場合は、周波<br>数のRT値を外部発振器周波数と同じか、やや低く設定してください。                      |

| SS/ENA             | 26    | スロースタート/イネーブル入力/出力。デバイス動作をイネーブル/ディスエーブルするロジック入力、またはスタートアップ時間を外<br>部設定するキャパシタ入力に使用される兼用ピンです。                              |

| SYNC               | 27    | 同期入力。外部発振器に同期するためのロジック入力、または2つの内部設定周波数からいずれかを選択するために使用する兼用ピン<br>です。外部信号への同期に使用する場合は、RTピンに抵抗を接続する必要があります。                 |

| VBIAS              | 25    | 内部バイアス・レギュレータ出力。このレギュレータ出力電圧は内部回路用電源として使用され、高品質/低ESRの0.1μF〜1μFセラミック・キャパシタでVBIASとAGND間をバイパスしてください。                        |

| VIN                | 20-24 | パワーMOSFETスイッチと内部バイアス・レギュレータの入力電源。高品質/低ESRの10μFセラミック・キャパシタで、デバイスの出来<br>るだけ近くでVINとPGND間をバイパスしてください。                        |

| VSENSE             | 2     | 誤差増幅器反転入力端子。この端子と出力電圧間に、補償ネットワーク/出力デバイダが接続されます。                                                                          |

### 他の6A SWIFT<sup>TM</sup>デバイス(SLVS397およびSLVS400を参照)

| DEVICE   | OUTPUT VOLTAGE | DEVICE   | OUTPUT VOLTAGE | DEVICE   | OUTPUT VOLTAGE  |

|----------|----------------|----------|----------------|----------|-----------------|

| TPS54611 | 0.9V           | TPS54614 | 1.8V           | TPS54672 | DDR Memory/Adj. |

| TPS54612 | 1.2V           | TPS54615 | 2.5V           | TPS54673 | Pre-bias/Adj.   |

| TPS54613 | 1.5V           | TPS54616 | 3.3V           | TPS54680 | Sequencing/Adj. |

### 関連DC/DC製品

- TPS40000—DC/DCコントローラ

- TPS759xx-7.5A低ドロップアウト・レギュレータ

- PT6440シリーズ―6Aプラグイン・モジュール

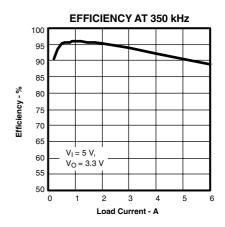

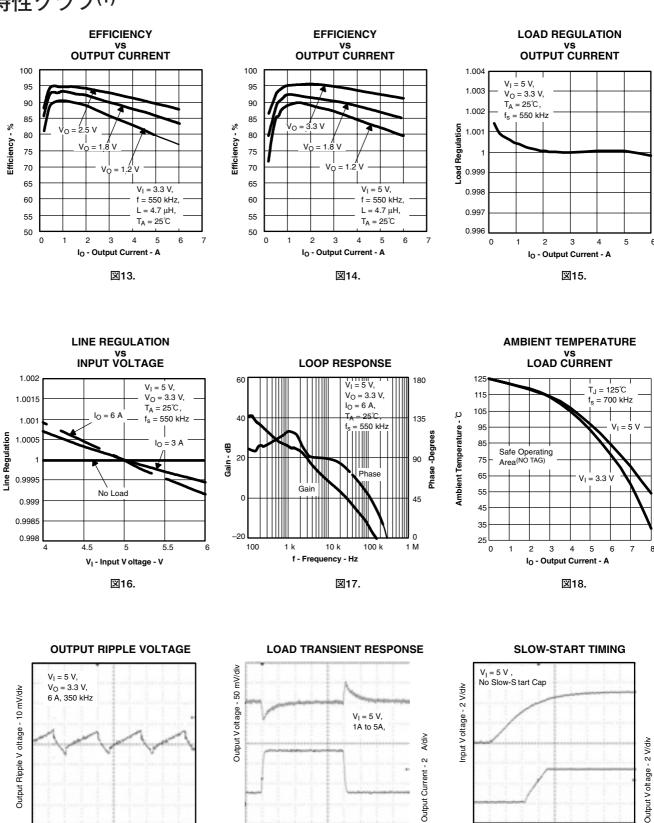

## 代表的特性

DRAIN-SOURCE ON-STATE RESISTANCE VS JUNCTION TEMPERATURE 60 C VIN = 3.3 V I<sub>O</sub> = 6 Å Drain Source OnúState Reststance 50 40 30 20 10 0 0 25 85 T<sub>J</sub> - Junction Temperature - °C -40 図1.

## アプリケーション情報

図10にTPS54610の代表的なアプリケーション回路図を示します。TPS54610 (U1) は標準出力電圧3.3V時6A以上の出力電流を供給することができます。適切な熱特性を実現するには、

ICパッケージの底面にむき出しの熱対策用のPowerPADをプリント基板にはんだ付けしなければなりません。

図10. アプリケーション回路

### 部品の選択

この設計例で使用された部品の値は、SWIFTデザイナー・ソフトウェア・ツールを使用して選択されています。SWIFTデザイナーは、TPS54610を使用してDC/DCコンバータを開発するための完全な設計環境を提供します。

### 入力フィルタ

回路への入力は標準で5VDCです。入力フィルタC2は、220μFのPOSCAPキャパシタで、最大許容リップル電流は3Aです。C8は、入力電源からTPS54610への高周波結合が起こらないようにするためのもので、できるだけデバイスの近くに配置しなければなりません。リップル電流はC2とC8に運ばれ、PGNDへの帰還パスにより電流が出力キャパシタC9、C10に循環するのを回避しなければなりません。

### フィードバック回路

抵抗デバイダ回路R3とR4により回路の出力電圧が3.3Vに設定されています。R4およびR1、R5、C3、C5、C6は回路のループ補償ネットワークを形成しています。この設計ではタイプ3のトポロジが使用されています。

### 動作周波数

アプリケーション回路で、RTおよびSYNC端子を開放にすると350kHz動作が選択されます。180k $\Omega$ ~68k $\Omega$ の抵抗をRT (28ピン)とアナログ·グランド間に接続するとスイッチング周波数を280kHz~700kHzに設定することができます。RTピンに接続する抵抗を計算するには以下の式を使用します。

$$R = \frac{500 \text{kHz}}{\text{Switching Frequency}} \times 100 \text{ [k}\Omega\text{]}$$

(1)

### 出力フィルタ

出力フィルタは $4.7\mu$ Hのインダクタ1個と $470\mu$ Fのキャパシタ2個で構成されています。インダクタは低DC抵抗 ( $12m\Omega$ )タイプのCoiltronics社型番UP3B-4R7です。キャパシタは4VのPOSCAPタイプで、最大ESRは $0.040\Omega$ です。フィードバック・ループは単一利得周波数が約25kHzとなるよう補償されています。

### PCBレイアウト

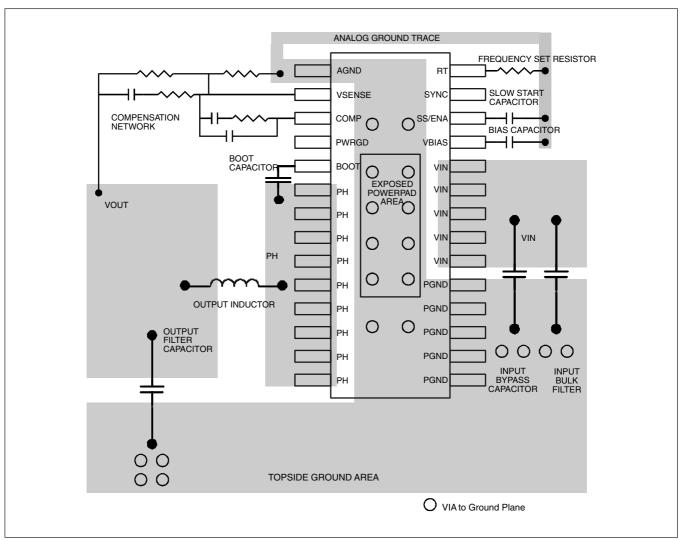

図11に、TPS54610のPCBレイアウトに関する一般的なガイドラインを示します。

すべてのVINピンは、プリント基板 (PCB) 上で同じ領域に接続し、低ESRのセラミック・バイパス・キャパシタを使用してバイパスします。バイパス・キャパシタ接続、VINピン、およびTPS54610のグランド・ピンによって形成されるループ領域は最小限に抑えるよう注意が必要です。推奨される最小のバイパス容量は、X5RまたはX7R特性の10μFのセラミック・キャパシタであり、VINピンおよびPGNDピンにできる限り近づけて配置するのが最適です。

TPS54610には内部グランドが2つあります(アナログとパ ワー)。TPS54610の内部で、アナログ·グランドはノイズに敏 感な信号全てに結びついており、一方、パワー・グランドはノ イズの大きい電源信号に結びついています。この2つのグラン ド間に入るノイズが、特に大出力電流時にTPS54610の性能を低 下させてしまいます。また一方、アナログ・グランド・プレーン 上のグランド・ノイズもコントロールおよびバイアス信号の一 部に問題を生じさせます。これらの理由により、アナログ・グ ランドとパワー・グランドのパターンをそれぞれ分離すること を推奨します。IC直下の最上層には、PowerPADへの接続用の 露出した領域を持った、グランド領域を設けます。このグラン ド領域は、ビアを使用して任意の内層グランド・プレーンに接続 してください。入力および出力フィルタ・キャパシタのグラン ド側にも、追加のビアを使用します。AGNDおよびPGNDピン は、PCBのグランドに接続します。これは、図に示すように、 各ピンをデバイスの下のグランド領域に接続することで行いま す。パワー・グランドのプレーンに直接接続する部品は、入力 キャパシタ、出力キャパシタ、入力電圧デカップリング・キャ パシタ、TPS54610のPGND端子です。アナログ·グランド信号 パスには、別の広いパターンを使用してください。このアナロ グ·グランドは、電圧設定点デバイダ、タイミング抵抗RT、ス ロースタート・キャパシタ、およびバイパス・キャパシタのグ ランド用に使用します。このパターンはAGND (ピン1) に直接 接続してください。

PHピンはすべて同じ領域に接続し、出力インダクタに接続します。PH接続はスイッチング・ノードであるため、インダクタはPHピンの近くに配置します。過度の容量性カップリングを避けるためにPCB導体の面積はできるだけ小さくしてください。図に示すように、フェーズ (PH) ノードとBOOTピンの間にはブート・キャパシタを接続します。ブート・キャパシタはICに近づけて配置し、パターンはできるだけ短くしてください。

VOUTパターンとPGNDの間には、図に示すように出力フィルタ・キャパシタを接続します。PHピン、LOUT、COUT、およびPGNDによって形成されるループは、実用上適切な範囲でなるべく小さくすることが重要です。

VOUTパターンとVSENSEおよびCOMPピンの間に、補償部品を配置します。これらの部品は、PHパターンにあまり近づけないようにしてください。ICパッケージのサイズとデバイスのピン配置の関係で、近くに配置されるようになりますが、レイアウトのコンパクトさを維持できる範囲で、できるだけ離して配置してください。

VBIASピンとアナログ・グランドの間に、独立したアナログ・グランド・パターンを使用してバイアス・キャパシタを接続します。スロースタート・キャパシタまたはRT抵抗を使用する場合、またはSYNCピンを使用して350kHzの動作周波数を選択する場合は、それらをこのグランド・パターンに接続してください。

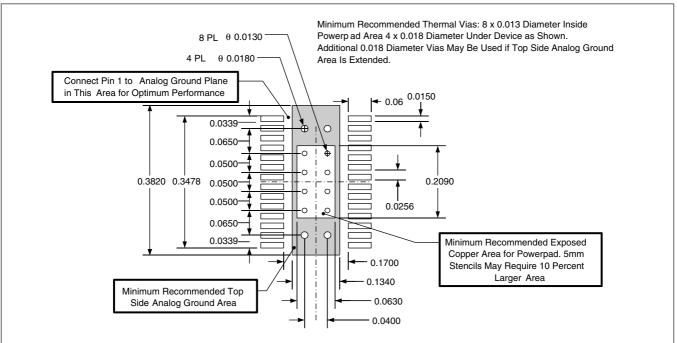

**図11.** 28ピンPWP PowerPADの推奨ランド・パターン

### 熱特性のためのレイアウトの考察

全定格負荷電流で動作を行うには、アナログ・グランドのプレーンは適切な放熱面積を備えていなければなりません。周囲の温度とエアフローにもより、強制ではありませんが、重量1オンスの銅で3インチ×3インチの大きさを推奨します。ほとんどのアプリケーションでは内部に大きな領域のグランド・プレーンをもつことができ、PowerPADはこの利用可能な最大領域に接続しなければなりません。上層または下層の追加領域も放熱の手助けとなり、6Aまたはそれ以上での動作が求められる場合には利用可能な領域はすべて使用しなければなりません。PowerPADのむき出しの領域からアナログ・グランド・プレーン

層へはビアの中でのはんだのウィッキング (ボイド) を避けるため直径0.013インチのビアを使って接続しなければなりません。PowerPAD領域に8つのビアと、デバイス・パッケージの下に設置される4つの追加ビアがなければなりません。むき出しのサーマル・パッド領域では不可能ですが、パッケージの下のビア寸法は0.018インチまで増やすことができます。熱特性を向上させるために、推奨される12個のビア以外にも、追加ビアをデバイス・パッケージの下以外の領域に置くことも必要です。

**図12.** 28ピンPWP PowerPADの推奨ランド・パターン

## 特性グラフ(1)

(1) "Safe operating area"は、定格消費電力でのテスト・ボード条件に該当します。

t - Time = 1 μs/div

図19.

t - Time = 100  $\mu$ s/div

図20.

t - Time = 2 ms/div

図21.

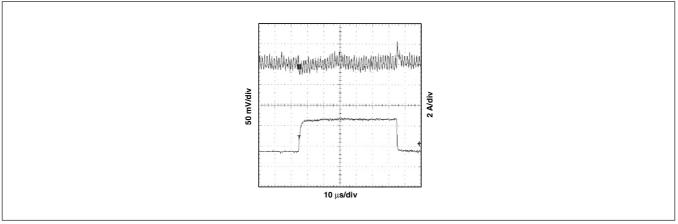

図22は、TPS54610を使用した小型高周波アプリケーションの回路図を示しています。TPS54610 (U1) は標準出力電圧1.8V 時最大6Aの出力電流を供給することができます。サイズの小さな0.56uHのインダクタを使用し、スイッチング周波数はR1により680kHzに設定されています。図22に示すように、補償ネットワークは高速の過渡応答を得るために最適化されています。

適切な熱特性を実現するには、TPS54610の下にあるPowerPADを、プリント基板にしっかりとはんだ付けしなければなりません。アプリケーション情報は、"Designing for Small-Size, High-Frequency Applications With Swift<sup>TM</sup> Family of Synchronous Buck Regulators" (TI文献番号SLVA107) に記載されています。

図22. 小型高周波数設計

図23. 過渡応答、1.5A→4.5Aステップ

### 詳細説明

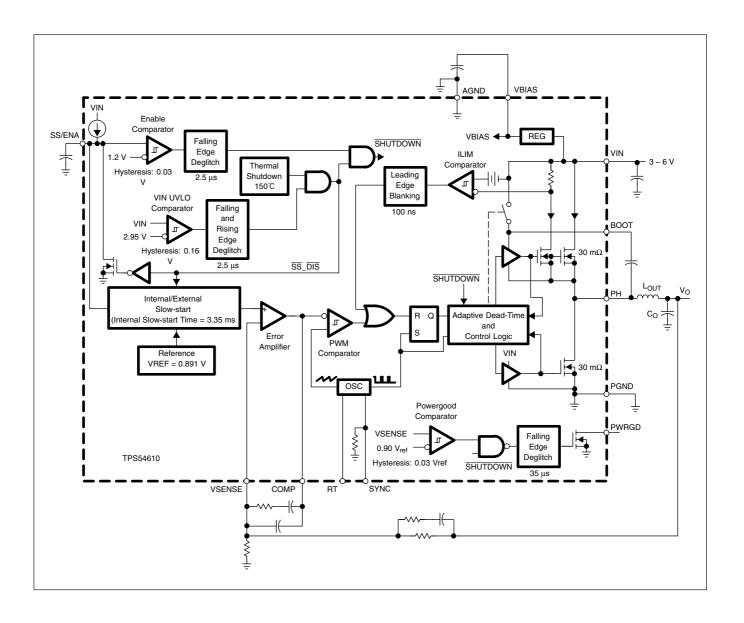

### 低電圧ロックアウト (UVLO)

TPS54610には入力電圧が (VIN) が不足している場合にデバイスをディスエーブルにしておく低電圧ロックアウト回路が内蔵されています。電源の立ち上がり時、内部回路はVINが標準のUVLOスレッシュホールド電圧である2.95Vを超えるまでインアクティブに保持されます。UVLOスタート・スレッシュホールド電圧に達するとデバイスの起動が始まります。デバイスはVINが標準のUVLOストップ・スレッシュホールド電圧である2.8V以下に低下するまで動作します。VINのノイズによりデバイスが停止してしまう可能性はUVLOコンパレータのヒステリシスおよび2.5μsの立ち上がり/立ち下がりエッジ・デグリッチ回路により低く抑えられています。

### スロースタート/イネーブル (SS/ENA)

スロースタート/イネーブル・ピンには、2つの機能があります。1つはイネーブル (シャットダウン) 制御であり、電圧が約1.2Vのスタート・スレッシュホールド電圧を超えるまで、デバイスをオンにしないようにします。SS/ENAがイネーブル・スレッシュホールドを超えると、デバイスのスタートアップが開始されます。誤差増幅器に供給される基準電圧は、3.35msの間に0Vから0.891Vまで直線的に上昇します。同様に、コンバータ出力電圧は、約3.35msでレギュレーションに達します。電圧ヒステリシスおよび2.5μsの立ち下がりエッジのデグリッチ回路により、ノイズによってイネーブルがトリガされるのを防止しています。

SS/ENAピンのもう1つの機能として、SS/ENAとAGNDの間に低容量キャパシタを接続し、スロースタート時間を外部から延長することができます。

SS/ENAピンにキャパシタを追加すると、スタートアップに関して2つの影響があります。まず、SS/ENAピンがリリースされてから出力がスタートアップするまでの間に、遅延が生じます。この遅延は、スロースタート・キャパシタの値に比例し、SS/ENAピンがイネーブル・スレッシュホールドに達するまで続きます。スタートアップ遅延時間は、次の式で概算できます。

$$t_{d} = C_{(SS)} \times \frac{1.2V}{5\mu A} \tag{2}$$

また、出力がアクティブになると、外部で設定されたスロースタート・レートが適用され、出力がスロースタート・キャパシタに比例したレートで上昇する前に、短時間、内部スロースタート・レートでの上昇が見られる場合があります。キャパシタにより設定されるスロースタート時間は、次の式で概算できます。

$$t_{(SS)} = C_{(SS)} \times \frac{0.7V}{5uA}$$

(3)

内部レートでのわずかな上昇により、実際のスロースタート時間はこの概算値より小さくなります。

### VBIASレギュレータ (VBIAS)

VBIASレギュレータは内部のアナログおよびデジタル・ブロックにジャンクション温度や入力電圧の変動にかかわらない安定した電源電圧を供給します。高品質で低ESRのセラミックのバイパス・キャパシタをVBIASピンに接続することが必要です。温度に対し特性値が安定しているため、X7RまたはX5Rクラスの特性を推奨します。バイパス・キャパシタはVBIASピンの近くに置き、AGNDに帰還させなければなりません。

VBIASに外部負荷を接続することは、内部回路がVBIASの最小電圧2.70Vを必要とすること、およびVBIASに接続する外部負荷がACまたはデジタル・スイッチング・ノイズを持ち性能を劣化させるかもしれない、という点に注意すれば可能です。VBIASピンは外付け回路への基準電圧としても有用です。

### 基準電圧

基準電圧システムは温度に対し安定なバンドギャップ回路の出力をスケーリングすることで高精度のVref信号を生成します。製造時、バンドギャップ回路とスケーリング回路は、ボルテージ・フォロワのように接続されたアンプにより誤差増幅器の出力で0.891Vが出力されるようトリミングされます。このトリミングは、スケーリング回路および誤差増幅器の回路のオフセット誤差をキャンセルするため、TPS54610での高精度のレギュレーションを可能にします。

### 発振器およびPWMランプ

発振器の周波数は、SYNCピンを静的デジタル入力として使用し、内部で350kHzまたは550kHzの固定値に設定できます。アプリケーションでそれ以外の周波数での動作が必要な場合、発振器の周波数は、RTピンとAGND間に抵抗を接続し、SYNCピンをフローティングにすることにより、280kHz~700kHzの範囲で外部から調整することができます。スイッチング周波数は以下の式で概算することができます。この式中のRはRTピンからAGNDに接続される抵抗です。

Switching Frequency =

$$\frac{100k\Omega}{R}$$

× 500 [kHz] (4)

SYNCに同期信号を入力し、RTとAGNDの間に抵抗を接続することにより、330kHz~700kHzの周波数範囲でPWMランプを外部同期させることが可能です。RTとAGNDの間の抵抗値は、フリー・ランニング周波数が同期信号の80%に設定されるように選択します。次の表に、周波数選択設定を示します。

| SWITCHING<br>FREQUENCY            |                        |                                                            |

|-----------------------------------|------------------------|------------------------------------------------------------|

| 350 kHz, internally set           | Float or AGND          | Float                                                      |

| 550 kHz, internally set           | ≥2.5V                  | Float                                                      |

| Externally set 280kHz to 700kHz   | Float                  | R = $180$ k $\Omega$ to $68$ k $\Omega$                    |

| Externally synchronized frequency | Synchronization signal | R = RT value for 80% of external synchronization frequency |

### 誤差増幅器

高性能で広い帯域幅をもつ誤差増幅器により、TPS54610はほとんどのDC/DCコンバータより際立って優れています。 ユーザーは特殊なアプリケーションのニーズに適応するようLとCから成る出力フィルタ部品を広範囲に選択使用することができます。外付けの補償部品によりタイプ2または3の補償を用いることができます。

### PWMコントロール

誤差増幅器の出力、発振器、電流制限回路からの信号は PWMコントロール·ロジックで処理されます。内部ブロック図 を参照すると、このコントロール・ロジックにはPWMコンパ レータ、ORゲート、PWMラッチ、およびアダプティブ·デッ ドタイムとコントロール・ロジックのブロックの一部が含まれ ます。電流制限スレッシュホールド電圧以下の定常状態動作で は、PWMコンパレータの出力と発振器の連続パルスが交互に PWMラッチのリセットとセットを行います。PWMラッチがリ セットされると、ローサイドFETは発振器のパルス幅で設定さ れる最小期間の間オン状態のままです。この期間で、PWMラン プはその下限電圧まで急速に放電します。ランプが再充電し始 めると、ローサイドFETはオフになり、ハイサイドFETがオン になります。PWMランプ電圧が誤差増幅器の出力電圧を超え ると、PWMコンパレータはラッチをリセットするため、ハイ サイドFETがオフ、ローサイドFETはオンになります。ローサ イドFETは、発振器の次のパルスがPWMランプを放電するま でオン状態を保持します。

過渡状態では、誤差増幅器の出力はPWMランプの下限電圧以下またはPWMピーク電圧以上である可能性があります。誤差増幅器の出力が高いと、PWMラッチはリセットされず、ハイサイドFETは発振器のパルスがハイサイドFETをオフに、ローサイドFETをオンにするようコントロール・ロジックに信号を送るまでオン状態を保持します。このデバイスは出力電圧がレギュレーションの設定点に達し、VSENSEの電圧がVREFとほぼ同じ電圧に設定されるまで、その最大デューティ・サイクルで動作します。一方、誤差増幅器の出力が低いと、PWMラッチは絶えずリセットされ、ハイサイドFETはオンになりません。ローサイドFETは、VSENSE電圧がPWMコンパレータに状態を変えさせる程度に減少するまでオン状態を保持します。TPS54610は出力がレギュレーションの設定点に達するまで連続して電流をシンクすることができます。

電流制限コンパレータが100ns以上トリップしている場合、PWMラッチはPWMランプが誤差増幅器の出力を超える前にリセットされます。ハイサイドFETはオフに、ローサイドFETはオンになり、出力インダクタのエネルギーは減少し、その結果出力電流は減少します。このプロセスは電流制限コンパレータがトリップするたびに各サイクルで繰り返し行われます。

### デッドタイム・コントロールおよびMOSFETドライバ

アダプティブ・デッドタイム・コントロールにより、MOS-FETドライバのターンオン時間が能動的にコントロールされ、スイッチング過渡時シュートスルー電流が両方のNチャネル・パワーMOSFETに流れることが防止されます。ハイサイド・ドライバはローサイドFETのゲート電圧が2V以下になるまでオンになりません。一方、ローサイド・ドライバはハイサイドMOS-FETのゲート電圧が2V以下になるまでオンになりません。

ハイサイド・ドライバおよびローサイド・ドライバはパワー MOSFETのゲートを高速に駆動するため300mAのソース/シンク能力をもつよう設計されています。ローサイド・ドライバはVINから電源を供給され、一方、ハイサイド・ドライバはBOOTピンから電源が供給されます。ブートストラップ回路は外付けのBOOTキャパシタと、VINとBOOTピン間に接続された $2.5\Omega$ の内部ブートストラップ・スイッチを利用しています。この内蔵ブートストラップ・スイッチにより、駆動効率が改善し、また外付け部品点数も削減します。

### 過電流保護

ハイサイドMOSFETを流れる電流を検出し、この信号をあらかじめ設定された過電流スレッシュホールドと比較することでサイクルごとの電流制限が実行されます。ハイサイドMOSFETは電流制限のスレッシュホールドに達した後200ns以内でオフになります。100nsのリーディング・エッジ・ブランキング回路は電流制限が誤ってトリップすることを防止します。電流制限の検出は出力フィルタへの電流をソースしている場合に電流がVINからPHに流れる時にのみ起こります。電流シンクの動作時に負荷を保護することはサーマル・シャットダウンにより行なわれます。

### サーマル・シャットダウン

このデバイスはジャンクション温度が150℃を超えるとサーマル・シャットダウンによりパワーMOSFETをオフにしコントローラをディスエーブルにします。デバイスはサーマル・シャットダウンのトリップ点より10℃下がると自動的にシャットダウンが解除され、スロースタート回路のコントロールの下で起動を開始します。

サーマル・シャットダウンは過負荷の状態が数ミリ秒間続いた時保護を行います。異常状態が続いていると、デバイスは連続して以下のサイクルを繰り返します。つまり、ソフトスタート回路のコントロールにより起動し、異常状態により熱をもち、その結果サーマル・シャットダウンのトリップ点に達した時シャットダウンします。このシーケンスは異常状態が解除されるまで繰り返されます。

### パワーグッド (PWRGD)

パワーグッド回路はVSENSEが低電圧状態かどうかをモニタします。VSENSEの電圧が基準電圧より10%低くなると、PWRGDのオープン・ドレイン出力が "L" レベルになります。また、VINがUVLOスレッシュホールド電圧以下またはSS/ENAが "L" レベル、あるいはサーマル・シャットダウンが起こった場合に、PWRGDは "L" レベルになります。VINがUVLOスレッシホールド電圧以上、SS/ENAがイネーブル・スレッシュホールド電圧以上、VSENSEが $V_{ref}$ 090%より大きい場合は、PWRGDピンのオープン・ドレイン出力は "H" レベルになります。 $V_{ref}$ 03%のヒステリシス電圧と35 $\mu$ sの立ち下がりエッジのデグリッチ回路により、高周波ノイズでパワーグッド・コンパレータがトリップするのを防止しています。

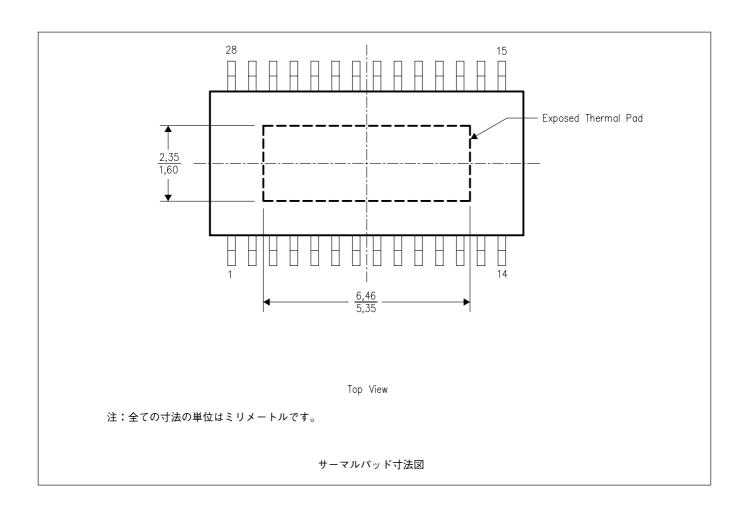

## サーマル情報

PowerPADTMパッケージには、外部のヒートシンクに直接取り付けられるむき出しのサーマルパッドがあります。このサーマルパッドを直接PCBに半田付けする場合には、PCBをヒートシンクとして使用できます。さらに、サーマルビアを使用することで、サーマルパッドを、PCB内部のグランドプレーンもしくは特別に準備されたヒートシンクエリアにも直接接続可能です。このような設計によって、ICからの熱伝導を最適化することが出来ます。

PowerPADTMパッケージについての追加情報およびその放熱能力の利用法については、テクニカル・ブリーフ "PowerPAD Thermally Enhanced Package" (TI文献番号SLMA002) およびアプリケーション・ブリーフ "PowerPAD Made Easy" (TI文献番号SLMA004) を参照してください。いずれもホームページwww.ti.comで入手できます。

サーマルパッドの寸法については、以下のようになります。

■パッケージに関しては、最新の正規英語版をご参照ください。

### パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> I | ₋ead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|-------------|---------------------------|------------------|------------------------------|

| TPS54610PWP      | ACTIVE                | HTSSOP          | PWP                | 28   | 50          | TBD                       | CU NIPDAU        | Level-1-220C-UNLIM           |

| TPS54610PWPR     | ACTIVE                | HTSSOP          | PWP                | 28   | 2000        | TBD                       | CU NIPDAU        | Level-1-220C-UNLIM           |

| TPS54610PWPRG4   | ACTIVE                | HTSSOP          | PWP                | 28   | 2000        | Green(RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

(1)マーケティング・ステータスは次のように定義されています。

**ACTIVE:**製品デバイスが新規設計用に推奨されています。

**LIFEBUY:TI**によりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW: デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

**OBSOLETE**: TIによりデバイスの生産が中止されました。

<sup>(2)</sup>エコ·プラン – 環境に配慮した製品分類プランであり、 Pb-Free (RoHS) およびGreen (RoHS & no Sb/Br) があります。 最新情報および製品内容の詳細については、

http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free" (鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Green (RoHS & no Sb/Br):TIにおける "Green" は、"Pb-Free" (RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) を ベースとした難燃材を含まない (均質な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

(3) MSL、ピーク温度 - JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じるTIの責任は、TIによって年次ベースで顧客に販売される、このドキュメント発行時点でのTI製品の合計購入価格を超えることはありません。

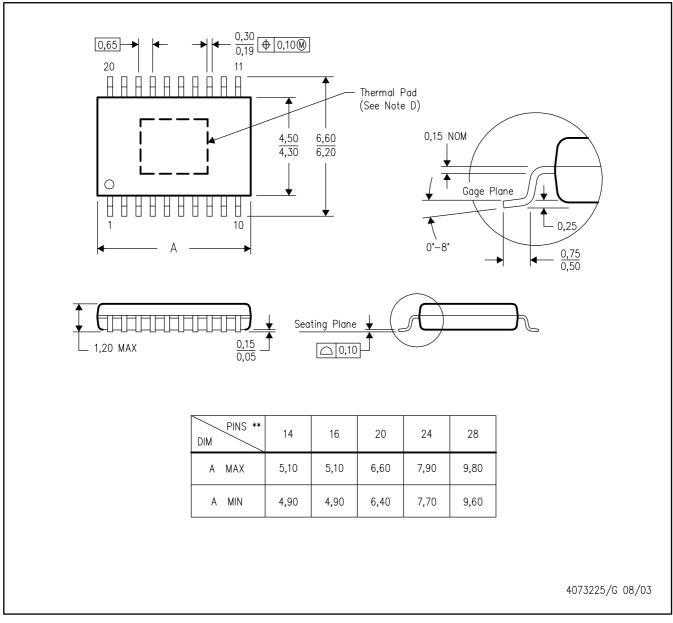

### PWP (R-PDSO-G\*\*)

### PowerPAD™ PLASTIC SMALL - OUTLINE PACKAGE

20 PIN SHOWN

注A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. 本体寸法にはバリや突起を含みません。

- D. このパッケージは、基板上のサーマルパッドに半田付けされるように設計されています。推奨基板レイアウトについては、テクニカル・ブリーフ "PowerPAD Thermally Enhanced Package" (TI文献番号SLMA002) を参照してください。

- このドキュメントはホームページwww.ti.com <http://www.ti.com>で入手できます。

- E. JEDEC MO-153に適合しています。

PowerPADは、Texas Instrumentsの登録商標です。

SLVS398E-JUNE 2001-REVISED FEBRUARY 2005

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます) 及びTexas Instruments Incorporated(TIJの親会社、以下TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、 条件その他のパラメーターと異なる、あるいは、それを超えてなされ た説明で当該TI製品もしくはサービスを再販売することは、当該 TI製品もしくはサービスに対する全ての明示的保証、及び何らか の黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為 です。TIは、そのような説明については何の義務も責任もありません。

なお、日本テキサス・インスツルメンツ株式会社半導体集積回路 製品販売用標準契約約款もご覧下さい。

http://www.tij.co.jp/jsc/docs/stdterms.htm

Copyright © 2005, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点 を遵守して下さい。

#### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装) 又は製品単品で取り扱いを行う場合は、接地された導 電性のテーブル上で(導電性マットにアースをとったも の等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる 全ての装置類は、静電気の帯電を防止する措置を施す こと。

- 前記のリストストラップ・導電性手袋・テーブル表面 及び実装装置類の接地等の静電気帯電防止措置は、常 に管理されその機能が確認されていること。

### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送 及び取り扱いを行うこと。(但し、結露しないこと。) ● 直射日光があたる状態で保管・輸送しないこと。

### 3. 防湿梱包

● 防湿梱包品は、開封後は個別推奨保管環境及び期間に 従い基板実装すること。

#### 4. 機械的衝擊

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、 衝撃を与えないこと。

#### 5. 熱衝撃

はんだ付け時は、最低限260℃以上の高温状態に、10 秒以上さらさないこと。(個別推奨条件がある時はそれ に従うこと。)

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。 (不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上