## MC145074

## **Stereo Audio Sigma-Delta Digital-to-Analog Converter** CMOS

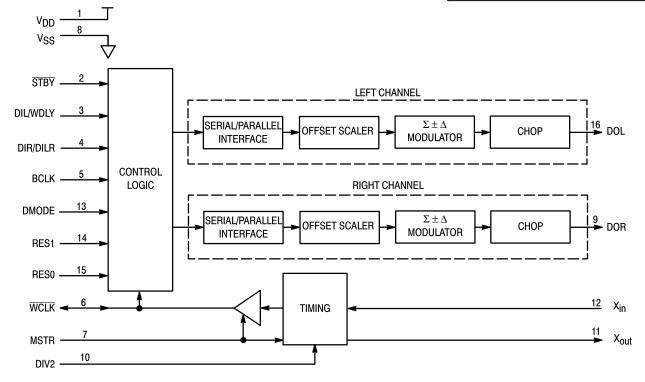

The MC145074 is a high precision, Stereo Audio Digital-to-Analog Converter that utilizes second order sigma-delta modulators with 2-tap FIR feedback architecture. The part can be used as a stand alone stereo digital modulator, or as a companion part to the MC145076 smoothing filter to achieve high quality, low cost audio performance.

- Peak S/(N+D) > 100 dB

- Single 5 V Supply Operation

- Accepts 16, 18, or 20-Bit Data Words

- Dual/Single Pin Data Input Modes

- Programmable WCLK Divider

- Operating Temperature Range: 40 to + 85°C

- Low Power Consumption: 40 mW Typical

- Companion to MC145076 Stereo Audio FIR Smoothing Filter

| PIN ASSIGNMENT    |    |                       |  |  |  |

|-------------------|----|-----------------------|--|--|--|

| V <sub>DD</sub> [ | 1● | 16 🛛 DOL              |  |  |  |

| STBY [            | 2  | 15 🛛 RES0             |  |  |  |

| dil/wdly [        | 3  | 14 🛛 RES1             |  |  |  |

| DIR/DILR [        | 4  | 13 DMODE              |  |  |  |

| BCLK [            | 5  | 12 🛛 X <sub>in</sub>  |  |  |  |

|                   | 6  | 11 🛛 x <sub>out</sub> |  |  |  |

| MSTR [            | 7  | 10 🛛 10/2             |  |  |  |

| v <sub>ss</sub> [ | 8  | 9 🛛 DOR               |  |  |  |

|                   |    |                       |  |  |  |

#### MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Symbol           | Parameter                                       | Value                                             | Unit |

|------------------|-------------------------------------------------|---------------------------------------------------|------|

| V <sub>DD</sub>  | DC Supply Voltage                               | 6.0                                               | V    |

| V <sub>in</sub>  | DC Input Voltage, Any Digital Input             | V <sub>SS</sub> – 0.5 to<br>V <sub>DD</sub> + 0.5 | V    |

| l <sub>in</sub>  | DC Input Current, per Pin                       | ±10                                               | mA   |

| T <sub>stg</sub> | Storage Temperature                             | – 55 to 150                                       | °C   |

| ΤL               | Lead Temperature, 1 mm from Case for 10 Seconds | 260                                               | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation, V<sub>in</sub> and V<sub>out</sub> should be constrained to the range VSS  $\leq$  (V<sub>in</sub> or V<sub>out</sub>)  $\leq$  VDD.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ). Unused outputs must be left open.

\* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Operation Ranges below.

#### **OPERATION RANGES** (Applicable to Guaranteed Limits)

| Symbol                             | Parameter                            | Value                                          | Unit |

|------------------------------------|--------------------------------------|------------------------------------------------|------|

| V <sub>DD</sub>                    | DC Supply Voltage, Referenced to VSS | 4.5 to 5.5                                     | V    |

| V <sub>in</sub> , V <sub>out</sub> | Digital Input/Output Voltage         | V <sub>SS</sub> – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| ۱ <sub>D</sub>                     | Input Pin Current Drain              | 1                                              | μΑ   |

| TA                                 | Operating Temperature                | – 40 to + 85                                   | °C   |

## DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to VSS, Full Temperature and Voltage Ranges per Operation Ranges table, unless otherwise indicated)

| Symbol                 | Parameter             |                                                                       | Min                        | Тур | Max                   | Unit |

|------------------------|-----------------------|-----------------------------------------------------------------------|----------------------------|-----|-----------------------|------|

| I <sub>dd</sub>        | Power Supply Current  |                                                                       | —                          | —   | 10                    | mA   |

| VIL<br>VIH             | Input Voltage         | Low Level Input<br>High Level Input                                   | —<br>V <sub>DD</sub> x 0.7 | _   | V <sub>DD</sub> x 0.3 | V    |

| V <sub>OL</sub><br>VOH | Output Voltage        | Low Level Output (Load = 0.4 mA)<br>High Level Output (Load = 0.4 mA) | —<br>V <sub>DD</sub> – 0.3 | _   | 0.3                   | V    |

| l <sub>lkg</sub>       | Input Leakage Current |                                                                       | —                          | —   | ± 10                  | μA   |

## AC ELECTRICAL CHARACTERISTICS

(Full Temperature and Voltage Ranges per Operation Ranges Table at 50 pf Loads on Outputs) (Output Current Loads =  $400 \ \mu$ A)

| Symbol                                | Parameter                                                                                                                                                                          | Figure | Guaranteed<br>Limit | Unit |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|------|

|                                       | Operating Frequency $X_{in}$ (DIV2 = 0)<br>(DIV2 = 1)                                                                                                                              |        | 18.5<br>37.0        | MHz  |

|                                       | Bit Clock Frequency                                                                                                                                                                |        | 18.5                | MHz  |

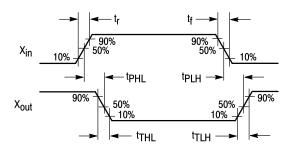

| t <sub>r</sub> , t <sub>f</sub>       | Maximum Rise and Fall Times (BCLK, WCLK)                                                                                                                                           | 2, 5   | 6                   | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> TLH  | X <sub>out</sub> L–H Propagation Delay<br>X <sub>out</sub> Rise Time                                                                                                               | 2      | 10<br>20            | ns   |

| <sup>t</sup> PHL<br><sup>t</sup> THL  | X <sub>out</sub> H–L Propagation Delay<br>X <sub>out</sub> Fall Time                                                                                                               | 2      | 10<br>20            | ns   |

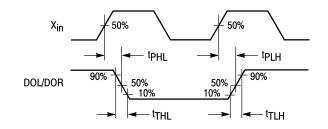

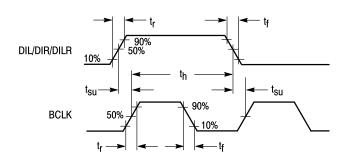

| <sup>t</sup> PLH<br><sup>t</sup> TLH  | DOL, DOR L–H Propagation Delays<br>DOL, DOR Rise Time                                                                                                                              | 3      | 15<br>7.5           | ns   |

| <sup>t</sup> PHL<br><sup>t</sup> THL  |                                                                                                                                                                                    |        | 15<br>7.5           | ns   |

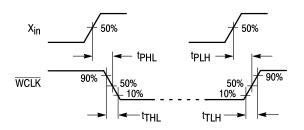

| <sup>t</sup> PLH<br><sup>t</sup> TLH  | WCLK Output L-H Propagation Delay<br>WCLK Output Rise Time                                                                                                                         | 4      | 15<br>7.5           | ns   |

| <sup>t</sup> PHL<br><sup>t</sup> THL  | WCLK Output H–L Propagation Delay<br>WCLK Output Fall Time                                                                                                                         | 4      | 15<br>7.5           | ns   |

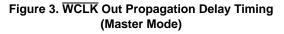

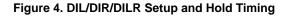

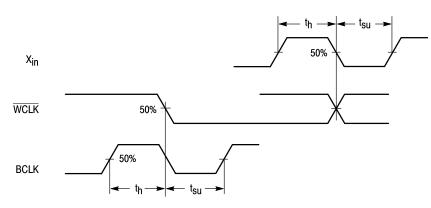

| t <sub>su</sub><br>t <sub>h</sub>     | DIR Master Program Mode Minimum Setup Time<br>DIR Master Program Mode Minimum Hold Time                                                                                            | 5      | 5<br>5              | ns   |

| t <sub>su</sub><br>t <sub>h</sub>     |                                                                                                                                                                                    |        | 5<br>5              | ns   |

| <sup>t</sup> su<br><sup>t</sup> h     |                                                                                                                                                                                    |        | 5<br>5              | ns   |

| t <sub>su</sub><br>t <sub>h</sub>     | $\frac{\overline{WCLK} \text{ Minimum Setup Time to } X_{in} \text{ (not DMODE = WDLY = 1)}}{\overline{WCLK} \text{ Minimum Hold Time to } X_{in} \text{ (not DMODE = WDLY = 1)}}$ | 6      | 5<br>5              | ns   |

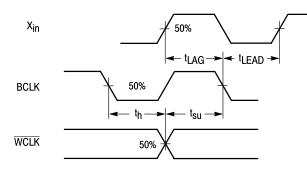

| t <sub>su</sub><br>t <sub>h</sub>     | WCLK Minimum Setup Time to BCLK (DMODE = WDLY = 1)       WCLK Minimum Hold Time to BCLK (DMODE = WDLY = 1)                                                                         | 7      | 5<br>5              | ns   |

| <sup>t</sup> LAG<br><sup>t</sup> LEAD | BCLK to $X_{in}$ (1st Edge Only) Lag Time (DMODE = WDLY = 1)<br>BCLK to $X_{in}$ (1st Edge Only) Lead Time (DMODE = WDLY = 1)                                                      | 7      | 5<br>5              | ns   |

## SWITCHING WAVEFORMS

Figure 1. Xout Propagation Delay Timing

Figure 2. DOL/DOR Propagation Delay Timing

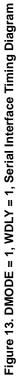

Figure 6. WCLK Timing (DMODE = 1, WDLY = 1)

| Bits | 16         | 18         | 20         |  |

|------|------------|------------|------------|--|

| OSR  | S/(N+D) dB | S/(N+D) dB | S/(N+D) dB |  |

| 128x | 90         | 90         | 90         |  |

| 192x | 94         | 98         | 99         |  |

| 256x | 95         | 103        | 105        |  |

| 384x | 96         | 107        | 113        |  |

NOTE: Values are for 0 dB input signal, 0 – 20 kHz BW, and 44.1 kHz 1x fs Sampling Rate.

Figure 7. Digital S/(N+D) Performance Levels

## VDD

## Positive Device Supply (Pin 1)

$V_{DD}$  is the positive supply, nominally + 5 volts.

## STBY

#### Active–Low Standby Input (Pin 2)

A low level on the  $\overline{\text{STBY}}$  pin will force the device into a standby state. If the device is being operated in the master mode (MSTR = 1), the WCLK internal divider can be programmed using the DIR/DILR, and BCLK pins while the STBY pin is active. When the device is in standby, the DOL and DOR pins will output a 50% duty cycle data stream that will generate a 1/2 scale analog output, when averaged through the output filter.

#### DIL/WDLY

## Left Channel Data/Word Clock Delay Input (Pin 3)

When the DMODE pin is low, this pin is the left channel (MSB first) 2's complement serial data input. When the DMODE pin is high, this pin controls the  $\overline{WCLK}$  delay. A high level on this pin will delay the  $\overline{WCLK}$  an additional clock cycle internal to the device.

#### **DIR/DILR**

# Right Channel Data/Multiplexed Left – Right Data Input (Pin 4)

When the DMODE pin is low, this pin is the right channel (MSB first) 2's complement serial data input. When the DMODE pin is high, this pin is the multiplexed left then right channel data input. If the part is being operated in the master mode (MSTR = 1), the WCLK internal divider can be programmed by clocking control word data onto this pin with the BCLK pin while the device is in the standby mode ( $\overline{\text{STBY}}$  = 0).

## BCLK

#### **Bit Clock Input (Pin 5)**

The BCLK pin provides the serial bit shift clock for the left and right channel data in all modes of operation. A rising edge on the BCLK pin shifts serial data into the device.

## WCLK

#### Word Clock Output/Input (Pin 6)

The WCLK pin is used to latch the shifted serial data word into the device. The MC145074 can accept an external word clock when in the slave mode, or can use an internally generated word clock when operating in the master mode. When DMODE is low, left and right channel data is latched into the device on the falling edge of WCLK. When DMODE is high, left channel data is latched on the rising edge of WCLK and right channel data is latched on the falling edge of WCLK with both channel inputs being input to the modulator on the next rising edge of WCLK. The internal divide ratio used to generate WCLK, as well as the rising or falling edge latching of the input data can be programmed using the DIR/ DILR and BCLK pins while the device is in the standby mode.

#### MSTR

#### Active-High Master Mode Select Input (Pin 7)

A high level on the MSTR pin will select the master mode of operation. In the master mode, the MC145074 will generate and output a word clock signal on the WCLK pin. A low level on the MSTR pin will place the MC145074 in the slave mode, and the WCLK signal must be provided by an external source. The default master mode divide rate is MODCLK/64.

## Vss

#### **Device Ground (Pin 8)**

VSS is normally connected to ground.

## DOR

## **Right Channel Data Output (Pin 9)**

DOR is the right channel modulator data output.

## DIV2

#### Master Clock Divide Control Input (Pin 10)

DIV2 is the X<sub>in</sub> divide by two control pin. When cleared, the X<sub>in</sub> pin directly provides the modulator clock (MODCLK), and the data output bit streams are not chopped. When this pin is set, the X<sub>in</sub> clock is divided by two to provide the modulator clock and the output data bit stream is chopped at the X<sub>in</sub> frequency using an alternating 1,0 chop. The chop is used to reduce even order distortion for a stand–alone application without the MC145076. The reconstructed output signal will drop 6dB due to the chopping.

## Xout

#### Master Clock Output (Pin 11)

$X_{out}$  is the inverted output signal of  $X_{in}$  and may be used for a buffered clock output or for a crystal oscillator.

## Xin

## Master Clock Input (Pin 12)

$X_{\text{in}}$  is the input clock pin for the MC145074, and may be used with  $X_{\text{out}}$  as the inverter for a crystal oscillator.

## DMODE

#### Data Mode Input (Pin 13)

A low level on the DMODE pin will select the dual data pin mode of operation. In this mode, the serial input data is entered on the DIR and DIL pins. A high level on the DMODE pin selects the multiplexed mode of operation. In this mode, the left and right channel serial input data must be multiplexed on the DIR/DILR pin.

## **RES0 and RES1**

#### Input Data Resolution Pins (Pins 14, 15)

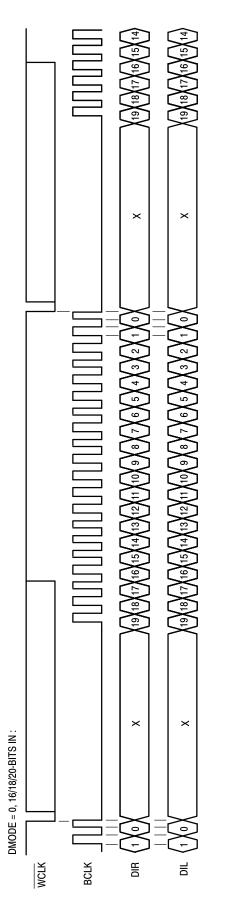

The RES0 and RES1 pins select the length of the serial data word input to the MC145074. The serial input data can be 16, 18, or 20–bits in length with the most significant bits clocked in first. Figure 9 lists the serial interface formats.

## DOL

## Left Channel Data Output (Pin 16)

DOL is the left channel modulator data output.

| DMODE | RES1 | RES0 | Operating Mode               |

|-------|------|------|------------------------------|

| 0     | 0    | 0    | Dual Data Pin 16–Bit Input   |

| 0     | 0    | 1    | Dual Data Pin 18–Bit Input   |

| 0     | 1    | 0    | Dual Data Pin 20–Bit Input   |

| 0     | 1    | 1    | Factory Test Mode            |

| 1     | 0    | 0    | Single Data Pin 16–Bit Input |

| 1     | 0    | 1    | Single Data Pin 18–Bit Input |

| 1     | 1    | 0    | Single Data Pin 20–Bit Input |

| 1     | 1    | 1    | Factory Test Mode            |

#### Figure 8. Serial Interface Formats

#### **FUNCTIONAL DESCRIPTION**

The MC145074 is a high precision Stereo Audio Digitalto-Analog Converter, which utilizes a second-order sigmadelta modulator with a patented 2-tap architecture that significantly reduces problems normally associated with one-bit sigma-delta technology. Normally, a second order modulator can develop patterns in the digital output representation of small signals and with small DC input offsets. It is common to add dither to mask these effects, but a reduction of dynamic range can result. The implementation used in the MC145074 has considerable immunity to these troublesome inputs, and without performance compromise.

With RC filtering, the MC145074 can be used as a standalone stereo digital modulator for applications with modest requirements. High performance can be realized with the companion MC145076 Stereo Audio FIR Smoothing Filter, which reduces the in-band IM products formed by large amplitude spectral components of the out-of-band noise shaping, clock corruption, and power supply noise.

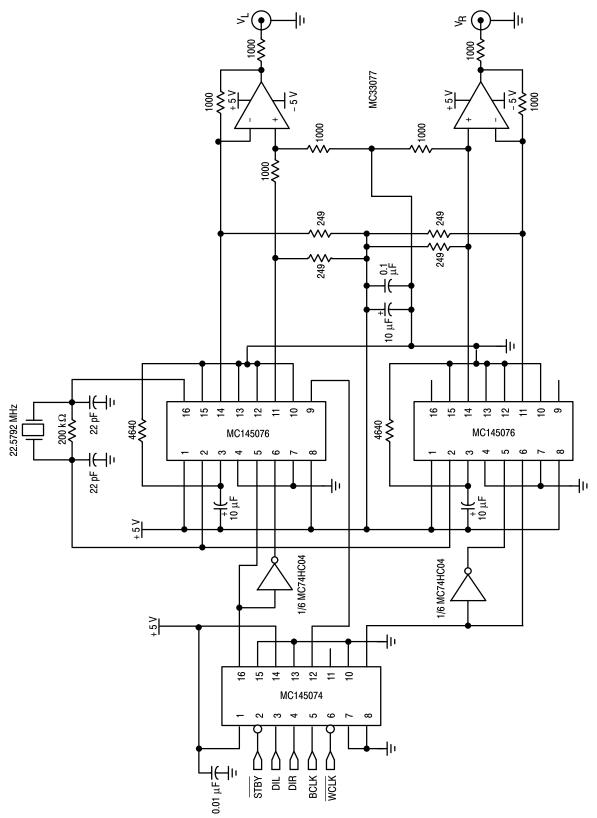

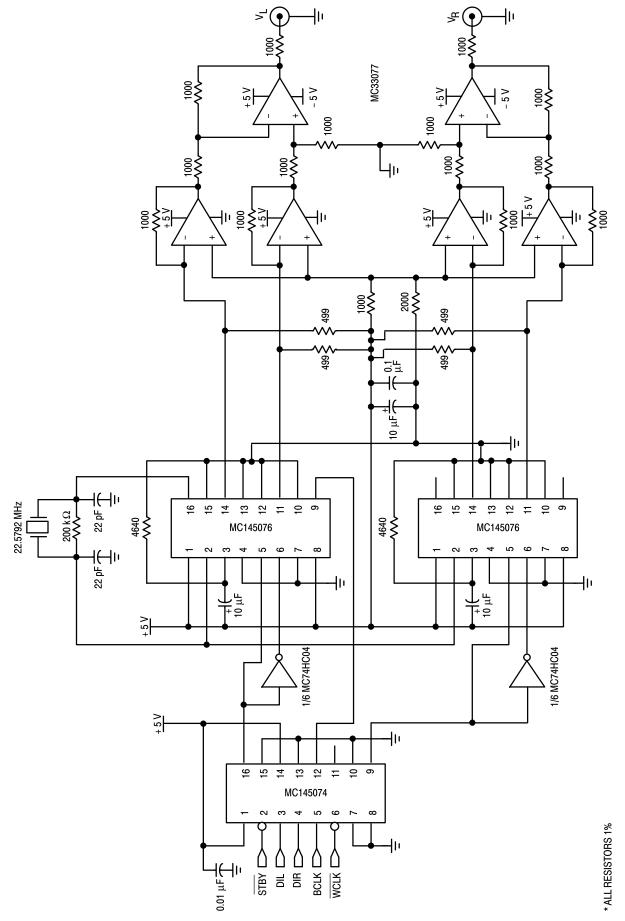

The MC145074 has been designed for maximum flexibility and is well suited for high fidelity audio and multimedia applications. If used in conjunction with a differential MC145076 smoothing filter, a peak S/(N+D) ratio of > 100 dB can be achieved by utilizing 18 or 20-bit input data and a 256x oversampling ratio. The MC145074 has a maximum operating frequency of 18.5 MHz, and can be used with any sampling rate including 32, 44.1, or 48 kHz.

The MC145074 can accept a 1x, or a 2x input clock with serial data output chop. The device can accept 16, 18, or 20–bit digital data in a dual data pin input format, or single pin multiplexed format. An offset scaler is included to allow 0 dB digital inputs while maintaining low distortion. The offset, scaled data is applied to the D/A modulator before being optionally chopped (2x mode), and sent to an external smoothing filter. When this device is used with the MC145076, dividing the clock down or using the chop mode is not necessary.

#### **TIMING CIRCUIT**

The internal timing circuits of the MC145074 are driven by the X<sub>in</sub> clock. When the DIV2 pin is active high, the MC145074 divides the X<sub>in</sub> clock by two to generate the internal modulator clock (MODCLK), and uses the X<sub>in</sub> clock frequency to chop the output data using a 50% chop signal.

When the MC145074 is operated in the master mode, the  $\overline{\text{WCLK}}$  pin is configured as an output. The  $\overline{\text{WCLK}}$  output is generated by dividing down the modulator clock. The divide

ratio of the internal frequency divider can be programmed utilizing a 5-bit control word while the MC145074 is in the standby mode. The 5-bit control word is defined as the last 5-bits (MSB first) that are clocked into the DIR/DILR pin using the BCLK signal. When cleared, the most significant bit of the control word indicates that the WCLK signal is negative edge triggered (just as in the slave mode). If the most significant bit is set, the WCLK is positive edge triggered. The next three most significant or middle three bits of the control word determine the value of the divide ratio of the internal frequency divider. The least significant bit of the 5-bit control word indicates a prescaler divide by two when cleared, and divide by three when set. The divider modes are summarized in Figure 10.

#### NOTE

The default mode of operation is control word \$06 which provides a  $\overline{WCLK}$  signal (negative edge triggered) at a frequency of 1/64 the modulator clock frequency. This is the preferred operating mode of 256x OSR and 4x FIR.

| Control<br>Word<br>Value<br>(Hex) | Divide<br>Ratio                   | WCLK<br>Edge | Control<br>Word<br>Value<br>(Hex) | Divide<br>Ratio                   | WCLK<br>Edge |

|-----------------------------------|-----------------------------------|--------------|-----------------------------------|-----------------------------------|--------------|

| 0<br>1<br>2                       | 8<br>12<br>16                     |              | 10<br>11<br>12                    | 8<br>12<br>16                     |              |

| 3<br>4<br>5<br>6<br>7             | 24<br>32<br>48<br>64              |              | 13<br>14<br>15<br>16              | 24<br>32<br>48<br>64              |              |

| 7<br>8<br>9<br>A                  | 96<br>128<br>192<br>256           |              | 17<br>18<br>19<br>1A              | 96<br>128<br>192<br>256           |              |

| B<br>C<br>D<br>E<br>F             | 384<br>512<br>768<br>1024<br>1536 |              | 1B<br>1C<br>1D<br>1E<br>1F        | 384<br>512<br>768<br>1024<br>1536 |              |

#### Figure 9. WCLK Divider Modes

## **OFFSET SCALER**

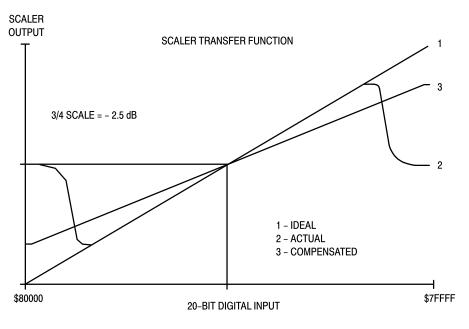

Second order sigma-delta modulators typically give up about 2 dB of dynamic range and an adjustment to the digital input words must be made if full scale digital input word recognition is desired. The offset scaler circuitry of the MC145074 digitally attenuates the input linearly to 3/4 or approximately - 2.5 dB. Figure 11 illustrates the function of the offset scaler block. An ideal DAC would perform as shown in curve one, but the sigma-delta modulator actually operates as shown in curve two. The digital input words to the MC145074 are attenuated to 3/4. This allows the MC145074 to operate on all 2's compliment digital inputs from \$80000 to \$7FFFF, with the resulting response shown in curve three. In addition to scaling the digital input word, the offset scaler adds a digital dc offset of 1/8th to re-center the digital input word so that the MC145074 output signal is centered around VDD/2.

Figure 10. Offset Scaler Operation

## SERIAL INTERFACE AND CONTROL LOGIC

The serial interface and control logic of the MC145074 may be configured to accept 16, 18, or 20–bit data words by applying the appropriate logic levels to the RES1 and RES0 pins. The DMODE input pin configures the serial interface to accept 2's complement data (MSB first) in a dual data pin or single pin, multiplexed input format. It should be noted that in some cases when using the single data pin input mode and a large OSR, the BCLK rate may be too high for some DSPs, unless an interface formats of the MC145074.

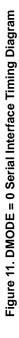

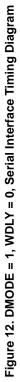

When operating in a dual data pin mode, 2's complement data words are serially input from the DIR and DIL pins as shown in Figure 12. A rising edge on BCLK serially shifts in the data present on the DIR and DIL inputs. After all data bits of an input word are shifted in, a falling edge on  $\overline{WCLK}$

latches the data word into the MC145074. The BCLK can be a continuous clock as long as the serial input data word is right justified in the word time, or as long as there exists one and only one BCLK cycle for every data bit input to the device.

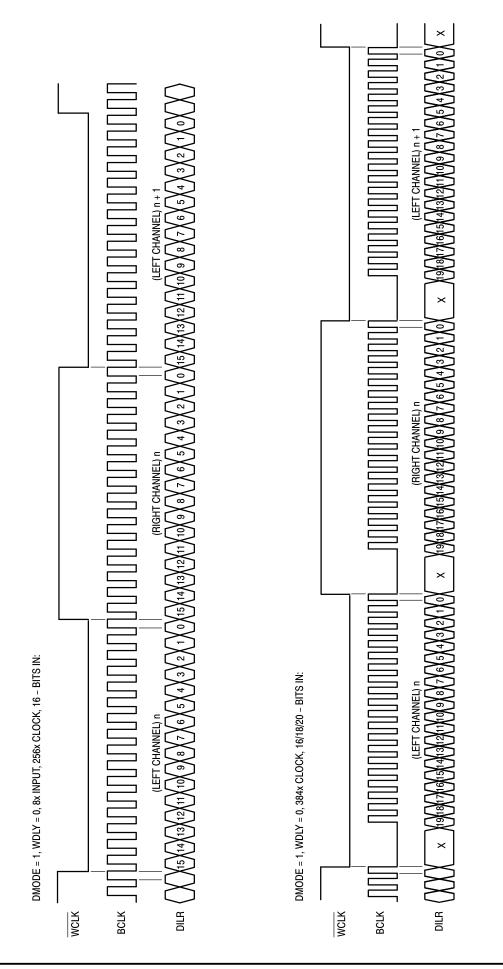

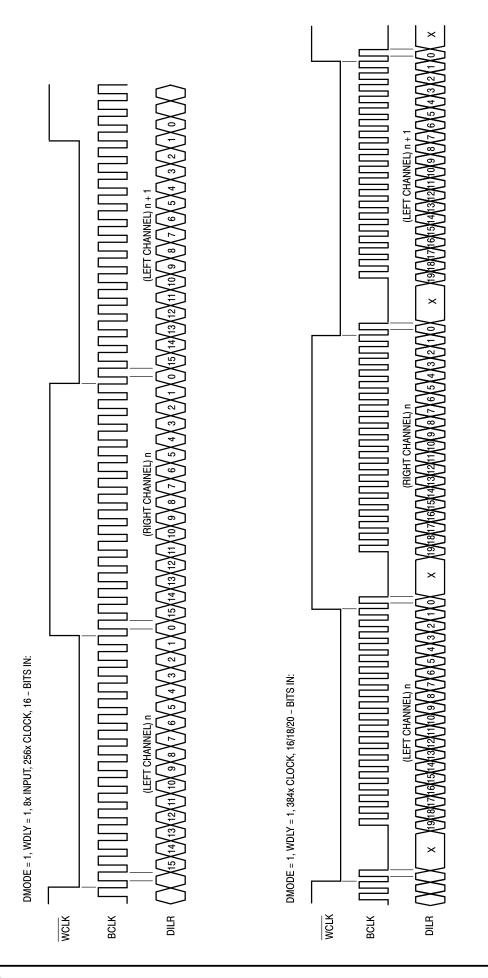

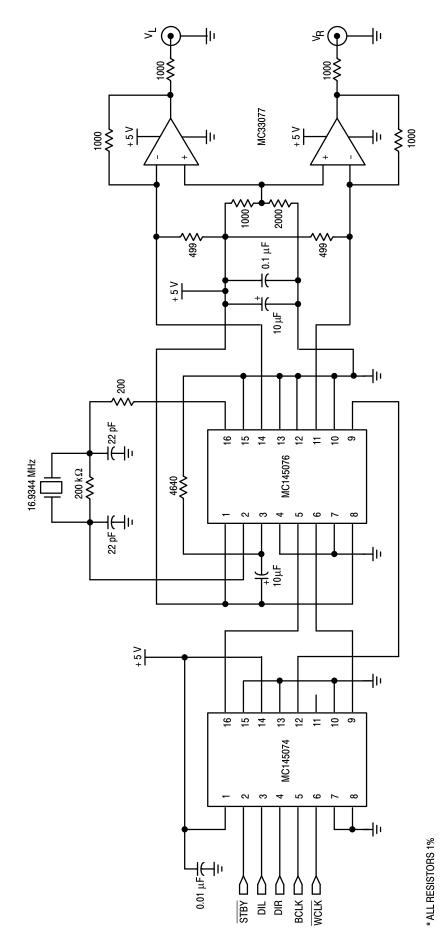

When operating in a single pin multiplexed mode, the DIR input pin is reconfigured as the DILR pin. Left and right channel serial input data is multiplexed into the MC145074 on the DILR pin, and is serially shifted into the part using BCLK as shown in Figure 13. When WDLY is low, left channel data is latched into the part on the rising edge of WCLK, and right channel data is latched on the falling edge of WCLK. As in the dual data pin mode, the BCLK can be either an asynchronous or continuous clock as long as the serial input data word is right justified in the word time. Forcing WDLY high allows the WCLK cycle to appear one clock cycle early as shown in Figure 14.

\* ALL RESISTORS 1%

Figure 16. High Performance Stereo Audio System, Typically 105 dB S/(N+D)

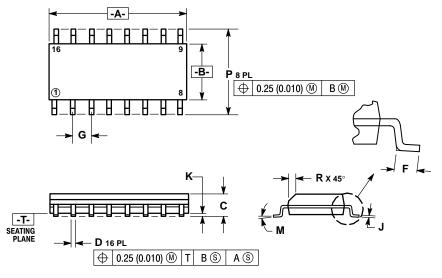

## PACKAGE DIMENSIONS

#### SOIC PACKAGE CASE 751B-05

NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIM | IETERS     | INC       | HES        |

|-----|--------|------------|-----------|------------|

| DIM | MIN    | MAX        | MIN       | MAX        |

| Α   | 9.80   | 10.00      | 0.386     | 0.393      |

| В   | 3.80   | 4.00       | 0.150     | 0.157      |

| С   | 1.35   | 1.75       | 0.054     | 0.068      |

| D   | 0.35   | 0.49       | 0.014     | 0.019      |

| F   | 0.40   | 1.25       | 0.016     | 0.049      |

| G   | 1.27   | BSC        | 0.050 BSC |            |

| J   | 0.19   | 0.25       | 0.008     | 0.009      |

| K   | 0.10   | 0.25       | 0.004     | 0.009      |

| М   | 0°     | <b>7</b> ° | 0°        | <b>7</b> ° |

| Р   | 5.80   | 6.20       | 0.229     | 0.244      |

| R   | 0.25   | 0.50       | 0.010     | 0.019      |

This page intentionally left blank.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 🖗 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution;

Mfax is a trademark of Motorola, Inc.

P.O. Box 5405, Denver, Colorado 80217. 303-675-2140 or 1-800-441-2447

JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, 6F Seibu-Butsuryu-Center, 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 81-3-3521-8315

Mfax™: RMFAX0@email.sps.mot.com - TOUCHTONE 602-244-6609

INTERNET: http://www.mot.com/SPS/

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, - US & Canada ONLY 1-800-774-1848 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298