| |

|

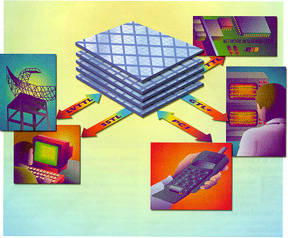

1,000,000 System Gates at 100+ MHz in 1998  The Virtex series of FPGAs features a cutting edge 0.25 micron family that will deliver 1,000,000 gate devices by the end of 1998 and address the need for the rapidly growing demand in todays telecommunication, networking, and computer market segments. Virtex combines the best concepts of the highly successful XC4000 and XC4000XL series of FPGAs with numerous enhancements including highly flexible I/O buffers, multiple PLLs, and dedicated 4-kbit, dual-ported SRAM blocks, and 2.5-volt internal operation. First Fully Programmable Alternative to System-level ASIC Design

Virtex Features:

Virtex has all of these attributes and more, making it a true system level solution!  Continuing and further expanding the Xilinx technological leadership of 0.25 micron process technology and five layer metal, the Virtex series is optimized for increased performance and density while providing predictable routing delays. In close partnership with United Microelectronics Corporation, Xilinx is the first major programmable logic supplier to offer 0.25 micron as a standard production process. Building on the 0.25u, five layer metal process, a new architecture has been created that combines the best features of programmable logic with the best features of system-level ASIC solutions.  Architectural Advantages and Family Highlights SelectI/O eliminates challenges of multiple standards Hierarchy of RAM integration A common example of system-level designs requiring fast access to varied sizes of RAM is a video processing application: video frame data is stored in megabytes of RAM; line data is stored in kilobytes of RAM; and pixel and coefficient data is stored in bytes of RAM. The Virtex series offers an ideal hierarchy of SelectRAM+ features for such applications. For megabytes of storage, the Virtex SelectI/O feature provides 133 MHz external synchronous DRAM access compatible with the SSTL3 I/O standard. Kilobytes of data can be stored in block SelectRAM memory. Virtex series offers up to 32 blocks of 133 MHz dual port synchronous SRAM yielding internal memory bandwidth up to 17 gigabytes/second. For bytes of data, Virtex offers distributed SelectRAM memory. Pioneered in the Xilinx XC4000 family of FPGAs, the distributed SelectRAM provides fast and flexible access to shallow single and dual port synchronous SRAM. Vector-based interconnect produces fast and predictable routingThe Virtex series uses a segmented routing optimized for interconnect delays as a function of the distance, or vector, from source to destination. This offers a faster, more predictable routing scheme than non-segmented interconnect. Virtex devices contain interconnects of varied lengths, resulting in delays that are fast, predictable, and insensitive to minor changes in placement. These advantages of segmented interconnect become increasingly important in high-density design. Synthesis tools will accurately model interconnect delays in Virtex series without placement information.

Innovations in FPGA design methodology available now The first Virtex devices contain 250,000 system gates and 316 user I/O lines and are expected to be sampling in the second quarter of 1998. Virtex devices, offering up to one million system gates are expected in the second half of 1998. More Information | ||||