THE QUARTERLY JOURNAL FOR XILINX PROGRAMMABLE LOGIC USERS

The Programmable Logic Company<sup>SM</sup>

#### Inside This Issue:

#### GENERAL

| Fawcett: Reconfigurable Computing 2 |

|-------------------------------------|

| Guest Editorial 3                   |

| Customer Success Stories            |

| GPT Video Systems 6-7               |

| BICOM 7                             |

| Xilinx Funds Seiko-Epson Foundry    |

| New Data Book Now Available8        |

| What's New on WebLINX9              |

| Training Update9                    |

| Financial Results 10                |

| New Product Literature 10           |

| Upcoming Events 10                  |

|                                     |

#### PRODUCTS

| XC5200 Prices Down, Value Up      | 11    |

|-----------------------------------|-------|

| XC7300 Best 44-Pin PLD            | 12-13 |

| XC8100 Family Discontinued        | 13    |

| Production Begins for XC4000EX    | 14    |

| Faster -2 Speed Grade for XC4000E | 14    |

#### **DEVELOPMENT SYSTEMS**

| Synopsys' FPGA Express              | 15-16 |

|-------------------------------------|-------|

| LogiCore PCI Initiator Debuts       | 17    |

| Foundation Introduction Successful. | 17    |

#### **HINTS & ISSUES**

| XC9500 CPLD Pin-Locking 18-21              |

|--------------------------------------------|

| XC9500 Slew Rate Controls 22               |

| Using XC5200 Carry Logic23-25              |

| Advantages of Select-RAM26-27              |

| Power, Package & Performance 28-29         |

| Metastability Recovery in FPGAs 30-31      |

| XACT step on Alternate Systems             |

| E-Mail Group Monitors Xilinx Products . 33 |

| New Technical Support Choices 34-35        |

| Questions & Answers                        |

| Component Availability Chart               |

| Development Systems Chart 40               |

| Programming Support Charts 41-43           |

| Alliance Program Charts 44-46              |

| Reader Survey 47                           |

| Fax Response Form 48                       |

| -                                          |

# PRODUCTINFORMATION

# **XC5200 FPGAs:** Prices Go Down and Performance Goes Up

Process improvements and record sales have helped to knock as much as 50% off the price on XC5200<sup>TM</sup> family FPGAs, while boosting performance by as much as 30%...

## Synopsys Introduces FPGA Express

Alliance partner Synopsys has built on the strengths of its FPGA Compiler to create a Windows 95 and NT product that includes all of the hottest new Xilinx products...

See Page 15

## **DESIGN TIPS & HINTS**

## Pinlocking & XC9500 CPLDs

In further proof that designers must consider more than just the expected specifications, XC9500<sup>TM</sup> CPLDs have proven themselves to be the best choice for maintaining pinouts during design iterations...

See Page 18

# Using XC5200 FPGA Carry Logic

Tips for using this simple, but flexible, feature...

See Page 23

#### FROMTHEFAWCETT

## Reconfigurable Computing: **Coming of Age** By BRADLY FAWCETT Editor

•The conference

provided some valuable insights

into the nature of the nascent

his past June, Xilinx held its first Reconfigurable Computing Developer's

•

•

•

•

Program Conference at a hotel in Santa Clara, not far from company headquarters. Planned to be an annual event, the conference brought together representatives from 11 of the more than 20 companies that are participants in the Developer's Program.

The Reconfigurable Computing (RC) Developer's Program was founded in mid-1995 to proactively spur commercial development of reconfigurable computing applications and products (*see* XCell #19, *page 35*). The program is designed to aid commercial companies through technical,

marketing and, in some cases, financial assistance. In this context, reconfigurable computing is loosely defined as the practice of using in-system-

loosely defined as the practice of using in-systemconfigurable FPGAs as computing elements to accelerate operations in general-purpose computers. In these systems, FPGAs are reconfigured during system operation to perform a variety of operations directly in hardware,

off-loading the host processor and dramatically increasing system performance.

Each company attending the meeting gave a short presentation about the products it has developed or is developing. Several companies brought demonstration systems to the meeting. The conference was an ideal forum for letting representatives of the member companies interact with Xilinx R&D personnel and each other.

The conference provided some valuable insights into the nature of the nascent but growing market for RC-based products. Among this small sampling, there were *two main business models*. Some companies specialize *in providing hardware and software tools to OEM accounts* that develop their own products, while other member companies are *focused on their own specific end applications*.

The first category includes Annapolis Micro Systems (Annapolis, MD), Virtual Computer Corp. (Reseda, CA), and Giga Operations (Berkeley, CA). All are making significant strides in the development of RC-based hardware platforms and soft-

> ware tools. One of the most interesting aspects of their presentations was the mention of the types of large corporate OEM accounts that are using or

evaluating those products — names like Boeing, Ericsson, Loral, NTT, Delco, E-Systems and TRW.

Other companies are using RC-based systems in their end products to tackle a wide variety of high-performance computing tasks, ranging from satellite communications to automated searches of DNA sequences to 3-D graphic rendering for video games.

### XCELL

Please direct all inquiries, comments and submissions to:

Editor: Bradly Fawcett

#### Xilinx, Inc.

2100 Logic Drive San Jose, CA 95124 **Phone:** 408-879-5097 **FAX:** 408-879-4676 **E-Mail:** brad.fawcett@xilinx.com

©1996 Xilinx Inc. All rights reserved.

XCELL is published quarterly for customers of Xilinx, Inc. Xilinx, the Xilinx logo and XACT are registered trademarks; all XC-designated products, HardWire, Foundation Series, and XACTstep are trademarks; and "The Programmable Logic Company" is a service mark of Xilinx, Inc. All other trademarks are the property of their respective owners.

•

#### **GUESTEDITORIAL**

# Xilinx Takes the Lead in ISP Standardization Effort

By NEIL G. JACOBSON  $\blacklozenge$  Manager, JTAG Research & Development

In-system programming (ISP) allows users to program and re-program parts that are already soldered on a system board to facilitate prototyping, streamline manufacturing flows and enable remote system updating.

As ISP proliferates, end-users are strained by the difficulty of finding third party applications solutions that address the system-level issues for the wide variety of ISP parts available. In addition, their own test and diagnostic software development costs escalate as new devices come on-line, requiring extensive programming algorithm re-work.

At the last IEEE 1149.1 (JTAG) working group meeting, it was recognized that the use of the 4-pin 1149.1 test access port (TAP) as the platform for ISP development is becoming a de facto standard among most PLD manufacturers. (For example, XC9500 family CPLDs are always programmed through the TAP, and XC4000 series FPGAs optionally can be programmed through the TAP). The working group chose to take a active role in bringing an ISP extension to 1149.1 under its purview, with Xilinx taking the lead in this effort.

Xilinx and Hewlett Packard organized a meeting of more than 30 participants from about 20 companies. This first 'study group' meeting was held on April 19 at

Hewlett Packard's Manufacturing Test Division in Loveland, CO. The attendees included PLD manufacturers such as Xilinx, Altera, Lattice, AMD, Cypress and IBM; third-party tool manufacturers such as Asset Intertech, Corelis, Intellitech and APG Test Consultants; automatic test equipment manufacturers such as HP, GenRad and Teradyne; and ISP end-users such as Cisco Systems and HP.

There was broad agreement that the value of standardization was great. Immediate applications could be envisioned in fields as diverse as emulation technologies and remote field test and diagnostics. The vendor approaches to ISP were close enough to one another for the development of a standard approach to be meaningful. General consensus seems to be forming in the following areas:

A. The IDCODE and USERCODE registers are a vital part of any ISP device and will probably be made mandatory.

The XC9500 CPLD architecture already includes these optional 1149.1 functions. Indeed, not supporting these part, program content and version identification instructions makes ISP impractical since the revision level and contents of a system would be otherwise unobtainable.

Continued on the next page

•••••

•As ISP proliferates, endusers are strained by the difficulty of finding third party applications solutions that addresss the systemlevel issues for the wide variety of ISP parts available."

Continued from page 2

Products that have already reached the marketplace include *Digital Wings for Audio* from Metalithic Systems (Sausalito, CA), satellite ground station communications systems from TSI Telsys (Columbia,

•The enormous potential of reconfigurable computing is beginning to attract the attention of the CAE tool vendors." MD), the *DeCypher II* 'Genetics Supercomputing PC' from Time Logic (Incline Village, NV), and the *X-CIM* line of DSP acceleration modules from MiroTech Microsystems (Saint Laurent, Quebec, Canada).

• Available soon in retail music equipment stores, *Digital Wings* is a 128-track audio authoring system that operates in the Windows environment on a PC (*see XCell #20, page 42*). Metalithic Systems is targeting the 'music enthusiasts' market with this product, and is developing a lower-cost version for the consumer market.

- TSI Telsys recently sold several of its satellite 'gateway' systems to NASA's Marshall Space Flight Center, where it will support programs such as the Space Station project.

- Time Logic's *DeCypher II* system, designed for screening DNA sequence data, is proving popular with both pharmaceutical companies and medical research facilities, where it outperforms multi-million-dollar supercomputers.

- MiroTech Microsystems is addressing the FPGA-based DSP market. Its DSP acceleration modules are fully

#### GUESTEDITORIAL

Continued from the previous page

- B. The system-level issues related to ISP (i.e., safe pin states during ISP operations, describing how parts can safely initialize after ISP is completed, etc.) must be addressed. The XC9500 ISPEN and ISPEX instructions provide a framework for protecting the user's system during ISP operations. This type of functionality is absolutely critical for developing a truly workable ISP-based system — Xilinx has it now.

- C. The interchange of information should be included as part of the

**Getther way, Xilinx has** already equipped the new XC9500 family with the industry's best JTAG/ISP capabilities and is spearheading the next generation of programming and testing standards." overall standard. Serial vector format (SVF), suitably modified, might best serve as that vehicle.

The EZTag software generates SVF files to describe all XC9500 ISP operations.

**D.** The RUN-TEST/IDLE state is the "action" state in which programming or erase latency times are spent. This is exactly the way XC9500 parts function.

A final report will be made to the 1149.1 working group at the International Test Conference in October. At that time, it will be decided whether to pursue this as a separate standard within the 1149 frame-work or as an application of the 1149.1 standard.

Either way, Xilinx has already equipped the new XC9500 family with the industry's best JTAG/ISP capabilities and is spearheading the next generation of programming and testing standards. compliant with Texas Instrument Modules (TIM) specifications and are supported by a library of common DSP functions. MiroTech has signed an OEM agreement with a major manufacturer of DSP boards.

The remaining companies at the conference previewed products in development. enVia Inc. (Menlo Park, CA) is developing consumer telecommunications equipment that uses reconfigurable FPGAs to address the growing problem of incompatible wireless telecommunications standards. Octree Corp. (Cupertino, CA) has implemented 3D volume rendering systems on Annapolis Micro Systems and Giga Operations platforms, and is developing products for both medical equipment and video game manufacturers. Start-up Adaptive CAD Technologies (Sunnyvale, CA) and consulting firm Memec Design Services (Garden Valley, CA) also attended, and are applying RC technology in some new application areas (but it's too early to reveal them).

Another encouraging sign was the presence of representatives from several of the CAE companies in the Xilinx Alliance Program. The enormous potential of reconfigurable computing is beginning to attract the attention of the CAE tool vendors. For many of these vendors, this conference was their first chance to talk with the early adopters of reconfigurable computing technology; it is certainly not inconceivable that some cooperative product development efforts will eventually result from this meeting. Continued from the previous page

*Conference* was their first chance to talk with the early adopters of reconfigurable computing technology; it is certain not inconceivable that some cooperative product development efforts will eventually result from this meeting."

In summary, reconfigurable computing technology is continuing to 'come of age,' with several companies already garnering revenue from a wide variety of RC-based products, penetration of RC technology into large, well-known electronic equipment manufacturers, and the attention of leading design tool vendors. I'm already looking forward to next year's conference. ◆

**Sharp-eyed readers** may notice a slight change to the format of *XCell* in this issue. The tables listing component availability, Xilinx software status, Alliance partner information, and device programmer status have been moved from the "General Information" section to the last few pages of the newsletter. As a few readers have suggested, this will make the tables easier to find as well as providing for better continuity for those who read the whole journal front-to-back.

We are always interested in reader feedback. This issue includes a short reader survey on page 47. We would greatly appreciate if you would take a few minutes to fill out this questionnaire and mail or FAX it back to us. Alternatively, you can send your comments directly to me via E-mail at brad.fawcett@xilinx.com. We're looking forward to hearing from you.

# Videoconferencing with XC4000 FPGAs

GPT Video Systems (Maidenhead, Berks, U.K.) designs and manufactures high-quality videoconferencing solutions under the brand name FOCUS. GPT Video Systems is a long time user of Xilinx products; its designers use FPGA technology to maintain the flexibility and rapid time-tomarket required in the fast moving multimedia market.

The flexibility of FPGA technology was evident in the design of the latest FOCUS videoconferencing systems, where  $XC4000^{TM}$  series FPGAs were used for both prototyping and production applications.

During system prototyping, three XC4013

devices were used to develop and test the functionality required for a large ASIC device. Meanwhile, XC4010 FPGAs were used to implement key data routing and timing generation functions in the production version of the video processing module.

An audio, video and data multiplexer design targeted for a semi-custom gate array implementation was prototyped with three XC4013 devices. The development was carried out using Cadence Verilog software running on a Sun SparcStation. The FPGAs provided a fast and flexible development route, culminating in a fullyfunctional ASIC on the first try. The ASIC device holds about 30,000 gates of logic, with a 20 MHz system clock rate. Verifying the design with the FPGAs saved significant additional NRE costs and development time that would have been incurred if changes to the design had been required after committing to custom silicon. Furthermore, this development route allowed beta versions of the system to be shipped with the FPGA solution before production volumes of the ASIC were available, further accelerating time-to-market.

Three XC4010 FPGAs hold the majority of the logic in the video processing module in the main codec design. Two of the FPGAs share a common design and act as video routers, passing CCIR601 digital video data from various input sources to the desired outputs. Each device is designed to route data in the form of an 8-bit data bus, requiring two to be used for the 16-bit data in the CCIR601 format. Thus, one device handles the routing and control of the luminance data, and the other handles the chrominance data.

These two devices also perform the task of overlaying the graphical user interface directly onto the video outputs. This includes a patented function that produces semi-transparent video, allowing on-screen text to be displayed in an easily-readable format while not obscuring the live video beneath. The design makes specific use of the XC4000 architecture's on-chip RAM capability to implement fast look-up tables.

The third XC4010 FPGA in the video processing module is a timing generator, providing all the timing functions for the various video field store read and write operations. This FPGA also contains the state machines that control the reading and writing of captured video images to and from the graphics frame stores.

The XC4010 designs were entered using a combination of schematic capture and ABEL hardware descriptions and verified with the ViewSim simulator, using a PC-based Viewlogic environment. All three FPGAs are about 80% full and run at a system clock speed of 13.5 MHz, a performance level that was easily reached using timing constraints and automatic placement and routing tools.

To further reduce hardware costs during volume production of the codecs, the XC4010 FPGA designs were frozen and converted into HardWire<sup>TM</sup> XC4310 devices. Since the Hard-Wire devices are pin and function compatible with the FPGAs that they replace, system flexibility is maintained; the HardWire devices can be replaced with newly-designed FPGAs if the design evolves at a later date. According to Richard McCandless, Project Leader at GPT

Video Systems, "The HardWire conversion went extremely well, with very little engineering effort required at all, and they came in on time! In fact, it surprised us how little engineering effort was needed."

As noted by McCandless, "These video interface designs were fairly complex, but the FPGAs proved to be very flexible and easy to work with. The high level of integration provided by the FPGA devices has helped to create the most user-friendly graphical user interface in the videoconferencing industry."

# Video Processing With XC7300 CPLDs

BICOM, Inc., (Monroe, CT) is a provider of hardware and software "building blocks" for developing a

wide range of voice processing applications. BICOM's products are used in the development of systems for voice mail, interactive voice response, audiotex, dictation and call center management.

The recent design of their new Gemini series of high-density computer telephony

platforms required a high-performance CPLD to integrate a variety of logic functions. With cost and ease-of-use considerations in mind, the Xilinx XC7300<sup>™</sup> CPLD family was chosen.

The voice processing board contains 14 XC7336 devices. The XC7336-5 CPLDs are used to hold a variety of logic functions, including address decoders, state machines, I/O func-

tions and glue logic, with XC7336-15 CPLDs for the com-

plicated timing associated with the telecommunications channel. If BICOM had used traditional PALs for these logic functions, the design would have encompassed two boards rather than one.

The design was entered and implemented on a PC

using OrCAD schematic entry tools. The complexity of the design (which included a mix of analog and digital technologies) and tight development schedules dictated the use of programmable devices with predictable performance and good pin-locking capabilities. The XC7336 CPLD fulfilled both these needs. Pinouts were pre-

assigned and maintained throughout multiple design iterations. This allowed the designers to concentrate on the more difficult architectural aspects of the design.

As first-time Xilinx users, BICOM engineers were impressed with the level of technical support provided by the Xilinx team.

> In summary, by using the XC7300CPLD family, BICOM

engineers were able to meet their

performance needs, reduce design complexity and cost, and save valuable board space as well.  $\blacklozenge$

# Xilinx Helps Fund New Seiko-Epson Foundry

Xilinx has announced its funding of up to \$300 million for the construction of a new semiconductor manufacturing facility. The facility will be built and operated by Seiko-Epson Corp. in Sakata, Japan (about 200 miles north of Tokyo). Xilinx will make incremental advance payments over the next two and one-half years to help finance construction of the facility. In return, Xilinx will receive a specified number of wafers from the new line through the year 2002.

The new operation will manufacture 8" wafers using advanced 0.35 to 0.25 micron CMOS technology. In time, these advanced processes will enable the development of programmable logic devices with capacities reaching 500,000 gates. Production at the facility is expected to begin in early 1998.

"We're confident that our continuing partnership with Seiko-Epson will enhance our competitive position and allow us to design products with ever higher densities and faster performance, " stated Xilinx Chief Executive Officer Willem Roelandts. "Just as important, it will help us meet growing customer demand worldwide for our products into the next century."

This investment agreement further strengthens the close relationship between Xilinx and Seiko-Epson; Seiko-Epson has been a supplier to Xilinx for more than a decade. Xilinx also will maintain its existing foundry partnerships with Yamaha, Taiwan Semiconductor Manufacturing Company (TSMC), United Microelectronics Corporation (UMC) and IC Works. As reported in XCell #20, Xilinx owns a 25% equity stake in a new foundry being constructed by UMC in Taiwan and scheduled to come on-line in the first half of 1997.  $\blacklozenge$

## New Data Book Now Available

B oth CD-ROM and printed versions of the new "Xilinx Programmable Logic Data Book" are now available. The material in the new data book also is available on WebLINX<sup>TM</sup>, the Xilinx World Wide Web site (www.xilinx.com), in the form of individual product specifications. Data Book The CD-ROM, a first with this edition, works with PCs, Sun workstations, and HP workstations. Detailed tables of contents and the ability to search for keywords makes the CD-ROM a valuable tool. The entire data book resides in a single ".pdf" file. The Acrobat<sup>TM</sup> Reader program (that allows users to view .pdf

1996

Now On

CD-ROM

files) and its installer are included on the CD-ROM. The main table of contents, chapter tables of contents and the index all include hypertext links to immediately jump to the appropriate pages in the book.

At 900 pages, the data book includes data sheets for the XC7300, XC9500, XC3000A/L, XC3100A/L, XC4000E, XC4000EX/XL, XC5200, XC6200, and XC1700D device families. Product specifications for the older XC2000, XC3000, XC3100, and XC4000/A/H/D/L families are not included, but are still available on WebLINX. The military/high-reliability and HardWire<sup>™</sup> product lines are overviewed, but detailed product specifications are still found in separate, dedicated documents.

To obtain a copy, contact your local Xilinx sales representative.

8

#### Xilinx Home Page • www.xilinx.com

WebLINX was recently named an Infoworld HotSite! Here are a few of the reasons why:

#### ◆ SmartSearch<sup>™</sup> Agents Released

Come visit the industry-wide search engine made specifically for topics involving programmable logic. You can create your own agents to notify you by e-mail as material you want becomes available in any of multiple sites on the web.

#### ♦ Xilinx Guided Tour

Check out this on-line company and product overview covering topics such as Xilinx corporate and product strategies, device selection,  $XACTstep^{TM}$  software solutions, quality assurance and Xilinx technical support services.

#### Product Spotlights

Examine a showcase of our latest products, currently featuring the XC4000EX and XC9500 device families and the Foundation Series software, with its easy-to-use, low-cost VHDL synthesis solution.

#### On-Line Net Seminars

In cooperation with Marshall Industries, Xilinx holds live seminars on the Internet, complete with an on-line slide and audio presentation and a live chatresponse forum for asking questions. Recorded seminars on the XC5200 and XC9500 device families also are available to review at your convenience. ◆

#### **TECHNICAL TRAINING UPDATE**

# Both Schematic- and Synthesis-Based Classes Offered

#### I wo basic classes are available from Xilinx, a schematic-based and a synthesis-based class.

Actually, both classes focus more on overall design methodologies for using Xilinx devices, rather than the specific front-end tools. (The tutorials shipped with the development systems provide the specific tool training for the new user.) The schematic-based class has traditionally utilized ViewLogic tools in the examples and labs. However, with the introduction of XACT*step* version 6.0.1, the class has been updated to use the Foundation<sup>TM</sup> Development System and its front-end tools from Aldec.

The synthesis-based class uses the Synopsys tools. The course goes beyond

explaining and demonstrating the basic concepts behind HDL-based design by examining many of the specific language constructs that should be used when designing with these tools.

All designers can benefit from taking one of these classes. Even designers already familiar with Xilinx technology can learn some new methods to reduce design time and increase device performance.

Remember, either class (and even customized classes) can be presented right at your own facility. Please contact your local Sales office or our training registrar with your needs. The latest schedule of classes and contact information is always available on WebLINX, our World Wide Web site (www.xilinx.com). ◆

# New Product Literature

Learn about the newest Xilinx products and services through our extensive library of product literature. The most recent pieces are listed below. To order or to obtain a complete list of all available literature, please contact your local Xilinx sales representative.

| TILE                                        | DESCRIPTION         | NUMBER     |

|---------------------------------------------|---------------------|------------|

| 1996 Programmable Logic Data Book           | Technical Data      | 0010303    |

| 1996 Programmable Logic Data Book on CD-ROM | Technical Data      | 500360     |

| Product Overview Brochure                   | Features & Benefits | 0010130-05 |

| Software Selector Guide                     | Features & Benefits | 0010304    |

| FPGABrochure                                | Features & Benefits | 0010305    |

**UPCOMING EVENTS**

Look for Xilinx technical papers and/or product exhibits at these upcoming industry forums. For further information about any of these conferences, please contact Kathleen Pizzo (Tel: 408-879-5377 FAX: 408-879-4676). ◆

**EuroDAC & EuroVHDL** Sept. 16-20 Geneva, Switzerland

International Workshop on Field Programmable Logic and Applications Sept. 23-25 Darmstadt, Germany

**PCI Europe** Oct. 1-2 Paris, France

**DSP Germany** Oct. 1-2 Munich, Germany **DSP World/ICSPAT** Oct. 8-10 Boston, MA

Silicon Design Conference Oct. 9-10 Birmingham, United Kingdom

WESCON Oct. 22-24 Anaheim, California

**DSP France** Oct. 22-24 Paris, France **Electronica** Nov. 12-15 Munich, Germany

Photonics East Nov. 18-22 Boston, Massachusetts

**BIAS & DSP Italy** Nov. 26-29 Milan, Italy

DSP UK Dec. 3-4 London, United Kingdom

#### **FINANCIAL RESULTS**

Quarterly Revenue Tops \$150M

Sales revenues rose to \$150.2 million in the first fiscal quarter of 1977 (ending June 30, 1996), a 19% increase over the same quarter one year ago and a 0.3% increase from the immediately preceding quarter.

"The June quarter was a difficult quarter for the semiconductor industry," noted Xilinx Chief Executive Officer Willem Roelandts. "Although Xilinx was not immune to this widespread slowdown, we did experience minor sequential revenue growth. The bright spot was the North American distribution channel, which grew 10% over the prior quarter."

The XC5000 FPGA family continued its torrid growth rate, with sales up 30% over the previous quarter. Recently announced price cuts (*see page 11*) should even further expand the market for this cost-optimized FPGA family.

Xilinx stock is traded on the NASDAQ exchange under stock symbol XLNX.

# **XC5200 Family:** Lower Prices & Higher Performance

Xilinx recently announced significant price reductions and performance improvements for the XC5200 FPGA family, further

advancing its position as the industry's most cost-effective FPGA family.

#### Prices Reduced by up to 50%

XC5200 sales have risen at a record pace. The rapid increase in shipments and a shift to a 0.5  $\mu$  process have resulted in significant cost advantages; these savings are being passed on directly to our users. With its segmented interconnect structure and an architecture optimized for its submicron, triple-layer metal (TLM) process, the XC5200 FPGA family has a significant technological advantage over other architectures. The family's small die sizes — in some cases even approaching today's gate array die sizes — lead to correspondingly low component costs. The chart below shows current highvolume pricing and projected pricing one year from now.

#### XC5200 Family Volume Pricing\*

| Device | Maximum<br>Logic <b>G</b> ates | End of 1996 | 2H97    |

|--------|--------------------------------|-------------|---------|

| XC5202 | ЗK                             | \$5.00      | \$4.50  |

| XC5204 | 6K                             | \$10.00     | \$8.00  |

| XC5206 | 10K                            | \$17.00     | \$12.00 |

| XC5210 | 16K                            | \$27.00     | \$18.00 |

| XC5215 | 23K                            | \$47.00     | \$33.00 |

\* Plastic package, -6 speed grade, 25,000 unit quantity, U.S. direct pricing only

### Performance Improved by 30%

In addition to price reductions, a patented charge-pump transistor design has been added to the XC5200 family. When combined with a semiconductor process shrink from 0.6µm to 0.5µm triple-layer metal technology, the result is a new -3 speed-grade that offers up to a 30% performance improvement over the -5 speed grade (*see table*).

The XC5200 family delivers 2,000 to 23,000 usable gates and robust features, such as the VersaRing<sup>™</sup> I/O interface that maximizes overall utilization and pin assignment flexibility, dedicated JTAG boundary scan logic for increased testability, and

#### **XC5200 Performance Benchmarks**

|                        | XC5210-5 | XC5210-3 | %Improvement |

|------------------------|----------|----------|--------------|

| 16-Bit Decoder         | 8 ns     | 6 ns     | 25%          |

| 24-Bit Accumulator     | 39 MHz   | 50 MHz   | 28%          |

| 16-to-1 Multiplexer    | 13 ns    | 9 ns     | 31%          |

| 16-Bit Adder           | 20 ns    | 15 ns    | 25%          |

| 16-Bit Up/Down Counter | 50 MHz   | 65 MHz   | 30%          |

fast carry logic for high speed arithmetic functions. The XC5200 FPGA family continues to lead the industry as the lowest cost/gate programmable logic solution. •

# XC7300 CPLDs & XABEL-CPLD: The Industry's

The combination of ultra-low-cost 44-pin XC7300 CPLDs and easy-to-use XABEL-CPLD development software provides users with the best value in programmable logic. Three XC7300 family members are now available in 44-pin PLCC, PQFP or VQFP packages — the XC7336, XC7336Q and XC7354 devices.

Xilinx 44-pin XC7300 CPLDs provide a greater range of performance and significantly lower costs than PALs and GALs. In fact, the logic from several PAL /GAL devices can be integrated into a single XC7300 CPLD at a lower device cost than the replaced PALs/GALs (and sometimes at a component cost equivalent to a single high-speed PAL). The XC7300 CPLDs also can replace TTL bus drivers, further reducing component count and cost. Advanced system features such as 3.3V or 5V I/O signaling levels and 100% PCI compliance provide support for the newest CPUs and high-performance memories.

44-pin CPLDs also have proven extremely adept at fixing "broken" ASICs. ASIC users are discovering that 44-pin CPLD solutions can be used to safeguard or repair ASIC functionality. Sometimes fixed-function ASICs can be rendered "unusable" by specification changes, process variations that disrupt system timing or design errors. Planning ahead by reserving board space for a small form factor, 44pin CPLD can provide ASIC designers with "system insurance." The CPLD can be used to implement control circuitry or correct sensitive timing paths. In this way, the flexibility to fix unwanted surprises is builtin to the design.

|                             | XC7336 | XC7336Q    | XC7354 | BENEFITS                                          |

|-----------------------------|--------|------------|--------|---------------------------------------------------|

| 22V10 equiv.<br>16V8 equiv. | 3<br>4 | 3<br>4     | 5<br>6 | lower inventory & production costs                |

| macrocells                  | 36     | 36         | 54     |                                                   |

| usablegates                 | 800    | 800        | 1500   |                                                   |

| t <sub>PD</sub>             | 5.0 ns | 10 ns      | 7.5 ns | XC7336-world's fastest CPLD                       |

| l <sub>cc</sub> (typ.)      | 126 mA | 50 mA      | 140 mA | Significant power savings over multiple PALs/GALs |

| 3.3V/5V I/O                 | Y      | Y          | Y      | Interface with high performance memories and MPUs |

| 24 mA high drive I/O        | Y      | Y          | Y      | PCI Bus compliance                                |

| packages                    | PC44,  | PC44,      | PC44   | VQ44 53% smaller than PC44                        |

|                             | PQ44   | PQ44, VQ44 |        |                                                   |

#### Push-Button Software Gets the Job Done

Low-cost XABEL-CPLD software obsoletes all PAL/GAL and low-end CPLD tools and provides push-button ease of use. Based on ABEL 6.0, XABEL-CPLD offers instant productivity enhancement to all PAL/GAL users and makes the migration to higher-density, cost-effective CPLD technology quick and easy. The combination of highly-capable, low-cost silicon and software makes Xilinx 44-pin CPLD solutions the best choice in a world where product development schedules and system component budgets are shrinking at an ever-accelerating pace.

# Best 44-Pin PLD Value

| FEATURES                                                                                                                                                                  | BENEFITS                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Familiar Data I/O ABEL, Windows-based environ-<br>ment for design entry, simulation and fitting                                                                           | Push button design flow improves productivity                                                                                                                                                          |

| Industry-standard-ABEL-HDL supports state machines, high level logic descriptions, truth tables and equation entry                                                        | ABEL-HDL familiar to PAL users, optimized<br>for PAL and CPLD development                                                                                                                              |

| Hierarchical design entry and JEDEC file<br>conversion for integration of existing PAL designs<br>into Xilinx CPLDs                                                       | Enables reuse of existing PAL codes, simplifying design effort                                                                                                                                         |

| Functional simulation with graphical Waveform<br>Viewer and Static Timing Reports                                                                                         | Facilitate rapid design verification                                                                                                                                                                   |

| Advanced XACT <i>step</i> v6 XC7K & XC9K fitter with auto-<br>omatic device selection, multiple pass optimization,<br>partitioning and mapping, and timing driven fitting | Fitter's architecture-specific knowledge frees the user to focus on design functionality                                                                                                               |

| Animated tutorial and on-line help                                                                                                                                        | <ul> <li>Reduces learning curve:</li> <li>tutorial leads users through entire<br/>design process in minutes</li> <li>extensive on-line help places all<br/>documentation a mouse-click away</li> </ul> |

#### ANNOUNCEMENT

## **XC8100 FPGA Product Family is Discontinued**

Citing the strong market success of SRAM and FLASH technologies, Xilinx announced on Aug. 31, 1996, that it will discontinue the  $XC8100^{TM}$  family of one-time programmable antifuse FPGA devices. The XC8100 family, first introduced last autumn, was just entering production.

No layoffs or reductions in R&D spending are associated with this decision. Xilinx employees involved with antifuse development are taking on new duties in other areas of the company. Resources and research and development spending are being redirected to focus more effectively on SRAM-based FPGAs, CPLDs and new opportunities more closely aligned with those products, such as LogiCore modules.

"The XC8100 team successfully developed a number of patented, industry-first innovations in antifuse architecture, design, programming and processes — accomplishments no one else in the entire semiconductor industry has been able to achieve so far with this difficult technology," stated Xilinx CEO Wim Roelandts.

"But, compared to SRAM development, there are very few people working in antifuse. As a result, antifuse will lag be-

hind SRAM, entail disproportionately large development costs, and be relegated to limited markets. For these reasons we believe further investment in antifuse product development are too large to be justified."

A number of options are available to support current XC8100 users, including assistance in moving designs to other pin-compatible Xilinx devices, software upgrades to support other

programmable logic products and refunds for XACT*step*<sup>TM</sup> 8000 software.  $\blacklozenge$

# *Compared* to

SRAM development, there are very few people working in antifuse. As a result, antifuse will lag behind SRAM, entail disproportionately large development costs, and be relegated to limited markets."

# **XC4000EX Family FPGAs Entering Production**

The XC4000EX family elevates the XC4000 series to new heights in density and performance, with up to 125,000 logic

gates and 66 MHz system speeds. Designed "from the ground up" for speed and density using a deep-submicron, triple-layermetal process, the XC4000EX family has abundant routing resources for high utilization and buffered interconnect to provide maximum performance. (*See* XCell #20, page 21.) Xilinx has started sample shipments of the first two members of the high-density XC4000EX family. The XC4036EX, with a typical gate range of 22,000 to 65,000 gates, and the XC4028EX, with a typical gate range of 18,000 to 50,000 gates, will enter volume production in the fourth quarter of this year.

The next member of the family to be introduced is the XC4062XL, featuring a typical gate range of 40,000 to 130,000 gates. The XC4062XL will begin sampling in December. ◆

## Faster XC4000E FPGAs Now Available

Continuing process improvements have led to the release of a new, faster speed grade for  $XC4000E^{TM}$  FPGAs, available now for every member of the device family.

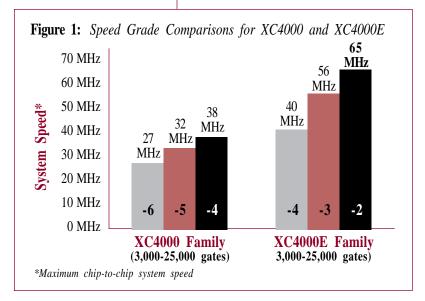

The new -2 speed grade achieves a 15-20 percent performance improvement over the -3 speed grade as a result of a logic block propagation time  $(T_{ILO})$  of 1.6 ns, clock-to-output delays  $(T_{OKPOF})$  of under 5 ns and global-clock-to-out, pin-to-pin delays  $(T_{ICKOF})$  ranging from 8.7 ns for the XC4003E to 10.7 ns for the XC4025E. See **Figure 1** for a comparison of the maxi-

mum chip-to-chip system speeds of the XC4000 and XC4000E devices for their available speed grades.

The XC4000 series (i.e., the XC4000, XC4000E and XC4000EX families) incorporates the world's most widely used FPGA architecture with advanced features such as Select-RAM<sup>TM</sup> memory, wide edge decoders, internal three-state buffers and multiple global clock distribution networks. The high performance levels offered from the -2 speed grade, when combined with these leading-edge architectural features, further extends the range of possible applications for these popular devices.

For example, the capabilities of the XC4000E-2 device enable the delivery of the LogiCore<sup>TM</sup> PCI Initiator module — an implementation that requires extremely high performance levels, especially for FIFO buffer and registered I/O operations (see page 17).

For further technical information, please refer to the product specifications and application notes on WebLINX, the Xilinx web site (www.xilinx.com). For pricing and availability, contact your local Xilinx sales representative.  $\blacklozenge$

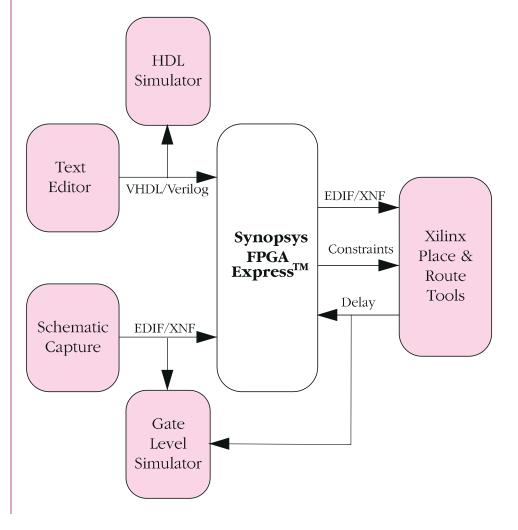

# **Synopsys Introduces**

New Logic Synthesis Tool Tagets Xilinx

Xilinx Alliance member Synopsys unveiled its first entry into the Win95/ Windows NT market at the Design Automation Conference in Las Vegas on June 3. "FPGA Express" is a PC-based FPGA

synthesis tool for leading FPGA architectures. The first version has Xilinx XC3000 family, XC4000 series and XC5200 family support. It is scheduled for production shipment in September. Later versions will support the XC9500 CPLD family, as well as other programmable logic vendors.

FPGA Express is unique in its knowledge of Xilinx architectures and tools, allowing designers who are new to HDL to get high-quality results. The expert user will find the sophisticated controls needed to work with very challenging designs.

FPGA Express is not a rewrite of FPGA Compiler, although for compatibility it uses the same VHDL and Verilog compiler technology as Synopsys' workstation tools (Design Compiler and FPGA Compiler). FPGA Express was designed "from the ground up" with PC users specifically in mind.

**FPGA** Families

The Xilinx/Synopsys relationship was key in the development of this product. "This is an excellent example of Xilinx and one of its Alliance partners working together to meet user requirements with a quality product," noted Wallace Westfeldt, manager of the Xilinx Alliance program.

Xilinx supplied architectural information and assisted in the market research, definition and development of FPGA Express. As a result, FPGA Express makes optimum use of Xilinx device features to maximize density and performance. For example, it includes an automatic module generator that can infer various operations within the HDL source, such as adders, comparators

and multipliers, as well as automatically build the circuits using the dedicated carry logic in the XC4000 series and XC5200 family architectures. FPGA Express also makes full

use of complex

I/O structures present in the Xilinx devices, including the clock enable feature of the XC4000E IOB registers. Global clock buffers are assigned based on an intelligent algorithm that allocates the available buffers based on clock signal fanout while

Continued on the next page

unique in its knowledge of Xilinx architectures and tools, allowing designers who are new to HDL to get high-quality results.<sup>99</sup>

## FPGA Express Continued from the previous page

filtering out gated clocks. If desired, users can specify specific input pins that need to be connected to a global buffer.

Synopsys revised the mapping and optimization algorithms to provide all HDL users with the best possible synthesis results for area, performance and predictability. Testing has shown that FPGA Express can improve area and performance by up to 25% over existing PC-based synthesis tools. Run times are excellent — a 3,000-gate design compiled in under a minute and a 20,000-gate design required approximately 10 minutes using a Pentiumclass computer.

Xilinx also collaborated with Synopsys to integrate FPGA Express into the XACT*step*<sup>™</sup> system. FPGA Express uses a sophisticated constraint-entry GUI, with an "XACT*step*-like" from/to syntax for timing constraints that directly translates to the XACT*step* TIMESPEC format. All netlist and constraint translation is done by FPGA Express, eliminating the need for external translators. The tool outputs Unified Library XNF with group TIMESPECS. The result is a "plug & play" interface between FPGA Express and the XACT*step* tools (v6.0.x and beyond).

#### Pricing and Availability

Sold by Synopsys, FPGA Express starts at \$12,000 (one HDL language and support for one FPGA vendor). It will be available in full production in September, running on Windows 95 and Windows NT-based personal computers.

For more information about FPGA Express contact Bruce Jorgens, Product Line Manager for FPGA Products at Synopsys 415-528-4955. ◆

FPGA Express provides a smooth interface to other Xilinx FPGA development tools

# LogiCore<sup>TM</sup> PCI Intitiator Debuts

Xilinx recently announced the delivery of its second, 100% compliant PCI core, the LogiCore<sup>™</sup> PCI "Master" (Initiator/ Target) module. Previously, the LogiCore PCI "Slave" (Target only) module could only perform slave functions. With the new module, a user can now complete a master interface design in which the Master module acts as a controller for the PCI bus. The implementation of critical paths in the core are pre-defined to ensure PCI compliance. As a result, designers can reduce design risk and cut development time by at least nine months.

The new -2 speed grade for the XC4013E FPGA enables the delivery of the PCI Master module, which requires a high level of design complexity and performance (see article about -2 speed grade on page 14). The LogiCore PCI modules were closely developed with beta users who have successfully implemented the design

in XC4013-2 FPGAs. These devices operate at 33 MHz and include high-speed burst synchronous FIFOs. The modules can be customized to fit individual design requirements, resulting in a cost-effective, singlechip solution.

The LogiCore PCI Master module (LC-DI-PCIM-C) for Xilinx FPGA and HardWire devices, complete with a data sheet, comprehensive user guide and PCI Systems Architecture textbook, is available for designing with Viewlogic schematics, VHDL and Verilog for \$8,995. The PCI Slave module (LC-DI-PCIS-C) is available for \$4,995.

For further information about the LogiCore PCI Interface or other modules in the program, please contact your local Xilinx representative or visit the LogiCore section of the WebLINX World Wide Web site.  $\blacklozenge$

## 17

# Foundation Series Enjoys Successful Introduction

The number of Foundation Series<sup>™</sup> users has been growing rapidly since the inaugural release of this fully integrated PLD design software package in 2Q96. User feedback has been extremely positive, especially regarding the ease-of-use resulting from the tight integration of all the design tools. There also has been high praise for the HDL Wizard, including the HDL Editor, with color coding, and the Language Assistant, with templates for easy and quick coding of VHDL and ABEL-HDL.

The Foundation Series development tools for FPGA and CPLD design include a highly integrated set of Windows-based design tools. Along with the Xilinx XACT *step*<sup>TM</sup> implementation tools, it includes an HDL editor, synthesis compiler, schematic editor and simulator.

Xilinx has added more features to the Foundation packages in the v6.0.1 release, which is now shipping. Features in this release include support for the latest Xilinx device families: the XC9500 CPLDs and XC4000E FPGAs. Both device families are integrated into the easy-touse, shrink-wrapped solution, making it simple to access and convert designs for these new families. All users who purchased Foundation v6.0 will automatically receive this new update. ◆

•Xilinx has

added more features to the Foundation packages in the v6.0.1 release, which is now shipping.<sup>99</sup>

#### **DESIGN HINTS AND ISSUES**

# Benchmarks Confirm XC9500 CPLD

The Xilinx XC9500 CPLD family provides the most-advanced, most-reliable pinlocking capability in the industry. This important feature allows designers to maintain pinouts after making design changes, eliminating costly, time-consuming PC board re-work. CPLDs that do not have adequate pin-locking capability often require pinout changes even after minor design changes, leaving no room for error and no possibility for field upgrades or field customization.

#### **Pin-Locking Issues**

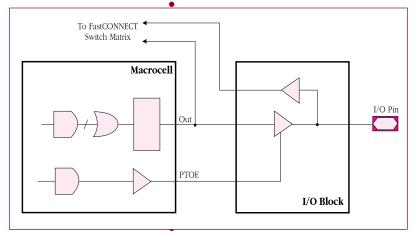

In most CPLDs, each I/O pin is driven directly by a macrocell through an I/O block, as shown in **Figure 1**. When the

Figure 1: Simplified XC9500 I/O Architecture

design is pinlocked, the fitter is forced to map logic into specific macrocells to maintain the pinout. If the device architecture is limited, with inadequate routing in the central switch matrix, the fitter may not be able to place and route the design when the pins are locked.

Some CPLDs use an output routing pool to compensate for their primary routing deficiencies. However, output routing pools introduce additional delays and do not prevent the fitter from having to consume logic resources as routing feedthroughs, impacting both design performance and resource utilization.

Logic requirements also affect the ability of the fitter to place and route the design when the pinout is locked. Slow speed designs with simple, narrow logic functions requiring few inputs, feedbacks and product terms are inherently easier to pinlock than high speed designs with wide fan-in and product term intensive logic functions.

#### The Keys to Reliable Pin-Locking

To address these pin-locking issues, Xilinx XC9500 CPLDs feature abundant routing resources, wide function block fanin and flexible product term allocation. The XC9500 fitter also optimizes the initial placement to maximize the design's pinlocking capability.

Pin-locking restricts the fitter's capability to place design resources; therefore, good routability is crucial. The routing resources of a CPLD determine how much of the logic block resources (inputs, product terms and registers) can be used to accommodate design changes after the pins are locked in a design. In a fully routable CPLD, buried logic can be moved without regards to routing restrictions, freeing function block resources that may be needed by the logic that drives the I/O pins.

The XC9500 family provides the most routing resources of any available CPLD family. All devices in the XC9500 family are 100% routable; if there are enough function block resources to implement the design, it will route.

Wide function block fan-in is another important requirement for pin-locking. Since CPLDs typically are used for highspeed, signal-intensive logic functions, wide function block fan-in is a requirement for implementing functions in a single logic

# Pin-Locking Capabilities

level. The number of available function block inputs affects the fitter's ability to add more signals to any logic that must remain in that function block (because it drives I/O pins). Wide fan-in capability also helps the fitter implement that logic in a single pass though the device.

Each XC9500 function block has 36 inputs from the switch matrix. Competing in-system programmable CPLDs have as few as 16 inputs.

Product term allocation is important to pin-locking because it allows design changes that increase the product term requirement. All XC9500 devices allocate individual product terms from anywhere in the function block to the macrocell that needs them, accommodating logic changes when the design is pinlocked.

In the XC9500 family, up to 90 product terms can be allocated to any macrocell in the function block. This is in contrast to competing CPLDs that restrict the product term availability (from 5 to 32 pterms) on the basis of macrocell location in the function block.

Fitter software is a key component of any successful CPLD pin-locking solution. The fitter must work in conjunction with the device architecture, spreading the outputs to accommodate design changes when the design is pinlocked.

The XC9500 fitter is optimized to take full advantage of the hardware resources of the XC9500 family. The Xilinx fitter is capable of intelligently utilizing all available device resources to retain pinouts and still maintain the required performance, even after significant design changes.

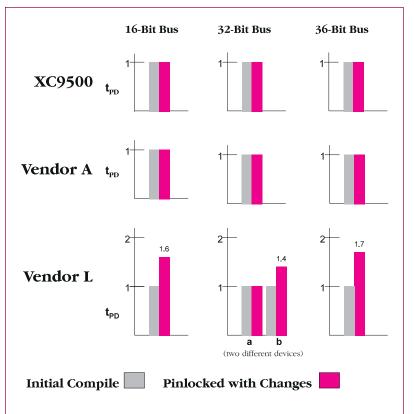

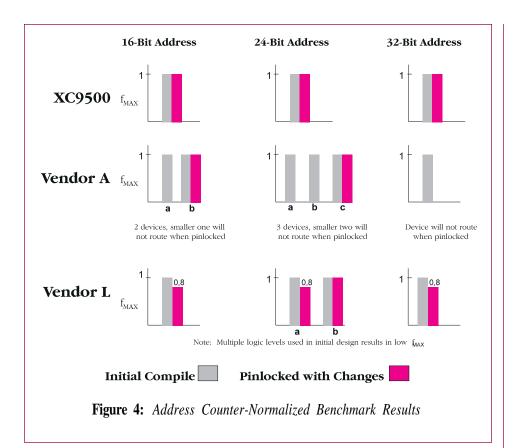

#### The Pin-locking Benchmarks

The following three sets of benchmark data show the relative pin-locking perfor-

mance of the XC9500 CPLDs and two competitor's ISP CPLD families. These benchmarks are based on typical applications such as address decoders, datapath designs and address counters. They illustrate the CPLD device's capability to accommodate design changes while maintaining an acceptable level of design performance; not only must the iterated design reroute when the pinout is maintained, it must do so with minimal impact on design performance. Therefore, all of the benchmark data is normalized to the design performance that is achieved when the fitters are free to choose the pinouts without restrictions.

**••**The benchmark results confirm the superior pin-locking performance of the Xilinx XC9500 family. This performance is consistent across all devices and package types."

#### Address Decoder Benchmark

This benchmark design contains two 16-, 32- or 36-bit busses which are decoded to generate two chip select outputs and is intended to measure the effect of routing resources and function block fan-in on the CPLD's pin-locking

capability. A typical design change involves the correction of an error in which the outputs are decoded incorrectly.

Continued on the next page

Figure 2: Address Decoder-Normalized Benchmark Results

### **XC9500 Benchmarks**

Continued from the previous page

The benchmark results in **Figure 2** demonstrate that both the Xilinx XC9500 family and the Vendor A devices were able to accommodate the design changes without any impact on design performance. Vendor L devices maintained the same pinout, but with a significant (up to 60%) performance penalty. Since the Vendor L devices have 16 input logic blocks, the performance degradation of the 16-bit address decoder can be attributed to poor routing resources while the performance of the 32 and 36-bit decodes is degraded by both poor routing and narrow logic block fan-in.

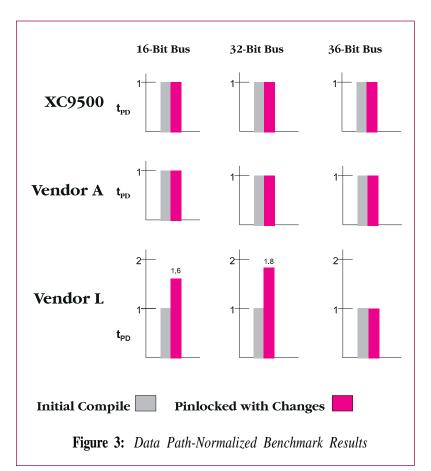

#### **Datapath Benchmark**

This benchmark design measures the affect of routing resources on the CPLD's pin-locking capability. This design contains a single 16-, 32- or 36-bit wide data bus. A typical design change involves the reordering of data bits.

The benchmark results shown in **Figure 3** show that both the Xilinx XC9500 family and Vendor A devices were able to accommodate the design changes without any impact on design performance. Vendor L devices sacrificed performance (up to 80%) to reroute the design when pinlocked. Since only one logic block input was required for each output, this performance degradation can be attributed to poor routing resources, or fitter performance, or both, but cannot be attributed to logic block fan-in.

#### **Address Counter Benchmark**

This benchmark design contains two 16-, 24- or 32-bit loadable address counters loaded from separate buses but with common clock and hold signals. A typical design change alters the initial count load value. This benchmark measures the effect of routing resources and function block fan-in on the CPLDs pin-locking capability

when macrocell feedbacks and other high fan-out signals are involved.

The benchmark results shown in Figure 4 demonstrate the superiority of the XC9500 CPLD architecture. All XC9500 devices were able to accommodate the design changes without any impact on design performance. When Vendor A's routing resources were stressed, performance didn't just degrade, the devices completely failed to route. Vendor L devices used several layers of logic in the initial design, with correspondingly low  $f_{MAX}$ . This enabled the fitter to reroute the design using alternate routing paths, with less performance degradation (20%) than designs initially requiring only one logic level.

#### Conclusions

The benchmark results confirm the superior pin-locking performance of the Xilinx XC9500 family. This performance is consistent across all devices and package types. The wide function block fan-in enables pin-locking of wide, high-speed logic functions. Furthermore, because feedthroughs are not needed for routing, there is no performance degradation due to routing congestion. This timing consistency is as important as routing ability for maintaining pin-locked designs.

The XC9500 CPLD devices feature the industry's best pin-locking capability, eliminating the need for PCB modifications due to design changes. This feature not only shortens design cycles and decreases design costs but also facilitates the use of in-system programmability to upgrade or modify systems in the field. ◆

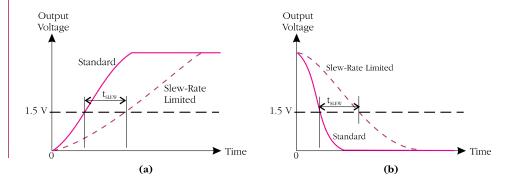

# Using XC9500 Slew Rate Controls

Designers need options for managing the many signal switching conditions that occur in their systems. One simple but effective option is the output slew rate control provided in the XC9500 family CPLDs. This feature permits the simple selection between a slew-rate-limited output drive and a high-speed output drive. The result is easy, convenient control of switching characteristics on a pin-by-pin basis.

Currently, the default condition of the design software provides a slew-rate-limited configuration on all output pins. This is consistent with the default condition provided by the Xilinx FPGA development tools. To obtain faster switching speeds, the designer must configure the appropriate output buffers for the fast slew rate.

Since the slower slew rate is the default, reported timing for an implemented design may be slower than expected for a given speed grade. This is simply due to the fact that a slower slew rate output crosses the switching threshold at a later time than a faster slewing signal (*see Figure 1*). The Xilinx timing report simply adds a small time delay to the output signal, accounting for the added delay.

#### A number of methods are available for specifying the fast slew rate, dependent on the design style chosen.

- For XABEL-CPLD, include one or more of the following directives: XEPLD Property 'FAST ON'; Sets all pins to fast slew rate XEPLD Property 'FAST ON A B C'; Pins A,B and C will be fast & all others remain slew rate limited

- For schematic entry, attach a FAST attribute to the appropriate output pad symbol.

- For Synopsys VHDL, use the following DC Shell commands to set all outputs for the fast slew rate:

```

set_port_is_pad ``*"

set_pad_type -slewrate NONE all_outputs()

insert_pads

```

Alternatively, the fast slew rate can be specified for individual outputs by replacing the second line above with commands of the form:

set\_pad\_type -slewrate NONE port\_name

- For Metamor VHDL, add the Metamor library to your VHDL file with the commands: library metamor; use metamor.attributes.all

- Then, after your signal declarations, assign the fast attribute to a signal with the command: attribute property of port\_name : signal is "Fast"

Figure 1: Effect of slew rate control on output switching times

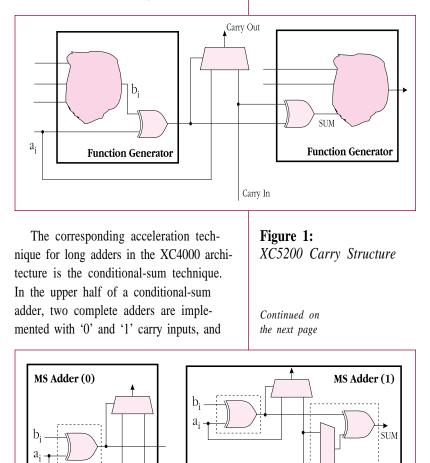

# Designing With

Simple design makes XC5200 carry logic even more flexible than that of XC4000 Series

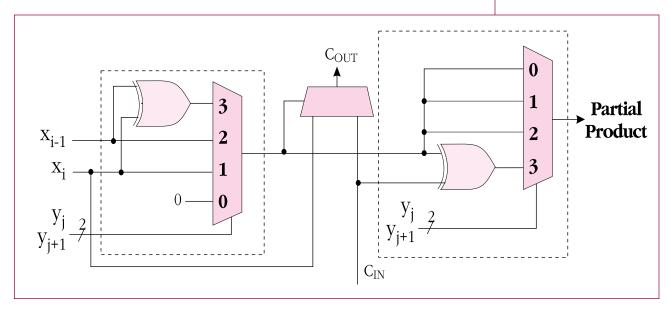

The XC5200 FPGA's carry logic is deceptively simple. While this architecture only provides a series of multiplexers interconnected by dedicated carry nets, the use of function generators to control these multiplexers makes the XC5200 FPGA's carry logic extremely flexible — more flexible, in fact, than the XC4000 carry logic with its multiplicity of modes.

In the XC5200 architecture, one bit of a simple adder uses two function generators and a carry chain multiplexer, as shown in **Figure 1**. However, not all of the function generator's capability is utilized in the basic adder. In the input function generator, the adder input,  $b_i$ , can be any function of the three inputs that are available. For example, one of these inputs could be used as an add/subtract control, inverting  $b_i$  in an XOR gate when necessary.

Similarly, the adder output can be combined in any way with the two remaining function generator inputs. In a typical counter application, these might be used for a multiplexer to load the counter or, alternatively, for an AND gate to provide a synchronous clear.

A more complex example uses this additional capability in a carry-select adder that trades additional logic for higher performance (**Figure 2**). The adder is divided into two sections. The lower half operates normally, but in the upper half two carry chains are used in parallel, one initialized with a '0' and the other with a '1.' The carry output of the lower half is used to select which carry chain is used to complete the sum. The carry propagates simultaneously in the upper and lower halves of the adder; thus, the settling time is reduced.

# **Carry Logic**

Since a single function generator can both select the carry and complete the sum, the incremental cost over the basic adder is only 25%. The direct access to the carry chain minimizes the timing overhead associated with this technique, which is effective even for relatively short adders.

CIN=0

XC5200 Carry-Select Adders

Figure 2:

C<sub>IN</sub>=1

COUT

LS Adder

23

additional CLBs are required to select between the outputs of these adders according to the carry output from the lower half. The technique is only effective for relatively long adders; the incremental cost is 100%.

It is interesting to note that, in the XC5200 architecture, the carry-select and conditional-sum techniques cannot always

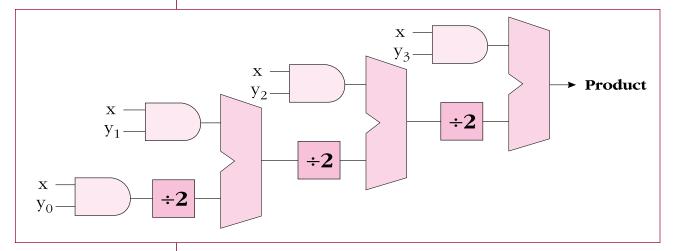

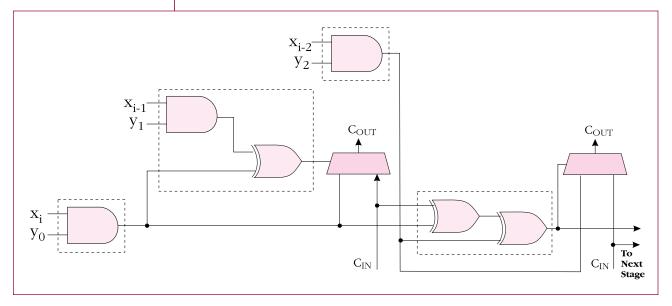

In a simple multiplier, the product is computed using a cascade of gated adders together with appropriate shifts (**Figure 3**). A more detailed view of a single bit slice through the first two adders of this multiplier is shown in **Figure 4**. One of the two AND gates that precedes the first adder is combined into the function generator that controls the carry multiplexer. The other

**Figure 3:** 4-Bit Cascade Multiplier

be distinguished. Both sums of the conditional-sum adder can be completed in the same function generator. This function generator can be further used to select between them. If this is done, all the function-generator truth tables and all the interconnections become identical to the carryselect adder. This should not be surprising, however, since both techniques implement the same uniquely defined adder function. AND gate, however, must use a separate function generator because there is a fanout point at the second input to the adder.

In the second and subsequent adders, the AND gates again use separate function generators. This permits the XOR gates that complete the previous sums to be merged adder inputs, thus saving both logic resources and critical-path delay. If, instead, the AND gates had been merged into the

**Figure 4:** *Bit-Slice of First Two Adders*

inputs, the XOR gates would have required function generators. In this case, the resource utilization would have been the same, but the delay longer. Only in the final adder is a separate function generator needed for the XOR gate.

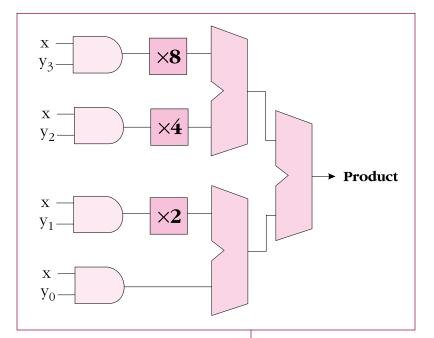

The speed of the multiplier can be increased by rearranging the cascade of adders into a tree, as in **Figure 5**. After the first set of adders, the input of each adder can absorb the output XOR gate of one of the two preceding adders, as described in the cascade multiplier. The other preceding adder, however, must use a separate function generator for its XOR gate.

In the first set of adders, the objective is to multiply the X input by bit pairs of Y, creating products that are 0X, 1X, 2X or 3X. This is usually achieved by gating X and 2X into an adder, as is shown in Figure 5.

However, a different, more direct approach may be used in XC5200 FPGA.

A bit slice of this more efficient approach is shown in **Figure 6**. The carry chain is only used to add X and 2X when the 3X output is required. Otherwise, 0, X or 2X is selected in the first function generator and routed to the second function generator where it passes through unaltered. While the carry chain continues to operate in a meaningless way, it cannot damage itself, and its outputs are not required. When 3X is required, the first function generator XORs X and 2X to control the carry chain in a normal addition. The sum is completed in the XOR gate that precedes the multiplexer in the second function generator.

**Figure 5:** Adder-Tree Multiplier

**Figure 6:** *First Stage of a Tree-Adder Multiplier*

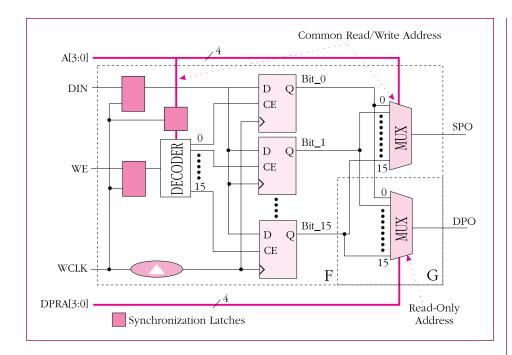

# XC4000 Series Select-RAM Memory:

# Advantages and Uses

The XC4000 Series of FPGA devices (i.e., the XC4000E and XC4000EX families, and their low-voltage counterparts, the XC4000L and XC4000XL families) includes several architectural improvements over the highly-successful XC4000 FPGA family. One of the most important new features is Select-RAM<sup>™</sup> memory. Select-RAM memory can be defined as the capability of programming the look-up tables in Configurable Logic Blocks (CLBs) as ROM or as single- or dual-port RAM, with edgetriggered (synchronous) or level-sensitive (asynchronous) timing. Select-RAM memory also can be initialized to a known value in all RAM and ROM modes.

Select-RAM memory is unique in its range of options and ability to deliver highspeed dual-port memory. The advantages of the Select-RAM capability include flexibility, increased ease-of-use, shorter design cycles and increased performance.

#### Flexibility

Clearly, the options of edge-triggered or level-sensitive and single-port or dual-port RAM provide a wide selection of choices for the designer. The distributed nature of the RAM, which is implemented in individual CLBs, also contributes to the flexibility of Select-RAM memory. Only sufficient CLBs to implement a given memory block need be allocated as RAM: the memory block size can be scaled to exactly match the requirements of the application. Each RAM block can be placed close to related logic. There is no need to consume a large block of dedicated memory to implement a small RAM function, nor to route control and data lines across the device to reach such dedicated blocks. Each CLB can be individually configured, so the designer can "mix and match" RAM modes. Select-RAM is the most flexible memory implementation available in an FPGA today.

#### Ease of Use

Traditional RAM capability, now referred to as the level-sensitive or asynchronous option to Select-RAM memory, has never been simple to use. Meeting the required timing relationships often involved careful layout and detailed timing analysis. To guarantee correct behavior, a 2X clock is typically required, in order to generate the Write Enable during the third quadrant of the write clock cycle. This type of RAM is the only available option in the original XC4000 family devices.

None of these delicate timing relationships need be maintained when using one of the edge-triggered Select-RAM modes available in XC4000-Series devices. Instead, writing to a memory block is just like writing to a data register: set up the address and data, enable the RAM and apply the effective clock edge. A conceptual model for a Select-RAM block in edge-triggered mode is shown in the **Figure 1**.

The ability to initialize RAM, as well as ROM, as part of device configuration eliminates the need for logic to perform that initialization. Reduced logic results in smaller, simpler and more reliable designs.

All of the Select-RAM options are directly and easily implemented using any of the schematic entry, MemGen memory block generator tool, X-BLOX<sup>TM</sup> schematicbased synthesis, or HDL synthesis design environments. Detailed information on how to use these tools to implement Select-RAM is available in the new Xilinx application note "Using Select-RAM Memory in XC4000 Series FPGAs."

#### Figure 1: XC4000 Series Conceptual Model for Edge-Triggered Memory

#### Shorter Design Cycles

The ease-of-use associated with edgetriggered memory design results in shorter design cycles as compared to using levelsensitive RAM. The design, simulation and testing steps are all simplified.

#### Performance

As mentioned above, level-sensitive RAM designs may require both a 2X clock and significant signal manipulation to meet the stringent timing requirements on the Write Enable signal. The Address and Data inputs must be set-up at the RAM input pins by the time the Write Enable signal arrives, typically halfway through the write cycle.

When the same design is implemented using edge-triggered RAM, Address and Data may change in response to (for example) the rising edge of the input clock. The Write can occur on the next rising edge of the same clock. Therefore, the Address and Data have the full write cycle to set-up at the RAM input pins. The result is a memory block that operates at approximately twice the speed of the level-sensitive version of the design. When the simultaneous read/write capability of the dual-port Select-RAM option is taken into account, data throughput can be doubled again, resulting in a total four-fold increase in effective data rates. These results are demonstrated in a simple FIFO design in the Xilinx application note "Implementing FIFOs in XC4000 Series RAM."

Distributed RAM provides an additional speed advantage: locating RAM blocks closer to related logic minimizes routing delays on critical paths.

#### Uses of Select-RAM Memory

The edge-triggered RAM capability can and should be used in all new designs requiring RAM. These applications include register files, FIFO buffers, multipliers, shift registers and pseudo-random sequence generators.

The dual-port option adds the ability to read and write simultaneously from two different addresses. This ability considerably simplifies FIFO designs and is useful for constructing dual-port register files.

The Application Notes referenced in this article are available on the Xilinx WebLINX web site at www.xilinx.com, or by contacting the Xilinx Technical Hotline.

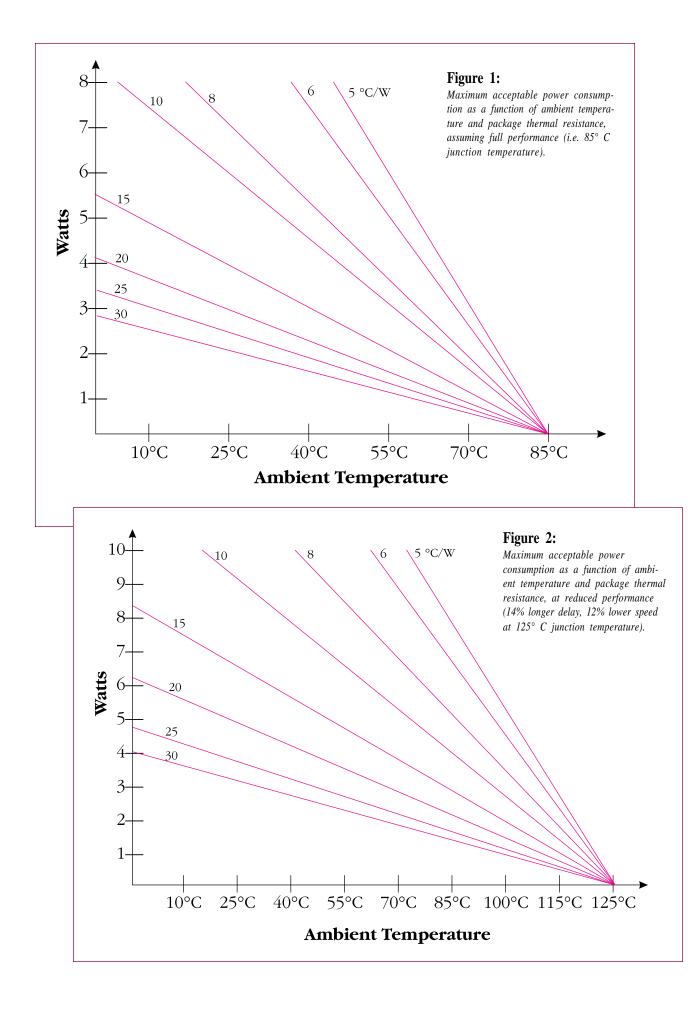

# Trading Off Among the Three Ps

# Power, Package & Performance

There are well-defined relationships between chip power consumption, package thermal characteristics, ambient and junction temperature, and device performance.

In many cases, the user has no control over the maximum ambient temperature, but can choose the device and package, and then strive for an acceptable power consumption.  $\Theta_{J-A}$  is expressed in degrees C of junction temperature rise over the ambient temperature for every Watt dissipated in the device.  $\Theta_{J-A}$  is primarily a function of the package and the airflow, with die size a secondary factor. (Larger die have a lower  $\Theta_{J-A}$  value). See Table 1.

When the junction is hotter than 85°C, where Xilinx tests and guarantees perfor-

In other cases, The governing equation is chip, package,  $T_{I} = T_{A} + P \times \Theta_{IA}$ power consumption and where  $T_{I}$  = junction temperature ambient tem- $T_{\Lambda}$  = ambient temperature perature are  $\Theta_{J-A}$  (Theta J-A) = Thermal resistance of the package-die combination given, and the resulting achievable P = power dissipationperformance level must be

arantees performance parameters, delays increase 0.35% for every additional degree C. At 125°C, the maximum allowed junction temperature in a plastic package, delays are 14% longer, and

calculated. If performance cannot be sacrificed, thermal management techniques (e.g, airflow and heat sinks) can be used to lower the thermal resistance. speed is thus 12% lower than the guaranteed values in the data book and the software. In ceramic packages, the maximum allowed junction temperature is 150°C. ◆

# Typical thermal resistance for various packages with and without airflow

| PACKAGE | STILL AIR | <b>250 FT/MIN</b><br>(1.3 M/S) | 500 FT/MIN<br>(2.5 ⊮/s) | <b>750 FT/MIN</b><br>(3.8 k/s) |      |

|---------|-----------|--------------------------------|-------------------------|--------------------------------|------|

| HQ304   | 11        | 7                              | 6                       | 5                              | °C/W |

| HQ240   | 12        | 9                              | 7                       | 6                              | °C/W |

| HQ208   | 14        | 10                             | 8                       | 7                              | °C/W |

| MQ240   | 17        | 12                             | 11                      | 10                             | °C/W |

| MQ208   | 18        | 14                             | 13                      | 12                             | °C/W |

| PQ240   | 23        | 17                             | 15                      | 14                             | °C/W |

| PQ208   | 32        | 23                             | 21                      | 19                             | °C/W |

| PQ160   | 32        | 24                             | 21                      | 20                             | °C/W |

| PQ100   | 33        | 29                             | 28                      | 27                             | °C/W |

| PC84    | 33        | 25                             | 21                      | 17                             | °C/W |

| TQ100   | 31        | 26                             | 24                      | 23                             | °C/W |

| VQ100   | 38        | 32                             | 30                      | 29                             | °C/W |

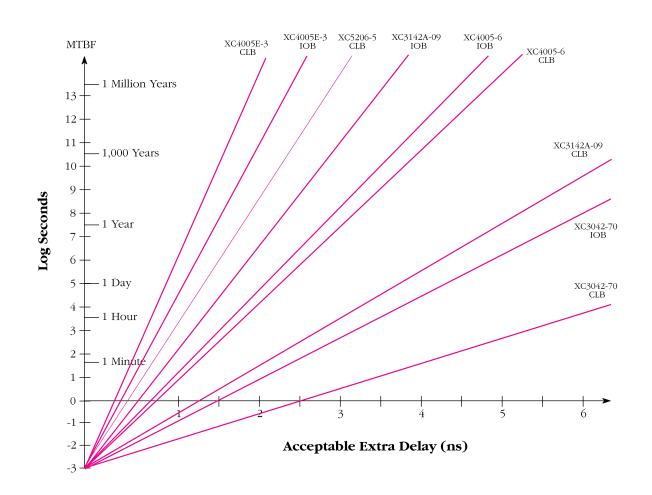

# Metastability Recovery in Xilinx FPGAs

Whenever a clocked flip-flop synchronizes an asynchronous input, there is a small probability that the flip-flop output will exhibit an unpredictable delay. This happens when the input transition not only violates the setup and hold-time specifications, but actually occurs within the tiny timing window where the flip-flop accepts the new input. Under these circumstances, the flip-flop can enter a symmetricallybalanced transitory state, called a metastable state.

While the slightest deviation from perfect balance will cause the output to revert to one of its two stable states, the delay in doing so depends not only on the gainbandwidth product of the circuit, but also on how perfect the balance was and on the noise level within the circuit; the delay can, therefore, only be described in statistical terms. The problem for the system designer is not the illegal logic level in the balanced state (it's easy enough to translate that arbitrarily to either a 0 or a 1), but the unpredictable timing of the final change to a valid logic state. If the metastable flip-flop drives two destinations with differing path delays, one destination might clock in the final data state while the other does not.

#### Metastability Measurements

Recently, the metastable delays of four different Xilinx FPGA devices were measured: two cutting-edge devices using 0.5 micron, 3-layer-metal technology, the