#### Reed-Solomon Encoder

January 12, 1998

**Product Specification**

# Integrated Silicon Systems, Ltd.

50 Malone Rd Belfast BT9 5BS Northern Ireland

Phone: +44 1232 664664

Fax: +44 1232 669664

E-Mail: info@iss-dsp.com

URL: www.iss-dsp.com

#### **Features**

- Programmable solution for high data rate Reed-Solomon encoding

- ISS can configure to support a range of standards involving Reed-Solomon encoding, e.g. European Telecommunication Standard 300 421 and 300 429.

- Architecture can be customized using the following parameters:

- Symbol size

- Number of parity symbols

- Field polynomial

- Generator polynomial

- Single encoder implementation supports any valid data block length

- Systematic code structure where each code word can be partitioned into original data block and appended parity symbols

- Encoder can process continuous or burst data

- Supports high speed (>570 Mbps) applications

- Symbol-wide inputs and outputs, clocked by a single symbol-rate clock

- Simple interface allows easy integration into larger system

# **Applications**

- Digital video and audio broadcast

- · Digital satellite broadcast

- Data storage and retrieval systems (e.g. hard disks, CD-ROM etc)

| AllianceCORE™ Facts      |                               |                    |  |  |  |

|--------------------------|-------------------------------|--------------------|--|--|--|

| Core Specifics           |                               |                    |  |  |  |

| Device Family            | Spartan                       | XC4000E/XL         |  |  |  |

| CLBs Used                |                               |                    |  |  |  |

| IOBs Used                | See Table 1                   |                    |  |  |  |

| System Clock fmax        |                               |                    |  |  |  |

| Device Features          |                               |                    |  |  |  |

| Used                     |                               | Carry Logic, RPM   |  |  |  |

| Supported Dev            | ices/Resources                | Remaining          |  |  |  |

|                          | See Table 1                   |                    |  |  |  |

| Pro                      | vided with Core               |                    |  |  |  |

| Documentation            | Core Documentation            |                    |  |  |  |

| Design File Formats      | XNF or NGD netlis             |                    |  |  |  |

| Constraint Files         | Timespec, .cst and .tnm files |                    |  |  |  |

| Verification Tool        |                               | Test Vectors       |  |  |  |

| Schematic Symbols        | None                          |                    |  |  |  |

| Evaluation Model         | None                          |                    |  |  |  |

| Reference designs &      |                               |                    |  |  |  |

| application notes        | None                          |                    |  |  |  |

| Additional Items         | Bit-accurate C                | Model is available |  |  |  |

| Design Tool Requirements |                               |                    |  |  |  |

| Xilinx Core Tools        |                               | Alliance 1.3       |  |  |  |

| Entry/Verification       | Synopsys Design Compiler      |                    |  |  |  |

| Tool                     | Synopsys VSS                  |                    |  |  |  |

| Support                  |                               |                    |  |  |  |

| Support provided by ISS. |                               |                    |  |  |  |

# **General Description**

The Reed-Solomon encoder is a Xilinx FPGA-based core for systems where data error detection/correction is required. The core implements the full functionality of a general Reed-Solomon encoder and all necessary interface circuitry using a single Xilinx FPGA.

The source code version of the core is extremely flexible due to its parameterized design, and can be rapidly configured for a wide variety of applications. Table 1 shows density and performance metrics for specific implementation examples. ISS will customize and provide a Xilinx-specific implementation of the core tailored to the needs of your application, (see Ordering Information).

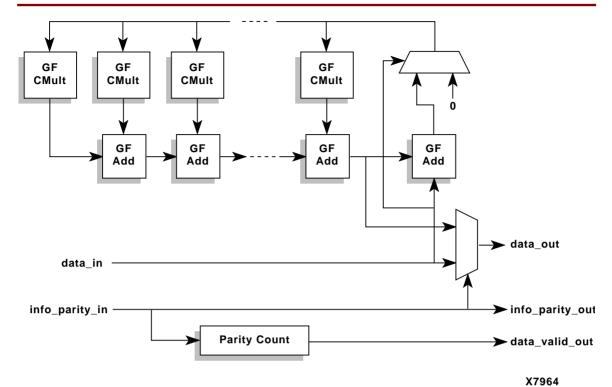

Figure 1: Reed Solomon Encoder Block Diagram

**Table 1: Example Encoder Implementations**

|                               | Example #1      | Example #2     | Example #3   | Example #4     |

|-------------------------------|-----------------|----------------|--------------|----------------|

| Parity Symbols                | 16              | 16             | 16           | 8              |

| Bits/Symbol                   | 8               | 8              | 8            | 4              |

| Device                        | XC4005XL-1 PC84 | XC4005E-3 PC84 | XCS10-3 PC84 | XC4003E-3 PC84 |

| CLBs Used                     | 105             | 98             | 106          | 24             |

| IOBs Used                     | 20              | 21             | 19           | 13             |

| System Clock f <sub>max</sub> | 72.2 MHz        | 42 MHz         | 49.3 MHz     | 48 MHz         |

| CLBs Remaining                | 91              | 98             | 90           | 172            |

| IOBs Remaining                | 41              | 40             | 42           | 48             |

# **Functional Description**

The Reed-Solomon encoder core is partitioned into modules as shown in Figure 1 and described below.

#### **GF CMult**

This block performs the multiplication of two symbol values over a Galois Field that is defined by the choice of the number of bits per symbol. For example, choosing 8 bits per symbol, the block performs multiplication over GF(2<sup>8</sup>). One of the multiplier inputs is a constant, corresponding to a co-

efficient value from the generator polynomial, which is also customizable by the user. Multiplication is carried out using a bit-parallel, polynomial basis architecture. One GF CMult block is required for each parity symbol to be generated.

#### **GF Add**

The GF Add block performs the addition of two symbol values over the appropriate Galois Field.

#### **Parity Count**

The parity count block counts the number of parity symbols

produced by the encoder for each block of data. The number of valid parity symbols is twice the maximum number of errors that are to be corrected. Any additional symbols produced by the encoder are caused by spurious symbol values that may exist between successive data blocks when burst data is being processed. These spurious symbols are marked in the output data stream by changing the value of the "data\_valid\_out" signal from high to low.

#### **Pinout**

The pinout of the Reed-Solomon Encoder has not been fixed to specific FPGA I/O, allowing flexibility with a users application. Signal names are shown in the block diagram of Figure 1 and in Table 2.

**Table 2: Core Signal Pinout**

| Signal          | Signal Direction | Description                                         |

|-----------------|------------------|-----------------------------------------------------|

| DATA_IN [x:0]   | Input            | Input data symbols                                  |

| INFO_PARITY_IN  | Input            | Marks valid input infor-<br>mation symbols          |

| CLK             | Input            | Symbol Clock                                        |

| RESET           | Input            | System Reset, active high                           |

| DATA_OUT [x:0]  | Output           | Output data symbols                                 |

| INFO_PARITY_OUT | Output           | Marks valid output infor-<br>mation symbols         |

| DATA_VALID_OUT  |                  | Marks valid output infor-<br>mation and parity sym- |

|                 | Output           | bols.                                               |

#### **Verification Methods**

The core has been fully tested across a wide range of parameter settings, using input sequences compatible with many international digital video, audio and satellite standards.

# **Recommended Design Experience**

Familiarity with system standards relevant to the particular application is assumed. A basic understanding of Reed-Solomon encoding is useful, but not essential.

# **Available Support Products**

A C model of the Reed-Solomon encoder is available to assist in functional verification and system integration.

ISS also supplies a complete line of peripheral cores that can be integrated with the Reed Solomon Encoder and De-

coder cores for a complete forward error correction system using Xilinx FPGAs. For more information, contact ISS directly regarding:

- Block and convolution interleavers and deinterleavers

- · Scramblers and descramblers

- · Sync detection and insertion

- Convolution encoders

- Viterbi decoders

### **Ordering Information**

The Reed Solomon Encoder is available for purchase directly from ISS. The implementation will vary depending upon your application. To determine what is required for your system, fill out and fax the attached Implementation Request Form to ISS at +44 1232 669664.

#### **Related Information**

# **European Telecommunications Standards Institute**

For information on European digital broadcasting systems standards contact:

European Telecommunications Standards Institute 06921 Sophia Antipolis Cedex

France

Phone: +33 92 94 42 00 Fax: +33 93 65 47 16

### Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124

Phone: +1 408-559-7778

Fax: +1 408-559-7114

URL: www.xilinx.com

For general Xilinx literature, contact:

Phone: +1 800-231-3386 (inside the US) +1 408-879-5017 (outside the US)

E-mail: literature@xilinx.com

For AllianceCORE™ specific information, contact:

Phone: +1 408-879-5381

E-mail: alliancecore@xilinx.com

URL: www.xilinx.com/products/logicore/alliance/

tblpart.htm

# **Reed-Solomon Implementation Request Form**

| To:<br>FAX:<br>E-mai                 | Integrated Silicon Systems, Inc.<br>+44 1232 669664<br>il: info@iss-dsp.com                                                                                                                                                                                              | 10. | Indicate error statistics reporting requirement(s): Signal to show position of corrected errors Signal to show position of uncorrected blocks                                                                                       |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| From:                                |                                                                                                                                                                                                                                                                          |     | Other (please specify)                                                                                                                                                                                                              |

| Comp                                 | any:                                                                                                                                                                                                                                                                     | 11. | Indicate required control signals:                                                                                                                                                                                                  |

| Name                                 | :                                                                                                                                                                                                                                                                        |     | low to high transition at start of codeword,high                                                                                                                                                                                    |

| Addre                                | ss:                                                                                                                                                                                                                                                                      |     | to low transition at end of codeword low to high transitional start of codeword, high                                                                                                                                               |

| Count                                | ry:                                                                                                                                                                                                                                                                      |     | to low transition at start of parity symbols                                                                                                                                                                                        |

| Phone                                | e:                                                                                                                                                                                                                                                                       |     | delayed control signals available at output other (please specify)                                                                                                                                                                  |

| Fax:                                 |                                                                                                                                                                                                                                                                          |     | otrier (please specify)                                                                                                                                                                                                             |

| E-mai                                | l:                                                                                                                                                                                                                                                                       | 12. | Please specify any additional requirements:                                                                                                                                                                                         |

| Solom<br>out an<br>ate qu<br>rics fo | onfigures and ships Xilinx netlist versions of the Reed non cores customized to your specification. Please fill not fax this form so ISS can respond with an appropri-<br>uotation that includes performance and density metar the target Xilinx FPGA.  mentation Issues |     | If interleaver and/or deinterleaver functions are required, specify maximum depth of interleaving:  If the interleaver and/or deinterleaver are required is the depth of interleaving to be programmable and if so, to what degree? |

|                                      | ndicate your exact requirement: Reed-Solomon encoder                                                                                                                                                                                                                     | Bus | siness Issues                                                                                                                                                                                                                       |

| -                                    | Reed-Solomon decoder Interleaver                                                                                                                                                                                                                                         | 15. | Indicate timescales of requirement:                                                                                                                                                                                                 |

| _                                    | Deinterleaver                                                                                                                                                                                                                                                            |     | a. date for decision b. date for placing order                                                                                                                                                                                      |

| 2. N                                 | Maximum symbol rate:                                                                                                                                                                                                                                                     |     | c. required delivery date                                                                                                                                                                                                           |

| 3. N                                 | Number of bits per symbol:                                                                                                                                                                                                                                               | 16. | Indicate your area of responsibility: decision maker                                                                                                                                                                                |

| 4. lı                                | ndicate clock availability:                                                                                                                                                                                                                                              |     | budget holderrecommender                                                                                                                                                                                                            |

| -                                    | Bit clock Symbol Clock                                                                                                                                                                                                                                                   |     | recommender                                                                                                                                                                                                                         |

| -                                    | Both                                                                                                                                                                                                                                                                     | 17. | Has a budget been allocated for the purchase? Yes No                                                                                                                                                                                |

| 5. C                                 | Code generator polynomial (e.g. (x+a¹)(x+a²))                                                                                                                                                                                                                            | 18. | What volume do you expect to ship of the product that will use this core?                                                                                                                                                           |

| 6. F                                 | Field generator polynomial (e.g. x8+x4+x3+x2+1)                                                                                                                                                                                                                          | 19. | What major factors will influence your decision? cost                                                                                                                                                                               |

| 7. N                                 | Number of errors:                                                                                                                                                                                                                                                        |     | customization testing                                                                                                                                                                                                               |

| 8. (                                 | Codeword length/format (e.g. 204, 188):                                                                                                                                                                                                                                  |     | implementation size                                                                                                                                                                                                                 |

|                                      |                                                                                                                                                                                                                                                                          | 20. | Are you considering any other solutions?                                                                                                                                                                                            |

|                                      | Erasure support required:<br>/es No                                                                                                                                                                                                                                      |     |                                                                                                                                                                                                                                     |