# 16-Word Deep Registered Look-Up Table

February 8, 1998

**Product Specification**

Xilinx Inc. 2100 Logic Drive San Jose, CA 95124 Phone: +1 408-559-7778 Fax: +1 408-559-7114 E-mail: dsp@xilinx.com URL: www.xilinx.com

X7548

## **Features**

- Drop-in modules for the XC4000E, EX, and XL families

- High performance and density guaranteed through Relational Placed Macro (RPM) mapping and placement technology

- Available in Xilinx CORE Generator

## **Functional Description**

This macro is a registered look-up table, or ROM-based storage array. This is equivalent to an N-bit wide, 16-bit deep ROM. The address pins, A[3:0], are used to address the LUT data. The output of the LUT is registered on the rising edge of the C (CLOCK) signal with the CE (CLOCK ENABLE) signal asserted (HIGH).

The ROM data is defined via the INIT attribute. The INITs are attached to the LUT by the CORE Generator, which defines the memory's contents.

## Pinout

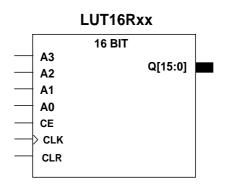

Signal names for the schematic symbol are shown in Figure 1 and described in Table 1.

Figure 1: Core Schematic Symbol

#### **Table 1: Core Signal Pinout**

| Signal    | Signal<br>Direction | Description                                   |

|-----------|---------------------|-----------------------------------------------|

| A[3:0]    | Input               | ADDRESS – the ROM loca-                       |

|           |                     | tion, predefined by the INIT                  |

|           |                     | value, is decoded from these                  |

|           |                     | Address pins and presented                    |

|           |                     | to the register's input                       |

| CE        | Input               | CLOCK ENABLE – active                         |

|           |                     | high signal used to enable                    |

|           |                     | the transfer of data from the                 |

|           |                     | LUT to the output register                    |

| CLK       | Input               | CLOCK – clocks the output                     |

|           |                     | register on the rising edge                   |

| CLR       | Input               | ASYNCHRONOUS CLEAR                            |

|           |                     | <ul> <li>clears the register. Does</li> </ul> |

|           |                     | not require the Clock or CE                   |

|           |                     | signal                                        |

| Q[N-1, 0] | Output              | REGISTER LUT DATA                             |

|           |                     | OUTPUT – the registered                       |

|           |                     | output of the look-up table                   |

### **CORE Generator Parameters**

The CORE Generator dialog box for this macro is shown in Figure 2. The parameters are as follows:

- **Component Name**: Enter a name for the output files generated for this module.

- Data Width: Select an input bit width from the pull-down menu. The valid range is 2-31.

- LUT Data: Enter the data for each address location.

- Radix: Select the radix of the LUT data: Hexadecimal or Decimal.

- **Sign**: If the radix is decimal, select the sign of the constant value: Signed or Unsigned. If the radix is hex, the constant is always signed.

- Read From File: In the pop-up window, set the name of the file that contains your LUT data.

| 🐃 16 Word Deep Registered Look-Up Table 👘 🔲 🗙 |   |          |           |  |  |

|-----------------------------------------------|---|----------|-----------|--|--|

| Component Name:                               |   |          |           |  |  |

| Data Width: 12 💌                              |   |          |           |  |  |

| LUT Data                                      |   |          |           |  |  |

| Add. 0                                        |   | Add. 8   |           |  |  |

| Add. 1                                        |   | Add. 9   |           |  |  |

| Add. 2                                        |   | Addr. A  |           |  |  |

| Add. 3                                        |   | Addr. B  |           |  |  |

| Add. 4                                        |   | Addr. C  |           |  |  |

| Add. 5                                        |   | Addr. D  |           |  |  |

| Add. 6                                        |   | Addr. E  |           |  |  |

| Add. 7                                        |   | Addr. F  |           |  |  |

| Radix Sign                                    |   |          |           |  |  |

| 🛛 🛈 Hex                                       | 0 | Signed   | Read From |  |  |

| O Decii                                       |   | Jnsigned | File      |  |  |

|                                               |   |          |           |  |  |

|                                               |   |          |           |  |  |

| Generate Cancel                               |   |          |           |  |  |

|                                               |   |          |           |  |  |

Figure 2: CORE Generator Dialog Box

# **Ordering Information**

This macro comes free with the Xilinx CORE Generator. For additional information contact your local Xilinx sales representative, or e-mail requests to dsp@xilinx.com.

## **Core Resource Utilization**

Table 2 shows the number of CLBs required for each available bit width.

#### Table 2: Bit Width versus CLB Count

| Bit Width | CLB Count |

|-----------|-----------|

| 2         | 1         |

| 3         | 2         |

| 4         | 2         |

| 5         | 3         |

| 6         | 3         |

| 7         | 4         |

| 8         | 4         |

| 9         | 5         |

| 10        | 5         |

| 11        | 6         |

| 12        | 6         |

| 13        | 7         |

| 14        | 7         |

| 15        | 8         |

| 16        | 8         |

| 17        | 9         |

| 18        | 9         |

| 19        | 10        |

| 20        | 10        |

| 21        | 11        |

| 22        | 11        |

| 23        | 12        |

| 24        | 12        |

| 25        | 13        |

| 26        | 13        |

| 27        | 14        |

| 28        | 14        |

| 29        | 15        |

| 30        | 15        |

| 31        | 16        |

| 32        | 16        |