XC1701, XC1701L & XC17512L Family

## **Description**

The XC1701/L and XC17512L Serial Configuration PROMs provide easy-to-use, cost-effective configuration memory for Xilinx Field Programmable Gate Arrays.

These devices use a simple serial-access procedure to configure one or more LCA devices. The user can select the polarity of the reset function by programming a special bit. These devices are fully compatible and can be cascaded with other members of the XC1700 family of devices.

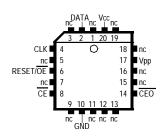

### 20-Pin PLCC Pin Assignments

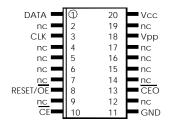

## 20-Pin SOIC Pin Assignments

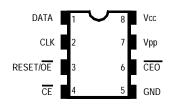

### 8-Pin DIP Pin Assignments

The XC1701/L and XC17512L devices are one-time programmable (OTP), devices organized as follows:

XC1701/L 1,048,576 x 1 bit

XC17512L 524,288 x 1 bit

XC1701, XC1701L & XC17512L Family

## **Programming Overview**

All the XC1701/L and XC17512L SPROMs are internally organized in rows, each row containing eight (8) 64-bit words. Additional non-data rows are used to read the Manufacturer's/Device ID and set the Reset Polarity and cannot be used to store configuration data. The device programmer should prompt the user for the desired Reset Polarity.

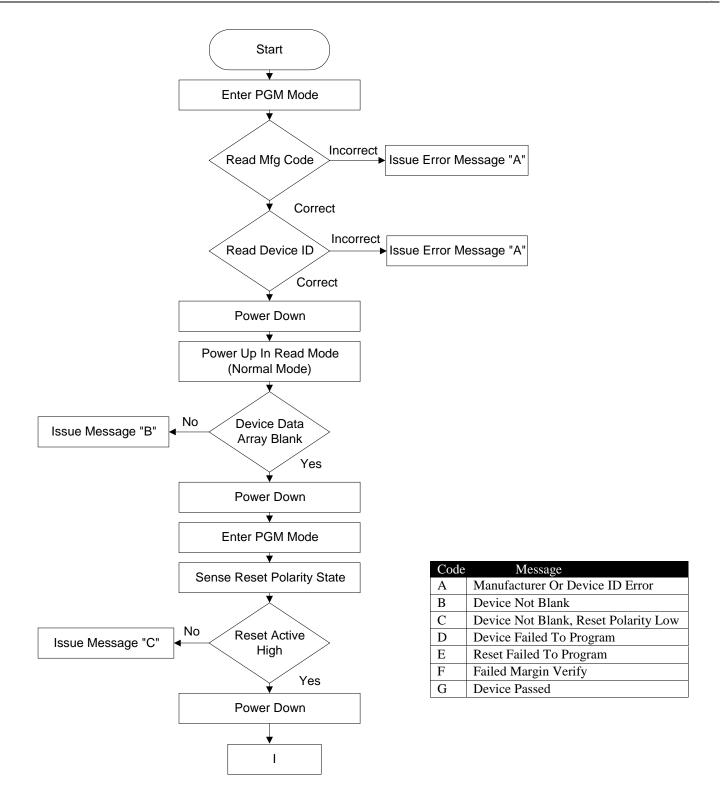

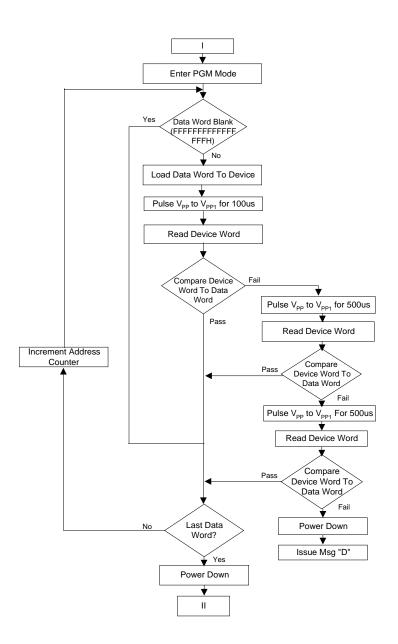

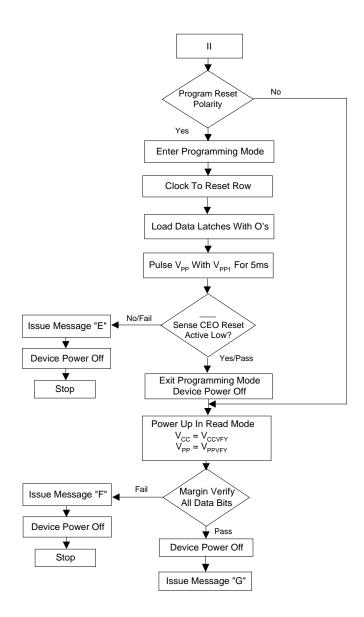

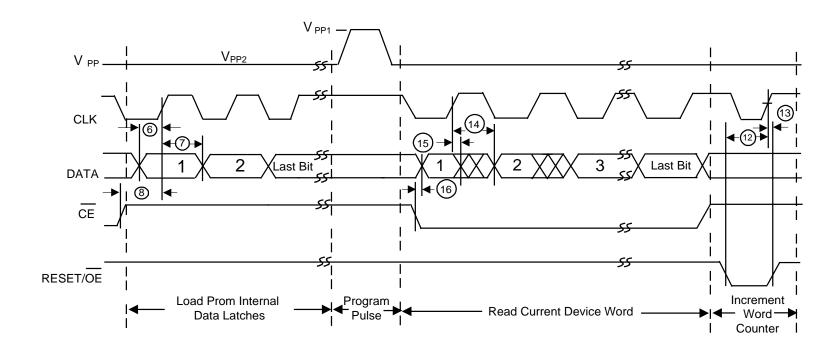

Figure 1 shows the flow of how the SPROMs are programmed. See Figure 2 for the programming cycle overview and Figure 4 for the details of the programming cycle.

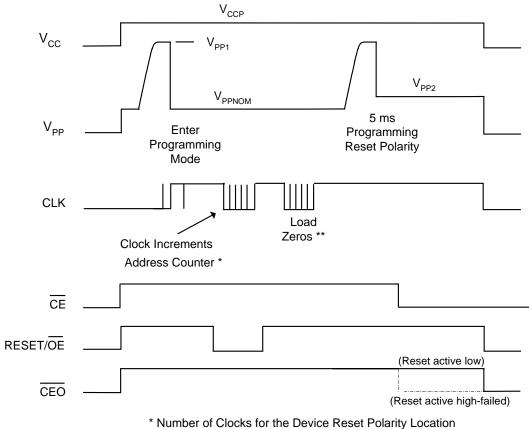

### **Enter Programming Mode**

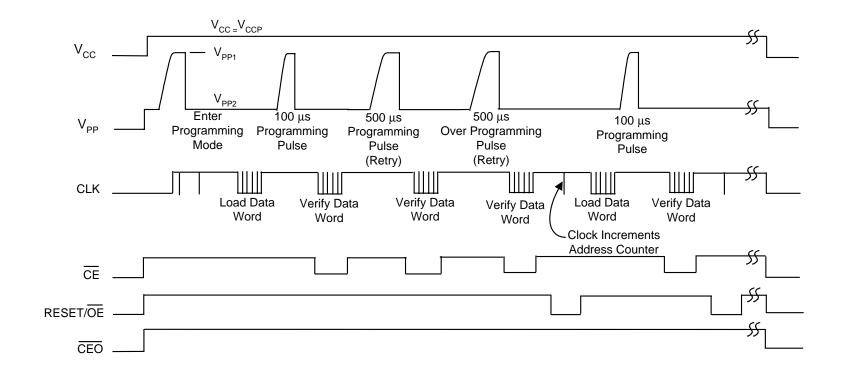

The programming mode is entered by holding  $\overline{CE}$  and  $\overline{OE}$  High with  $V_{PP}$  at  $V_{PP1}$  for two rising clock edges, then lowering  $V_{PP}$  to  $V_{PPNOM}$  for one more rising clock edge (See Figure 3). Once in the programming mode, the following functions are available.

### Read Manufacturer's/Device ID

All of the SPROMs contain a Manufacturer's and Device identification code. Prior to attempting to program or verify the device, the device programmer should read this code and verify that it is the correct code for the device selected by the user. If not, display message "Manufacturer or Device ID Error."

To read the Manufacturer's/Device identification code, first enter the programming mode.

While holding  $\overline{CE}$  High and  $\overline{OE}$  Low, apply 19,791 clock signals to the clock pin to access the ID row.

Then bring  $\overline{\text{OE}}$  High and  $\overline{\text{CE}}$  Low\*. The first bit of the identification word is present when  $\overline{\text{CE}}$  goes Low and does not require a clock. Apply 15 additional clock signals to the CLK pin to read the complete device ID.

### The Manufacturer's/Device ID

Consisting of 2 bytes of data. The first byte contains the JEDEC assigned Manufacturer's ID code for Xilinx (C9). The first four bits of the second byte define the density of the PROM, while the last four bits of the second byte contain specific programming algorithm information, currently:

F for XC1700D and E for XC1700L D for XC1700E and C for XC1700X A for XC1701 and B for XC1701L/512L

The data is read out MSB first.

XC1701, XC1701L & XC17512L Family

### The density codes are defined as follows:

XC1701/L D(1101) XC17512L 9(1001)

## **Loading and Programming a Data Word**

The data word is shifted into the SPROM, one bit at a time, on the rising edge of the clock, while  $\overline{CE}$  and  $\overline{OE}$  are High. The data word counter is temporarily held in internal latches until the address is advanced to the next address, and is programmed into the memory as an entire word upon strobing the device with  $V_{PP}$  at  $V_{PP1}$  for 100µs.

The contents of the data word must now be verified at V<sub>PP2</sub>. The data word is read while lowering  $\overline{CE}$  and capturing the data while clocking the device 63 times. The first bit of the word (LSB) is present when  $\overline{CE}$  goes low. After all 64 bits were read, bring  $\overline{CE}$  high and compare the data to the original file data. If the data does not compare, stroke V<sub>PP</sub> at V<sub>PP1</sub> for 500µs. (Note, the original data is still contained in internal latches and does not have to be loaded into the device again.) Read the data word again (as described above) and compare it to the original data. If it still does not compare, pulse V<sub>PP</sub> at V<sub>PP1</sub> for another 500µs. Now read the data word again. If it still does not compare, power the device down and issue message: "Device Failed to Program". See Figure 4. If the word compares, increment the word counter as described below.

## **Increment the Address (Word) Counter**

After successfully programming a data word, the address counter must be incremented. This is done on the rising edge of the clock while  $\overline{\sf CE}$  is High and  $\overline{\sf OE}$  is Low.\*

### **Set RESET Polarity**

The polarity of the Reset/ $\overline{OE}$  pin may be made active Low by writing zeros into a dedicated row.(See Figure 5).

Reset/ $\overline{\text{OE}}$  is located outside of the user data array. Enter the programming mode, then lower Reset/ $\overline{\text{OE}}$ , hold the Data pin Low, strobe the clock 16,384 times, raise the Reset/ $\overline{\text{OE}}$  pin, load the data latches with all zeros (see Load a Data Word above), and strobe V<sub>PP</sub> at V<sub>PP1</sub> for 5 ms.

The reset polarity has to be verified (sensed) at  $V_{PP2}$  while in programming mode. To sense the polarity bit, after strobing  $V_{PP}$  for 5ms, set  $\overline{CE}$  low and sense the  $\overline{CEO}$  pin. If  $\overline{CEO}$  is high, reset is active low (successfully programmed). If  $\overline{CEO}$  is low, reset is active high (failed to program).

Writing ones or not writing anything maintains RESET active High.

#### Note:

The Reset Polarity is actually only the MSB of the data word.

\* Be careful not to have  $\overline{CE}$  and  $\overline{OE}$  Low at the same time, as this causes the device to exit programming mode.

XC1701, XC1701L & XC17512L Family

## **Sensing RESET Polarity**

To sense or read the polarity of the Reset/ $\overline{OE}$  pin, enter the programming mode, then lower Reset/ $\overline{OE}$ , hold the Data pin High, then strobe the clock 16,384 times. Set Reset/ $\overline{OE}$  High, set  $\overline{CE}$  Low and sense the  $\overline{CEO}$  pin. If  $\overline{CEO}$  is High, Reset is active Low. If  $\overline{CEO}$  is Low, Reset is active High. The reset polarity bit is defaulted (unprogrammed) to active high. When the reset bit is programmed, the "reset" polarity is active low.

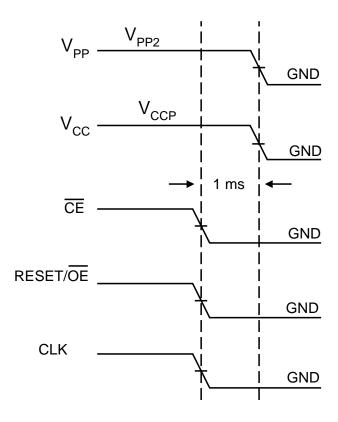

## **Exit Programming Mode**

To exit the programming mode, remove power from the device, per Figure 6.

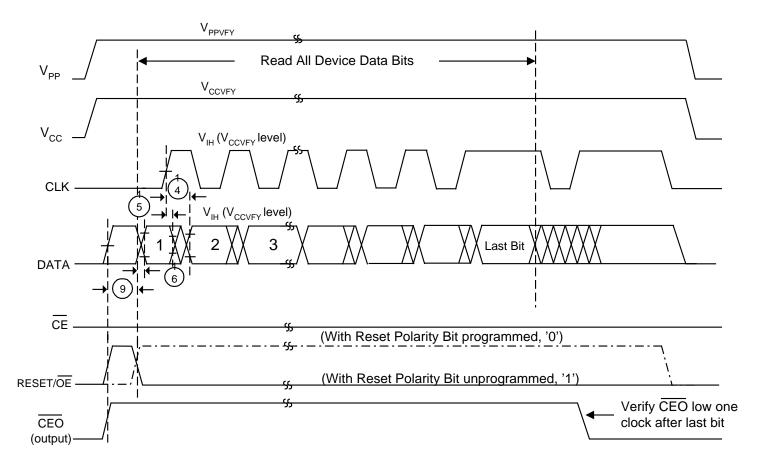

# Stand Alone Verify Of Data Bits (Normal Mode)

The verify operation should be performed after programming. Power up the device and read the data bits out serially in normal readout mode (see Figure 7). A margin voltage (difference between  $V_{PP}$  and  $V_{CC}$ ) is applied to the device to ensure charge retention on each programmed bit. Set  $V_{CC}$  to  $V_{CCVFY}$  and  $V_{PP}$  to  $V_{PPVFY}$ . When in normal mode, the Reset/ $\overline{OE}$  signal should be driven active high if the reset polarity bit was unprogrammed (logic "1"). It should be driven active low if the reset polarity bit was programmed (logic "0").

At the end of the verify operation the programmer must confirm that the  $\overline{\text{CEO}}$  pin has gone Low one clock after the last bit is read out.

If the data fails to verify, display message "Failed Margin Verify". If the data verifies, display message "Device Passed".

XC1701, XC1701L & XC7512L Family

# **Programming Mode Pin Assignments**

| DIP<br>Pin | PLCC<br>Pin | SOIC<br>Pin | Name            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------------|-------------|-------------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | 2           | 1           | Data            | I/O | The rising edge of the clock shifts a data word in or out of the SPROM one bit at a time.                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 2          | 4           | 3           | CLK             | I   | Clock input. Used to increment the internal address/word counter for reading and programming.                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 3          | 6           | 8           | RESET/<br>ŌĒ    | 1   | The rising edge of CLK shifts a data word into the PROM when $\overline{CE}$ and $\overline{OE}$ are High; it shifts a data word out of the PROM when $\overline{CE}$ is Low and $\overline{OE}$ is High. The address/word counter is incremented on the rising edge of CLK while $\overline{CE}$ is held High and $\overline{OE}$ is held Low. Note: Any modified polarity of the RESET/ $\overline{OE}$ pin is <b>ignored</b> in the programming mode. |  |  |

| 4          | 8           | 10          | CE              | I   | The rising edge of CLK shifts a data word into the PROM when $\overline{CE}$ and $\overline{OE}$ are High; it shifts a data word out of the PROM when $\overline{CE}$ is Low and $\overline{OE}$ is High. The address/word counter is incremented on the rising edge of CLK while $\overline{CE}$ is held High and $\overline{OE}$ is held Low.                                                                                                          |  |  |

| 5          | 10          | 11          | GND             |     | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 6          | 14          | 13          | CEO             | 0   | The polarity of the RESET/ $\overline{OE}$ pin can be read by sensing the $\overline{CEO}$ pin. Note: The polarity of the RESET/ $\overline{OE}$ pin is ignored while in the programming mode. In final verification, this pin must be monitored to go Low one clock cycle after the last data bit has been read.                                                                                                                                        |  |  |

| 7          | 17          | 18          | V <sub>PP</sub> |     | Programming Voltage Supply. Programming mode is entered by holding $\overline{CE}$ and $\overline{OE}$ High and $V_{PP}$ at $V_{PP1}$ for two rising clock edges and then lowering $V_{PP}$ to $V_{PPNOM}$ for one more rising clock edge. A word is programmed by strobing the device with $V_{PP}$ for the duration $T_{PGM}$ . $V_{PP}$ must be held at $V_{CC}$ for normal operation.                                                                |  |  |

| 8          | 20          | 20          | V <sub>CC</sub> |     | V <sub>CC</sub> power supply input.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

XC1701, XC1701L & XC7512L Family

## **DC** Programming Specifications

| Symbol                                  | Description                                     | Min  | Recommended     | Max             | Units |

|-----------------------------------------|-------------------------------------------------|------|-----------------|-----------------|-------|

| V <sub>CCP*</sub>                       | Supply voltage during programming               |      | 5.0             |                 | V     |

| V <sub>IL</sub>                         | Low-level input voltage                         | 0.0  | 0.0             | 0.5             | V     |

| V <sub>IH</sub>                         | High-level input voltage                        | 2.4  | V <sub>CC</sub> | V <sub>CC</sub> | V     |

| V <sub>OL</sub>                         | Low-level output voltage                        |      |                 | 0.4             | V     |

| V <sub>OH</sub>                         | High-level output voltage                       | 2.5  |                 |                 | V     |

| V <sub>PP1**</sub>                      | Programming voltage                             | 12.0 | 12.25           | 12.5            | V     |

| V <sub>PP2***</sub>                     | Margin verify voltage during programming        |      | 5.4             |                 | V     |

| I <sub>PPP</sub>                        | Supply current on programming pin               |      |                 | 60              | mA    |

| V <sub>CCNOM</sub> /V <sub>PPNOM</sub>  | Nominal Voltage                                 |      | 5.0             |                 | V     |

| V <sub>CCVFY</sub> (XC1701)             | Supply voltage during stand alone margin verify |      | 5.0             |                 | V     |

| V <sub>CCVFY</sub> (XC1701L & XC17512L) | Supply voltage during stand alone margin verify |      | 3.3             |                 | V     |

| V <sub>PPVFY</sub> (XC1701)             | Margin voltage during stand alone margin verify |      | 5.4             |                 | V     |

| V <sub>PPVFY</sub> (XC1701L & XC17512L) | Margin voltage during stand alone margin verify |      | 3.7             |                 | V     |

<sup>\*</sup> Noise and voltage deviation allowed:  $5.0V \pm 50 \text{ mV}$ .

<sup>\*\*</sup> No overshoot is permitted on signal. V<sub>PP</sub> must not be allowed to exceed V<sub>PP1</sub> max.

<sup>\*\*\*</sup> Noise and voltage deviation allowed: 5.4V ± 250 mV.

XC1701, XC1701L & XC7512L Family

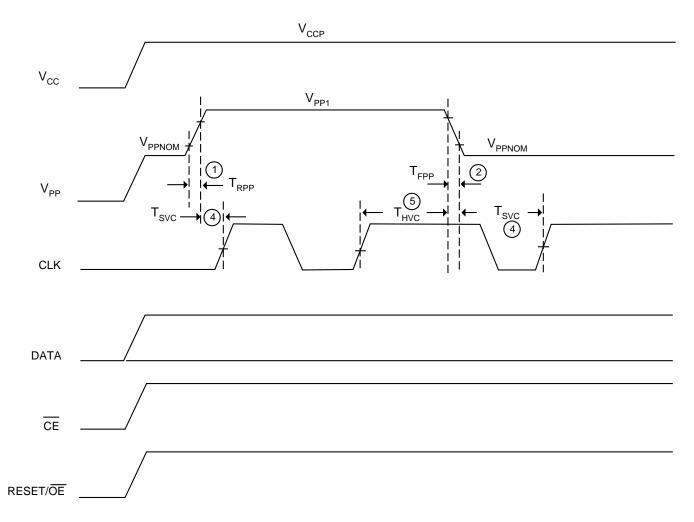

# **AC Programming Specifications**

| Symbol |                  | Description                                            |     | Rec             | Max | Units |

|--------|------------------|--------------------------------------------------------|-----|-----------------|-----|-------|

| 1      | $T_RPP$          | 10% to 90% rise time of V <sub>PP</sub>                |     | 5               |     | μs    |

| 2      | $T_{FPP}$        | 90% to 10% fall time V <sub>PP</sub>                   |     | 5               |     | μs    |

| 3      | $T_{PGM}$        | V <sub>PP</sub> programming pulse width                |     | 100 (500 Retry) |     | μs    |

| 4      | T <sub>SVC</sub> | V <sub>PP</sub> setup to CLK for entering programming  | 100 |                 |     | ns    |

| 5      | $T_HVC$          | V <sub>PP</sub> hold from CLK for entering programming |     |                 |     | ns    |

| 6      | $T_{SDP}$        | Data setup to CLK for programming                      | 50  |                 |     | ns    |

| 7      | $T_{HDP}$        | Data hold from CLK for programming                     | 0   |                 |     | ns    |

| 8      | $T_{SCC}$        | CE setup from programming/verifying                    | 100 |                 |     | ns    |

| 9      | $T_{ON}$         | Reset Pulse Width                                      |     | 5               |     | ms    |

| 10     | T <sub>SCV</sub> | CE hold from CLK for programming/verifying             | 100 |                 |     | ns    |

| 11     | T <sub>HCV</sub> | CE hold from V <sub>PP</sub> for programming           | 50  |                 |     | ns    |

| 12     | $T_{SIC}$        | OEsetup to CLK for incrementing address                | 100 |                 |     | ns    |

| 13     | T <sub>HIC</sub> | OE hold from CLK for incrementing address              | 0   |                 |     | ns    |

| 14     | $T_CAC$          | CLK to data valid                                      |     |                 | 400 | ns    |

| 15     | T <sub>OH</sub>  | Data hold from CLK                                     | 0   |                 |     | ns    |

| 16     | $T_CE$           | CE low to data valid                                   |     |                 | 250 | ns    |

XC1701, XC1701L & XC7512L Family

Figure 1. Programming Flow

XC1701, XC1701L & XC7512L Family

Figure 1. Programming Flow (Continued)

XC1701, XC1701L & XC7512L Family

Figure 1. Programming Flow (Continued)

XC1701, XC1701L & XC7512L Family

Figure 2. Programming Cycle Overview

XC1701, XC1701L & XC7512L Family

Figure 3. Enter Programming Mode

XC1701, XC1701L & XC7512L Family

Figure 4. Details Of The Programming Cycle

XC1701, XC1701L & XC7512L Family

Figure 5. Programming Reset Polarity

<sup>\*\*</sup> Number of Clocks for the Device Word

XC1701, XC1701L & XC7512L Family

If your programming hardware does not allow  $V_{PP}$  and  $V_{CC}$  to power up and down simultaneously, make sure to first power up  $V_{PP}$  during power up and power down  $V_{PP}$  after  $V_{CC}$  during power down.

Figure 6. Exit Programming Mode

XC1701, XC1701L & XC7512L Family

Figure 7. Details Of Verify Cycle