# XC6200 Development System

January 28, 1998 (Version 1.2)

### **Table of Contents**

| FEATURES                                | 3        |

|-----------------------------------------|----------|

| DESCRIPTION                             | 4        |

| ARCHITECTURE                            | 5        |

| MODES OF OPERATION                      | 6        |

| MODE 1: PCI TO 6200, 6200 TO 32 BIT RAM | <i>6</i> |

| MODE 2: PCI TO 32 BIT RAM               |          |

| MODE 3: 6200 TO 32 BIT RAM              |          |

| MODE 4: PCI AND 6200 TO 16 BIT RAM      |          |

| SRAM INTERFACE                          |          |

| 6200 INTERFACE                          | 9        |

| PCI 6200 INTERFACE.                     |          |

| READ 6200 IOBs                          |          |

| CLOCKING                                | 10       |

| PROGRAMMABLE CLOCK GENERATOR            |          |

| PROGRAMMABLE REFERENCE CLOCK            | 11       |

| A/D CONVERTER                           | 11       |

| INTERRUPT LOGIC                         | 12       |

| EXPANDABILITY                           | 14       |

| SERIAL DOWNLOAD                         | 14       |

| 6200 SERIAL DOWNLOAD                    | 14       |

| SUPPORT SOFTWARE                        | 15       |

| REFERENCES                              |          |

| APPENDIX A. MEMORY MAP                  | 17       |

| APPENDIX B. I/O SPACE REGISTER SUMMARY  | 18       |

| APPENDIX C. XC6200 PIN DESCRIPTIONS     | 21       |

| XC6200 PINOUTS - WEST SIDE.             | 21       |

| XC6200 PINOUTS - SOUTH SIDE             | 22       |

| XC6200 PINOUTS - EAST SIDE              |          |

| XC6200 PINOUTS - NORTH SIDE             |          |

| ADDENING D. MEZZANINE CONNECTOD DINOUT  | 25       |

| MEZZANINE PINOUT - J1  | 25 |

|------------------------|----|

| MEZZANINE PINOUT - J2  | 26 |

| MEZZANINE PINOUT - J3  |    |

| MEZZANINE PINOUT - J4  | 28 |

| MEZZANINE PINOLIT - 15 |    |

#### **Features**

- PCI Based Development System

- Upto 64K User Programmable Gates

- Up to 2 Mb fast SRAM

- IDD Monitoring of Xilinx 6200

- Flexible clock generation for Xilinx 6200

- Expansion via Mezzanine connectors to standard prototyping board

- Plug and Play Compliant

- Hardware implements XC6200 Compute Element Reference Design

- Device Driver interface to board implements standard Application Binary Interface

- First affordable FPGA Coprocessor platform for medium volume OEM applications

- Debugger software supports validation of XC6200 based designs and reduces time to market

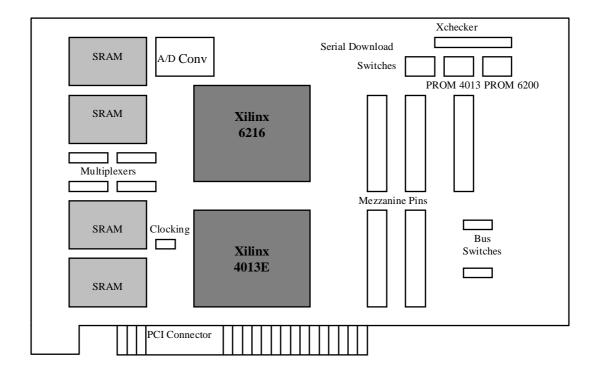

Figure 1 Board layout

#### **Description**

The XC6200 development system (XC6200DS) is a high performance PCI based input/output coprocessor for Win95 and WinNT based PC's.

The XC6200DS supports the time-to-volume advantages of the XC6200 FPGA family in four ways.

- XC6200DS cuts verification time on complex designs by implementing a test harness into

which real data (e.g. graphics images) can be loaded and results displayed and analyzed

using the host PC. Conventional logic simulators are orders of magnitude too slow to

support this application and generation of test vectors is unwieldy and time consuming.

- XC6200DS allows development of software to proceed in parallel with FPGA logic design and design of the printed circuit board. Xilinx supplies drivers and plug and play software which simplifies development of PCI based applications.

- XC6200DS boards can be supplied as an OEM product to final customers or used as a low volume demonstration platform until market demand justifies a custom board design for the application.

- XC6200DS schematics, PCB layout, 6200 FPGA design files and support software source are made available as a developer support package and can be used as the basis of customer products.

The XC6200DS realises a hardware and software standard for XC6200 based algorithm accelerators. By supporting the minimum feature set specified in the hardware standard and implementing the driver software specified in the software standard, hardware vendors are guaranteed that their systems can run compliant applications. The standard allows third party developers to create `shrink wrapped' applications consisting of FPGA configurations and host code within a single Microsoft Windows executable file.

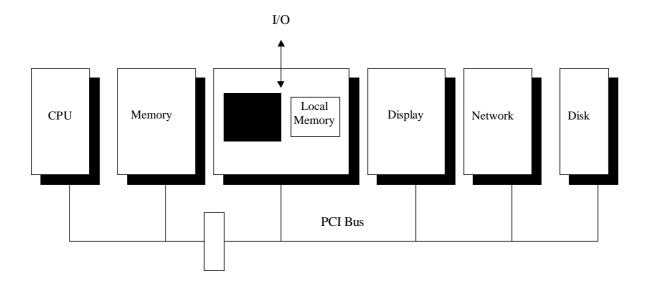

Figure 2 FPGA Coprocessor

#### **Architecture**

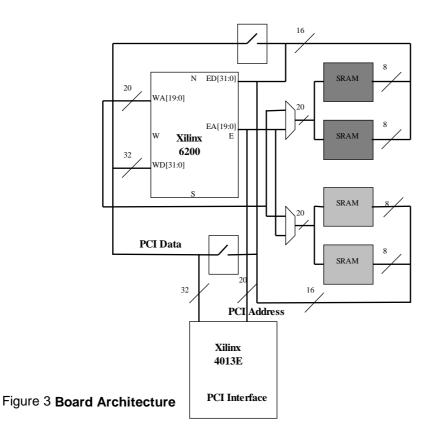

The Xilinx 6200 development system consists of a Xilinx 4013E [ Ref 3] and a compute element. The compute element consists of a Xilinx 6200 FPGA [ Ref 2], four 8-bit wide SRAM's and six bus controller chips to control data flow. Figure 3 shows the primary components of the architecture. A Xilinx 4013E FPGA is used as the PCI bus interface. Approximately 50% of the chip is used for this function and the remaining area is used for card control logic. The XC4013E is electrically and functionally 100% PCI compliant. For details of the PCI interface see the PCI logicore product description which is available separately from Xilinx [ Ref 4]. The primary component of the compute element is the Xilinx 6216. The board architecture allows the XC6200 to be reconfigured through the PCI interface during run-time. The PCI interface provides direct access from the host PC to logic cells within the user's circuit. The output of any cell's function unit can be read and the flip-flop within any cell can be written through the PCI interface.

The compute element memory is organised into two banks. Each bank consists of a maximum of two 512K x 8 SRAM's. A bank of RAM can be accessed from either the PCI Interface or the XC6200. The banks of memory have two separate address busses and four read/write signals to control the RAMs individually. The development system provides a flexible architecture in order to implement a wide variety of algorithms. Multiple modes of operation can be set-up by selecting the muxes and bus switch in the desired manner. These modes are described in detail in the following section (Modes of Operation).

A 44-bit external data path is available to XC6200 Input Output Blocks (IOB's). This data path can be used to attach daughter boards for video I/O, network connections, or sensor I/O.

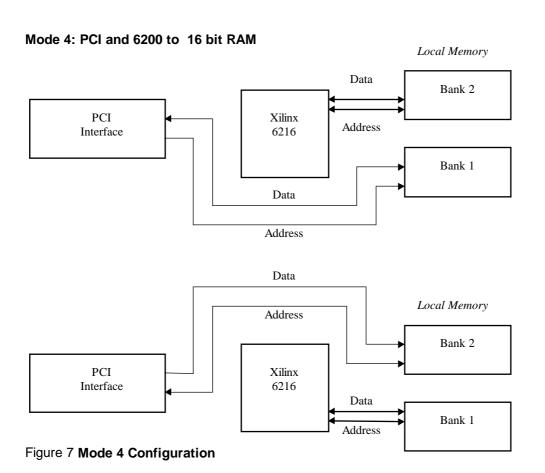

### **Modes of Operation**

The development system can be configured to operate with regards to memory reads and writes in many different configurations. Some of the possible configurations are outlined below.

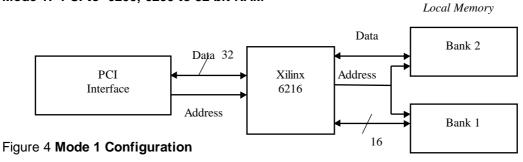

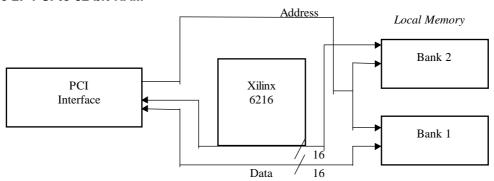

Mode 1: PCI to 6200, 6200 to 32 bit RAM

- Single 32-bit read or write to local memory from 6216

- One address to both banks of memory

- · Concurrent PCI and local memory accesses

- Can reconfigure logic in 6216 while still processing data from local memories

- Can store data into 6216 registers and access data from local memories

#### Mode 2: PCI to 32 bit RAM

Figure 5 Mode 2 Configuration

- Single 32-bit read or write to local memory from PCI

- One address to both banks of memory

- The 6216 address and data bus are disabled

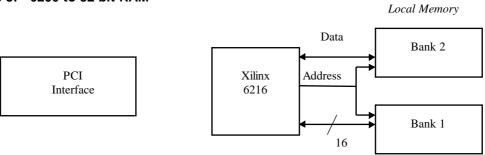

Mode 3: 6200 to 32 bit RAM

Figure 6 Mode 3 Configuration

- Single 32-bit read or write to local memory from 6216

- One address to both banks of memory

- Can store data into 6216 registers and access data from local memories

One bank of memory can be filled by the PCI interface and the other bank can be read from the 6216 so that real-time image processing can be performed

• One address can be generated from the 4013E and one from the 6216

#### All Modes:

• Separate read/write and control signals for each memory chip.

#### **SRAM Interface**

The SRAM [Ref. 6] on the PCI/6200 Evaluation Board is mapped transparently into a region of PCI memory address space. The PCI address is mapped to the East Address bus  $\mathbb{E}A[19:0]$  (see Figure 3) as follows:

```

EA[19:0] = PCI\_ADDRESS[21:2]

```

The mapping of bytes within the PCI data bus AD[31:0] to the West Data bus WD[31:0] is as follows:

```

AD[7:0] corresponds to WD[7:0]

AD[15:8] corresponds to WD[15:8]

AD[23:16] corresponds to WD[23:16]

AD[31:24] corresponds to WD[31:24]

```

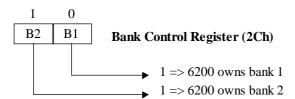

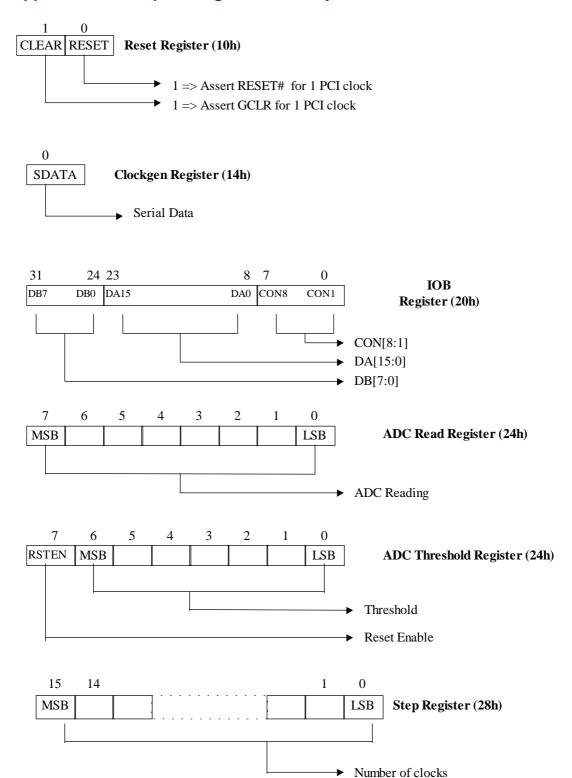

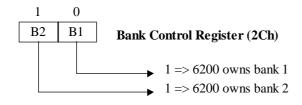

SRAM access by the PCI interface and the Xilinx 6200 is controlled by the bus switches which are enabled by the Bank Control register. The **Bank Control Register**, can be used to effectively split the on-board SRAM into two independent 16-bit banks. Each bank may then be owned (i.e. controlled) by either the PCI Interface (4013) or the 6200. Control of a particular bank is defined to be ownership of the address, data and control signals of the two SRAM chips in the bank in question. During an SRAM access by the PCI interface, if the bus switches are enabled then the West Data bus  $\mathtt{WD}[31:0]$  is connected to the East Data bus  $\mathtt{ED}[31:0]$ .

When a bank is not controlled by the PCI interface, the data bus from the PCI interface to that bank is held in high impedance, allowing the 6200 to drive it. Conversely, the user of the PCI/6200 board must ensure that when the 6200 does not own a particular bank, it must not attempt to drive the data bus to that bank.

When the 6200 owns both banks, writes to SRAM from the PCI bus will return undefined data. The arrangement of data in the host's memory, when performing a transfer to or from the SRAM, depends on the current value of the Bank Control Register. Bank1 controls data bits[15:0] and Bank2 controls data bits [31:16]:-

| Bank 1 owned by | Bank 2 owned by | Data arrangement in host me | mory        |

|-----------------|-----------------|-----------------------------|-------------|

| PCI             | PCI             | Bank 1 data                 | Bank 2 data |

| 6200            | PCI             | undefined                   | Bank 2 data |

| PCI             | 6200            | Bank 1 data                 | undefined   |

| 6200            | 6200            | undefined                   | undefined   |

#### 6200 Interface

#### PCI 6200 Interface

The 6200 register read/write mechanism is supported via the PCI interface, mapped into a region of PCI memory address space. A PCI address is mapped to the East Address bus EA[19:0] (and therefore the address bus of the 6200 register read/write interface) as follows:

```

EA[19:0] = PCI ADDRESS[21:2]

```

The mapping of bytes within the PCI data bus AD[31:0] to the West Data bus WD[31:0] is as follows:

```

AD[7:0] corresponds to WD[7:0]

AD[15:8] corresponds to WD[15:8]

AD[23:16] corresponds to WD[23:16]

AD[31:24] corresponds to WD[31:24]

```

The Bank Control Register has no effect on 6200 accesses.

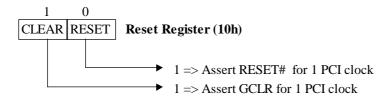

The 6200 may be reset, via its RESET# pin, or cleared, via its GCLR pin, by writing to the Reset Register. A write to this register can cause either, both, or none of these signals to be asserted for a single PCI clock cycle (therefore, >30ns):

#### Read 6200 IOBs

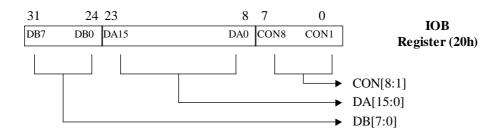

A set of thirty-two IOBs on the 6200 are connected directly to pins on the PCI Interface, and may be read asynchronously with respect to the design running in the 6200. They are useful for monitoring the 6200 without disturbing its state, for example. The thirty-two IOBs may be read simultaneously by performing an I/O read to the IOB Register.

### Clocking

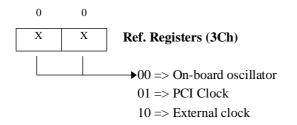

Clock signals for the XC6200 and for timing on board memory accesses are generated from an on board PLL based clock chip [ Ref 1] controlled from the XC4013E. There are various optional methods by which the on board clock signal can be generated. All off these methods pass a clock signal to the on board programmable clock generator chip which then generates the appropriate clocking frequency to 6200 and the rest of the board.

Three main sources of clock signals are available:

- · An on board crystal oscillator

- An external clock signal from the mezzanine connectors

- A PCI bus clock

The 6200 can also be run in a single stepping mode where each clock transition is initiated by a host software access.

#### **Programmable Clock Generator**

The PCI/6200 Evaluation Board allows the 6200 to be run in what are termed `continuous clock mode' and `single clock mode'. In continuous clock mode, the global clock driving the 6200 is simply run continuously. In single clock mode, the global clock is stopped, and individual clock pulses or individual trains of clock pulses may be sent to the 6200, under control of the user's software.

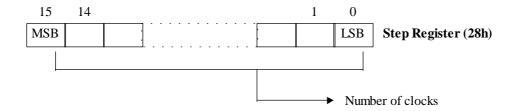

The PCI/6200 board is put into continuous clock mode by PCI reset, or by performing a write (with dummy data) to a specific location in I/O space. To put the board into single clock mode, a write is made to another location in I/O space. Once the board is in single clock mode, the user may send trains of clock pulses to the 6200 by writing values to the **Step Register**. The value written to the Step Register is an unsigned 16-bit integer, representing the number of clock pulses to send to the 6200.

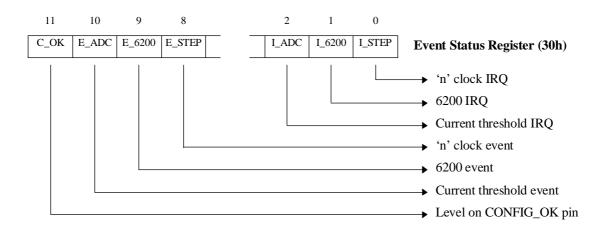

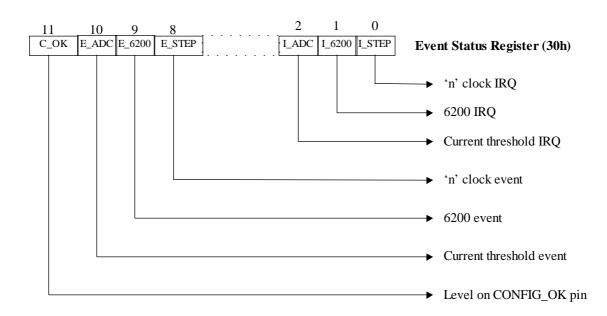

At the end of a sequence of clock pulses, the **E\_STEP** bit in the Event Status Register is set high, remaining high until acknowledged, and optionally, an interrupt can be caused on the host.

When a 6200 read is performed while the board is in single clock mode, three 6200 clock pulses are required. Two are required for the data read and the third for switching off the data bus. A 6200 write requires a minimum of two clock pulses. These accesses never cause an interrupt, or alter the Event Status Register.

#### **Programmable Reference clock**

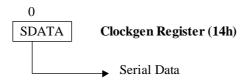

As well as stopping and starting the 6200 clock, the PCI/6200 Evaluation Board permits any clock frequency in the range 1MHz to 33MHz to be sent to the XC6200 global clock. A single-bit register allows the configuration of the clock generator chip in bit-serial mode. Refer to the data sheet for ICD2053B for details on the bitstream format [ Ref 1].

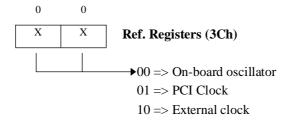

The programmable clock chip used to derive the 6200 clock requires a reference clock. The registers shown below are used do determine which reference clock frequency is used.

#### A/D Converter

The purpose of the A/D converter [ Ref 5] is to monitor power supply current (IDD) to the XC6200. If power consumption exceeds a preset value the XC4013E will reset (if enabled) the XC6200, clearing the faulty user configuration. Users can also monitor power consumption via software to help track down less dramatic or intermittent faults in their designs or to evaluate power consumption for different 6200 designs.

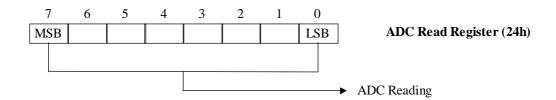

Circuitry on the PCI/6200 board measures the supply current drawn by the 6200. The **ADC Read Register** is an eight bit register in I/O space which returns the last reading made by the analogue-to-digital converter. The equation for converting ADC readings to a supply current values is as follows:

$$IDD = (ADC \text{ reading}) * \sim 5.0 \text{ (mA)}$$

At all times, the last reading from the analogue-to-digital converter is available via the ADC Read Register as an unsigned eight bit value:

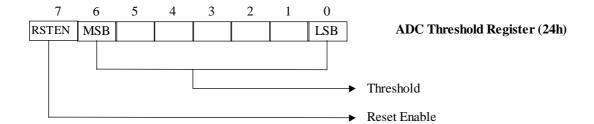

The host can be interrupted when the 6200 supply current exceeds a user-programmable threshold. In addition, the 6200 may be automatically reset when this event occurs. The **ADC Threshold Register** is written with a value consisting of:

- · An unsigned eight bit threshold value, and

- A single bit flag, which if true, causes the 6200 to be reset when the threshold is exceeded.

The threshold is exceeded when the ADC reading exceeds the threshold value written into the ADC Threshold Register. When exceeded, the **E\_ADC** bit in the Event Status Register is set high, and remains high until acknowledged, even if the current falls below the threshold.

#### **Interrupt Logic**

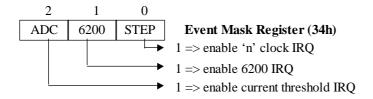

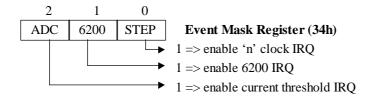

There are three possible sources of interrupts from the PCI/6200 Evaluation Board:

- The last clock pulse in a sequence has been sent to the 6200.

- 6200 requests an interrupt.

- 6200 supply current threshold is exceeded.

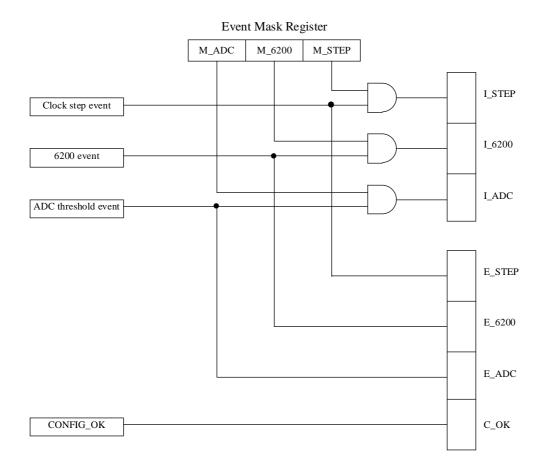

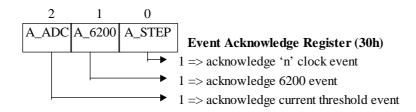

Each of the above events may be masked using the **Event Mask Register**. An event may cause an interrupt on the host when the corresponding bit in the Event Mask is a 1. When it is 0, the event may not cause an interrupt on the host. To disable interrupts entirely, the Event Mask Register should be written with 0.

Whether masked or not, the event status is available via the **Event Status Register**. Even if masked by the Event Mask Register, when the 6200 requests an interrupt, for example, a corresponding bit will be set in the Event Status Register. In addition, the masked event status is available in the Event Status Register, which consists of the bitwise product of the set of detected events and the Event Mask.

The 6200 requests an interrupt on the host by pulsing the signal CON8 low. The PCI interface senses the falling edge of this signal, and sets the E\_6200 bit in the Event Status Register. Provided that it is not masked by the Event Mask Register, the I\_6200 bit will also be set.

The bit C\_OK is simply the level of the signal CONFIG\_OK from the 6200, and the discussion below does not apply to this flag. Those bits prefixed with E\_ (to denote event) appear in the Event Status Register regardless bof the Event Mask Register. Those bits prefixed with I\_ (to denote interrupt) appear as 1 in the Event Status Register only if the corresponding event (E\_) bit is 1 and the corresponding bit in the Event Mask Register is 1. The following diagram illustrates the relationship between event bits and interrupt bits:

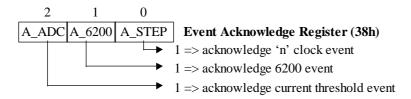

Once an event has occurred, in order to clear the event condition in the Event Status Register, it is necessary to acknowledge it by performing an I/O write to the **Event Acknowledge Register**. Writing a 1 to a particular bit clears the event condition associated with that bit. A 0 written to a particular bit has no effect.

### **Expandability**

Access to the complete range of on board signals and busses is provided through the five mezzanine connectors. Details of the mezzanine pinouts can be found in Appendix C.

User defined designs can be connected via the mezzanine connectors allowing complete configurability and testing of the design through the PCI bus. The mezzanine connectors can also be used to connect several XC62000DS boards together to create a high performance system. Any Xilinx chips on the daughter boards can have their configuration loaded as slaves from the XC62000DS.

The XCHECKER connector supports the use of a Xilinx XCHECKER and XC4000 JTAG circuitry.

#### **Serial Download**

The two PROM chips allow complete configuration of the XC4013 and XC6200 chips. The XC4013 prom configures the XC4013E-2 on power-up, whereas the XC6200 prom is initiated via the PCI interface.

Given a suitable configuration for the XC4013E in the Flash device and a power source the development system can operate outside the host computer.

#### 6200 Serial Download

The PCI/6200 Evaluation Board initiates a 6200 Serial download by asserting the XC6200 Serial line low then negating the signal after SECE line is negated i.e. on completion of the serial download sequence. A single-bit register is used to store the value of the Serial line. The register defaults to one (negated) on power-up.

Note. Con7/Seclk, Con4/Sereset and Con3/SECE are dual purpose pins (Serial download control signals and general purpose output pins). Therefore, any users design must reframe from configuring CON pins 7, 4 and 3 as general purpose outputs when using the 6200 Serial Download feature.

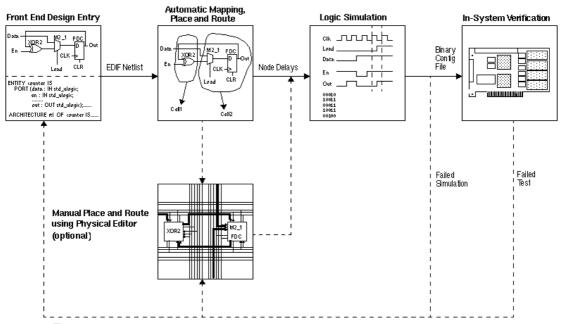

#### **Support Software**

The XC6200DS is supplied with; a win95 or winNT device driver, low level class function software and two top level graphical user interfaces.

The device driver supports a standard interface to the XC6200 board and provides easy access to the XC6200 device and the XC4013. This interface allows easy reconfiguration of registers, on board memory, processing of interrupts etc.. The device driver uses the FASTmap interface to transfer user logic to the XC6200 device. Additional non-standard support is provided with the monitoring of on-board power consumption and the availability of single stepping clock mode allowing easy debugging of the XC6200 device.

The graphical user interface WebScope provides a complete real-time debugging interface to the XC6200DS. The graphical display allows complete access to the XC6200 device giving both a graphic display of the logic values on cell outputs and a symbolic display of the logic of groups of cells. Through the WebScope interface complete real-time simulation of a design can be undertaken in a matter of seconds compared with the hours involved in non real-time standard simulation.

The user interface PCITEST provides a complete debugging interface to the XC6200DS. PCITEST provides; a command line interface to the board, a graphical register display of all the XC6200DS features and command file capability.

A typical design flow is shown in figure 8.

Figure 8 XC6200 Logic Design Flow

#### References

[ Ref 1] Cypress - Programmable Clock Generator ICD2053B - August 1994 - Revised 1995.

[ Ref 2] Xilinx - XC6200 Field Programmable Gate Arrays DataSheet - April 24, 1997 - Version 1.10

[ Ref 3] Xilinx - The Programmable Logic Data Book 1996.

[ Ref 4] Xilinx - LogiCore PCI Master and Slave Interface User's Guide - July 24, 1996 - Version 1.1

[ Ref 5] National Semiconductor - ADC0804 8-bit µP compatible A/D converters - May, 1989.

[ Ref 6] NEC - IC Memory - Static RAM - 1995 Data Book.

## **Appendix A. Memory Map**

### PCI I/O Space Assignments

| I/O Offset | Type | Function                    |

|------------|------|-----------------------------|

| 00 - 0C    |      | Unused                      |

| 10         | WO   | Reset Register              |

| 14         | WO   | Clockgen Register           |

| 18         | WO   | Enter continuous clock mode |

| 1C         | WO   | Enter single clock mode     |

| 20         | RO   | Read 6200 IOBs              |

| 24         | R    | ADC Read Register           |

|            | W    | ADC Threshold Register      |

| 28         | WO   | Step Register               |

| 2C         | WO   | Bank Control Register       |

| 30         | R    | Event Status Register       |

|            | W    | Event Acknowledge Register  |

| 34         | WO   | Event Mask Register         |

| 38         | WO   | XC6200 Serial Download      |

| 3C         | WO   | Clock Reference select      |

### PCI Memory Space Assignments

| PCI Address bit 23 | Type | Function            |

|--------------------|------|---------------------|

| 0                  | R    | Read SRAM           |

|                    | W    | Write SRAM          |

| 1                  | R    | 6200 register read  |

|                    | W    | 6200 register write |

### Appendix B. I/O Space Register Summary

# Appendix C. XC6200 Pin Descriptions

### XC6200 Pinouts - West Side

| PinOut  | HQ240 | XC6200DS |

|---------|-------|----------|

| D0/W1   | P60   | WD_0     |

| GND     | P59   | GND      |

| W14     | P58   | WA_7     |

| NC      | P57   |          |

| D1/W3   | P56   | WD_1     |

| W16     | P55   | WA_8     |

| D2/W5   | P54   | WD_2     |

| W18     | P53   | WA_9     |

| D3/W7   | P52   | WD_3     |

| W20     | P51   | WA_10    |

| D4/W9   | P50   | WD_4     |

| W22     | P49   | WA_11    |

| W24     | P48   | WA_12    |

| W26     | P47   | WA_13    |

| D5/W11  | P46   | WD_5     |

| GND     | P45   | GND      |

| W28     | P44   | WA_14    |

| W30     | P43   | WA_15    |

| W32     | P42   | WA_16    |

| D6/W13  | P41   | WD_6     |

| Vcc     | P40   | VCC      |

| D16/W33 | P39   | WD_16    |

| W34     | P38   | WA_17    |

| GND     | P37   | GND      |

| D7/W15  | P36   | WD_7     |

| D17/W35 | P35   | WD_17    |

| W36     | P34   | WA_18    |

| D18/W37 | P33   | WD_18    |

| D8/W17  | P32   | WD_8     |

| W38     | P31   | WA_19    |

| PinOut              | HQ240 | XC6200DS |

|---------------------|-------|----------|

| Vcc                 | P30   | VCC      |

| GND                 | P29   | GND      |

| D19/W39             | P28   | WD_19    |

| D9/W19              | P27   | WD_9     |

| D20/W41             | P26   | WD_20    |

| D21/W43             | P25   | WD_21    |

| D10/W <sub>21</sub> | P24   | WD_10    |

| D22/W45             | P23   | WD_22    |

| GND                 | P22   | GND      |

| W48                 | P21   | C29      |

| W50                 | P20   | C30      |

| Vcc                 | P19   | VCC      |

| D24/W49             | P18   | WD_24    |

| D11/W23             | P17   | WD_11    |

| D23/W47             | P16   | WD_23    |

| D25/W51             | P15   | WD_25    |

| GND                 | P14   | GND      |

| W56                 | P13   | C31      |

| D12/W <sub>25</sub> | P12   | WD_12    |

| W58                 | P11   | C32      |

| D26/W53             | P10   | WD_26    |

| D27/W55             | P9    | WD_27    |

| D13/W27             | P8    | WD_13    |

| D28/W57             | P7    | WD_28    |

| D14/W29             | P6    | WD_14    |

| D29/W59             | P5    | WD_29    |

| D15/W31             | P4    | WD_15    |

| D30/W61             | P3    | WD_30    |

| D31/W63             | P2    | WD_31    |

| GND                 | P1    | GND      |

### XC6200 Pinouts - South Side

| PinOut               | HQ240 | XC6200DS |

|----------------------|-------|----------|

| Vcc                  | P61   | VCC      |

| RdWr/S1              | P62   | RDWR#    |

| CS/S <sub>3</sub>    | P63   | CS       |

| W12/S0               | P64   | WA_6     |

| OE/S <sub>5</sub>    | P65   | OE#      |

| W10/S2               | P66   | WA_5     |

| Reset/S7             | P67   | RESET#   |

| W8/S4                | P68   | WA_4     |

| W6/S6                | P69   | WA_3     |

| W4/S8                | P70   | WA_2     |

| W2/S10               | P71   | WA_1     |

| W0/S12               | P72   | WA_0     |

| S14                  | P73   | 6K_WE1#  |

| S16                  | P74   | 6K_WE2#  |

| GND                  | P75   | GND      |

| S26                  | P76   | 6K_WE3#  |

| S33                  | P77   | 6K_WE4#  |

| Serial/S9            | P78   | SERIAL#  |

| Wait/S <sub>11</sub> | P79   | WAIT     |

| Vcc                  | P80   | VCC      |

| S28                  | P81   | 6K-OE1#  |

| S35                  | P82   | 6K-OE2#  |

| GND                  | P83   | GND      |

| GClk/S13             | P84   | GCLK     |

| S38                  | P85   | 6K-OE3#  |

| GClr/S <sub>15</sub> | P86   | GCLR     |

| S37                  | P87   | LED1     |

| S40                  | P88   | 6K-OE4#  |

| S39                  | P89   | LED2     |

| Vcc                  | P90   | VCC      |

| PinOut                   | HQ240 | XC6200DS |

|--------------------------|-------|----------|

| GND                      | P91   | GND      |

| G1/S17                   | P92   | G1       |

| G2/S <sub>19</sub>       | P93   | G2       |

| S42                      | P94   | C12      |

| S41                      | P95   | C13      |

| E0/S50                   | P96   | ED_0     |

| E2/S52                   | P97   | ED_1     |

| GND                      | P98   | GND      |

| E4/S54                   | P99   | ED_2     |

| S45                      | P100  | C14      |

| Vcc                      | P101  | VCC      |

| ShiftDOut/S21            | P102  | C15      |

| SEData/S <sub>23</sub>   | P103  | SEDATA   |

| E6/S56                   | P104  | ED_3     |

| S47                      | P105  | C16      |

| GND                      | P106  | GND      |

| E8/S58                   | P107  | ED_4     |

| S49                      | P108  | C17      |

| S <sub>51</sub>          | P109  | CON1     |

| <b>S</b> 53              | P110  | CON2     |

| E10/S60                  | P111  | ED_5     |

| E12/S62                  | P112  | ED_6     |

| SECE/S25                 | P113  | CON3     |

| SEReset/S27              | P114  | CON4     |

| S59                      | P115  | CON5     |

| S61                      | P116  | CON6     |

| SECIk/S29                | P117  | CON7     |

| ConfigOK/S <sub>31</sub> | P118  | C_OK     |

| GND                      | P119  | GND      |

| S63                      | P120  | CON8     |

### XC6200 Pinouts - East Side

| PinOut              | HQ240 | XC6200DS |

|---------------------|-------|----------|

| Vcc                 | P121  | VCC      |

| E14                 | P122  | ED_7     |

| A0/E1               | P123  | EA_0     |

| E16                 | P124  | ED_8     |

| A1/E3               | P125  | EA_1     |

| E18                 | P126  | ED_9     |

| A2/E <sub>5</sub>   | P127  | EA_2     |

| E20                 | P128  | ED_10    |

| A3/E7               | P129  | EA_3     |

| E22                 | P130  | ED11     |

| E24                 | P131  | ED12     |

| E26                 | P132  | ED13     |

| A4/E9               | P133  | EA_4     |

| E28                 | P134  | ED_14    |

| GND                 | P135  | GND      |

| E30                 | P136  | ED_15    |

| E32                 | P137  | ED_16    |

| A5/E11              | P138  | EA_5     |

| A16/E <sub>33</sub> | P139  | EA_16    |

| Vcc                 | P140  | VCC      |

| E34                 | P141  | ED_17    |

| A17/E <sub>35</sub> | P142  | EA_17    |

| GND                 | P143  | GND      |

| A6/E13              | P144  | EA_6     |

| E36                 | P145  | ED_18    |

| E37                 | P146  | EA_18    |

| E38                 | P147  | ED_19    |

| A7/E <sub>15</sub>  | P148  | EA_7     |

| E39                 | P149  | EA_19    |

| Vcc                 | P150  | VCC      |

| PinOut              | HQ240 | XC6200DS |

|---------------------|-------|----------|

| GND                 | P151  | GND      |

| A8/E17              | P152  | EA_8     |

| E40                 | P153  | ED_20    |

| A9/E <sub>19</sub>  | P154  | EA_9     |

| E41                 | P155  | C18      |

| E42                 | P156  | ED_21    |

| E43                 | P157  | ED_22    |

| GND                 | P158  | GND      |

| A10/E <sub>21</sub> | P159  | EA_10    |

| E <sub>50</sub>     | P160  | ED_26    |

| Vcc                 | P161  | VCC      |

| E45                 | P162  | ED_23    |

| E52                 | P163  | ED_28    |

| A11/E23             | P164  | EA_11    |

| E47                 | P165  | ED_24    |

| GND                 | P166  | GND      |

| E58                 | P167  | C19      |

| E49                 | P168  | ED_25    |

| A12/E <sub>25</sub> | P169  | EA_12    |

| E51                 | P170  | ED_27    |

| E53                 | P171  | ED_29    |

| E55                 | P172  | ED_30    |

| A13/E27             | P173  | EA_13    |

| E57                 | P174  | ED_31    |

| A14/E <sub>29</sub> | P175  | EA_14    |

| E59                 | P176  | C20      |

| A15/E31             | P177  | EA_15    |

| E61                 | P178  | C21      |

| E63                 | P179  | C22      |

| Vcc                 | P180  | VCC      |

### XC6200 Pinouts - North Side

| PinOut          | HQ240 | XC6200DS |

|-----------------|-------|----------|

| Vcc             | P240  | VCC      |

| N <sub>1</sub>  | P239  | DA0      |

| N <sub>3</sub>  | P238  | DA1      |

| No.             | P237  | C0       |

| N <sub>2</sub>  | P236  | C1       |

| N <sub>4</sub>  | P235  | C2       |

| N <sub>6</sub>  | P234  | C3       |

| N <sub>5</sub>  | P233  | DA2      |

| N <sub>7</sub>  | P232  | DA3      |

| <b>N</b> 12     | P231  | C4       |

| N14             | P230  | C5       |

| <b>N</b> 16     | P229  | C6       |

| <b>N</b> 18     | P228  | C7       |

| GND             | P227  | GND      |

| N24             | P226  | C8       |

| N <sub>26</sub> | P225  | C9       |

| N33             | P224  | DB0      |

| N28             | P223  | C10      |

| Vcc             | P222  | VCC      |

| N35             | P221  | DB1      |

| <b>N</b> 9      | P220  | DA4      |

| GND             | P219  | GND      |

| <b>N</b> 11     | P218  | DA5      |

| N38             | P217  | C11      |

| N37             | P216  | DB2      |

| <b>N</b> 40     | P215  | C23      |

| <b>N</b> 39     | P214  | DB3      |

| N <sub>13</sub> | P213  | DA6      |

| Vcc             | P212  | VCC      |

| GND             | P211  | GND      |

| PinOut           | HQ240 | XC6200DS |

|------------------|-------|----------|

| N15              | P210  | DA7      |

| N17              | P209  | DA8      |

| <b>N</b> 19      | P208  | DA9      |

| <b>N</b> 42      | P207  | C24      |

| <b>N</b> 41      | P206  | DB4      |

| N44              | P205  | C25      |

| GND              | P204  | GND      |

| N43              | P203  | DB5      |

| N21              | P202  | DA10     |

| Vcc              | P201  | VCC      |

| N23              | P200  | DA11     |

| <b>N</b> 54      | P199  | C26      |

| N45              | P198  | DB6      |

| N56              | P197  | C27      |

| GND              | P196  | GND      |

| N47              | P195  | DB7      |

| N58              | P194  | C28      |

| <b>N</b> 49      | P193  | DB8      |

| N <sub>51</sub>  | P192  | DB9      |

| N53              | P191  | DB10     |

| <b>N</b> 55      | P190  | DB11     |

| N57              | P189  | DB12     |

| <b>N</b> 59      | P188  | DB13     |

| N25              | P187  | DA12     |

| N <sub>2</sub> 7 | P186  | DA13     |

| <b>N</b> 61      | P185  | DB14     |

| N63              | P184  | DB15     |

| N <sub>29</sub>  | P183  | DA14     |

| GND              | P182  | GND      |

| <b>N</b> 31      | P181  | DA15     |

# Appendix D. Mezzanine Connector Pinout

| Pin# | SignalName    | SignalName  | Pin# |

|------|---------------|-------------|------|

| 1    | C25/TCK       | -12V        | 2    |

| 3    | GND           | C21/INTA#   | 4    |

| 5    | C22/INTB#     | C23/INTC#   | 6    |

| 7    | C14/BUSMODE1# | 5V          | 8    |

| 9    | C24/INTD#     | PCI-RSVD*   | 10   |

| 11   | GND           | PCI-RSVD*   | 12   |

| 13   | G2/CLK        | GND         | 14   |

| 15   | GND           | C12/GNT#    | 16   |

| 17   | C28/REQ#      | 5V          | 18   |

| 19   | 5V/V(I/O)     | DB15/AD[31] | 20   |

| 21   | DB12/AD[28]   | DB11/AD[27] | 22   |

| 23   | DB9/AD[25]    | GND         | 24   |

| 25   | GND           | C3/C-BE[3]# | 26   |

| 27   | DB6/AD[22]    | DB5/AD[21]  | 28   |

| 29   | DB3/AD[19]    | 5V          | 30   |

| 31   | 5V/V(I/O)     | DB1/AD[17]  | 32   |

| 33   | C4/FRAME#     | GND         | 34   |

| 35   | GND           | C6/IRDY#    | 36   |

| 37   | C10/DEVSEL#   | 5V          | 38   |

| 39   | GND           | C11/LOCK#   | 40   |

| 41   | C30/SDONE#    | C29/SBO#    | 42   |

| 43   | C8/PAR        | GND         | 44   |

| 45   | 5V/V(I/O)     | DA15/AD[15] | 46   |

| 47   | DA12/AD[12]   | DA11/AD[11] | 48   |

| 49   | DA9/AD[09]    | 5V          | 50   |

| 51   | GND           | C0/C-BE[0]# | 52   |

| 53   | DA6/AD[06]    | DA5/AD[05]  | 54   |

| 55   | DA4/AD[04]    | GND         | 56   |

| 57   | 5V/V(I/O)     | DA3/AD[03]  | 58   |

| 59   | DA2/AD[02]    | DA1/AD[01]  | 60   |

| 61   | DA0/AD[00]    | 5V          | 62   |

| 63   | GND           | C31/REQ64#  | 64   |

| Pin# | Signal Name   | Signal Name   | Pin# |

|------|---------------|---------------|------|

| 1    | 12V           | C27/TRST#     | 2    |

| 3    | C26/TMS       | C19/TDO       | 4    |

| 5    | C18/TDI       | GND           | 6    |

| 7    | GND           | PCI-RSVD*     | 8    |

| 9    | PCI-RSVD*     | PCI-RSVD*     | 10   |

| 11   | C15/BUSMODE2# | 3.3V          | 12   |

| 13   | C20/RST#      | C16/BUSMODE3# | 14   |

| 15   | 3.3V          | C17/BUSMODE4# | 16   |

| 17   | PCI-RSVD*     | GND           | 18   |

| 19   | DB14/AD[30]   | DB13/AD[29]   | 20   |

| 21   | GND           | DB10/AD[26]   | 22   |

| 23   | DB8/AD[24]    | 3.3V          | 24   |

| 25   | C13/IDSEL     | DB7/AD[23]    | 26   |

| 27   | 3.3V          | DB4/AD[20]    | 28   |

| 29   | DB2/AD[18]    | GND           | 30   |

| 31   | DB0/AD[16]    | C2/C-BE[2]#   | 32   |

| 33   | GND           | PCI-RSVD      | 34   |

| 35   | C5/TRDY#      | 3.3V          | 36   |

| 37   | GND           | C7/STOP#      | 38   |

| 39   | C9/PERR#      | GND           | 40   |

| 41   | 3.3V          | C_OK/C_OK     | 42   |

| 43   | C1/C-BE[1]#   | GND           | 44   |

| 45   | DA14/AD[14]   | DA13/AD[13]   | 46   |

| 47   | GND           | DA10/AD[10]   | 48   |

| 49   | DA8/AD[08]    | 3.3V          | 50   |

| 51   | DA7/AD[07]    | PCI-RSVD      | 52   |

| 53   | 3.3V          | PCI-RSVD      | 54   |

| 55   | PCI-RSVD      | GND           | 56   |

| 57   | PCI-RSVD      | PCI-RSVD      | 58   |

| 59   | GND           | PCI-RSVD      | 60   |

| 61   | C32/ACK64#    | 3.3V          | 62   |

| 63   | GND           | PCI-RSVD      | 64   |

| Pin# | Signal Name        | Signal Name        | Pin# |

|------|--------------------|--------------------|------|

| 1    | PCI-RSVD*          | GND                | 2    |

| 3    | GND                | ED_16/C-BE[7]#     | 4    |

| 5    | BANK1_SEL/C-BE[6]# | BANK2_SEL/C-BE[5]# | 6    |

| 7    | LED1/C-BE[4]#      | GND                | 8    |

| 9    | 5V/V(I/O)          | LED2/PAR64         | 10   |

| 11   | WD_31/AD[63]       | WD_30/AD[62]       | 12   |

| 13   | WD_29/AD[61]       | GND                | 14   |

| 15   | GND                | WD_28/AD[60]       | 16   |

| 17   | WD_27/AD[59]       | WD_26/AD[58]       | 18   |

| 19   | WD_25/AD[57]       | GND                | 20   |

| 21   | 5V/V(I/O)          | WD_24/AD[56]       | 22   |

| 23   | WD_23/AD[55]       | WD_22/AD[54]       | 24   |

| 25   | WD_21/AD[53]       | GND                | 26   |

| 27   | GND                | WD_20/AD[52]       | 28   |

| 29   | WD_19/AD[51]       | WD_18/AD[50]       | 30   |

| 31   | WD_17/AD[49]       | GND                | 32   |

| 33   | GND                | WD_16/AD[48]       | 34   |

| 35   | WD_15/AD[47]       | WD_14/AD[46]       | 36   |

| 37   | WD_13/AD[45]       | GND                | 38   |

| 39   | 5V/V(I/O)          | WD_12/AD[44]       | 40   |

| 41   | WD_11/AD[43]       | WD_10/AD[42]       | 42   |

| 43   | WD_9/AD[41]        | GND                | 44   |

| 45   | GND                | WD_8/AD[40]        | 46   |

| 47   | WD_7/AD[39]        | WD_6/AD[38]        | 48   |

| 49   | WD_5/AD[37]        | GND                | 50   |

| 51   | GND                | WD_4/AD[36]        | 52   |

| 53   | WD_3/AD[35]        | WD_2/AD[34]        | 54   |

| 55   | WD_1/AD[33]        | GND                | 56   |

| 57   | 5V/V(I/O)          | WD_0/AD[32]        | 58   |

| 59   | PCI-RSVD*          | PCI-RSVD*          | 60   |

| 61   | PCI-RSVD*          | GND                | 62   |

| 63   | GND                | PCI-RSVD*          | 64   |

| Pin# | Signal | Signal | Pin# |

|------|--------|--------|------|

|      | Name   | Name   | _    |

| 1    | ED_7   | ED_6   | 2    |

| 3    | ED_5   | ED_4   | 4    |

| 5    | ED_3   | ED_2   | 6    |

| 7    | ED_1   | ED_0   | 8    |

| 9    | WA_19  | WA_18  | 10   |

| 11   | WA_17  | WA_16  | 12   |

| 13   | WA_15  | WA_14  | 14   |

| 15   | WA_13  | WA_12  | 16   |

| 17   | WA_11  | WA_10  | 18   |

| 19   | WA_9   | WA_8   | 20   |

| 21   | WA_7   | WA_6   | 22   |

| 23   | WA_5   | WA_4   | 24   |

| 25   | WA_3   | WA_2   | 26   |

| 27   | WA_1   | WA_0   | 28   |

| 29   | EA_19  |        | 30   |

| 31   | EA_17  | EA_18  | 32   |

| 33   | EA_15  | EA_16  | 34   |

| 35   | EA_13  | EA_14  | 36   |

| 37   | EA_11  | EA_12  | 38   |

| 39   | EA_9   | EA_10  | 40   |

| 41   | EA_7   | EA_8   | 42   |

| 43   | EA_5   | EA_6   | 44   |

| 45   | EA_3   | EA_4   | 46   |

| 47   | EA_1   | EA_2   | 48   |

| 49   | ED_31  | EA_0   | 50   |

| 51   | ED_29  | ED_30  | 52   |

| 53   | ED_27  | ED_28  | 54   |

| 55   | ED_25  | ED_26  | 56   |

| 57   | ED_23  | ED_24  | 58   |

| 59   | ED_21  | ED_22  | 60   |

| 61   | ED_19  | ED_20  | 62   |

| 63   | ED_17  | ED_18  | 64   |

| Pin | Signal  | Signal  | Pin |

|-----|---------|---------|-----|

| #   | Name    | Name    | #   |

| 1   | 6K_WE3# | 6K_WE4# | 2   |

| 3   | 6K_WE1# | 6K_WE2# | 4   |

| 5   | 6K_OE3# | 6K_OE4# | 6   |

| 7   | 6K_OE1# | 6K_OE2# | 8   |

| 9   | CLKIN   | DONE    | 10  |

| 11  | GND     | WAE1#   | 12  |

| 13  | WAE0#   | OE4#    | 14  |

| 15  | OE3#    | OE2#    | 16  |

| 17  | OE1#    | CS4#    | 18  |

| 19  | CS3#    | CS2#    | 20  |

| 21  | CS1#    | WE4#    | 22  |

| 23  | WE3#    | WE2#    | 24  |

| 25  | WE1#    | BE4#    | 26  |

| 27  | BE3#    | BE2#    | 28  |

| 29  | BE1#    |         | 30  |

| 31  |         | SEDATA  | 32  |

| 33  | WAIT    | GCLR    | 34  |

| 35  | CON8    | SERIAL# | 36  |

| 37  | CON6    | CON7    | 38  |

| 39  | CON4    | CON5    | 40  |

| 41  | CON2    | CON3    | 42  |

| 43  | ED_15   | CON1    | 44  |

| 45  | ED_14   | GND     | 46  |

| 47  | GND     | G1      | 48  |

| 49  | GCLK    | ED_13   | 50  |

| 51  | ED_11   | ED_12   | 52  |

| 53  | ED_9    | ED_10   | 54  |

| 55  | RESET#  | ED_8    | 56  |

| 57  | CS      | OE#     | 58  |

| 59  | GND     | RDWR#   | 60  |

| 61  | 5V      | GND     | 62  |

| 63  | GND     | 5V-CLC  | 64  |