# XEPLD SCHEMATIC DESIGN GUIDE

TABLE OF CONTENTS

INDEX

**GO TO OTHER BOOKS**

0401417

# Contents

#### Chapter 1 Getting Started with Schematic Design

| An Overview of Schematic Design Methods               | 1-1  |

|-------------------------------------------------------|------|

| Using the Unified Library                             |      |

| Behavioral Modules and PAL Conversion                 |      |

| Schematic Design Flow Example                         | 1-5  |

| Viewlogic Procedure                                   | 1-6  |

| Step 1 — Configure ViewDraw                           | 1-6  |

| Step 2 — Enter XDM and Select the Device              | 1-6  |

| Step 3 — Enter Workview and Draw the Design           | 1-7  |

| Step 4 — Perform Functional Simulation (Optional)     | 1-7  |

| Step 5 — Fit the Design and Create a Programming File | 1-8  |

| Step 6 — Examine the Reports                          | 1-8  |

| Step 7 — Prepare for Timing Simulation                | 1-8  |

| Step 8 — Perform Timing Simulation                    |      |

| OrCAD Procedure                                       |      |

| Step 1 — Enter XDM and Select the Device              |      |

| Step 2 — Enter and Configure OrCAD                    |      |

| Step 3 — Enter Draft and Draw the Design              |      |

| Step 4 — Add Simulation Information                   |      |

| Step 5 — Prepare for Functional Simulation (Optional) |      |

| Step 6 — Perform Functional Simulation (Optional)     |      |

| Step 7 — Fit the Design and Create a Programming File |      |

| Step 8 — Examine the Reports                          |      |

| Step 9 — Prepare for Timing Simulation                |      |

| Step 10 — Perform Timing Simulation                   | 1-13 |

|                                                       |      |

#### Chapter 2 Device-Independent Design

| Choosing Components                  | 2-1 |

|--------------------------------------|-----|

| When to Use EPLD-Specific Components |     |

| When to Use Common Components        | 2-2 |

|           | Attributes and Device Independence                  | 2-3  |

|-----------|-----------------------------------------------------|------|

|           | General Conversion Procedure: FPGA to EPLD          | 2-3  |

|           | Converting Behavioral Modules                       |      |

|           | FPGA to EPLD Conversion Example: CALC Design        | 2-6  |

|           | Procedure for Viewlogic Users                       | 2-6  |

|           | Reconfiguring the Libraries and Schematic Symbols   | 2-6  |

|           | Editing the Schematic                               | 2-7  |

|           | Performing Functional Simulation                    | 2-8  |

|           | Running the Fitter Commands                         | 2-8  |

|           | Performing Timing Simulation                        | 2-8  |

|           | Procedure for OrCAD Users                           | 2-10 |

|           | Reconfiguring the Libraries and Schematic Symbols   | 2-10 |

|           | Editing the Schematic                               | 2-10 |

|           | Performing Functional Simulation                    | 2-11 |

|           | Running the Fitter Commands                         | 2-13 |

|           | Performing Timing Simulation                        |      |

|           | Converting a Xilinx-ABEL Module (Optional)          | 2-14 |

| Chapter 3 | EPLD Architecture and Design Tradeoffs              |      |

|           | EPLD Architecture                                   | 3-1  |

|           | Input Pad Structures                                |      |

|           | Output Pad Structures                               |      |

|           | High-Density Function Blocks                        |      |

|           | Fast Function Blocks                                |      |

|           | The Universal Interconnect Matrix (UIM)             | 3-4  |

|           | Designing for Speed                                 | 3-4  |

|           | Assigning Logic to Fast Function Blocks             |      |

|           | Logic Requirements for Fast Function Blocks         | 3-5  |

|           | Components Not Allowed in Fast Function Blocks      | 3-6  |

|           | Using Input Pad Registers                           | 3-7  |

|           | Placing Clock Enable Signals in Input Pad Registers | 3-8  |

|           | Using EPLD-Specific Arithmetic Functions            | 3-9  |

|           | Cascading Counters                                  | 3-9  |

|           | Reducing Levels of Logic                            | 3-10 |

|           | Splitting Wide Functions                            | 3-11 |

|           | Random Logic                                        | 3-12 |

|           | Designing for Density                               | 3-13 |

|           | Maximally Encoding State Machines                   | 3-13 |

|           | Using Global Nets                                   |      |

|           | Moving Logic into the Universal Interconnect Matrix |      |

|           | Using Input Pad Registers                           | 3-15 |

| Macrocell Register vs. I/O Pin Tradeoff             | 3-15 |

|-----------------------------------------------------|------|

| UIM Versus Fast Input Paths                         | 3-16 |

| Controlling Logic Optimization                      | 3-16 |

| Master Reset Pin Tradeoffs                          | 3-16 |

| Designing to Preserve the Pinout                    | 3-17 |

| Manual Pin Assignment                               | 3-18 |

| Manual Pin Assignment Precautions                   | 3-19 |

| The LOC Attribute                                   | 3-20 |

| Controlling Power Consumption                       | 3-20 |

| Controlling Preload Values                          | 3-20 |

| Physical Resources of EPLDs                         | 3-21 |

| Attributes for Controlling Preload Values           | 3-22 |

| Preload Values for Functional and Timing Simulation | 3-22 |

| Destant Annelles d'anne                             |      |

#### Chapter 4 Design Applications

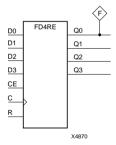

| Reset and Preload Control in FFB and Input Pad Registers | 4-1  |

|----------------------------------------------------------|------|

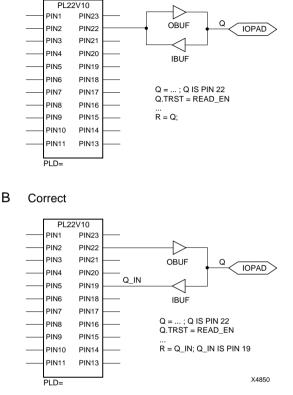

| Read-Back Registers                                      | 4-2  |

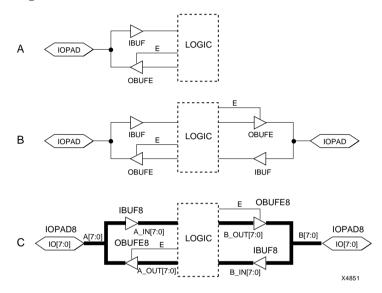

| Bidirectional Signals and Buses                          | 4-3  |

| Bidirectional Signals in PLDs                            | 4-3  |

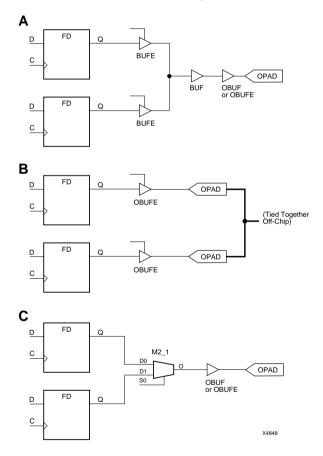

| Multiplexing 3-State Signals                             | 4-4  |

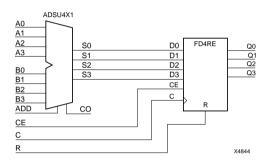

| Optimizing Registered Arithmetic Performance             | 4-6  |

| Hierarchical Design                                      | 4-10 |

| Schematic Custom Component Example                       | 4-11 |

## Chapter 5 Using Behavioral Modules in Schematics

| Preparing a Component                 | 5-1  |

|---------------------------------------|------|

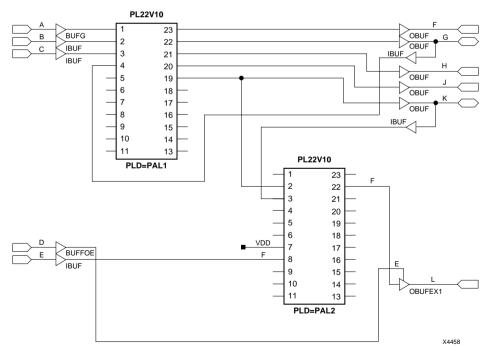

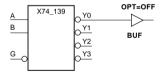

| Behavioral Module Example             | 5-2  |

| Choosing the Behavioral Design Method | 5-4  |

| Using PLUSASM                         | 5-4  |

| PLUSASM File Structure                | 5-4  |

| Using JEDEC Files                     | 5-6  |

| Using Xilinx ABEL                     |      |

| Using a PLD Compiler                  |      |

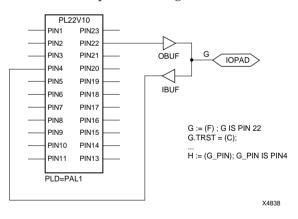

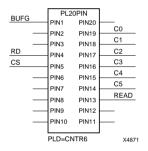

| Choosing the Symbol                   | 5-7  |

| Using the PL22V10 or PL20V8           |      |

| Using SymGen to Create Custom Symbols | 5-8  |

| Viewlogic Symbols                     | 5-8  |

| OrCAD Symbols                         | 5-9  |

| Editing Existing Library Components   | 5-9  |

| Storing Custom Components             | 5-10 |

| Viewlogic Components                  | 5-10 |

|                                       |      |

|   | OrCAD Components                                 | 5-11 |

|---|--------------------------------------------------|------|

|   | Editing Behavioral Modules for Use in Schematics | 5-11 |

|   | Assigning Output Enable Signals to FOE Nets      | 5-13 |

|   | Assigning Functions to Fast Function Blocks      | 5-13 |

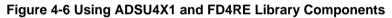

|   | Assigning Bidirectional I/O Signals              | 5-13 |

|   | Case 1 — Bidirectional Outputs That Go Off-Chip  | 5-14 |

|   | Case 2 — Using Both Macrocell and Pin Feedback   | 5-15 |

| 6 | Design Varification                              |      |

## Chapter 6 Design Verification

| Simulating Designs                                  | 6-1 |

|-----------------------------------------------------|-----|

| Making a ViewSim or VST Functional Simulation Model | 6-1 |

| Making a ViewSim or VST Timing Simulation Model     | 6-2 |

| Using XNF-Compatible Simulators                     | 6-2 |

| Simulating Board-Level Designs in Viewlogic         | 6-3 |

| Functional Simulation                               | 6-3 |

| Timing Simulation                                   | 6-3 |

| Preload Values in Functional and Timing Simulation  | 6-4 |

| Verifying Designs                                   | 6-5 |

| Verifying Design Fit                                | 6-5 |

|                                                     |     |

#### Appendix A Common Questions and Answers

| Drawing the Design A-                                  | 1  |

|--------------------------------------------------------|----|

| Why Do I See White Boxes Instead of Components? A-     | 1  |

| Why Are Some of My Components Missing? A-2             | 2  |

| Fitting the Design A-2                                 | 2  |

| What Does "Component Not Found" Mean? A-2              | 2  |

| What Does "Component Not Supported" Mean? A-3          | 3  |

| Why Can't I Make a Direct Pin-To-Pin Path? A-4         | 4  |

| What Does "Has No Logic Connection" Mean? A-4          | 4  |

| What Do I Do If I Have "Hanging Inputs"? A-8           | 5  |

| Why Are Some of the Outputs Removed? A-8               | 5  |

| What Does "The Tristate Will Affect the Pad" Mean? A-6 | 6  |

| What Does "Connects to an External Pad" Mean? A-6      | 6  |

| What If My Design Doesn't Fit? A-6                     | 6  |

| If Your Design is Product Term Constrained A-7         | 7  |

| If Your Design is FB Input Constrained A-8             | 8  |

| If Your Design has Unused Fast Function Blocks A-S     | 9  |

| Simulating the Design A-                               | 10 |

| Why Can't I Functionally Simulate a Design with a      |    |

| Behavioral Module? A-                                  | 10 |

| Why Are My Registers Stuck at the Preload Value? A-    | 10 |

|             | Simulation?<br>Why Do Functional and Timing Simulation Yield Different | A-10 |

|-------------|------------------------------------------------------------------------|------|

|             | Results?                                                               | A-12 |

| Appendix B  | Attributes                                                             |      |

|             | Component Attributes                                                   |      |

|             | Viewlogic Procedure                                                    | B-2  |

|             | OrCAD Procedure                                                        | B-2  |

|             | Global Attributes                                                      | B-2  |

|             | Viewlogic Procedure                                                    | B-3  |

|             | OrCAD Procedure                                                        | B-3  |

|             | Net or Flag Attributes                                                 | B-3  |

|             | Net Attributes (Viewlogic)                                             | B-4  |

|             | Flag Attributes (OrCAD)                                                | B-4  |

|             | Target Device Selection — The PART Attribute                           | B-4  |

|             | Viewlogic Procedure                                                    | B-5  |

|             | OrCAD Procedure                                                        |      |

|             | PLD Equation File Name — The PLD Attribute                             | B-5  |

|             | Pin Assignment — The LOC Attribute                                     | B-7  |

|             | Power Setting — The LOWPWR Attribute                                   | B-7  |

|             | F/H                                                                    | B-8  |

|             | MRINPUT                                                                |      |

|             | Logic Optimization Attributes                                          | B-9  |

|             | OPT=OFF and OPT=ON                                                     | B-9  |

|             | OPT=UIM                                                                | B-10 |

|             | LOGIC_OPT                                                              | B-10 |

|             | MINIMIZE                                                               | B-10 |

|             | UIM_OPT                                                                | B-10 |

|             | FOE_OPT                                                                | B-10 |

|             | CLOCK_OPT                                                              | B-11 |

|             | REG_OPT                                                                | B-11 |

|             | PRELOAD_OPT                                                            | B-11 |

|             | INIT                                                                   | B-12 |

| Index       |                                                                        | i    |

| Trademark I | nformation                                                             |      |

Why Are My Internal Nodes Not Visible During Timing

# **Chapter 1**

# **Getting Started with Schematic Design**

This chapter will help you quickly understand how to develop a schematic design using XEPLD. Brief schematic design examples are included, illustrating the device-independent schematic library and the automatic PAL conversion process.

# An Overview of Schematic Design Methods

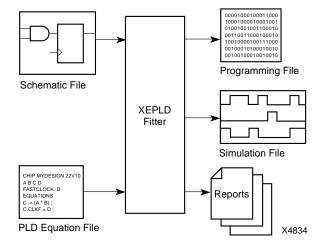

A schematic design defines the functionality of a logic circuit using one or more schematic files, each of which contains components whose functions are already defined (74xx TTL or similar functions) and components for which you define the function using behavioral modules. Figure 1-1 summarizes the design flow.

Figure 1-1 Basic Schematic Design Flow

The Viewlogic, OrCAD, Mentor, and Cadence software packages are supported.

The following sections provide an overview of methods for creating schematics and behavioral modules for schematic designs.

# **Using the Unified Library**

The Unified Library allows you to create a device-independent design to test how the design works in different devices, or to create a device-specific design to take full advantage of a device's unique architectural features.

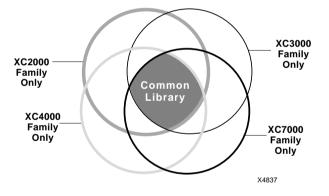

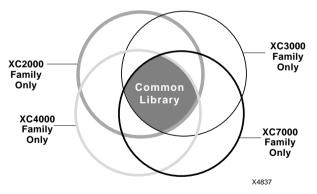

The Unified Library contains all the component symbols for all the available device families. As illustrated in Figure 1-2, most of the symbols can be used in designs targeted for any Xilinx device, but some of the symbols are specific to one or more device families.

# **Xilinx Unified Library**

#### Figure 1-2 Device Families and the Unified Library

The common symbols are automatically mapped to the chosen target device. The same common symbol may be mapped differently to target devices with different architectures.

The "Device-Independent Design" chapter describes the library components and how to retarget an existing FPGA design to an EPLD device.

For more information about the Unified Library, refer to the XACT *Libraries Guide*.

# **Behavioral Modules and PAL Conversion**

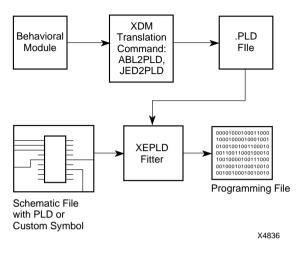

There are two ways to include a behavioral module in a schematic design. Both are described in the chapter entitled "Using Behavioral Modules in Schematics."

- Use a PLD symbol from the XC7000 library. This method is best if you have a module that is already targeted to a standard PAL such as a 22V10.

- Create a custom component, and use SymGen to create the custom symbol for it. This method is best if your behavioral module is not already targeted to a standard PAL, for example if it is a state machine expressed in a high-level language.

The PLD symbols are a special group of EPLD-specific symbols in the Unified Library. You define the logic behind these symbols in a behavioral design file. To create a custom symbol, you create the behavioral design file, then use SymGen to create a symbol based on the file.

The original design file can be a new file created using the PLUSASM<sup>™</sup> language or an existing PAL file converted to PLUSASM. You can convert the following types of files to PLUSASM files and use them with PLD symbols:

- ABEL

- PALASM

- JEDEC

Figure 1-3 shows the design flow for including a behavioral module.

**Figure 1-3 Schematic PAL Conversion Flow**

# **Schematic Design Flow Example**

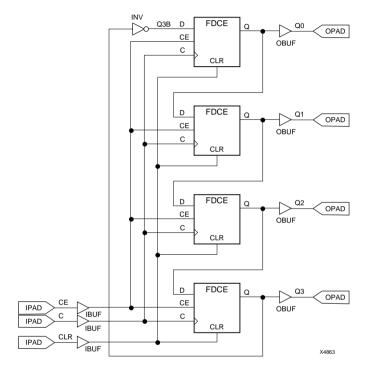

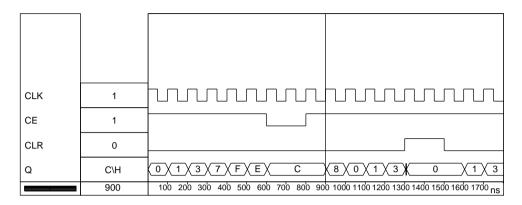

This section runs through the entire schematic design process, from creating a design to programming and simulating the design. The following device-independent design, a 4-bit Johnson counter, is used as an example:

Figure 1-4 Example 4-Bit Johnson Counter Design

Simulation results for this design are shown in Figure 1-5.

This design contains no behavioral modules. For an example of a design that includes a behavioral module, see the chapter entitled "Using Behavioral Modules in Schematics."

The steps are summarized for Viewlogic and OrCAD.

## **Viewlogic Procedure**

#### Step 1 — Configure ViewDraw

Create a directory for your design. Copy the viewdraw.ini file from your workview\standard directory into that directory, and edit the end of it to include the following lines:

DIR [pw] . (primary)

DIR [m] \correct\_path\unified\xc7000 (xc7000)

DIR [m] \correct\_path\unified\builtin (builtin)

Note: Use [r] instead of [m] if you are using a UNIX workstation.

You could also use ViewFile to configure your library directory specifications.

#### Step 2 — Enter XDM and Select the Device

Enter XDM by typing the following at the operating system prompt:

XDM

Select the device family and part by clicking on the **Family** and **Part** fields in the lower left corner of the screen. For the family, select "XC7300". For the part, select "XC7318-PC44". For the speed grade, select "–5".

#### Step 3 — Enter Workview and Draw the Design

Enter Workview by selecting **DesignEntry**  $\rightarrow$  **Workview** from the XDM menu.

When the Workview screen appears, type the following to create a new schematic:

#### sch jcount

Draw the design as shown in Figure 1-5. For more information about using ViewDraw, see the *Viewlogic Interface User Guide*.

If you do not wish to draw the design, you can copy the jcount.1 schematic file in the \xact\tutorial\vwlogic\jcount\sch directory (\$XACT/tutorial/vwlogic/jcount/sch on the workstation).

**Note:** It is important that you label the nets between the IPADs and IBUFs and between the OPADs and OBUFs, because these names will appear in reports and on simulation traces.

Save your design using the **File**  $\rightarrow$  **Write** command.

#### Step 4 — Perform Functional Simulation (Optional)

If you wish to perform functional simulation, first use the **Export** → **Wirelist** → **ViewSim** command to create a simulation file.

Use the **Window**  $\rightarrow$  **Open**  $\rightarrow$  **ViewSim S**/**D** command to enter ViewSim. Type  $\rightarrow$  in response to the network file name prompt.

Type **jcount** to run the following command file, jcount.cmd, which simulates the design:

```

restart

vector Q Q[3:0]

wave jcount.wfm CLK CE CLR Q

clock c 1 0

step 50ns

h prld

h CE

l CLR

cycle

l prld

cycle 5

l CE

```

```

cycle 2

h CE

cycle 5

h CLR

cycle 2

l CLR

cycle 3

```

To view the waveform file, type **wv**, then type  $\leftarrow$  when prompted for the file name.

Exit Workview by typing **quit**. If asked Are you sure? type **y**. You are back in XDM.

#### Step 5 — Fit the Design and Create a Programming File

Select **Translate**  $\rightarrow$  **XEMake**. Select **Done** in response to the options window. Select the **jcount.1** file from the list. Finally, select **Make Intel HEX File** as the target. Type **jcnt.a** as the signature.

The XEMake command creates a netlist, fits the design, and creates a programming file in one step.

#### Step 6 — Examine the Reports

Examine the reports to verify that the design was implemented as you expected. The following reports are most useful for schematic designs:

- *design*.ERR This is the error log. Use it to correct mistakes in your design.

- *design*.RES The resource report lists the device resources used by the design and the resources remaining.

- *design*.PIN The pinlist report shows how the external nets in your design were mapped to the device pins.

- *design*.MAP The mapping report tells you how the logic in the design was mapped to the device.

#### Step 7 — Prepare for Timing Simulation

To prepare for timing simulation, select **Verify** → **XSimMake**. Select **Viewlogic\_EPLD\_Timing** as the flow name. Select **jcount.vmh** as the file name.

#### Step 8 — Perform Timing Simulation

When XSimMake is finished running, enter Workview again and follow the same instructions as for functional simulation.

#### **OrCAD** Procedure

#### Step 1 — Enter XDM and Select the Device

Enter XDM by typing the following at the operating system prompt:

XDM

Select the device family and part by clicking on the **Family** and **Part** fields in the lower left corner of the screen. For the family, select "XC7300". For the part, select "XC7318-PC44". For the speed grade, select "–5".

#### Step 2 — Enter and Configure OrCAD

Enter OrCAD by selecting **DesignEntry**  $\rightarrow$  **OrCAD** from the menu.

Double click on **Design Management Tools**. Click on **Create Design**.

In the prompt box that appears, type **jcount**, then click on **OK**.

The JCOUNT design appears, highlighted, in the list. Click on **Suspend to System**. Type the following at the DOS prompt:

xdraft 7

(wait for the command to complete)

exit

You are back in the Design Management Tools window. Click on **OK** to exit.

#### Step 3 — Enter Draft and Draw the Design

Double click on **Schematic Design Tools**. Double Click on **Draft**. A blank schematic window appears.

Draw the design as shown in Figure 1-5. For more information about using Draft, see the *OrCAD Interface User Guide*.

If you do not wish to draw the design, you can copy the jcount.sch schematic file in the xact\tutorial\orcad\jcount directory.

**Note:** It is important that you label the nets between the IPADs and IBUFs and between the OPADs and OBUFs, because these names will appear in reports and on simulation traces.

#### Step 4 — Add Simulation Information

To add trace information, follow these steps for each net that is between an IPAD and an IBUF or between an OBUF and an OPAD:

- Place the mouse cursor over the net and select the Place → Trace Name command.

- 2. In response to the Trace Name? prompt, type the name of the net, for example **CE**.

- 3. Double click to place the trace marker, then click with the right button to exit the command.

To add stimulus information, follow these steps for each net that is between an IPAD and an IBUF:

- Place the mouse cursor over the net and select the Place → Stimulus command.

- 2. In response to the Stimulus? prompt, type the following:

For CE:

0:1 6000:0 8000:1

For CLK:

0:0 500:T 1000:G:500

For CLR:

0:0 13000:1 15000:0

3. Double click to place the stimulus marker, then click with the right button to exit the command.

Save your design using the  $Quit \rightarrow Update$  File command. Exit Draft using  $Quit \rightarrow Abandon$  Edits.

To exit OrCAD, double click on **To Main**, then on **Exit ESP**. You are back in XDM.

#### Step 5 — Prepare for Functional Simulation (Optional)

To prepare for functional simulation, select  $Verify \rightarrow XSimMake$ . Select  $Orcad\_EPLD\_Func$  as the flow name. Select jcount.sch as the file name.

XSimMake produces ASCII versions of OrCAD stimulus and trace files, which you must convert to binary. The conversion command is memory-intensive, so it is best to execute it in DOS.

Quit XDM using the **Quit** command. Type the following at the DOS prompt:

asctovst jcount.ast

(wait for the command to complete)

asctovst jcount.atr

(wait for the command to complete)

xdm

You are back in XDM.

#### Step 6 — Perform Functional Simulation (Optional)

Enter OrCAD by selecting **DesignEntry**  $\rightarrow$  **OrCAD** from the menu. Double click on **Design Management Tools**, select **JCOUNT** from the list, and click on **OK**.

Double Click on Digital Simulation Tools.

Click once on Simulate. Select Local Configuration and then Configure Simulate. Change jcount.inf to jcount.vst, then select OK.

Double click on **Simulate**. A blank simulation waveform window appears with the R, Q3, Q2, Q1, Q0, CE, and CLK nets listed.

Select **Edit** Stimulus  $\rightarrow$  Yes. The Stimulus Editor window appears.

Select **Add**. Press the down arrow key to highlight the **Signal Name** field, then select **Browse**. Type a **P** to scroll down to the net names beginning with P. Press the down arrow key to highlight **PRLD**, then press  $\dashv$ .

Press the down arrow key to highlight the **Initial Value** field. Type **1**.

Press the down arrow key again. Select **Add**. In response to Time of Function? type **10**, then press → to accept a 0 (zero) value.

Select **Return** to return to the main stimulus editor, select **Write**  $\rightarrow$  **Yes** to add PRLD to the stimulus file, and select **Use** to return to the waveform window.

Select **Trace** → **Change** View and enter **150**. Select **Run Simulation** and enter **18000**. The simulation waveforms appear.

Exit Simulate using  $Quit \rightarrow Abandon Simulation$ .

To exit OrCAD, double click on **To Main**, then on **Exit ESP**. You are back in XDM.

#### Step 7 — Fit the Design and Create a Programming File

Select **Translate** → **XEMake**. Select **Done** in response to the options window. Select the **jcount.sch** file from the list. Finally, select **Make Intel HEX File** as the target. Type **jcnt.a** as the signature.

The XEMake command creates a netlist, fits the design, and creates a programming file in one step.

#### Step 8 — Examine the Reports

Examine the reports to verify that the design was implemented as you expected. The following reports are most useful for schematic designs:

- *design*.ERR This is the error log. Use it to correct mistakes in your design.

- *design*.RES The resource report lists the device resources used by the design and the resources remaining.

- *design*.PIN The pinlist report shows how the external nets in your design were mapped to the device pins.

- *design*.MAP The mapping report tells you how the logic in the design was mapped to the device.

#### Step 9 — Prepare for Timing Simulation

To prepare for timing simulation, select **Verify** → **XSimMake**. Select **Orcad\_EPLD\_Timing** as the flow name. Select **jcount.vmh** as the file name.

#### Step 10 — Perform Timing Simulation

If you skipped functional simulation, follow the preceding instructions for functional simulation. If you did perform functional simulation, follow the instructions in this section.

Enter OrCAD by selecting **DesignEntry**  $\rightarrow$  **OrCAD** from the menu. Double click on **Design Management Tools**, select **JCOUNT** from the list, and click on **OK**.

Double Click on **Digital Simulation Tools**. Double click on **Simulate**. A blank simulation waveform window appears with the R, Q3, Q2, Q1, Q0, CE, and CLK nets listed.

Select **Trace** → **Change** View and enter **125**. Select **Run Simulation** and enter **15000**. The simulation waveforms appear.

Exit Simulate using  $Quit \rightarrow Abandon Simulation$ .

To exit OrCAD, double click on **To Main**, then on **Exit ESP**. You are back in XDM.

# **Chapter 2**

# **Device-Independent Design**

This chapter discusses how and why to create a device-independent or device-specific design. It also explains how to take an existing FPGA design and retarget it to an EPLD device.

# **Choosing Components**

The Unified Library contains all Xilinx component symbols, some of which are specific to one device family, some of which are common to two or more families, and some of which are common to all families.

## Xilinx Unified Library

#### Figure 2-1 Common Symbols in the Unified Library

When a component of the same name is present in multiple families' libraries, it has the same functionality and graphic symbol body, and similarly named pins. However, the component's implementation, including whether the symbol is a primitive (behavioral module) or macro (schematic module), may vary between families.

### When to Use EPLD-Specific Components

In general, common library components work well for EPLD designs. You should use XC7000-specific components only under these special conditions:

- If you are cascading arithmetic components, you should use EPLD-specific arithmetic components, because the carry lines that go between components are mapped to the carry chain.

- If you are cascading up/down counters, you should use EPLDspecific counters, because the separate up and down terminal counts can be placed in the UIM for greater speed and density.

- If you need input pad registers with clock enable, you must use an EPLD-specific component such as IFDX1.

For example, suppose you were working on a design that needed an 8-bit full adder. In most designs, you could use a device-independent adder, such as ADD8. If this component is used in an EPLD design, the internal logic is mapped onto the special EPLD arithmetic carry lines; if used in an FPGA design, the logic is mapped in the way that is most efficient for the FPGA's architecture.

However, if you needed to cascade two 8-bit adders, it would be most efficient to use EPLD-specific adders, because the carry lines that go between components would be mapped to the carry chain.

#### When to Use Common Components

To make your design device-independent, use only the symbols common to all device families — the shaded area in Figure 2-1. The XACT software automatically maps the symbols in your design onto the chosen target device. Creating a device-independent design allows you to easily test your design with different Xilinx devices.

For a complete list of Unified Library components and their compatibility with the different Xilinx device families, refer to the *XACT Libraries Guide*.

# **Attributes and Device Independence**

If you want your design to be completely device-independent, do not use schematic attributes. The only attributes common to FPGA and EPLD devices are as follows:

- PART=*device\_name* (or PARTTYPE in OrCAD)

- LOC=device\_pin

Even these attributes are not truly device independent, because you must change the values when you change devices. All other EPLDcompatible attributes are EPLD-specific. For more information about these attributes, refer to the "Attributes" appendix. These attributes are also described in the context of how they are used in the "EPLD Architecture and Design Tradeoffs" and "Design Applications" chapters of this manual.

# **General Conversion Procedure: FPGA to EPLD**

The basic steps for retargeting an FPGA design to an EPLD device are as follows. Examples in this section assume you are converting from the XC3000 family.

- 1. Change (cd) to your working directory and reconfigure the libraries in your CAE tool for the XC7000 family.

- If you are using Viewlogic software, edit your viewdraw.ini file so it looks like this:

DIR [pw] . (primary) DIR [r] /correct\_path/unified/xc3000 (xc3000) DIR [r] /correct\_path/unified/xc7000 (xc7000) DIR [r] /correct\_path/unified/xblox (xblox) DIR [r] /correct\_path/unified/builtin (builtin)

Substitute the path to your libraries for *correct\_path*. Leave the XC3000 library reference in the file, because the Altran command, which you will use in the next step, requires it.

• If you are an OrCAD user, type the following at the DOS prompt while in your working directory:

xdraft 7

- 2. Use any necessary conversion program to make the symbols in your schematic reference the reconfigured libraries. If you are using OrCAD software, skip this step.

- If you are using Viewlogic software, use the Altran command, where *N* is 2, 3, or 4:

#### altran -1 primary xcN000=xc7000

- 3. Enter your CAE tool and open your design.

- 4. Find all the library components in the schematic that are not EPLD-compatible, and use the *XACT Libraries Guide* to find EPLD-compatible equivalents.

- If you have run Altran on a Viewlogic schematic, incompatible components appear as white squares in the schematic.

- If you have run XDraft 7 on an OrCAD schematic, the incompatible components generate error messages in OrCAD and do not appear in the schematic.

- 5. If necessary, use EPLD-specific components to obtain a more efficient design. In most cases, device-independent components are mapped onto the EPLD architecture efficiently, but there are exceptions, which are described in the "When to Use EPLD-Specific Components" section earlier in this chapter.

- 6. Remove all attributes except PART=*device\_name* and LOC=*pin\_name*. You can change the device name to the new target device if you wish. If you wish to reassign pins, see the "EPLD Architecture and Design Tradeoffs" chapter for information about EPLD pin assignment. If you do not wish to reassign pins, remove the LOC=*pin\_name* attributes as well.

- 7. You may want to look over the list of EPLD attributes, especially the optimization attributes, and use them to fine-tune your design. The software optimizes everything it can by default; you may want to prevent optimization in some cases, for example to ensure that an internal node is visible during timing simulation.

- Enter XDM. Run the XEMake command to fit your design. Run XSimMake if you also want to perform functional or timing simulation.

- When you perform either functional or timing simulation, you must set the PRLD (preload) signal High then Low instead of setting GR (global reset) Low then High.

- 10. If you wish to perform timing simulation, you may have to change the nodes you drive and monitor. The EPLD fitter optimizes the logic, which makes many of the internal nodes in the design disappear. However, all external signals are always visible.

**Note:** If your FPGA design has RAM, ROM, or other elements that do not have EPLD equivalents, you cannot retarget your design unless you redesign those parts.

#### **Converting Behavioral Modules**

If your design contains Xilinx-ABEL or XBLOX modules, you must perform these additional steps before running XEMAKE:

Change the encoding of state machine modules. You do not have to rewrite the logic, just the state assignment. For FPGAs, which are rich in registers, one-hot encoding (a symbolic state machine) is most efficient. For EPLDs, which are rich in product terms, maximal encoding (an encoded state machine) is most efficient. Conversion may be unnecessary for very simple state machines.

For more information about symbolic and encoded state machines, see the "Simulating an ABEL-HDL Design" and "Converting Encoded State Machine to Symbolic State Machine" sections in the "Design Examples" chapter of the *Xilinx ABEL User Guide*. You should follow the steps of the latter section in reverse.

- Convert the files behind all Xilinx-ABEL modules to PLUSASM using the ABL2PLD command. Use the existing Xilinx-ABEL symbols, but remove the DEF=XABEL and FILE=*file\_name* attributes, replacing them with PLD=*file\_name*. To ensure that the software does not process old files, delete the *file\_name*.xnf files in the xnf directory.

- 3. Convert the XBLOX modules. There is no straightforward conversion—you can rewrite the logic using a behavioral entry tool (PLUSASM, Xilinx-ABEL, ABEL) or create an EPLD-compatible lower-level schematic.

# FPGA to EPLD Conversion Example: CALC Design

The CALC design is extensively documented in the tutorial chapters of the Xilinx Interface User Guide for your CAE tool. It is used as an example of an FPGA design. This section describes the steps necessary to convert the XC3000 version of this design to an EPLD design.

The steps are different for each CAE tool. The procedure for Viewlogic users is described first, followed by OrCAD.

#### **Procedure for Viewlogic Users**

#### **Reconfiguring the Libraries and Schematic Symbols**

To reconfigure the libraries for the XC7000 family and update all the symbols so their properties are compatible with XC7000 devices, follow these steps:

- Copy the CALC tutorial files to a directory under your home directory as described in the *Xilinx Viewlogic Interface User Guide*. Change (cd) to the calc/soln\_3k directory.

- 2. Edit your viewdraw.ini file so it looks like this:

```

DIR [pw] . (primary)

DIR [r] /correct_path/unified/xc3000 (xc3000)

DIR [r] /correct_path/unified/xc7000 (xc7000)

DIR [r] /correct_path/unified/xblox (xblox)

DIR [r] /correct_path/unified/builtin (builtin)

```

Substitute the path to your libraries for *correct\_path*. Leave the XC3000 library reference in the file, because the Altran command, which you will use in the next step, requires it.

3. While in your working directory, type this command at the operating system prompt:

```

altran -1 primary xc3000=xc7000

```

#### **Editing the Schematic**

To edit the schematic so all its symbols are compatible with XC7000 devices, follow these steps:

- Start up XDM. Select the Workview command from the Design-Entry menu.

- Open the CALC schematic. Select the OSC\_3K symbol and select the Level → Push → Schematic command.

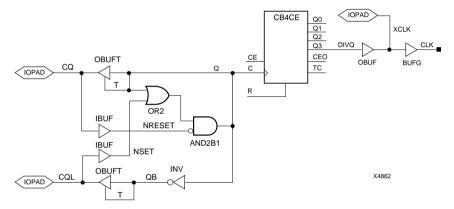

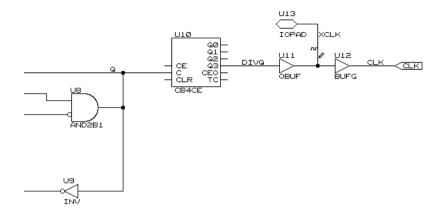

- 3. Edit the schematic so it looks like Figure 2-2:

#### Figure 2-2 New Viewlogic Oscillator Schematic for EPLD CALC

- 4. Be sure to label the new IOPAD net "XCLK".

- 5. Select the File → Write command. Select the Level → Pop command. (If you wish, you can use the File → Write to command to save this schematic as OSC\_7K. If you save this schematic to a new name, be sure to save the corresponding symbol file to the same name. In addition, make sure the new symbol is added to and saved in the top-level CALC schematic.)

- 6. Search the top-level schematic and every sub-schematic for attributes, including LOC= pin assignments. Delete all except the PART= attribute. Attributes are displayed in yellow to distinguish them from labels, which are white. Save each schematic that you change using the File → Write command.

Use the Change → Text command to change the part name as follows:

```

PART=7372-10PC68

```

8. Save the top-level schematic using the **File**  $\rightarrow$  **Write** command.

#### **Performing Functional Simulation**

To perform functional simulation, follow these steps:

- 1. Select the **Export** → **Wirelist** → **ViewSim** command.

- 2. Run simulation as described in the ViewSim tutorial in the *Viewlogic Interface User Guide*, except change these lines in the calc\_3k.cmd file (which you can rename calc\_7k.cmd if you wish):

```

l gr

...

h gr

```

to the following:

h prld ... l prld

#### **Running the Fitter Commands**

To map the design onto a target XC7000 device, follow these steps:

1. Exit Workview by typing the following:

quit

- 2. Select the **XEMake** command from the **Translate** menu in XDM.

- 3. Select **Done** to select all the default options.

- 4. Select the **calc.1** file from the list.

- 5. Select Make design database as the target.

#### **Performing Timing Simulation**

To perform timing simulation, follow these steps:

1. Select the **XSimMake** command and **Viewlogic\_EPLD\_Timing** as the flow name. Select the **calc.vmh** file from the list.

2. Run simulation as described in the ViewSim tutorial in the *Viewlogic Interface User Guide*, except change the lines in the Vector Definition, Simulation Output Definition, Clock Definition, and Global Reset & Initial Input Values to those shown in the following file. The ... indicates comments that have been removed.

You must make these changes because the EPLD fitter optimizes the logic, removing many internal nodes. This makes the design more efficient, but harder to simulate.

```

-----VECTOR DEFINITION-------

. . .

vector SW sw7\sw6_p sw7\sw5_p sw7\sw4_p sw7\sw3_p +

sw7\sw2_p sw7\sw1_p sw7\sw0_p

You can also use bus syntax when defining vectors

vector ALU alu[3:0]

vector LED_P led\led[3:0]_p

Set radices for vectors

The default radix is binary for input, hex for output

radix hex SW ALU

radix bin LED_P

-----SIMULATION OUTPUT DEFINITION---------

wave calc_7k.wfm osc_7k\xclk SW exc_p ALU LED_P we rst

| Save simulation values for these nodes

watch osc_7k\xclk SW exc_p ALU LED_P we rst

| Output the values of all watched signals each time

"xclk" goes high. Create tabular output.

break osc_7k\xclk 1 do (print > calc_7k.tab)

| Output node and vector transitions and simulation time

whenever any of the nodes or vectors changes state

trace osc_7k\xclk SW exc_p ALU LED_P we rst > calc_7k.trc

-----CLOCK DEFINITION------

clock osc_7k\xclk 1 0

Use a clock period of 100ns. Set stepsize=50ns

step 50ns

-----GLOBAL RESET & INITIAL INPUT VALUES------

Set initial values for all inputs using the "H" and "L"

commands for nets and "assign" for vectors

h exc_p

assign SW 00\h

Initialize all flip-flops (preload- is active high

for 7k designs, you can abbreviate to prld)

h prld

Viewsim uses units of 0.1 ns, so this statement

simulates for 100 ns.

cycle

l prld

cycle

```

## **Procedure for OrCAD Users**

#### **Reconfiguring the Libraries and Schematic Symbols**

To reconfigure the libraries for the XC7000 family and update all the symbols so their properties are compatible with XC7000 devices, follow these steps:

- Copy the CALC tutorial files to a directory under your home directory as described in the OrCAD Interface User Guide. Change (cd) to the calc\soln\_3k directory.

- 2. While in your working directory, type the following at the DOS prompt:

xdraft 7

#### **Editing the Schematic**

To edit the schematic so all its symbols are compatible with XC7000 devices, follow these steps:

- 1. Start up XDM. Select the **OrCAD** command from the **DesignEntry** menu.

- 2. Double click on the **Design Management Tools** button. Select **CALC** from the list on the left, then select the **OK** button.

- 3. Enter **Schematic Design Tools** and then **Draft**. The toplevel schematic of the CALC design appears. If you see a message about an X being deleted, do not worry; this is an FPGA-specific property that you would have to delete anyway.

- 4. Change the PART= text to 7372-10PC68.

- 5. Enter the OSC\_3K sheet symbol using the Quit  $\rightarrow$  Enter Sheet  $\rightarrow$  Enter command.

The OSC\_3K schematic is displayed. There may be messages telling you that two components, ACLK and GCLK, are unavailable. The spaces where these two components were on the original schematic are left open, with unconnected nets.

6. Edit the schematic so it looks like Figure 2-3. The part of the schematic that is not visible is unchanged except for LOC= properties being removed.

#### Figure 2-3 New OrCAD Oscillator Schematic for EPLD CALC

- 7. Be sure to label the new IOPAD net "XCLK".

- Be sure to delete the LOC=... properties from the two IOPADs at the left end of the schematic. (Use the Edit → Edit → 1st Part Field → Name command.)

- 9. Select Quit  $\rightarrow$  Update File  $\rightarrow$  Leave Sheet.

- 10. Use the Quit → Enter Sheet, Edit → Edit → 1st Part Field → Name, and Quit → Update File → Leave Sheet commands to delete all the LOC= and FAST statements in the CALC schematic and all its sub-schematics.

- 11. When you are finished editing all the schematics, select Quit → Update File → Abandon Edits from the top-level schematic, double click on the To Main button, double click on the Exit ESP button, and press any key to return to XDM.

#### **Performing Functional Simulation**

To perform functional simulation, follow the instructions in the "VST Tutorial" chapter of the *OrCAD Interface User Guide*, with the exceptions in the following steps.

1. If you plan to perform timing simulation later, place stimulus and trace information on the XCLK signal in the OSC\_3K schematic

instead of on the CLK signal, and on the LED\_P signals in the LED schematic instead of on the STACK signals (pp. 12-6 to 12-8).

- 2. In addition, you will have to move the stimulus information in the SW7 schematic from the SW signals to the SW\_P signals and subtract one clock cycle. Follow these steps:

- a) Place the mouse cursor on the stimulus symbol on the SW4 signal and select the **Inquire** command. The following line is displayed in the top left corner of the screen:

Stimulus: 0:0 6000:1

- b) Subtract 500 time units, which is equal to one clock cycle, from the times at which the signal changes value. Replace all time values less than or equal to 500 with 0. In this case, 0 remains 0 and 6000 becomes 5500.

- c) Use the Place → Stimulus command to add the following stimulus to the SW4\_P signal:

0:0 5500:1

- d) Delete the stimulus indicator on the SW4 signal.

- e) Repeat steps a through d to delete all stimulus information from each SW signal and add it to each SW\_P signal.

- f) Use  $Quit \rightarrow Update$  File to save your edits.

The EPLD fitter software optimizes away many internal nodes such as the CLK, STACK, and SW7 signals, but cannot optimize external signals such as the XCLK, LED\_P, and SW\_P signals. This does not affect functional simulation, but it does affect timing simulation.

- Substitute "EPLD" wherever the VST Tutorial says "FPGA". For example, select Orcad\_Epld\_Func as the XSIMMAKE flow name instead of Orcad\_Fpga\_Func.

- 4. Instead of adding a GR or GSR stimulus (p. 12-21), add a PRLD stimulus. Like GSR, the PRLD stimulus has an initial value of 1 and is brought down to 0 at 1 nanosecond.

#### **Running the Fitter Commands**

To map the design onto a target XC7000 device, follow these steps:

- 1. Select the **XEMake** command from the **Translate** menu in XDM.

- 2. Select **Done** to select all the default options.

- 3. Select **CALC.SCH** from the list of files.

- 4. Select Make design database as the target.

#### **Performing Timing Simulation**

To perform timing simulation, follow the instructions in the "VST Tutorial" chapter of the *OrCAD Interface User Guide*, with the exceptions in the following steps.

- 1. Place stimulus and trace information on the XCLK signal in the OSC\_3K schematic instead of on the CLK signal, and on the LED\_P signals in the LED schematic instead of on the STACK signals (pp. 12-6 to 12-8).

- In addition, you will have to move the stimulus information in the SW7 schematic from the SW signals to the SW\_P signals and subtract one clock cycle. Follow these steps:

- a) Place the mouse cursor on the stimulus symbol on the SW4 signal and select the Inquire command. The following line is displayed in the top left corner of the screen:

Stimulus: 0:0 6000:1

- b) Subtract 500 time units, which is equal to one clock cycle, from the times at which the signal changes value. Replace all time values less than or equal to 500 with 0. In this case, 0 remains 0 and 6000 becomes 5500.

- c) Use the Place → Stimulus command to add the following stimulus to the SW4\_P signal:

0:0 5500:1

- d) Delete the stimulus indicator on the SW4 signal.

- e) Repeat steps a through d to delete all stimulus information from each SW signal and add it to each SW\_P signal.

- f) Use  $Quit \rightarrow Update$  File to save your edits.

The EPLD fitter software optimizes away many internal nodes such as the CLK, STACK, and SW7 signals, but cannot optimize external signals such as the XCLK, LED\_P, and SW\_P signals.

- Substitute "EPLD" wherever the VST Tutorial says "FPGA". For example, select Orcad\_Epld\_Timing as the XSIMMAKE flow name instead of Orcad\_Fpga\_Timing.

- 4. Instead of adding a GR or GSR stimulus (p. 12-21), add a PRLD stimulus. Like GSR, the PRLD stimulus has an initial value of 1 and is brought down to 0 at 1 nanosecond.

## **Converting a Xilinx-ABEL Module (Optional)**

You can use a Xilinx-ABEL module instead of the STATMACH schematic in the CALC design. The stat\_abl.abl file specifies the logic. Substituting this Xilinx-ABEL module is described in the Interface User Guide for your CAE tool. This section describes how to make this module EPLD-compatible after you have substituted it.

- Select the ABL2PLD command in the XDM menu. Select the stat\_abl.abl file from the list. The ABL2PLD command creates a file named stat\_abl.pld.

- 2. Start up your CAE tool.

- 3. Open the schematic named CONTROL. Delete the DEF=XABEL attribute from the STATMACH symbol, which referenced the Xilinx-ABEL module, and change FILE=stat\_abl to PLD=stat\_abl. For specific instructions on changing attributes, see the "Attributes" appendix.

**Note:** If you wish, you can convert the stat\_abl.abl file from symbolic (one-hot) encoding to maximal encoding. It is not really necessary, however, because this state machine has only three states, and therefore the conversion spares only one register.

# **Chapter 3**

# **EPLD Architecture and Design Tradeoffs**

This chapter discusses EPLD architecture and tradeoffs in fitting your design to the EPLD architecture: designing for speed, density, or pinout preservation; controlling power consumption; and controlling preload values.

The tips and techniques in this chapter are guidelines only. They are general principles that work in most cases. They may or may not be applicable to a particular design.

# **EPLD** Architecture

EPLD devices have special architectural features that can make your design faster and more efficient. The XEPLD fitter software automatically analyzes your design, optimizes the logic, and maps functions into the appropriate device resources. However, an understanding of the EPLD architecture can help you exercise complete control of design optimization.

For more detailed information about EPLD architecture, refer to the EPLD device data sheets.

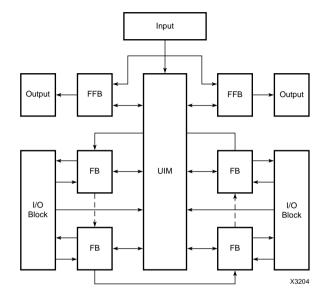

Figure 3-1 is a simplified diagram of the XC7354 device that shows the main architectural features of EPLD devices.

#### Figure 3-1 EPLD Device Structure

The five basic architectural features in an EPLD device are as follows:

- Input Pads

- Output Pads

- High Density Function Blocks (HDFBs)

- Fast Function Blocks (FFBs)

- The Universal Interconnection Matrix (UIM)

This section describes these features and how designs are mapped onto them for best results.

**Note:** For a complete explanation of the XC7000 architectural features, see the EPLD device data sheets.

## **Input Pad Structures**

The XC7000 devices have two types of input pads: Fast Inputs and standard inputs.

Fast Input pins have two paths through the device. One path drives directly into the Fast Function Blocks, bypassing the UIM, and is used for signals that require the fastest propagation delays and shortest macrocell register setup times. The second path drives all function blocks (both FFBs and HDFBs) through the UIM.

Standard inputs and UIM paths of Fast Inputs can be configured as follows:

- Registered

- Registered with clock enable

- Latched

- Combinatorial

Registering and/or latching signals at the input pad shortens register setup times and is used most often to pipeline data on-chip or synchronize asynchronous inputs. The input pad registers can also store data, making more macrocells available for implementing logic.

#### **Output Pad Structures**

The XC7000 devices have two types of output pads: those driven by HDFBs, which have standard drive capability; and those driven by FFBs, which have higher drive capability. These outputs can be configured as follows:

- 3-state with individual p-term control (HDFB only)

- 3-state with FOE and individual p-term control (HDFB only)

- 3-state with FOE control

- Direct (always on)

Each output pad driven by a HDFB can be 3-stated by its own macrocell product term for maximum flexibility. The global FOE net offers maximum speed.

Bidirectional pins have both input pad structures and output pad structures. See your device data sheet for details.

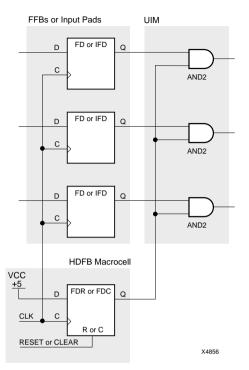

#### **High-Density Function Blocks**

High Density Function Blocks provide the maximum amount of logic resources for use in your design. They are well-suited for arithmetic functions, counters, and other kinds of complex logic.

High Density Function Blocks contain special fast carry lines for arithmetic logic. These lines extend between High-Density Function Blocks, allowing fast carry for very large arithmetic functions.

#### **Fast Function Blocks**

The XC7300-series devices have a combination of High Density Function Blocks and Fast Function Blocks; this is called "Dual Block Architecture."

Logic placed in Fast Function Blocks performs faster than logic in High Density Function Blocks. Fast Function Blocks are well-suited for critical decoding and ultra-fast state machine applications.

## The Universal Interconnect Matrix (UIM)

The Universal Interconnect Matrix, or UIM<sup>TM</sup>, provides a 100% interconnection matrix allowing any function block output to drive any function block input in the device; routing is never blocked. All function block inputs (except for the FastInputs) come from the UIM.

The UIM can perform wired-AND functions, which the software uses automatically when possible to improve resource utilization.

# **Designing for Speed**

To optimize for speed (faster pin-to-pin and register setup times), follow these guidelines:

- Use Fast Function Blocks for the functions in which speed is most critical.

- Use input pad registers.

- Use EPLD-specific arithmetic functions when cascading.

- Use EPLD-specific bidirectional counters when cascading.

- Reduce levels of logic.

## **Assigning Logic to Fast Function Blocks**

Fast Function Blocks (FFBs), which are available in XC7300 devices, have Fast Inputs and Fast Outputs, which bypass the UIM and thus do not incur a UIM delay. Their logic is simpler than that of High-Density Function Blocks (HDFBs), which also means less delay. Use FFBs for critical signals and functions in which speed is important.

To place logic in an FFB, use the F attribute on the outputs. Use the F attribute on inputs (the outputs of IBUF components) to make them Fast Inputs. For more about the F attribute, see the "Attributes" appendix.

Turning off preload optimization affects whether logic can be moved into Fast Function Blocks. For more information, see the "Controlling Preload Values" section in this chapter.

#### Logic Requirements for Fast Function Blocks

The XEPLD software automatically maps into the Fast Function Blocks any function that meets these requirements, even if you do not use the F attribute:

- All clocks use the global FastCLK<sup>TM</sup> signals, which means that the global clocks must be available.

- All 3-state controls use the global FOE signals.

- All registers may only be asynchronously set except in 7336 and 7318 devices (unless you use reset emulation, described in the "Design Applications" chapter).

- All registers may only be preloaded to a logic High state or have unspecified preload values except in 7336 and 7318 devices (unless you use reset emulation, described in the "Design Applications" chapter).

- All logic must use four or less p-terms when implemented as active-Low except in 7336 and 7318 devices. You can override this requirement by using the F attribute the software exports product terms if the output uses more than four product terms.

- All components used must be allowable in a Fast Function Block.

Use the F attribute in these cases:

• If you want a function to have priority for being placed in an FFB.

• If you have a function with more than four product terms that you would like to place in a Fast Function Block.

If your logic output signals must use an internal p-term clock, the software drives the p-term clock off-chip through a FastCLK pin and back into the global FastCLK net through the I/O buffer on the FastCLK pin.

If your registers require asynchronous reset inputs or if the preload state must be a logic Low, your design will need modification in order to fit into an FFB. See the "Reset and Preload Control in FFB and Input Pad Registers" section in the "Design Applications" chapter.

To place component outputs that do not drive anything in FFBs, add dangling nets to the outputs and apply the F attribute to the dangling nets as shown in Figure 3-2.

#### Figure 3-2 Assigning Dangling Outputs to Fast Function Blocks

**Note:** When placing functions into Fast Function Blocks, it is best to choose functions that require the least number of product terms.

#### **Components Not Allowed in Fast Function Blocks**

The following components are not allowed in a Fast Function Block because they require special features, such as arithmetic carry lines, that are not present in Fast Function Blocks.

- PLFB9

- ADD symbols

- ADSU symbols

- ACC symbols

- BUFCE

- IFD

- IFDX1

- ILD

- COMPM

- LD

- FDCP, FDCPE (If you use a flip-flop with both CLR and PRE, you must tie either CLR or PRE to GND)

- OBUFT

- OFDT

- XOR7, XOR8, XOR9 (cascade the smaller XORs instead)

**Note:** The BUFT and BUFE symbols are allowed for external outputs only (not nodes) and must allow FOE optimization.

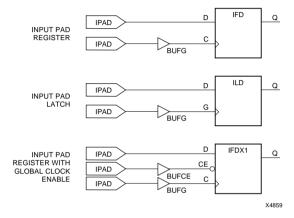

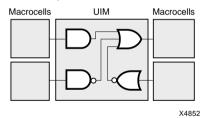

## **Using Input Pad Registers**

Input pad registers and latches offer these advantages:

- Faster setup-to-clock time than macrocell registers

- Additional storage for register-intensive designs

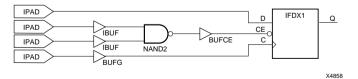

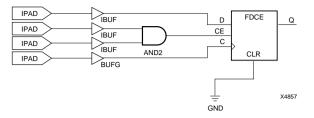

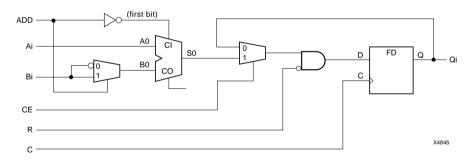

Figure 3-3 shows the components you use to specify a regular macrocell register, an input pad register, an input pad latch, and an input pad register with global clock enable.

**Note:** The XEPLD software automatically maps FDs and FD variations to input pad registers when possible. You need only use IFDs and variations for more direct control of the mapping, for latching (use ILD or a variation), or for global clock enable (use IFDX1).

Maps to a Macrocell or Input Pad Register

Maps Only to an Input Pad Register or Latch

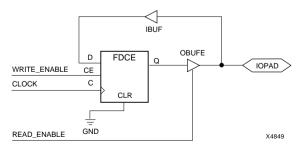

#### Placing Clock Enable Signals in Input Pad Registers

If you want to use the global clock enable net and an input pad register, but your clock enable signal must be controlled by internal logic, use the BUFCE and IFDX1 components as shown in Figure 3-4. The FDCE shown in Figure 3-5 is valid, but it does not use the global clock enable net or an input register.

Figure 3-4 Can Be Placed in an Input Pad Register

Figure 3-5 Cannot Be Placed in an Input Pad Register

## **Using EPLD-Specific Arithmetic Functions**

XC7000-specific arithmetic components use the fast carry chain for their CI and CO pins. Equivalent common components do not use the fast carry chain for their CI and CO pins and therefore slower and use more device resources when cascaded. If you are not cascading, however, the common arithmetic components work well.

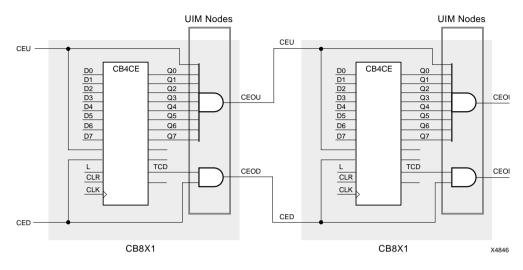

## **Cascading Counters**

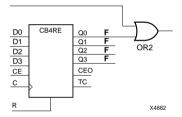

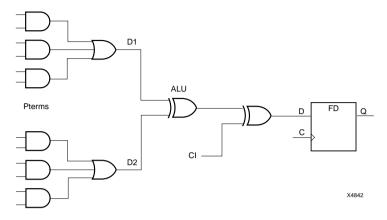

If you are cascading bidirectional or down counters, you should use XC7000-specific counters. These counters have separate up and down terminal counts (CEOU and CEOD) that can be cascaded in the UIM. The up terminal count is generated by ANDing all of the counter bits in the UIM. The down terminal count lookahead is generated in a macrocell. These terminal counts are then ANDed with the count enable inputs (CEU and CED) to produce the component's up and down terminal count outputs as shown in Figure 3-6.

Figure 3-6 Cascading EPLD-Specific Up/Down Counters

Because the XEPLD optimization software collapses the cascaded UIM nodes into a single level of logic, the speed of the cascaded counter is constant, no matter how many bits it has. However, in common library bidirectional counters, the up and down terminal counts are combined into a single terminal count. This terminal count uses both the true and the complement of the counter bits, which makes the terminal count impossible to place in the UIM.

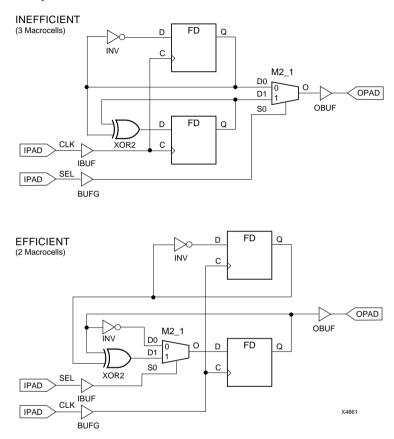

## **Reducing Levels of Logic**

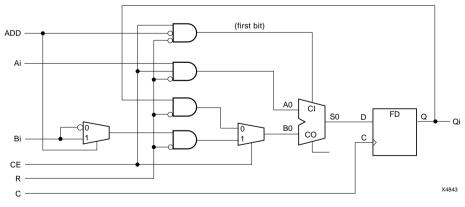

Each EPLD macrocell has several levels of logic followed by a register. If you put the logic first, the XEPLD fitter software maps the logic and register into the same macrocell. If you put logic after the registers, however, the XEPLD fitter software may use additional macrocells for the logic that follows the registers, decreasing both the speed and density of your design. Figure 3-7 shows two equivalent circuits, one that is efficient and one that is inefficient.

**Note:** There are exceptions to this guideline. For an example, see the following "Splitting Wide Functions" section.

Another way to minimize levels of logic is to make sure you do not exceed 21 inputs or 17 product terms for a function. This makes it likely that the function will fit in one HDFB macrocell.

Figure 3-7 Reducing Levels of Logic

#### **Splitting Wide Functions**

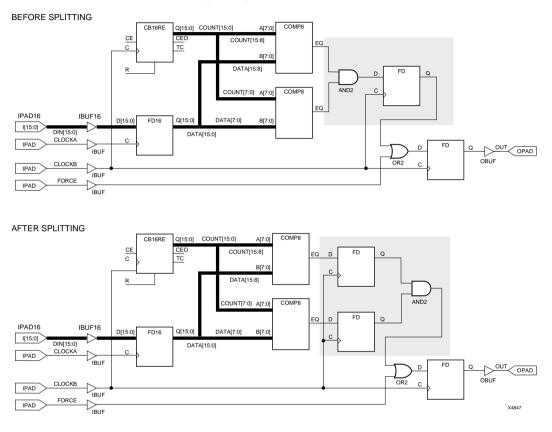

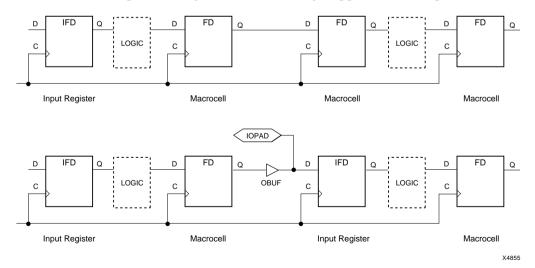

The XEPLD software can handle a function with up to 17 product terms and 21 inputs as a single level of logic in a High-Density Function Block. If the function exceeds these limits, it is implemented as two levels of logic and an extra delay occurs. This typically happens with wide compare functions, since two product terms are required for each pair of bits being compared. You can keep your wide function implemented as a single level of logic if you manually split the function.

Figure 3-8 shows a design with a wide compare function that is twice as fast after splitting.

Figure 3-8 Splitting a Wide Function

#### **Random Logic**

If your design contains custom gate-level logic, follow these guidelines to ensure that the logic will optimize well:

• Try not to exceed 21 inputs or 17 product terms for a single output or registered function. Logic must meet these requirements to fit within a single High-Density Function Block macrocell.

- For a Fast Function Block macrocell, the limit is 24 inputs. If a function exceeds 4 product terms, the product terms are exported from adjacent macrocells, but this means that a wide function uses up many macrocells.

- In general, use library components instead of gate-level logic wherever possible.

- If random logic is represented in many layers of combinatorial logic before it reaches pads or registers, it may be better to use a behavioral module.

The EPLD software will attempt to reduce the number of inputs to 21 or less so that the logic can be implemented in a single pass through the UIM. However, this may be more difficult if the design is implemented with large numbers of random gates.

# **Designing for Density**

The XEPLD software optimizes for density by default, but there are some additional things you can do to improve density optimization:

- Maximally encode all state machines.

- Specify active-High output enables and rising edge clocks so these signals can be mapped to global nets.

- Specify UIM nodes for wide input AND functions.

- Use input pad registers whenever possible to make more macrocells available for logic.

- Use the UIM paths of Fast Inputs.

- Turn off logic optimization on selected combinatorial nodes.

- Use the Master Reset pin if your design requires device reinitialization, or use this pin as a regular input if your design requires an additional I/O pin.

## **Maximally Encoding State Machines**

If your design contains behavioral modules written as state machines, be sure that the functions are maximally encoded. This works best for EPLDs, which are rich in product terms. (For FPGAs, it is best to use one-hot encoding, because FPGAs are rich in registers.)

## **Using Global Nets**

Clock and output enable signals mapped to global nets do not consume function block resources. Optimization software automatically maps the most used rising edge clock inputs to the FastCLK nets and the active-High output enable inputs to the FOE nets.

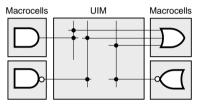

## Moving Logic into the Universal Interconnect Matrix

In addition to offering 100% routability, the UIM can function as a very wide AND gate. The UIM can also implement DeMorgan equivalent functions. The following figure illustrates this process:

Before UIM Optimization

After UIM Optimization

#### Figure 3-9 Moving Functions into the UIM

Sometimes specifying a UIM node for a wide ANDing function can result in improved optimization. Moving a node into the UIM can free up additional function block inputs for use by other logic functions. This should only be tried after reviewing the results of the automatic optimization. See the description of the OPT=UIM attribute in the "Attributes" appendix for more information.

## **Using Input Pad Registers**

Registering or latching signals at the input pad shortens register setup times and is often used to pipeline data on-chip or synchronize asynchronous inputs. The input pad registers can also store data, making more macrocells available for implementing logic. You can even emulate asynchronous set/reset control using a design technique outlined in the "Reset and Preload Control in Input Pad and FFB Registers" section in the "Design Applications" chapter.

#### Macrocell Register vs. I/O Pin Tradeoff

If your design is register-intensive but requires few I/O pins, you may be able to trade a few macrocell registers for I/O pins. A register having only a buffer or inverter in front of its D input can be converted to an input register. Use the method shown in Figure 3-10.

For clarity, IPAD, IBUF, and BUFG symbols are omitted from the inputs on the left, and OBUF and OPAD from the output on the right.

**Note:** Because IFDs preload to 1, you may see 1s propagate through your design at the beginning of simulation. To prevent this, you can use the technique described in "Reset and Preload Control in FFB and Input Pad Registers" in the "Design Applications" chapter.

Figure 3-10 Using a Macrocell vs. Using an I/O Pin

#### **UIM Versus Fast Input Paths**

A second path into the Fast Function Block in available through the UIM. If the Fast Function Block becomes input limited, moving a signal from the direct Fast Input path to the UIM path may allow the optimization software to free up an extra FB input.

To move a signal from the direct Fast Input path to the UIM path, remove the F attribute from the input signal. Do not remove the F attribute from the output signal, however, because this is what places the logic in a Fast Function Block.

## **Controlling Logic Optimization**

The XEPLD software attempts to reduce the number of logic levels for all signal paths. This means that the remaining logic functions have a wider signal fan-in and possibly require more product terms than if some combinatorial nodes were retained.

By turning off logic optimization on selected nodes, you may free up additional function block inputs and/or macrocell product terms, at the expense of the macrocells used to implement the nodes. Try this only after reviewing the results of the automatic optimization. See the "Attributes" appendix for details about LOGIC\_OPT and OPT.

#### Master Reset Pin Tradeoffs

This discussion describes tradeoffs of using the XC7000 MR pin as a global reset and 3-state control. Consult your device data sheet for specific requirements of the MR pin during power-up. See the "Controlling Preload Values" section at the end of this chapter for the default preload values of device registers.

The XC7000 devices feature a master reset pin that can be used to reinitialize the device. When the device is reinitialized, all device pins are 3-stated and registers are preloaded. When initialization is complete, the register preload is released and the outputs become operational.

The master reset pin can completely 3-state the device during board testing. It can also force state machines and registers to a known state if the reinitialization delay is not critical in your design (see the device datasheet for details). The advantage is that no product terms or Function Block inputs are required to preload the registers or

3-state the device pins. If the reinitialization delay is critical, use a logic input to force state machines and registers to a known state.

On the 7354, 7336, and 7318 devices, the master reset pin can also be programmed as a logic pin by assigning the MRINPUT=ON global attribute to a TBLOCK symbol. If this attribute is specified, the device is initialized only on power-up.

# **Designing to Preserve the Pinout**

In the XC7000 devices, logic capacity and device pinout are determined only by the resources available in the Function Blocks; the logic mapped into the Function Blocks is always guaranteed to route in the UIM. The factors that determine the logic capacity of the Function Block are as follows:

- Number of Function Block inputs

- Number of product terms available to each macrocell in the Function Block

- Number of macrocells in the Function Block

- Number of device pins driven by the Function Block

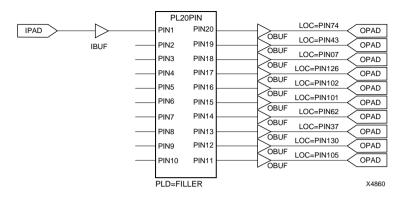

You can reserve High Density Function Block resources by adding a "filler" circuit to your design as shown in Figure 3-11. This circuit consumes two UIM inputs, one shared product term, and one macrocell for each output used in the design. It can be used to reserve resources in up to 10 Function Blocks. Each output is assigned to a specific Function Block by assigning it to a specific device pin with the LOC attribute. The equation file, filler.pld, is in the xact\examples\behavior\epld directory.

#### Figure 3-11 Filler Circuit

**Note:** If more than one output is assigned to the same Function Block, the first output consumes two UIM inputs. Each additional output consumes one additional UIM input.

You should evaluate the product term requirements of your logic assigned to pins that are driven by Fast Function Blocks. Check the design.eqn file to determine how many product terms (including the implied exported product terms) are required. Plan ahead for design iterations which may create functions that require the exported product terms from an adjacent macrocell.

To preserve the pinout from an earlier iteration of the design, use the **Translate**  $\rightarrow$  **PinSave** command to generate the .VMF pin freeze file. Then use the **Profile**  $\rightarrow$  **Options**  $\rightarrow$  **FitNet**  $\rightarrow$  **-f** command to turn pin freezing on for the design. Save the profile with the **Profile**  $\rightarrow$  **Save Profile** command. Now, each time you recompile the design, the old pinout will be reused.

#### **Manual Pin Assignment**

**Note:** Manual pin assignment can restrict the layout capability of the software. It is usually best to allow XEPLD to automatically assign pins based on the most efficient placement of logic in the device.

XEPLD automatically assigns device pins for you, based on the most efficient usage of device resources. This is usually the best method for pin assignment if you do not have specific pinout requirements. Automatic pin assignment is performed only for those pins that have not been assigned through some other method. After a successful design compilation, you can use the PinSave command to maintain the pin assignments during design iteration.

If you have specific pinout requirements you can use the LOC=*pin\_number* attribute to assign the signal to a specific pin.

**Note:** LOC attributes override the pin assignments in the pin-save file. This allows you to make changes to your fixed pin specifications. However, if you override the pin-save file with LOC attributes, the software will issue a warning.

#### Manual Pin Assignment Precautions

When you manually assign output and I/O pins, you force the software to place logic functions into specific function blocks. If the logic does not exceed the function block resources (macrocells, product terms, and UIM inputs) and the function block has the correct external pin resources to meet the logic I/O requirements, the logic is mapped into the function block and the design will route in the UIM.

Try to place product term intensive logic onto pins that are driven by High Density Function Blocks. Be sure that the Function Block's shared product term resources and UIM inputs will not be exhausted. You may also wish to leave additional room in the Function Block for design iterations.

Assign your external rising-edge clocks and active-High output enable signals to the FastCLK and FOE pins on the device. To create global on-chip clocks, assign them to the FastCLK nets. To create global output enable control signals, assign them to the FOE nets. These signals will use the I/O buffer on the pin to route the macrocell output onto the global net.

Evaluate the requirements of your logic assigned to pins that are driven by the Fast Function Blocks. Functions mapped to an FFB can be clocked only by global clocks, 3-stated only by FOEs, and, for the 7354, 7372, and 73108 devices, only asynchronously set. Plan ahead for design iterations which may create functions that require the exported product terms from an adjacent macrocell.

#### The LOC Attribute

Use the LOC=*pin\_name* attribute on a PAD symbol to assign the signal to a specific pin. The pin name is *Pnn* for PC packages; the *nn* is a pin number. The pin name is *rc* (rowcolumn) for PG packages. Examples are LOC=P24 and LOC=G2.

You can apply the LOC attribute to as many PADs in your design as you like. However, each pin assignment further constrains the software as it automatically allocates logic and I/O resources to internal nodes and I/O pins with no LOC attributes.

**Note:** Pin assignment using the LOC attribute is not supported for bus components such as OBUF8.

# **Controlling Power Consumption**

You control power consumption for specific macrocell outputs using the LOWPWR attribute. This attribute is valid only for XC7300 designs. This attribute is either a global or component attribute.

The default is LOWPWR=OFF (high speed) for all macrocells used in the design unless otherwise specified.

To make low power the global default power setting, place the global attribute LOWPWR=ALL in the schematic. (See the Global Attributes section of the "Attributes" appendix for instructions.)

To control the power setting of the macrocells used by an individual symbol, use LOWPWR=ON or LOWPWR=OFF (if the global LOWPWR=ALL was used). This attribute is ignored if assigned to a symbol that uses no macrocells, such as an inverter.

**Note:** Low-power outputs are slower than regular-power outputs. If you have a mixture of low- and regular-power outputs, pay close attention to simulation results or the timing report to see how the power settings affect timing interactions.

# **Controlling Preload Values**

The preload values used in the implementation of your design depend on these factors:

• The register resources of the target device

- The preload values of the library components used in the design. Every registered component in the Xilinx library has a default preload value defined; for most components, it is 0. You can look up preload values for any component in the *XACT Libraries Guide*.

- The .PRLD equations in the behavioral modules

- Whether preload optimization is on. By default, the XEPLD fitter performs preload optimization, ignoring the library defaults and .PRLD equations, to produce the most efficient mapping of components to available device resources. You can control preload optimization using the PRELOAD\_OPT and INIT attributes.

#### Physical Resources of EPLDs

Registers in EPLD devices can physically support the following initial preload states: