# XEPLD VIEWSYNTHESIS DESIGN GUIDE

TABLE OF CONTENTS

INDEX

**GO TO OTHER BOOKS**

0401419

Copyright 1994-1995 Xilinx Inc. All Rights Reserved.

# Contents

| Chapter 1 | System Configuration                                                                                                                                                                                                                            |                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

|           | Software Capabilities<br>Unsupported Features<br>System Requirements<br>Configuring the Viewlogic Library Search Order<br>The viewdraw.ini File<br>Verifying Your File Structure                                                                | 1-1<br>1-2<br>1-2<br>1-2                         |

| Chapter 2 | Getting Started With Xilinx EPLDs                                                                                                                                                                                                               |                                                  |

|           | Xilinx EPLD Design Flow<br>Design Example<br>Design Entry<br>Copying the Tutorial Files<br>Project Creation<br>Design Synthesis and Schematic Generation<br>Functional Simulation<br>Design Fitting and Device Programming<br>Timing Simulation | 2-2<br>2-3<br>2-6<br>2-6<br>2-12<br>2-13<br>2-19 |

| Chapter 3 | Designing With EPLDs                                                                                                                                                                                                                            |                                                  |

|           | VHDL Design File General Requirements                                                                                                                                                                                                           | 3-1<br>3-2<br>3-2<br>3-2<br>3-3<br>3-4<br>3-4    |

|           |                                                                                                                                                                                                                                                 | 00                                               |

| Using Registers And Latches                          | 3-5  |

|------------------------------------------------------|------|

| Using Input Pad Registers                            |      |

| Using Macrocell Registers                            | 3-6  |

| Using Input Pad Latches                              |      |

| Using Macrocell Latches                              |      |

| Using Special Logic Functions                        | 3-7  |

| Binary Counters                                      | 3-7  |

| State Machines                                       |      |

| Arithmetic Functions                                 | 3-8  |

| Comparators                                          | 3-8  |

| Targeting a Specific Device                          | 3-9  |

| Controlling Design Performance                       | 3-10 |

| Using High-Speed Clocks                              | 3-10 |

| Assigning Specific High-Speed Clocks                 | 3-11 |

| Selecting EPLD Function Block Types                  | 3-11 |

| Specifying High Speed Paths                          | 3-11 |

| Specifying High Density Paths                        | 3-11 |

| Using EPLD FastInputs                                | 3-11 |

| The Design Rule Checker                              | 3-12 |

| General Design Rule Violations                       | 3-12 |

| Pad Component Design Rule Violations                 | 3-12 |

| FastCLK, Clock Enable, Fast Output Enable Violations | 3-13 |

|                                                      |      |

## Chapter 4 Using PROflow

| Fitter Overview                          | 4-1 |

|------------------------------------------|-----|

| Creating a Project Directory             | 4-2 |

| Compiler Operation                       | 4-3 |

| Fitter Operation                         | 4-4 |

| Fitting Your Design                      | 4-4 |

| Fitter Reports                           | 4-6 |

| Design Timing Verification               | 4-7 |

| Creating The Xilinx Static Timing Report | 4-7 |

| Performing Timing Simulation             | 4-7 |

#### Appendix A Using the Command Line

| Using a Batch File        | A-1 |

|---------------------------|-----|

| Using Individual Commands | A-1 |

## Appendix B EPLD Architecture

| Device Selection                  | B-2 |

|-----------------------------------|-----|

| The Universal Interconnect Matrix | B-3 |

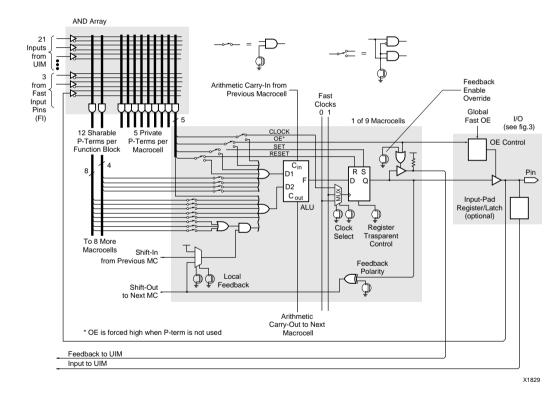

| High-Density Function Blocks           | B-4  |

|----------------------------------------|------|

| Shared and Private Product Terms       | B-5  |

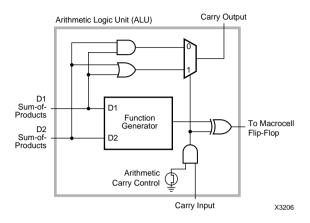

| Arithmetic Logic Unit                  | B-5  |

| Carry Lookahead (7300 Family Only)     | B-6  |

| Macrocell Flip-Flop                    | B-6  |

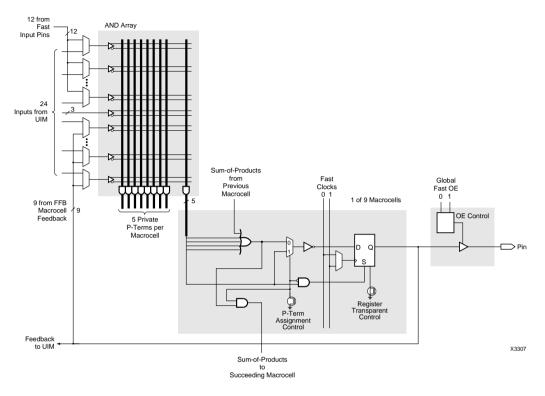

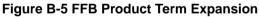

| Fast Function Blocks                   | B-7  |

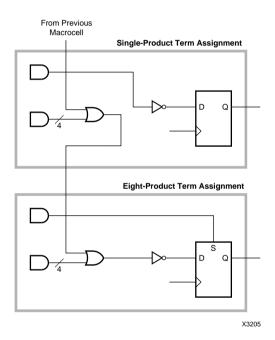

| Product Term Expansion                 | B-9  |

| XC7336 and XC7318 Fast Function Blocks | B-9  |

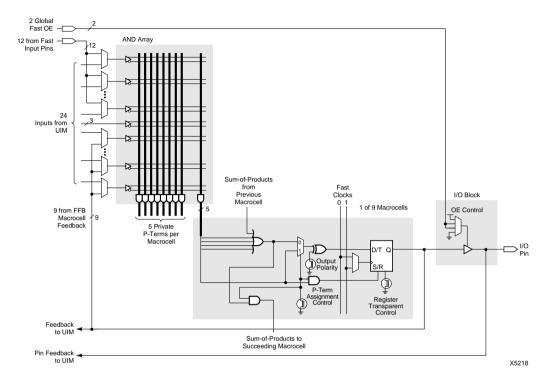

| Input/Output Blocks                    | B-10 |

|                                        |      |

## Appendix C Library Component Specifications

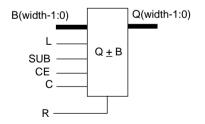

| ACC                         | C-3  |

|-----------------------------|------|

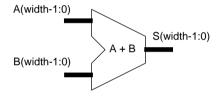

| ADD                         | C-4  |

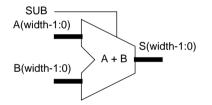

| ADSU                        | C-5  |

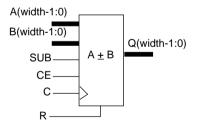

| ADSUR                       | C-6  |

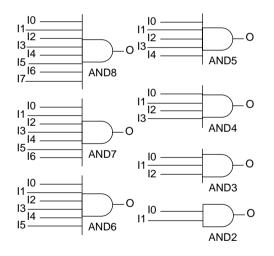

| AND2 — AND8                 | C-7  |

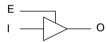

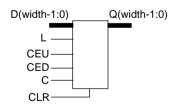

| BUF                         | C-8  |

| BUFCE                       | C-9  |

| BUFE                        | C-10 |

| BUFFOE                      | C-11 |

| BUFG                        | C-12 |

| CBX1                        | C-13 |

| CBX2                        | C-14 |

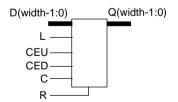

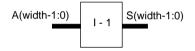

| DEC                         | C-15 |

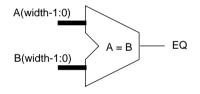

| EQ                          | C-16 |

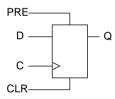

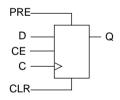

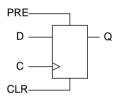

| FDCP                        | C-17 |

| FDCPE                       | C-18 |

| FDPC                        | C-19 |

| IBUF                        | C-20 |

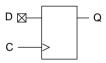

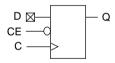

| IFD                         | C-21 |

| IFDX1                       | C-22 |

| ILD                         | C-23 |

| INC                         | C-24 |

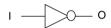

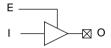

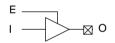

| INV                         | C-25 |

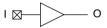

| LD                          | C-26 |

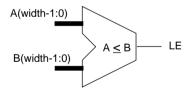

| LE_TC, LE_US                | C-27 |

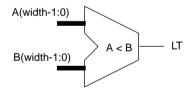

| LT_TC, LT_US                | C-28 |

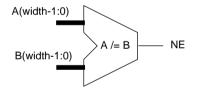

| NE                          | C-29 |

| OBUF, OBUF_F, OBUF_S        | C-30 |

| OBUFE, OBUFE_F, OBUFE_S     |      |

| OBUFEX1, OBUFEX1F, OBUFEX1S | C-32 |

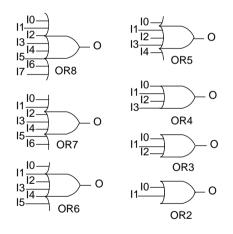

| OR2 — OR8   | C-33 |

|-------------|------|

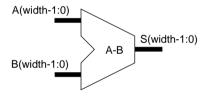

| SUBT        | C-34 |

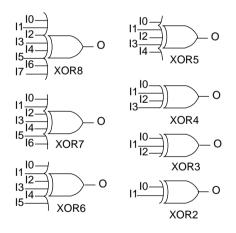

| XOR2 — XOR8 | C-35 |

#### **Appendix D Attributes**

| Global Attributes | D-1 |

|-------------------|-----|

| LOWPWR            | D-1 |

| MRINPUT           | D-1 |

| NO_FOE            | D-2 |

| NO_FCLK           | D-2 |

| NO_IFD            | D-2 |

| PRELOAD           | D-3 |

| Signal Attributes | D-3 |

| F                 | D-3 |

| Н                 | D-3 |

| OPT_OFF           | D-4 |

| OPT_UIM           | D-4 |

|                   |     |

#### **Appendix E Fitter Reports**

| Resource Report                 | E-2  |

|---------------------------------|------|

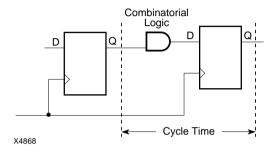

| The Static Timing Report        | E-3  |

| Creating the Timing Report      | E-3  |

| Combinational Pad-to-Pad Delays | E-4  |

| Setup-to-Clock Time             | E-5  |

| Clock-to-Output Delays          | E-6  |

| Cycle Time                      | E-7  |

| Example Timing Report           | E-8  |

| Pin-List Report                 | E-11 |

|                                 |      |

|                                 |      |

## Index..... i

#### **Trademark Information**

# **Chapter 1**

## **System Configuration**

This chapter describes the capabilities of the Xilinx<sup>®</sup> EPLD Viewlogic Synthesis Library and Interface and shows you how to configure your system. For installation instructions, refer to the Release Notes.

## **Software Capabilities**

The Xilinx EPLD Viewlogic Synthesis Interface has the following features:

- Supports all XC7200 and XC7300 devices.

- Functional simulation of synthesized gate-level designs (including all XC7000-specific library components).

- Full-timing simulation (after fitting).

- Static Timing Report created by the XEPLD<sup>™</sup> Fitter (after fitting).

- Attributes for allocating logic to EPLD Fast Function Blocks and Fast Inputs.

- Attributes for controlling XEPLD optimization of clocks, input pad registers, output enable signals, and UIM<sup>™</sup>-AND functions.

#### Unsupported Features

The Xilinx EPLD Viewlogic Synthesis Interface currently has the following limitations:

- No technology-specific optimization (for speed or density) is performed by the Viewlogic synthesizer; all optimization is performed by the Xilinx EPLD Translator Core Tool (XEPLD).

- No timing or area information is contained in the XC7000 library. Therefore, no timing or area estimation is available from

Viewlogic Synthesis. Timing and resource utilization results are available from XEPLD after completion of fitting.

• The XEPLD fitter (v5.1) currently does not support timingconstraint-driven optimization; Viewlogic Synthesis timing constraints have no effect on EPLD design processing. Instead, use the "F" attribute to designate EPLD Fast Function Block and Fast Input resources.

## System Requirements

You will need the following software installed on your system to develop EPLD designs:

- Viewlogic PRO series or Powerview with Viewlogic Synthesis v2.3.1 or later.

- Xilinx Viewlogic Interface and libraries version 5.1 PRO (all of the Xilinx Viewlogic system products contain this interface).

- Xilinx EPLD Implementation software (DS550) version 5.1 or later (all of the Xilinx Viewlogic system products contain this interface).

## **Configuring the Viewlogic Library Search Order**

After you have installed the Xilinx software, you must configure the viewdraw.ini file (originally in your Viewlogic STANDARD directory) for accessing the XC7000 library. Each design directory where XC7000 designs are processed must contain a properly configured viewdraw.ini file.

#### The viewdraw.ini File

Copy the viewdraw.ini file from the Viewlogic standard directory into your project directory, or use the Viewlogic project management utility to create a project directory containing a copy of viewdraw.ini. Edit your local viewdraw.ini file so that it contains the following library directory pointers in the following order:

- DIR [p] . (primary) DIR [m] Xilinx\_library\_path\unified\xc7000 (xc7000) DIR [m] Xilinx\_library\_path\unified\builtin (builtin) DIR [m] Xilinx\_library\_path\unified\builtin (builtin)

- DIR [m] Xilinx\_library\_path\unified\xbuiltin (xbuiltin)

On the workstation, use [r] instead of [m] in the library paths.

## **Verifying Your File Structure**

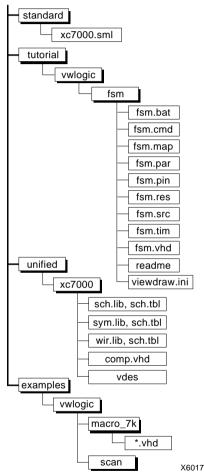

Figure 1-1 shows the relative locations of the essential files included with the Xilinx Viewlogic Synthesis Interface and Libraries:

#### Xilinx Viewlogic Software Directory

Figure 1-1 XEPLD Viewlogic Synthesis Interface (v5.1) Files

# **Chapter 2**

# **Getting Started With Xilinx EPLDs**

This chapter provides an overview of the basic steps for implementing Xilinx EPLD designs using PROsynthesis. The remaining chapters in this manual provide additional detailed information on these steps.

This overview assumes that you have installed and configured the Xilinx software and libraries. See the System Configuration chapter for instructions on how to verify your installation.

The examples in this chapter show the PRO series environment on a PC. You can also process EPLD designs using ViewSynthesis (for example, under Powerview on a workstation) using a similar sequence of steps.

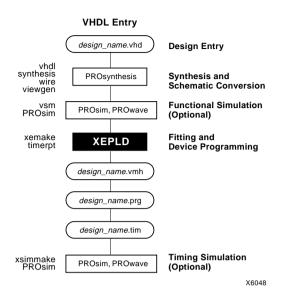

## Xilinx EPLD Design Flow

The basic steps for creating Xilinx EPLDs using Viewlogic Synthesis are described as follows:

- 1. Enter your VHDL design using a text editor.

- 2. Synthesize your design using PROsynthesis and generate a schematic for fitting.

- 3. Perform functional simulation using PROsim (optional).

- 4. Run the Xilinx fitter on the schematic and create a timing report and device programming file.

- 5. Perform timing simulation using PROsim (optional).

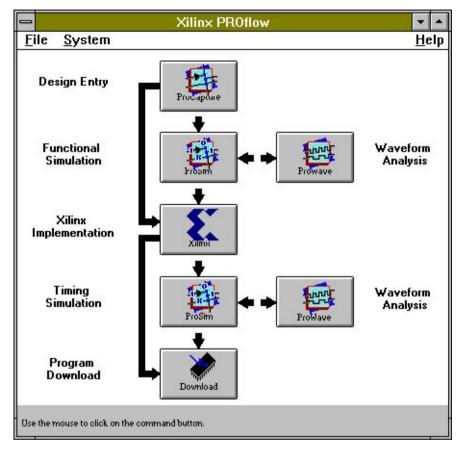

Figure 2-1 shows the basic design flow for creating EPLD designs. Each step is described in the following design example.

Figure 2-1 Basic EPLD Design Flow

## **Design Example**

The following design example, fsm.vhd, is used to demonstrate the basic EPLD design flow. The design is implemented in a Xilinx XC7336-5PC44 device.

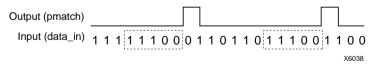

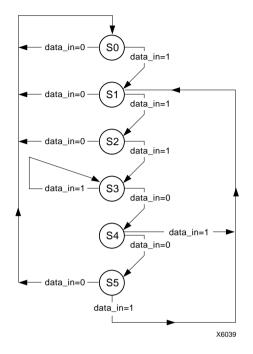

This design is a finite state machine that outputs a 1 only when the bitstream 11100 is present, ignoring all other 5-bit combinations. Figure 2-2 illustrates how this state machine works, and Figure 2-3 is a state diagram for the fsm.vhd design.

#### Figure 2-2 FSM Output vs. Input Relationship

Figure 2-3 FSM State Diagram

## **Design Entry**

The VHDL source file for the example design is shown in below. Note that this file contains IBUF and OBUF instances, which are necessary to identify all device input and output pins in all EPLD designs.

```

library synth; -- Used for simulation

use synth.stdsynth.all;

library xc7000; -- Used for EPLD I/O buffer components

-- use xc7000.components.all;

-- Entity: Input and Output Declarations.

---------

entity fsm is

port (

signal reset, clk, datain : in vlbit;

signal pmatch : out vlbit

);

end fsm;

```

```

_____

-- The architectural body - behavioral description.

architecture first of fsm is

signal reset in, clk in, datain in : vlbit;

signal pmatch out : vlbit;

constant s0 : vlbit 1d(2 downto 0) := "000";

constant s1 : vlbit_ld(2 downto 0) := "001";

constant s2 : vlbit 1d(2 downto 0) := "010";

constant s3 : vlbit_ld(2 downto 0) := "011";

constant s4 : vlbit_ld(2 downto 0) := "100";

constant s5 : vlbit_1d(2 downto 0) := "101";

signal next_state : vlbit_ld(2 downto 0);

signal state : vlbit 1d(2 downto 0);

begin

i1: ibuf port map (reset_in, reset);

i2: ibuf port map (clk_in, clk);

i3: ibuf port map (datain_in, datain);

ol: obuf port map (pmatch, pmatch_out);

cntl: process(datain_in, state)

begin

pmatch_out <= '0';</pre>

next_state <= s0;</pre>

_____

-- Begin CASE statement

CASE state(2) IS

WHEN '1' =>

IF state(1) = '1' THEN

next_state <= s0; -- error condition

ELSE

IF state(0) = '0' THEN

IF datain in = '1' THEN

next_state <= s1; --transition from "100" to "001"</pre>

ELSE

next_state <= s5; --transition from "100" to "101"

END IF;

ELSE

pmatch_out <= '1';</pre>

IF datain_in = '1' THEN

next_state <= s1; --transition from "101" to "001"

ELSE

next_state <= s0; --transition from "101" to "000"</pre>

```

```

END IF;

END IF;

END IF;

WHEN '0' =>

IF state(1) = '1' THEN

IF state(0) = '0' THEN

IF datain_in = '1' THEN

next state <= s3; --transition from "010" to "011"</pre>

ELSE

next state <= s0; --transition from "010" to "000"

END IF;

ELSE

IF datain in = '1' THEN

next state <= s3; --transition from "011" to "011"

ELSE

next state <= s4; --transition from "011" to "100"</pre>

END IF;

END IF;

ELSE

IF state(0) = '0' THEN

IF datain_in = '1' THEN

next_state <= s1; --transition from "000" to "001"</pre>

ELSE

next state <= s0; --transition from "000" to "000"</pre>

END IF;

ELSE

IF datain in = '1' THEN

next_state <= s2; --transition from "001" to "010"</pre>

ELSE

next_state <= s0; --transition from "001" to "000"

END IF;

END IF;

END IF;

WHEN OTHERS => next_state <= s0; -- error condition

END CASE;

end process cntl;

_____

_____

-- Seperate clocked process

-- state<=next_state

```

```

cntl_clk: process

begin

wait until (prising(clk_in) or (reset_in = '1'));

if (reset_in = '1') then

state <= s0;

else

state <= next_state;

end if;

end process cntl_clk;

end first;

```

The example file is already created for you and is located in the directory: tutorial\vwlogic\fsm.

## **Copying the Tutorial Files**

Before you start the tutorial, you should copy the files installed in tutorial\vwlogic\fsm to your own project directory. You can use DOS commands or the Windows File Manager to copy the files. In the examples that follow, the tutorial files are copied into c:\designs\fsm.

This will place the following four files, plus a few report files, into your new project directory:

- fsm.vhd VHDL source design file

- fsm.cmd PROsim simulation command file

- fsm.bat batch file to automatically run the tutorial from DOS

- fsm.src VHDLDES command file invoked by fsm.bat

#### **Project Creation**

To establish the FSM design as a Viewlogic project, follow these steps:

- 1. Start Windows by typing win at the DOS prompt.

- 2. Open the PRO Series window.

- 3. Open the Xilinx flow manager, PROflow, by double clicking on the **Psfm** icon.

The Xilinx PROflow window appears as in Figure 2-5:

Figure 2-4 Xilinx PROflow Window

4. Select the **PROcapture** button in PROflow. The Design Entry dialog box appears as in Figure 2-6:

|                                         | Design         | Entry                 |  |

|-----------------------------------------|----------------|-----------------------|--|

| Project: C:\PROSER\TUTORIAL\VWLOGIC\FSM |                |                       |  |

| Type<br>Schematic                       | O VHDL         |                       |  |

| Design Name:                            |                |                       |  |

|                                         |                |                       |  |

|                                         |                | Project Manager       |  |

|                                         |                | Family: XC7000        |  |

|                                         |                | Select <u>F</u> amily |  |

|                                         |                |                       |  |

| List Files of <u>Type</u> :<br>*.1      |                | X Start PROcapture    |  |

|                                         |                |                       |  |

| <u> </u>                                | <u>C</u> ancel | <u>H</u> elp          |  |

Figure 2-5 Design Entry Dialog Box

5. Click on the **Project Manager** button. The dialog box shown in Figure 2-7 appears:

| PRO Series Project Manage                                 | r                                |

|-----------------------------------------------------------|----------------------------------|

| Current Project: C:\PROSER\TUTORIAL\VWLO(<br>Project List | GIC\FSM                          |

| C:\PROSER\TUTORIAL\WWLOGIC\FSM                            | <u>C</u> reate<br><u>S</u> elect |

| E <u>x</u> it <u>H</u> elp                                | Remo <u>v</u> e                  |

#### Figure 2-6 Project Manager Dialog Box

6. Select the **Create** button. This opens the Create Project dialog box as in Figure 2-8:

| Create Pr                                   | roject                       |

|---------------------------------------------|------------------------------|

| Directory c:\designs\fsm                    | •                            |

| <ul> <li>C:\</li> <li>C→ designs</li> </ul> | +                            |

| n fsm                                       | <u>D</u> K<br><u>C</u> ancel |

| c: [MS-DOS_5]                               | ±                            |

Figure 2-7 Create Project Dialog Box

7. In the Create Project dialog box, select or type in the path of the directory to which you copied the FSM tutorial files, for example:

#### C:\DESIGNS\FSM

- 8. Select OK. The second dialog box closes.

- 9. Select the project you just created if it is not selected already, then click on the **Select** button.

- 10. Select the Exit button to close the Project Manager.

- 11. After you close the project manager, the dialog box shown in Figure 2-9 prompts you to select a device family:

| 😑 Select Family         |                |              |

|-------------------------|----------------|--------------|

| Please select a family: |                |              |

| © XC2000                | © XC3000       | © XC3000A    |

| O XC4000                | • XC7000       |              |

| <u>0</u> K              | <u>C</u> ancel | <u>H</u> elp |

#### Figure 2-8 Select Family Dialog Box

- 12. Select **XC7000**, then select **OK**.

- 13. In the Design Entry dialog box, select **VHDL** as the Type of design.

14. Select the **fsm.vhd** file from the list. The file name appears in the Design Name field. Make sure the **Start Notepad** box is NOT checked. The Design Entry dialog box should now look like Figure 2-10:

| 😑 Design E                                     | ntry                  |

|------------------------------------------------|-----------------------|

| Project: C:\DESIGNS\FSM<br>Type<br>O Schematic |                       |

| Schematic 💿 VHDL                               | Compile <u>V</u> HDL  |

| Design Name:                                   |                       |

| FSM.VHD                                        |                       |

| FSM.VHD                                        | Project Manager       |

|                                                | Family: XC7000        |

|                                                | Select <u>F</u> amily |

| List Files of Type:                            |                       |

| *.VHD                                          | Start Notepad         |

| <u>O</u> K <u>C</u> ancel                      | <u>H</u> elp          |

Figure 2-9 Design Entry Dialog Box After Changes

**Note:** If this were a multi-file design, for each lower-level file you would select the file from the list and then select the Compile VHDL button. You would then select the top-level file and select the OK button, just as in steps 14 and 15 here.

15. Select the **OK** button.

## **Design Synthesis and Schematic Generation**

To create a schematic representation of your design, follow these steps:

1. Select the **Xilinx** button in PROflow. The Xilinx Implementation dialog box appears as in Figure 2-11:

| 🛥 🛛 Xi             | linx Implementation [FSM] | j.               |

|--------------------|---------------------------|------------------|

| Package Selection  | Control Files             |                  |

| Part 👷             | Guide File                | Browse           |

| Package 📃          | Constraints File          | Browse           |

| Speed .            |                           |                  |

| Optional Targets   | <u>Synthesis</u> Options  | <u><u> </u></u>  |

|                    | Implementation Option     | s <u>C</u> ancel |

| Other Options      |                           |                  |

| Run Synthesis Only |                           |                  |

|                    |                           | <u>H</u> elp     |

#### Figure 2-10 Xilinx Implementation Dialog Box

2. Check the **Run Synthesis Only** box. This synthesizes your design without running the fitter, so you can functionally simulate your design.

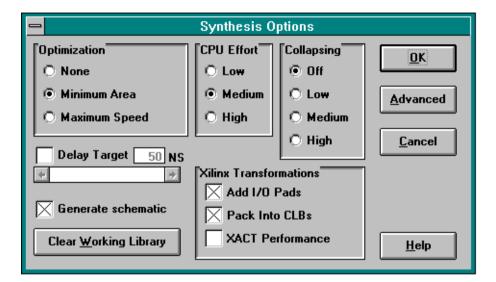

3. Click on the **Synthesis Options** button. The dialog box shown in Figure 2-12 appears:

#### Figure 2-11 Synthesis Options Dialog Box

- 4. Make sure the **Generate Schematic** box is checked. This will cause a schematic representation of the VHDL design to be created.

- 5. Select **OK** to close the Synthesis Options dialog box.

- 6. Select **OK** to close the Xilinx Implementation dialog box and run the synthesis. When synthesis is complete, you see the following message in a prompt box:

Synthesis complete. View report?

7. You can select Yes or No. If you select **Yes**, you must close the report window after you have finished reading the report.

#### **Functional Simulation**

After you have synthesized your design and created a schematic, you can perform functional simulation.

1. Select the **PROcapture** button in PROflow. The Design Entry dialog box appears.

2. Select **Schematic** as the Type of design. You should see the fsm.1 file in the Design Name field. Make sure the Start PROcapture box is NOT checked. The dialog box should look like Figure 2-13 after these changes:

| 😑 Design E                      | ntry                  |

|---------------------------------|-----------------------|

| Project: C:\DESIGNS\FSM<br>Type |                       |

| Schematic O VHDL                |                       |

| Design Name:                    |                       |

| FSM.1                           |                       |

| <b>FSM.1</b>                    | Project Manager       |

|                                 | Family: XC7000        |

|                                 | Select <u>F</u> amily |

| List Files of <u>Type</u> :     |                       |

| <b>™.1</b>                      | Start PROcapture      |

| <u>O</u> K <u>C</u> ancel       | <u>H</u> elp          |

Figure 2-12 Design Entry Dialog Box After Schematic Changes

3. Select the **OK** button.

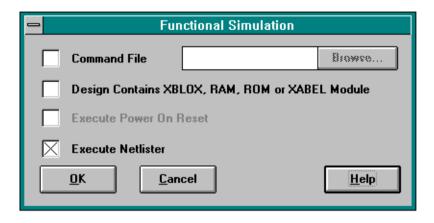

4. Select the **PROsim** button in PROflow. The Functional Simulation dialog box appears as in Figure 2-14:

Figure 2-13 Functional Simulation Dialog Box

5. Select the **Command File** box and the **Browse** button. The Command Files browser appears as in Figure 2-15:

| -              | Command File | :s             |

|----------------|--------------|----------------|

| File Name:     |              |                |

|                |              | <u> </u>       |

| FSM.CMD        |              |                |

|                |              | <u>C</u> ancel |

|                |              |                |

|                |              |                |

|                |              |                |

|                |              |                |

|                |              |                |

| Files of Type: |              |                |

| *.CMD          |              | Help           |

|                |              |                |

Figure 2-14 Command Files Browser

6. Select **fsm.cmd** from the list, then select **OK**. The browser closes.

The fsm.cmd file tells PROsim how to simulate the fsm design.The file's contents are shown here:

```

wave fsm.wfm PRLD CLK RESET DATAIN PMATCH

vector fsm PRLD CLK RESET DATAIN PMATCH

watch PRLD CLK RESET DATAIN PMATCH

break fsm ? do (print > fsm.out)

stepsize 250

clock CLK 0 1

wfm PRLD @0=1 +

@0500=0

wfm RESET @0=0 +

@0500=1 +

@1000=0

```

```

wfm DATAIN @0=1 +

@4000=0 +

@5500=1 +

@6500=0 +

@7000=1 +

@8000=0 +

@10000=0 +

@11000=1

sim 13000

```

- 7. Select **OK** in the Functional Simulation dialog box. After the simulation netlist is processed, the vsm.log file is displayed. Close this file window.

- 8. The PROsim window appears, and the netlist is read. Close the PROsim window when processing is complete (simulation is stopped at 1401 ns).

- 9. Select the **PROwave** button in PROflow. The PROwave Setup dialog box appears as in Figure 2-16:

| -            | ProWave Setup  |              |

|--------------|----------------|--------------|

| Stream Name: |                |              |

| FSM.WFM      |                |              |

| Signal Name: |                |              |

|              |                |              |

| <u>o</u> k   | <u>C</u> ancel | <u>H</u> elp |

#### Figure 2-15 PROwave Setup Dialog Box

- 10. Select OK in the PROwave Setup dialog box.

- 11. The PROwave window appears, along with the **File** → **Open** browser. Select **fsm.wfm** from the list and select **OK**.

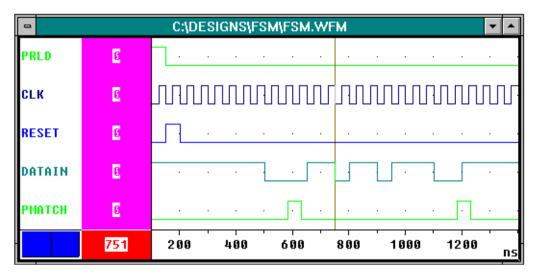

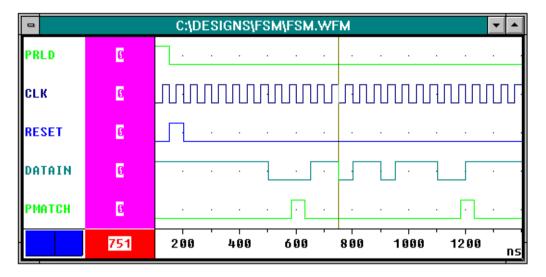

The waveforms appear as in Figure 2-17:

#### Figure 2-16 Simulation Waveforms for the FSM Design

12. When you are finished viewing, close the PROwave window.

#### **Design Fitting and Device Programming**

The XEPLD fitter translates the schematic representation of your FSM design into a physical device layout. To invoke the fitter, follow these steps:

1. Click on the **Xilinx Implementation** button in PROflow. The dialog box shown in Figure 2-18 appears:

| - Xi                                | linx Implementation [FSM] |                |

|-------------------------------------|---------------------------|----------------|

| Package Selection<br>Part 7336 ±    | Control Files             | Browse         |

| Package PC44                        | Constraints File          | Biowre         |

| Speed -5 👱                          |                           |                |

| Optional Targets                    | Senthesis Options         | <u> </u>       |

|                                     | Implementation Options    | <u>C</u> ancel |

| Other Options<br>Run Synthesis Only |                           |                |

|                                     |                           | <u>H</u> elp   |

#### Figure 2-17 Xilinx Implementation Dialog Box

- 2. Select **7336** in the Part field. The default package is PC44, and the default speed is 5.

- 3. Make sure the Run Synthesis Only box is NOT checked.

4. Click on the **Implementation Options** button. The dialog box shown in Figure 2-19 appears:

| Xilinx EPLD Design Implementation      |

|----------------------------------------|

| Imprementation Options                 |

| O Ignore Pin Assignments In Schematics |

| O Freeze Pins                          |

| Drive Unused I/O                       |

| Optional Targets                       |

| Produce Static Timing Report           |

| X Produce Pin Freeze File              |

| Produce Device Programming Data        |

| Signature: FSM                         |

| <u>O</u> K <u>C</u> ancel <u>H</u> elp |

Figure 2-18 Implementation Options Dialog Box

- 5. This dialog box offers the following implementation options. Do not check any of these first three options.

- Ignore Pin Assignments in Schematics Does not apply to PROsynthesis designs.

- Freeze Pins If checked, tells the fitter to use the pin freeze file created the last time the fitter was run on the design, thereby preserving the pinout (default is unchecked).

- Drive Unused I/O If checked, drives unused I/O pins to VCC or GND to prevent noise in the chip (default is unchecked).

- 6. In addition to creating a design database, fsm.vmh, which the fitter does automatically, you can also tell the fitter to perform the following functions. Check all of these last three boxes.

- Produce Static Timing Report When checked, creates a report showing the calculated worst case timing for your design, fsm.tim (default is unchecked).

See the Fitter Reports appendix for more information on how to interpret the Static Timing Report.

- Produce Pin Freeze File When checked, creates a file containing the pin assignments, fsm.vmf (default is unchecked).

- Produce Device Programming Data When checked, creates an Intel HEX file for programming the device, fsm.prg (default is unchecked). The device programming file contains all necessary information for programming EPLDs using a device programmer.

A Signature field also appears when you check this box. Use the default signature, which is the design name.

7. Select the **OK** button to close the Implementation Options window, then select **OK** to run the fitter.

You will see a series of windows pop up and display messages from the fitter as your design is processed. Each window stays up after processing is complete so you can read the final messages. The window names are as follows: XEMAKE, TIMERPT, PINSAVE, and MAKEPRG.

8. After each window shows that processing is complete, close the window so the next process can begin. The Xilinx Implementation window closes when all processing is complete.

## **Timing Simulation**

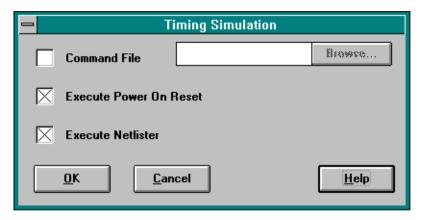

1. Select the second **PROsim** button in PROflow. The Timing Simulation dialog box appears as in Figure 2-20:

Figure 2-19 Timing Simulation Dialog Box

2. Select the **Command File** box and the **Browse** button. The Command Files browser appears as in Figure 2-21:

| -              | Command File | s              |

|----------------|--------------|----------------|

| File Name:     |              |                |

|                |              | <u>0</u> K     |

| FSM.CMD        |              |                |

|                |              | <u>C</u> ancel |

|                |              |                |

|                |              |                |

|                |              |                |

|                |              |                |

|                |              |                |

|                |              |                |

| Files of Type: |              |                |

| *.CMD          |              | <u>H</u> elp   |

|                |              |                |

Figure 2-20 Command Files Browser

- 3. Select **fsm.cmd** from the list, then select **OK**. The browser closes. The fsm.cmd file tells PROsim how to simulate the fsm design.

- 4. Select **OK** in the Timing Simulation dialog box. After the simulation netlist is created, the xsimmake.out file is displayed. Close this file window.

- 5. The PROsim window appears, and the netlist is read. Close the PROsim window when processing is complete (simulation is stopped at 1401 ns).

6. Select the **PROwave** button in PROflow. The PROwave Setup dialog box appears as in Figure 2-22:

|              | ProWave Setup               |

|--------------|-----------------------------|

|              |                             |

| Stream Name: |                             |

| FSM.WFM      |                             |

|              |                             |

| Signal Name: |                             |

|              |                             |

|              |                             |

| <u>0</u> K   | <u>C</u> ancel <u>H</u> elp |

#### Figure 2-21 PROwave Setup Dialog Box

- 7. Select **OK** in the PROwave Setup dialog box.

- 8. The PROwave window appears, along with the **File** → **Open** browser. Select **fsm.wfm** from the list and select **OK**.

The waveforms appear as in Figure 2-23:

#### Figure 2-22 Simulation Waveforms for the FSM Design

9. When you are finished viewing, close the PROwave window, then close the PROflow window.

# **Chapter 3**

# **Designing With EPLDs**

This chapter discusses how to use design techniques, library components, and attributes to get the best performance from Xilinx EPLDs. For more information on library components, see the Library Component Specifications appendix. For more information on attributes, see the Attributes appendix.

## VHDL Design File General Requirements

Design files for EPLD designs must reference the XC7000 library and must use IBUF and OBUF input and output buffers.

#### XC7000 Components Package

If you plan to instantiate any components from the XC7000 library, you will need to declare the Xilinx XC7000.components package in your design source file. It is generally a good idea to always declare this package in all EPLD designs.

To declare the XC7000.components package, insert the following two lines at the top of your VHDL source file:

```

library xc7000;

use xc7000.components.all;

```

## I/O Buffers

All input and output ports in your design must pass through IBUF and OBUF type buffer components. EPLD device pins will only be applied where IBUF and OBUF type buffers have been specified.

You can specify I/O buffers either in the main design file or in a separate file, whichever is more convenient.

#### Defining I/Os in the Main Design

For each input or output port in your main design, instantiate an IBUF or OBUF component from the XC7000 library and pass the signal through it on the way into or out of your design. For bus ports, you'll need to pass each signal through an individual IBUF or OBUF component. For 3-state output ports, you can either instantiate an OBUFE component and present the output enable signal to it, or express the 3-state assignment behaviorally and pass the resulting signal through an OBUF component. For bidirectional I/O ports, instantiate both an IBUF and either an OBUF or OBUFE, connecting both to the same inout-type port in your design.

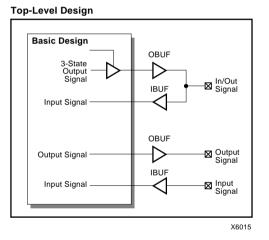

#### **Defining I/Os Using a Top-Level File**

Create your basic design using ViewLogic VHDL. In your design entity, define your input-only ("in") and output-only ("out" or "buffer") port signals as usual. However, do not define any bidirectional ("inout") ports in the basic design entity. Instead, define a separate input port signal ("in") and output port signal ("out") to represent the signals received from and transmitted to each physical I/O port. Each pair of input and output signals will later be connected to a pair of IBUF and OBUF components instantiated in the top-level design file to implement the desired bidirectional I/O port on the device.

Three-state output port signals, including those transmitted out to a bidirectional I/O, can be expressed in the basic design file as usual. Three-state outputs can be expressed either behaviorally or by instantiating a BUFE cell.

#### **Creating a Top-Level Design**

Your top-level design file defines the actual I/O ports to be implemented on the target device. The top-level design entity should define all the I/O port signals of your design as "in", "out" or "inout" (for bidirectional I/Os). Except for the inout ports, the port definitions in your top-level file should look similar to the port definition in your basic design file entity. Output ports defined as "buffer" in your basic design file can be declared as "out" in your toplevel file because they are not re-used as inputs at this level of the hierarchy. Within the architecture header of the top-level design file, you must declare the basic design entity as a component, and a set of intermediate signals used to connect the design instance to the I/O cell instances. In the architecture body, instantiate the basic design and connect the intermediate signals to it.

For each input signal, instantiate an IBUF cell (unless a special EPLDspecific input buffer is desired instead). For each output signal, instantiate an OBUF cell (unless a special EPLD-specific output buffer is desired instead). For each inout signal, instantiate both an IBUF and OBUF cell, and map their external ports to the same inout port signal.

The interconnections of port signals in the top-level design is illustrated in Figure 3-1.

#### **Special-Purpose I/O Ports**

As a minimum, you must instantiate IBUF and OBUF cells for all toplevel input, output, and I/O ports. However, the Xilinx component library also includes special-purpose I/O buffer cells that you can use instead of IBUF and OBUF to allow you to explicitly instantiate specific I/O functions. You will want to explicitly assign special I/O buffer cells for the following reasons.

- There are more clocks or OE signals in your design than there are FastClock or FOE pins available on the device. The Xilinx fitter automatically assigns the most frequently used clock signals to FastClock pins and the most frequently used 3-state control inputs to FOE pins. You can force specific clocks onto the global FastClock pins by instantiating the BUFG cell. You can force specific output enable signals onto the global FOE pins by instantiating the BUFFOE cell.

- You do not want some clocks, output enable signals, or registers to be optimized automatically. You can globally inhibit optimization of these resources by instantiating the NO\_FCLK, NO\_FOE, and NO\_IFD attribute cells. In this case you can manually assign selected clock or OE inputs to the global FastClock or FOE inputs by instantiating the BUFG or BUFFOE component. Instantiate the IFDX1 or ILD components to explicitly implement registers and latches in input pads.

- You are generating global clock or FOE signals from within your design. If you want to drive the global FastClock or FOE inputs from signals within your design, you must first drive those signals onto the corresponding device I/O pad through an output buffer (OBUF) and then back into the chip through either the BUFG component (for FastClocks) or through the BUFFOE component (for FOE inputs).

## **Selecting 3-State Control Sources**

Xilinx EPLDs have dedicated high-speed routing that can be used for fast output enable signals (FOE). Any unused FOE routing is automatically assigned by the fitter to the most used output enable signals in your design (unless you turn off optimization by using the NO\_FOE attribute).

To be eligible for optimization, an output enable signal must come directly from an input or I/O port and not be used for any other logic function.

#### Assigning Specific Fast Output Enable Signals

If you want to assign a specific output enable signal in your design to an FOE net, instantiate the BUFFOE input buffer to drive the Enable input of an OBUFEX1 component. The signal produced by the BUFFOE component cannot be used by any other logic, including the OE input of ordinary OBUFE components.

## Using Xilinx-Supplied Macros

The Xilinx library contains several VHDL macros of variable width (such as incrementors and comparators) that you can instantiate in your design.

To use these macros, do the following:

- Copy the macro from the examples\vwlogic\macro\_7k library to your design directory.

- Edit the macro and change the default value of the generic parameter WIDTH to your required width.

- Edit the macro and change its entity name to a new unique name (for example, append the width value to the original macro name). There are three places in the macro definition where this change needs to be made.

- Declare and instantiate the macro in your basic design.

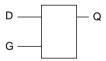

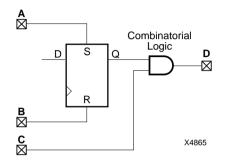

### Using Registers And Latches

The Xilinx EPLD architecture allows you to implement both registers and latches within function block macrocells and within input pads. This section shows you how to assign logic to specific registers and latches, and how to control their initial states after power is applied.

The Xilinx fitter uses input pad registers and latches to implement functions whenever possible to reduce the device macrocell resource requirements. Input pad registers also have a shorter setup time requirement than macrocell registers. Register functions using any control inputs, such as clear, preset, or clock enable, will only be implemented in macrocell registers; only simple D-type flip-flops can be optimized into input pads.

To be eligible for optimization into an input pad, a register's D and C inputs must come directly from input or I/O ports. The C (clock) input signal must be used only for register clocking, and the D (data) input signal must not be used for any other input.

**Note:** You can prevent the fitter from automatically assigning any registered or latched functions to the input pads by using the NO\_IFD global attribute cell in your source design, as described in the Attributes appendix.

#### **Using Input Pad Registers**

If you want to assign a specific register in your design to an input pad, instantiate the IFDX1 component. The Clock input must be driven by a BUFG component (global FastClk<sup>TM</sup>), and the Clock Enable input (if used) must be driven by a BUFCE component (Global Clock Enable). Except for signals declared as FastInputs, the D input signal must not be used for any other input.

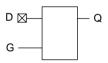

#### **Using Macrocell Registers**

Inferred registered functions will be placed either into macrocells or input pads at the discretion of the fitter (unless register optimization is turned off).

The techniques used to infer registers in EPLD designs are no different than for any other ViewSynthesis design. For example, the following behavioral VHDL process implements a D-type flip-flop with asynchronous clear and clock-enable:

```

process begin

wait until (prising (C) or (clr = '1'));

if (clr = '1') then

Q <= '0';

else

if (CE = '1') then

Q <= D;

end if;

end if;

end process;</pre>

```

You can also instantiate the FDCP, FDPC, or FDCPE register components. If none of the control inputs are used, the software will attempt to optimize these registers into input pads, provided optimization is enabled.

#### **Using Input Pad Latches**

If you want to assign a specific latch in your design to an input pad, instantiate the ILD component. The G input must be driven by a BUFG component (global FastClk). Except for signals declared as FastInputs, the D input signal must not be used for any other input.

#### **Using Macrocell Latches**

The EPLD architecture can implement simple transparent latches using the clear and preset product terms of macrocell flip-flops. However, any other logic functions adjacent to such a latch typically cannot be implemented in the same macrocell.

## **Using Special Logic Functions**

Some types of logic functions can be made faster and more efficient if they are constructed in a way that takes advantage of EPLD architectural features.

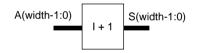

### **Binary Counters**

You should instantiate all counters, incrementers and decrementers from the XC7000 library. Do not attempt to express counters larger than 4 bits behaviorally using the "+1" or "-1" operations. If you do, the resulting implementation will tend to consume extra resources and run more slowly.

#### **State Machines**

When you initially compile a state machine, use the binary encoding option (the default). If the logic complexity of a binary encoded state machine results in poor device resource utilization, you can try less fully encoded state assignments explicitly in your VHDL design. In general you can use a few more registers to represent state vectors to reduce the amount of combinational logic required for each state flipflop.

In some cases, one-hot-encoding may produce satisfactory results, and it is convenient to specify to the synthesizer. Other schemes such as Gray coding do not help in EPLD designs because the EPLD architecture is primarily composed of D-type flip-flops.

#### **Arithmetic Functions**

All arithmetic components must be instantiated. Do not attempt to express adders or subtracters behaviorally using the "+" or "-" operators.

When creating registered arithmetic functions, instantiate the ACC component (Adder/Subtracter/Accumulator) or the ADSUR component (Adder/Subtracter with registered output) for best results. These components are scalable for any width and they are optimized for the Xilinx EPLD architecture.

#### Comparators

Magnitude comparators are expressed by instantiating the LT or LE components. They are implemented essentially the same as a subtracter, with the carry-out serving as the comparator output. 3-bit look-ahead logic at the low-order end of the comparator saves about 2 macrocells in the EPLD over the straight subtracter solution. The EPLD high-speed arithmetic carry chain is used for all magnitude comparators larger than 4 bits.

Equality comparators are implemented combinationally using XOR gates for each operand bit. The EPLD HDFB can accommodate up to an 8-bit equality compare in a single macrocell. You should use the EQ or NE components from the XC7000 library for all equality comparators. Comparators larger than 8 bits are implemented using multiple macrocells, each producing an 8-bit intermediate result. By using the EQ or NE components, the gate logic combining the macrocells' intermediate results is implemented in the UIM if possible (without extra delay).

Comparator outputs in high-speed applications are often pipelined before driving other logic or passing off-chip. By breaking larger comparators into 8-bit slices and pipelining each slice, gate logic combining the slices can still be implemented in the UIM (for on-chip logic).

In this example, a pipelined 16-bit comparator (with Boolean-type output Q) cannot be run at the maximum frequency of the EPLD because the logic preceding the register cannot fit a single macrocell:

```

U1: EQ_16 port map (AEQB, A(0 to 15), B(0 to 15));

process begin

```

```

wait (prising (clock));

Q0 <= AEQB;

end process;

```

In the following example, the 16-bit comparator is broken into two 8bit registered comparators, joined by a UIM-based AND-gate. This solution can be clocked at the maximum frequency of the EPLD if it drives on-chip logic.

```

U1: EQ_8 port map (AEQB_LOW, A(0 to 7), B(0 to 7));

U1: EQ_8 port map (AEQB_HI, A(8 to 15), B(8 to 15));

process begin

wait (prising (clock));

Q_LOW <= AEQB_LOW;

Q_HI <= AEQB_HI;

end process;

Q <= '1' when (Q_LOW = '1' and Q_HI = '1') else '0';</pre>

```

## **Targeting a Specific Device**

Before fitting your design you must select a target device. You have three key questions to consider when selecting an EPLD:

- How many signal pins are required?

- How much Logic resources are required?

- How much performance (speed) is required?

The answers to these questions determine which device you will choose to contain your design.

Device selection can be an iterative process, as shown in the following steps:

1. Use the Xilinx EPLD data book to make a preliminary choice. This choice is usually based on the number of required signal pins because this is often the easiest question to answer. It is easiest to begin with the largest device (XC73144); this gives you the best chance for a successful fit. Otherwise, you can get a very rough estimate of the number of required macrocells as follows:

[(the number of output ports)

+ (the number of flip-flops not directly driving output ports)] + [20%]

- 2. Run the fitter on your design using the selected device. After fitting, the Resource Report indicates how much device resources were required. This will help you determine the best device size. If your design does not fit you will need to choose a larger device or partition your design among multiple devices. If you have unused logic resources, you may want to try a smaller device.

- 3. Once an optimal device size has been determined, you can create a Static Timing Report that will indicate the calculated timing of your design based on the device layout. You can also simulate the timing of your design using the simulator. This timing information will help you select the optimal target device speed.

The EPLD Architecture appendix shows you a device selection chart. The Library Component Specifications appendix shows you which library components can be used with specific target devices. See the device data sheets for more information.

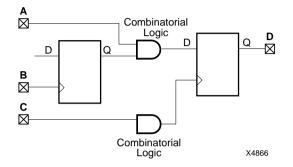

## **Controlling Design Performance**

Devices in the Xilinx EPLD family include Fast Function Blocks (FFBs) and/or High Density Function Blocks (HDFBs). Fast Function Blocks provide the shortest delay paths while High Density Function Blocks provide the most logic resources. EPLDs also contain special high speed routing for clocks, output enable signals, clock enable signals, and logic inputs to FFBs.

You can control your design performance by using attributes to assign specific signals in your design to the appropriate physical EPLD resources.

#### **Using High-Speed Clocks**

Xilinx EPLDs have dedicated high-speed (FastCLK) routing that can be used for global clock signals. Any unused FastCLK routing is automatically assigned by the fitter to the most used clock signals (if eligible) in your design (unless you turn off optimization). To be eligible for FastCLK optimization, an input port signal must be used only for register clocking using the positive clock edge.

**Note:** EPLD Fast Function Blocks, input pad registers, and input pad latches must use FastCLK routing; they cannot use normal signal routing for clocks.

#### Assigning Specific High-Speed Clocks

If you want to assign a specific clock in your design to a FastCLK net, instantiate the BUFG buffer cell in your design.

#### Selecting EPLD Function Block Types

By assigning logic signals to specific EPLD Function Block resources, you can control the performance of logic paths in your design.

#### **Specifying High Speed Paths**

To assign a logical signal to a Fast Function Block (shortest delay paths), instantiate the F attribute cell in your source design and pass the intended FFB output signal through it as follows:

U1: F port map (signal\_out, signal\_in);

This causes the logic function which produces *signal\_in* to be implemented in a FFB.

#### **Specifying High Density Paths**

To assign a logic signal to a High Density Function Block (normal delay paths), instantiate the H attribute cell in your source design and pass the intended HDFB output signal through it as follows:

U1: H port map (signal\_out, signal\_in);

This causes the logic function which produces *signal\_in* to be implemented in a HDFB.

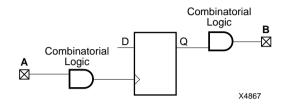

#### Using EPLD FastInputs

Some of the inputs to FFBs can be taken directly from input pins using a high-speed FastInput path which bypasses the Universal Interconnection Matrix. To assign input port signals to the EPLD FastInputs, instantiate the F attribute cell in your source design and pass the intended FastInput signal (from an IBUF buffer) through it as follows:

```

U1: F port map (signal_out, signal_in);

```

where *signal\_in* comes from an IBUF component. This causes any logic functions using *signal\_out* to take the input signal via the Fast

Input path, provided the function is implemented in a FFB.

**Note:** An input signal declared as a FastInput (applied to an F component) can also be used as the D input to an input pad register or latch (IFDX1 or ILD).

## The Design Rule Checker

The Design Rule Checker (DRC) reads the design from the database and checks to see if any of the design rules have been violated. The following is a partial list of rules that are checked.

#### **General Design Rule Violations**

The DRC displays an error or warning if:

- Open (hanging) inputs to an instantiated XC7000 component are found. Unless otherwise specified, all unused inputs of a library component must be connected or tied to VCC or GND.

- Some library components can only be used for a particular target EPLD. The DRC will generate an error if you attempt to use these components for other EPLDs. Restrictions on the use of components can be found in the library data sheets.

#### Pad Component Design Rule Violations

The DRC displays an error if:

- A signal driving an output port (input to an OBUF) is driven by more than one source.

- The same signal drives more than one output port (OBUF).

- An input port signal (from an IBUF) is connected directly to an output port signal (to an OBUF).

- An output port (OBUF) is driven by VCC or GND.

- Multiple input buffers (IBUFs) are connected to the same port (the exception is when an IBUF and F component are used with an IFD, IFDX1, or ILD to receive a FastInput signal).

#### FastCLK, Clock Enable, Fast Output Enable Violations

The DRC displays an error if:

- There are more FastCLK (BUFG), CE (BUFCE), or FOE (BUFFOE) ports in the design than the target EPLD can support.

- A FastCLK, CE, or FOE signal drives a component pin that is not a clock, CE, or FOE input.

# **Chapter 4**

## **Using PROflow**

This chapter shows you how to create a project directory, synthesize your design, fit your design, verify design timing, create a device programming file, and save your pinouts for later design iterations, all using the PROflow software.

You must have a complete VHDL design before compiling and fitting. You can run the compiler and fitter automatically one after the other, or you can run each separately.

### **Fitter Overview**

XEPLD is the Xilinx EPLD implementation software (fitter). XEPLD uses the schematic design produced by PROsynthesis (after compiling) to create a physical layout for a target EPLD. XEPLD performs the following functions:

- Converts a Viewlogic schematic into netlist form (XNF).

- Reads the netlist file (sch\*design\_name*.1) and reports any rule violations to the error log file (*design\_name*.err).

- Minimizes the combinational logic of your design so that it requires the least number of product term resources.

- Optimizes, partitions, and maps your design to fit within the architecture of the target device.

- Creates a pin-save file (optional) that is used to lock signal names to device pins, allowing you to keep the device pinouts during subsequent design iterations.

- Creates a Static Timing Report that shows the calculated worstcase timing for all signal paths in your design.

- Creates a timing simulation file that can be used by the PROsim simulator (*design\_name.*vsm).

- Creates a device programming file (*design\_name.prg*).

- Creates detailed reports that show you information such as the type and quantity of device resources used and device pinouts.

## **Creating a Project Directory**

To create and configure a project directory, follow these steps:

- 1. Open the Xilinx flow manager, PROflow, by double clicking on the Psfm icon. The Xilinx PROflow window appears.

- 2. Select the **PROcapture** button in PROflow. The Design Entry dialog box appears.

- 3. Click on the **Project Manager** button. The PRO Series Project Manager dialog box appears.

- 4. Select the Create button to open the Create Project dialog box.

- 5. In the Create Project dialog box, select or type in the path of the project directory you wish to create. If the directory does not exist, it is created automatically.

- 6. Select OK. The Create Project dialog box closes.

- 7. Select the project you just created if it is not selected already, then click on the **Select** button.

- 8. Select the Exit button to close the Project Manager.

- 9. After you close the project manager, the Select Family dialog box prompts you to select a device family. Select **XC7000** if it is not selected already, then select **OK**.

- 10. In the Design Entry dialog box, select **VHDL** as the Type of design.

- 11. Select the design file from the list. The file name appears in the Design Name field.

- 12. You can perform design entry at this point by checking the **Open Notepad** box.

- 13. Select the **OK** button to close the Design Entry window.

### **Compiler Operation**

To synthesize and create a schematic representation of your design, follow these steps.

- 1. Select the **PROcapture** button in PROflow. The Design Entry dialog box appears.

- 2. If your design has multiple files, for each lower-level file select the file name from the list and then select the **Quick Compile** button.

- 3. Select the top-level design file you want to process, then select **OK**. This closes the Design Entry window.

**Note:** If you have a purely behavioral VHDL design, you can perform functional simulation at this point by selecting the PROsim button in PROflow. For XC7000 designs, functional simulation is normally performed after you synthesize your design.

- 4. Select the **Xilinx** button in PROflow. The Xilinx Implementation dialog box appears.

- 5. Click on the **Synthesis Options** button. The Synthesis Options dialog box appears.

- 6. Make sure the **Generate Schematic** box is checked. This causes a schematic representation of the VHDL design to be created.

- 7. Select **OK** to close the Synthesis Options dialog box.

- 8. If you want to functionally simulate your design after synthesis, check the Run Synthesis Only box. This synthesizes your design without running the fitter. If you do not check this box, the fitter is automatically run after synthesis is complete.

If you are running synthesis and the fitter, DO NOT check Run Synthesis Only, skip the rest of this section, and go on to the next section, "Fitter Operation."

9. If you are running synthesis only, select **OK** to close the Xilinx Implementation dialog box and run the synthesis. When synthesis is complete, you see the following message in a prompt box:

Synthesis complete. View report?

You can select Yes or No. If you select **Yes**, you must close the report window after you have finished reading the report.

- 10. You are now ready to perform functional simulation. The steps for functional simulation are the same as for timing simulation, which is described later in this chapter; the only exception is step 5, in which the functional simulation flow displays the vsm.log file instead of the xsimmake.out file.

- 11. Click on the **Xilinx Implementation** button in PROflow to reopen the Xilinx Implementation dialog box.

## **Fitter Operation**

The following steps show you how to fit your schematic design into a target device using the Xilinx XEPLD fitter.

## **Fitting Your Design**

The XEPLD fitter translates the schematic representation of your design into a physical device layout. You can run the fitter automatically after synthesis or separately from synthesis.

At this point the Xilinx Implementation dialog box should be open. To invoke the fitter, follow these steps:

- 1. Select the part, package, and speed grade. The valid Xilinx EPLD part numbers are listed in the Part field. When you choose a part, valid packages and speed grades for that part are listed in the Package and Speed fields, respectively.

- 2. Make sure the Run Synthesis Only box is NOT checked.

- 3. Click on the **Implementation Options** button. The Implementation Options dialog box appears.

- 4. This dialog box offers the following implementation options.

- Ignore Pin Assignments in Schematics Does not apply to PROsynthesis designs.

- Freeze Pins If checked, tells the fitter to use the pin freeze file created the last time the fitter was run on the design, thereby preserving the pinout (default is unchecked).

- Drive Unused I/O If checked, drives unused I/O pins to VCC or GND to prevent noise in the chip (default is unchecked).

- 5. In addition to creating a design database, *design\_name*.vmh, which the fitter does automatically, you can also tell the fitter to perform the following functions.

- Produce Static Timing Report If checked, creates a report showing the calculated worst case timing for your design, *design\_name*.tim (default is unchecked).

See the Fitter Reports appendix for more information on how to interpret the Static Timing Report.

Produce Pin Freeze File — If checked, creates a file containing the pin assignments, *design\_name*.vmf (default is unchecked). During any subsequent invocation of the fitter, you can select the Freeze Pins option to restore pinouts saved in the .vmh file.

Making major changes to a fixed-pinout design may prevent the fitter from achieving a successful mapping if you use the Freeze Pins option. If the fitter fails, try running without this option to see if a fit is still possible. To fit a modified design into the selected device, you may need to delete some of the pin assignments in the .vmh file, allowing those pins to move to new locations.

You cannot use a previously saved pinout if you change the size or package type of the target device. See the EPLD Data Book to determine which devices in the EPLD family have compatible pinouts across similar packages.

• Produce Device Programming Data — If checked, creates an Intel HEX file for programming the device, *design\_name*.prg (default is unchecked). The device programming file contains all necessary information for programming EPLDs using a device programmer.

A Signature field also appears when you check this box. By default, the design name is used as the signature string. Only alphanumeric characters are allowed in the signature string; edit the string if necessary.

EPLD programmers are available from Xilinx and from thirdparty developers. See your device programmer documentation for instructions on how to download the programming file.

6. Select the **OK** button to close the Implementation Options window, then select **OK** to run the fitter.

You will see a series of windows pop up and display messages from the fitter as your design is processed. Each window stays up after processing is complete so you can read the final messages. The window names are as follows: XEMAKE, TIMERPT, PINSAVE, and MAKEPRG.

7. After each window shows that processing is complete, close the window so the next process can begin. The Xilinx Implementation Options window closes when all processing is complete.

### **Fitter Reports**

The fitter produces various reports:

- The Resource Report (*design\_name.*res) indicates how well your design fits in the target device. This report shows the utilization of macrocells, Function Blocks and each type of device pin, and indicates the amount of remaining logic and I/O resources in the device. The Resource summary is also displayed near the end of the fitnet process.

- The Pinlist Report (*design\_name*.pin) shows the signals assigned to each pin of the target device.

- The Partitioner Report (*design\_name.par*) and the Mapping Report (*design\_name.map*) show the detailed physical layout of your design within the EPLD.

- The Equation File (*design\_name*.eqn) contains boolean equations representing the final implementation of your design after minimization and optimization, and is expressed in Xilinx PLUSASM syntax.

- The Static Timing Report (*design\_name.tim*) shows the worst-case timing based on the physical implementation of your design.

**Note:** See the Fitter Reports appendix or the *Xilinx XEPLD Reference Guide* for more information on reports.

## **Design Timing Verification**

There are two ways you can verify your design timing:

- *The Xilinx Static Timing Report* provides the calculated worst-case timing for all signal paths in your design.

- *PROsim* provides timing simulation based on the physical layout of the target device.

## **Creating The Xilinx Static Timing Report**

The Static Timing Report is generated if you checked the Produce Static Timing Report box in the Implementation Options window.

The Static Timing Report is created and saved as *design\_name*.tim. See the Fitter Reports appendix for a complete description of the Static Timing report.

## **Performing Timing Simulation**

To perform timing simulation on the design, follow these steps:

- 1. Select the **PROcapture** button in PROflow. The Design Entry dialog box appears.

- 2. Select **Schematic** as the Type of design. You should see the schematic file in the Design Name field. Make sure the Start PROcapture box is NOT checked. Select the **OK** button.

- 3. Select the second **PROsim** button in PROflow. The Timing Simulation dialog box appears.

- If you are using a simulation command file (.cmd), select the Command File box and the Browse button. The Command Files browser appears. Select the .cmd file from the list, then select OK.

- 5. Select **OK** in the Timing Simulation dialog box. After the design is processed, the xsimmake.out file is displayed. Close this window.

- 6. The PROsim window appears, and the design is processed further. Close the PROsim window when processing is complete.

- 7. If your simulation command file created a waveform file, you can use PROwave to view it. (If you know PROwave commands, you can create a waveform file after simulation is complete.) Select the **PROwave** button in PROflow.

- 8. The PROwave Setup dialog box appears. Select **OK** in the PROwave Setup dialog box.

- 9. The PROwave window appears, along with the **File** → **Open** browser. Select the waveform file (.wfm) from the list (if you have one) and select **OK**.

- 10. Close the PROwave window.

# Appendix A

# **Using the Command Line**

You can run synthesis and the XEPLD fitter software from the DOS command line. This appendix shows you how to run the tutorial design, FSM, from the DOS command line. You can either run all the commands in a batch file or run each command individually.

## **Using a Batch File**

The files fsm.bat and fsm.src, which are supplied with the EPLD Viewlogic Synthesis tutorial, run all the DOS commands for the tutorial automatically and echo each command back to the screen. The fsm.bat file contains the Xilinx commands, and the fsm.src file contains the Viewlogic VHDL shell commands. The fsm.bat file invokes the fsm.src file, so all you need to do is type **fsm** at the DOS prompt.

## **Using Individual Commands**

Table A-1 shows, in the proper order, the specific commands needed to run the FSM design. This table also includes generic command formats and an explanation of each command.

| Command to Run Tutorial | Generic Format | Command Explanation                                                                                                |

|-------------------------|----------------|--------------------------------------------------------------------------------------------------------------------|

| vhdldes                 | vhdldes        | Enters the Viewlogic<br>VHDL design command<br>shell, where you can<br>invoke the VHDLDES<br>commands that follow. |

#### Table A-1 Commands to Run the Tutorial from DOS

| Command to Run Tutorial      | Generic Format                             | Command Explanation                                                                                                                                              |  |  |

|------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| technology xc7000            | technology family                          | Specifies the device fam-<br>ily.                                                                                                                                |  |  |

| (VHDLDES shell)              | (VHDLDES shell)                            |                                                                                                                                                                  |  |  |

| clear_work_library           | clear_work_library                         | Clears the working<br>library so that previously<br>run designs do not inter-<br>fere with the processing<br>of this design.                                     |  |  |

| (VHDLDES shell)              | (VHDLDES shell)                            |                                                                                                                                                                  |  |  |

| vhdl fsm.vhd                 | vhdl filename                              | Compiles the .vhd                                                                                                                                                |  |  |

| (VHDLDES shell)              | (VHDLDES shell)                            | source file(s). If your<br>design has more than<br>one file, run this com-<br>mand on each file, the<br>lowest-level files first<br>and the top-level file last. |  |  |

| synthesize                   | synthesize                                 | Produces a gate-level                                                                                                                                            |  |  |

| (VHDLDES shell)              | (VHDLDES shell)                            | representation of the design.                                                                                                                                    |  |  |

| wire                         | wire                                       | Produces a netlist of the                                                                                                                                        |  |  |

| (VHDLDES shell)              | (VHDLDES shell)                            | design in Viewlogic<br>WIR format.                                                                                                                               |  |  |

| exit                         | exit                                       | Exits the VHDLDES                                                                                                                                                |  |  |

| (VHDLDES shell)              | (VHDLDES shell)                            | command shell.                                                                                                                                                   |  |  |

| wir2xnf fsm -p<br>7336-5PC44 | wir2xnf design -p device                   | Creates an XNF format-<br>ted netlist file based on<br>the WIR file.                                                                                             |  |  |

| xnfmerge fsm                 | xnfmerge design                            | Flattens macros so the netlist is ready for fitting.                                                                                                             |  |  |

| fitnet fsm                   | fitnet design [-p device]<br>[-f   -i][-m] | Maps the design to the<br>device you specified<br>when using the wir2xnf<br>command. The -p option<br>can override the previ-<br>ous device specification.       |  |  |

| timerpt fsm                  | timerpt design                             | Creates a static timing report (.tim).                                                                                                                           |  |  |

| Command to Run Tutorial | Generic Format              | Command Explanation                                                                                                                                         |  |  |

|-------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| xsimmake -f vet fsm     | xsimmake -f vet design      | Creates a Viewsim netlist<br>(.vsm) file for timing<br>simulation. The -f vet<br>parameter stands for<br>"Viewlogic EPLD Tim-<br>ing."                      |  |  |

| pinsave fsm             | pinsave design              | Creates a pin freeze<br>(.vmf) file, which you<br>can use to preserve the<br>pinout in the next itera-<br>tion of the design (use<br>the fitnet -f option). |  |  |

| makeprg fsm -s fsm      | makeprg design -s signature | Creates an Intel HEX file,<br>which you use to pro-<br>gram the device.                                                                                     |  |  |

# Appendix B

# **EPLD** Architecture

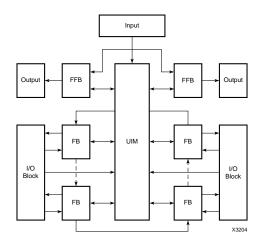

The Xilinx EPLD family uses a simple PAL-like architecture to provide both high speed and high density in a variety of packages and configurations. Through a unique Dual-Block architecture, High Density Function Blocks (FBs) provide high speed and maximum logic density for implementing complex functions while Fast Function Blocks (FFBs) provide even higher speed for critical decoding and ultra-fast state machine applications. For more information see *The Programmable Logic Data Book*.

The EPLD architecture consists of multiple Function Blocks and I/O blocks interconnected by the UIM as shown in Figure B-1.

Figure B-1 EPLD Architecture Block Diagram

## **Device Selection**

Table B-1 shows the Xilinx EPLD family, grouped by user application. Use this table to select the best target device for your design.