Introduction

**Getting Started**

**Design Entry**

**Functional Simulation**

**Design Implementation**

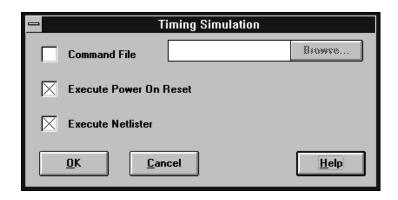

**Timing Simulation**

Design and Simulation Techniques

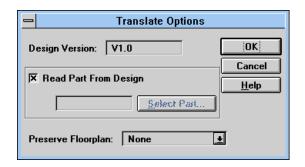

**Manual Translation**

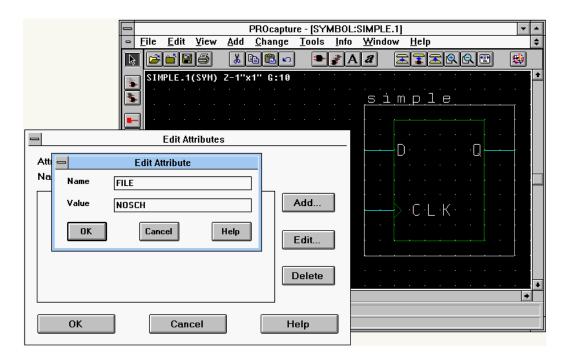

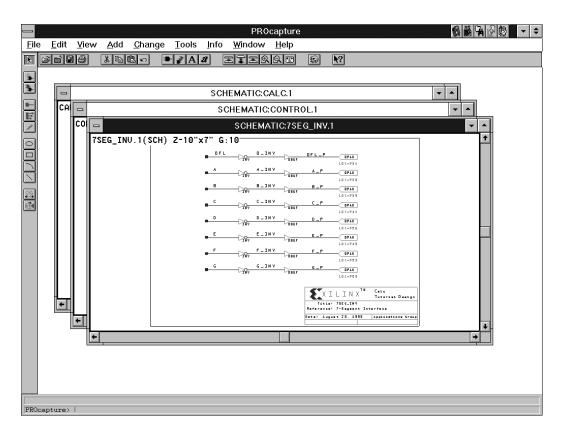

**PROcapture Commands**

**PROsim Commands**

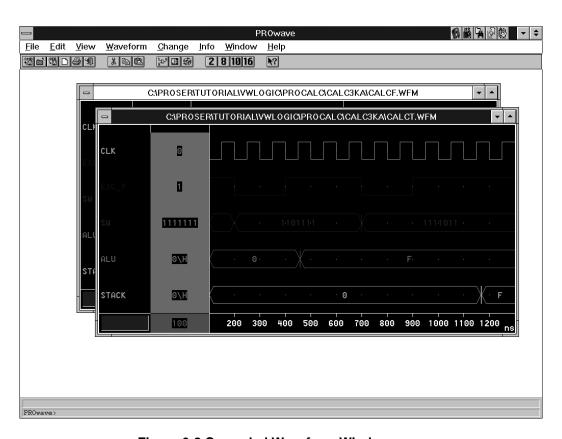

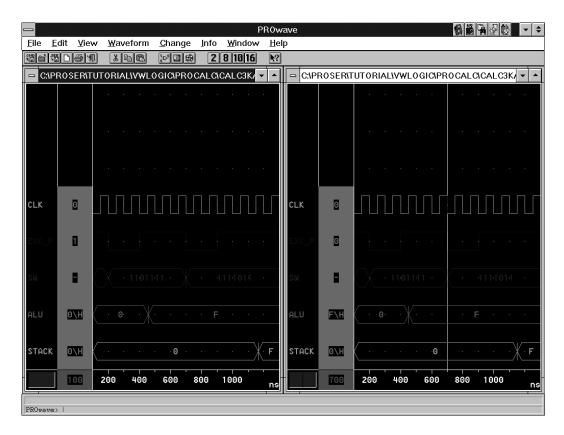

**PROwave Commands**

Glossary

Viewlogic Interface Guide — 0401307 01

Printed in U.S.A.

Chapter.book : covbook 2 Tue Sep 17 12:40:19 1996

#### Viewlogic Interface Guide

**₹XILINX**°, XACT, XC2064, XC3090, XC4005, and XC-DS501 are registered trademarks of Xilinx. All XC-prefix product designations, XACT-Floorplanner, XACT-Performance, XAPP, XAM, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, XPP, XSI, BITA, Configurable Logic Cell, CLC, Dual Block, FastCLK, HardWire, LCA, Logic Cell, LogicProfessor, MicroVia, PLUSASM, SMARTswitch, UIM, VectorMaze, VersaBlock, VersaRing, and ZERO+ are trademarks of Xilinx. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx.

IBM is a registered trademark and PC/AT, PC/XT, PS/2 and Micro Channel are trademarks of International Business Machines Corporation. DASH, Data I/O and FutureNet are registered trademarks and ABEL, ABEL-HDL and ABEL-PLA are trademarks of Data I/O Corporation. SimuCad and Silos are registered trademarks and P-Silos and P/C-Silos are trademarks of SimuCad Corporation. Microsoft is a registered trademark and MS-DOS is a trademark of Microsoft Corporation. Centronics is a registered trademark of Centronics Data Computer Corporation. PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc. UNIX is a trademark of AT&T Technologies, Inc. CUPL, PROLINK, and MAKEPRG are trademarks of Logical Devices, Inc. Apollo and AEGIS are registered trademarks of Hewlett-Packard Corporation. Mentor and IDEA are registered trademarks and NETED, Design Architect, QuickSim, QuickSim II, and EXPAND are trademarks of Mentor Graphics, Inc. Sun is a registered trademark of Sun Microsystems, Inc. SCHEMA II+ and SCHEMA III are trademarks of Omation Corporation. OrCAD is a registered trademark of OrCAD Systems Corporation. Viewlogic, Viewsim, and Viewdraw are registered trademarks of Viewlogic Systems, Inc. CASE Technology is a trademark of Digital Equipment Corporation. Synopsys is a registered trademark of Synopsys, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc.

Xilinx does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,853,626; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277;5,267,187;5,291,079;5,295,090;5,302,866;5,319,252;5,319,254;5,321,704;5,329,174;5,329,181;5,245,277;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,267,187;5,265,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; RE 34,363, RE 34,444, and RE 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Xilinx Development System

**Program Options**

Warning and Error Messages

Altran

## **Preface**

## **About This Manual**

This manual explains how to use the Viewlogic interface software to translate your FPGA or EPLD designs from Viewlogic schematics to implemented design and simulation files.

Before using this manual, you should be familiar with the operations that are common to all of Xilinx's software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*.

Other publications that you can consult for related information are the *Viewlogic Tutorials* manual, the *Xilinx ABEL User Guide*, the *X-BLOX Reference/User Guide*, the *Timing Analyzer Reference/User Guide*, and the *XEPLD Reference Guide*. You can also refer to the PRO Series documentation from Viewlogic.

## **Manual Contents**

This manual covers the following topics.

- Chapter 1, "Introduction," describes the programs that compose the Viewlogic interface, the Xilinx devices that Viewlogic's flow manager supports, and Viewlogic's design flow for FPGAs and EPLDs.

- Chapter 2, "Getting Started," explains how to configure your system to use PRO Series on PCs. It also briefly discusses how to use the Xilinx interface with Powerview on workstations.

- Chapter 3, "Design Entry," describes how to use PROcapture to enter a design.

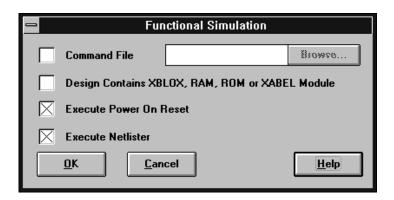

- Chapter 4, "Functional Simulation," describes how to use PROflow to create a simulation network and how to use PROsim to perform a functional simulation.

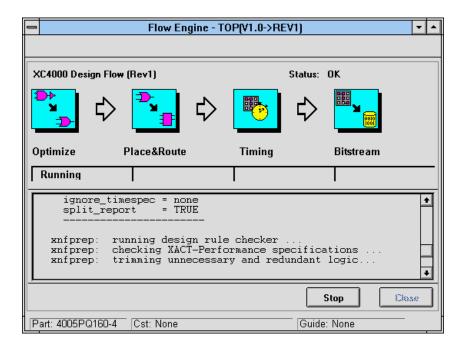

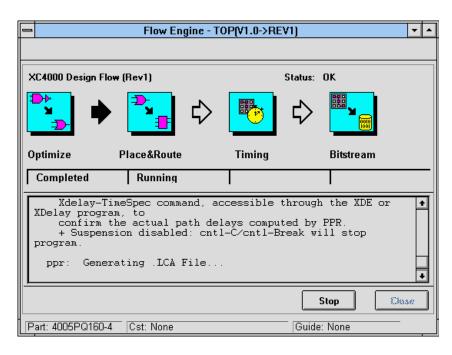

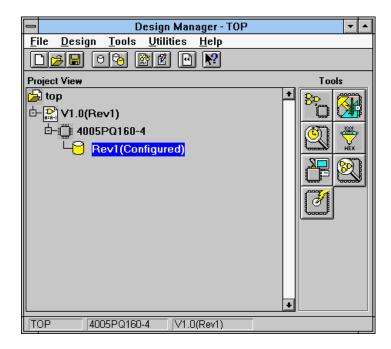

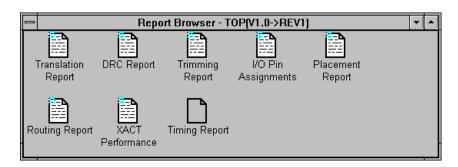

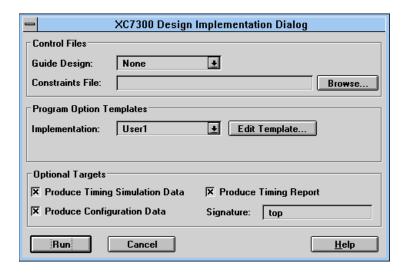

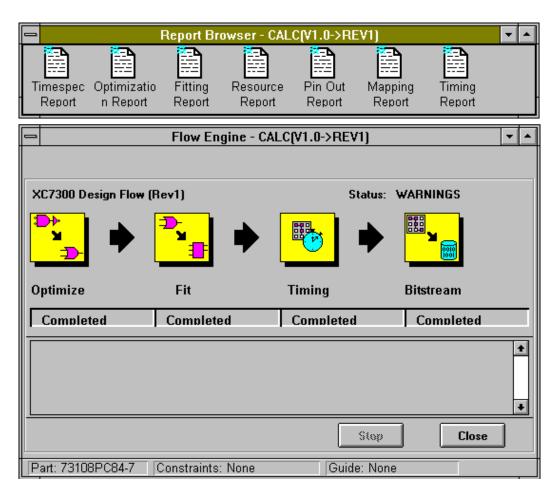

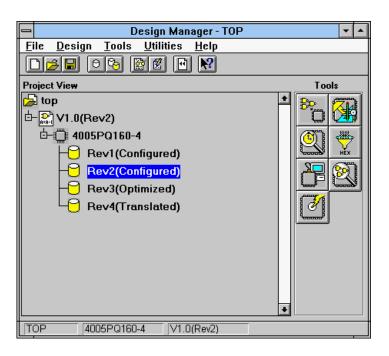

- Chapter 5, "Design Implementation," describes how to use the Xilinx Design Manager to implement and create timing simulation data for FPGA and EPLD designs.

- Chapter 6, "Timing Simulation," describes how to use PROflow to create a simulation network and how to use PROsim to perform a timing simulation.

- Chapter 7, "Design and Simulation Techniques," discusses aspects

of schematic entry and simulation with PRO Series and

Powerview that you should be familiar with to use these tools

effectively.

- Chapter 8, "Manual Translation," describes how to execute the XSimMake program, which automatically simulates your design; XMake, which automatically implements an FPGA design; and XEMake, which automatically implements an EPLD design. It also describes how to invoke the individual translation programs that produce a VSM file for simulation when you want to create it manually rather than automatically with XSimMake. In addition, this chapter explains how to use ViewGen to generate a ViewDraw schematic from a single WIR file.

- Chapter 9, "PROcapture Commands," lists and describes all the commands available in PROcapture.

- Chapter 10, "PROsim Commands," lists and describes all the commands available in PROsim.

- Chapter 11, "PROwave Commands," lists and describes all the commands available in PROwave.

- Appendix A, "Glossary," defines the key terms and concepts used throughout this manual.

- Appendix B, "Program Options," describes the options available in the translators that Viewlogic invokes to process your design manually.

Xilinx Development System

- Appendix C, "Warning and Error Messages," lists the warning and error messages that you may receive from the translators used to process your design manually.

- Appendix D, "Altran," gives instructions for using Altran, the Library Alias Maintenance Facility, to change the library aliases when you port a design from one family to another while using the Unified Libraries.

# **Conventions**

The following conventions are used in this manual's syntactical statements.

| Courier font regular | System messages or program files appear in regular Courier font.                                                           |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|

| Courier font bold    | Literal commands that you must enter in syntax statements are in bold Courier font.                                        |

| italic font          | Variables that you replace in syntax statements are in italic font.                                                        |

| [ ]                  | Square brackets denote optional items or parameters. However, in bus specifications, such as bus [7:0], they are required. |

| { }                  | Braces enclose a list of items from which you must choose one or more.                                                     |

|                      | A vertical ellipsis indicates material that has been omitted.                                                              |

|                      | A horizontal ellipsis indicates that the preceding can be repeated one or more times.                                      |

|                      | A vertical bar separates items in a list of choices.                                                                       |

| <b>→</b>             | This symbol denotes a carriage return.                                                                                     |

|                      |                                                                                                                            |

Chapter.book : conventions.doc vi Tue Sep 17 12:40:19 1996

| Chapter 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|           | Viewlogic Interface Programs PRO Series Workview PLUS Powerview PROcapture PROsim PROwave PROgen PROsynthesis Xilinx Device Support Design Flow Tutorials                                                                                                                                                                                                                                                                                                                                                              | 1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3                                              |

| Chapter 2 | Getting Started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

|           | PRO Series Required Software Installing the Software Starting Xilinx PROflow Creating a Project Obtaining Design Status Customizing Your Environment and Library Search Order Library Sequential Search Order Specifying Library Aliases Modifying the Viewdraw.ini File Invoking the Library List Editor Viewdraw.ini File Syntax Adding Xilinx Libraries Adding and Removing Libraries Powerview Required Software Installing the Software Creating a Project Customizing Your Environment and Library Search Order. | 2-1<br>2-2<br>2-3<br>2-5<br>2-10<br>2-11<br>2-13<br>2-15<br>2-15<br>2-17<br>2-18<br>2-19<br>2-19<br>2-19 |

Chapter 3

| Library Sequential Search Order          |      |

|------------------------------------------|------|

| Specifying Library Aliases               | 2-22 |

| Viewdraw.ini File Syntax                 | 2-24 |

| Modifying the Viewdraw.ini File          | 2-24 |

| Design Entry                             |      |

|                                          |      |

| Invoking PROcapture                      |      |

| Exiting PROcapture                       |      |

| Creating a Schematic                     |      |

| Creating Schematics with Multiple Sheets |      |

| Changing the PROcapture Window Colors    |      |

| Changing PROcapture Settings             |      |

| Navigating in PROcapture                 |      |

| Mouse Buttons                            |      |

| Keyboard Commands                        |      |

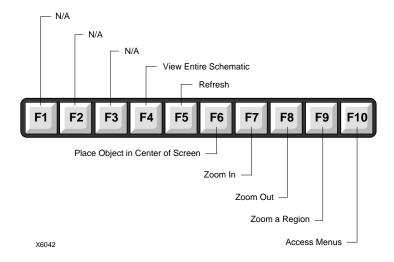

| Function Keys                            |      |

| Toolbar Icons                            |      |

| Menus                                    |      |

| Dialog Boxes                             |      |

| Obtaining Help                           |      |

| From the Toolbar                         |      |

| From the Menu                            |      |

| From the Keyboard                        |      |

| Online Product Information               |      |

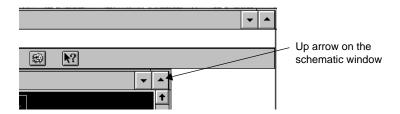

| Moving Around the Screen                 |      |

| Panning                                  |      |

| Zooming                                  |      |

| Making Icons of Schematics and Symbols   | 3-17 |

| Undoing Commands                         | 3-18 |

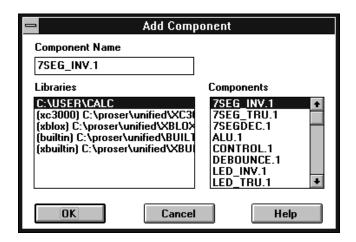

| Adding Components                        |      |

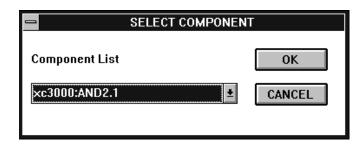

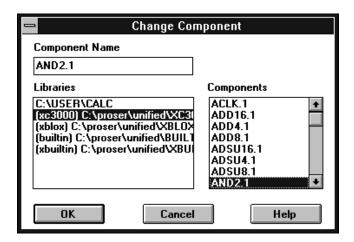

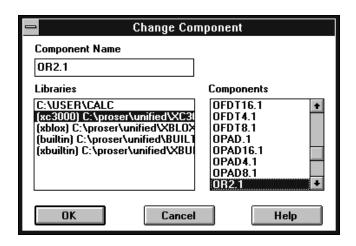

| Changing Components                      |      |

| Adding Nets                              | 3-23 |

| Adding Buses                             |      |

| Adding Arrays                            | 3-25 |

| Adding Graphical Objects                 | 3-26 |

| Adding Lines                             | 3-27 |

| Adding Boxes                             | 3-27 |

| Adding Arcs                              | 3-28 |

| Adding Circles                           | 3-29 |

| Adding Color and Pattern to Objects      | 3-29 |

| Rotating Objects                         |      |

| Mirroring Objects                       | 3-30 |

|-----------------------------------------|------|

| Scaling Objects                         | 3-31 |

| Re-Shaping Objects                      | 3-31 |

| User-Defined Macros                     |      |

| Creating Symbols (Macros)               | 3-33 |

| Changing Symbol Size                    | 3-34 |

| Creating Symbol Box                     | 3-34 |

| Adding Pins                             | 3-35 |

| Adding Pin Labels                       | 3-35 |

| Adding Pin Attributes                   | 3-36 |

| Merging Design Files from Other Sources | 3-36 |

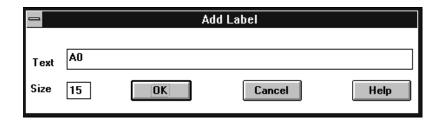

| Adding Labels                           | 3-36 |

| Naming Conventions                      |      |

| Reserved Names                          | 3-37 |

| Net Names                               | 3-37 |

| Component Names                         | 3-38 |

| Bus Names                               | 3-39 |

| Adding a Label                          | 3-39 |

| Changing Label Text                     |      |

| Changing Label Visibility               | 3-41 |

| Making Labels Invisible                 |      |

| Making Labels Visible                   | 3-41 |

| Adding Text                             |      |

| Changing Text Size                      | 3-43 |

| Adding Attributes                       |      |

| Using the Add Object Attribute Command  |      |

| Changing an Existing Attribute          | 3-44 |

| Changing Attribute Size                 |      |

| Changing Attribute Visibility           | 3-47 |

| Making Attributes Invisible             | 3-47 |

| Making Attributes Visible               | 3-47 |

| Copying Objects                         |      |

| Copying Directly to the Schematic       |      |

| Copying to the Clipboard                | 3-48 |

| Moving Objects and Text                 |      |

| Moving Objects                          |      |

| Moving Text                             |      |

| Deleting Objects                        |      |

| Removing Objects to the Clipboard       |      |

| Removing Objects                        | 3-51 |

| Saving Schematics                       | 3-51 |

|           | Copying Schematics  Navigating Through Schematics  Printing Schematics  Obtaining Information  Closing Schematics  Converting a Design                                                                                                                                                                                                                                                                                         | 3-55<br>3-56<br>3-57<br>3-60                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Chapter 4 | Functional Simulation                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

|           | Simulation Procedure Creating the Simulation Network Creating Vectors Adding Signals, Buses, and Vectors to the Waveform Defining Clocks, Standard Inputs, and Bidirectionals Defining a Clock Defining Standard Input Values Defining Bidirectional Input Values Simulating the Design Inputs Re-Creating Previous Simulation Invoking PROwave Changing the Display Radix in PROwave Changing the Display Radix in PROcapture | 4-2<br>4-5<br>4-5<br>4-6<br>4-7<br>4-7<br>4-7<br>4-8<br>4-8<br>4-10 |

| Chapter 5 | Design Implementation                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                     |

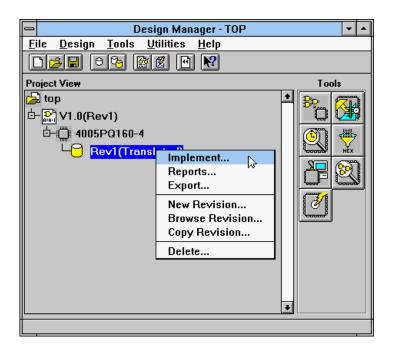

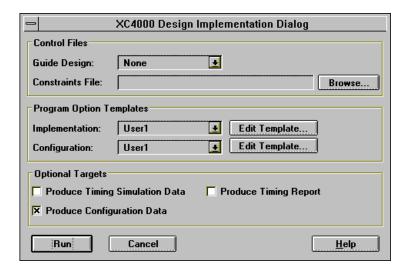

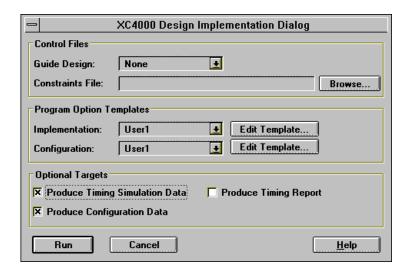

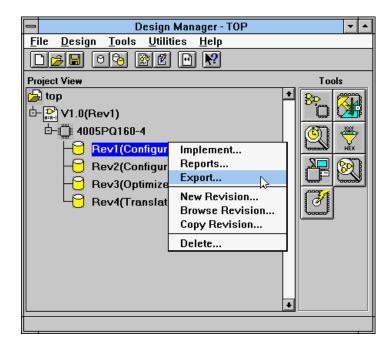

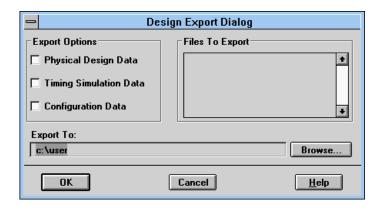

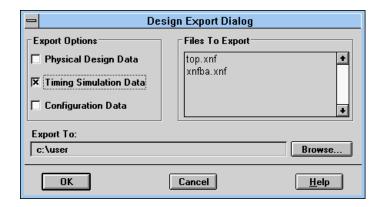

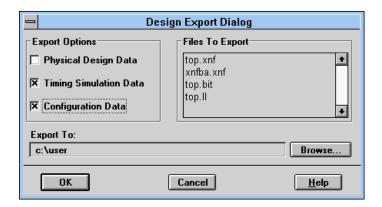

|           | Invoking the Design Manager  Creating the Xilinx Project and Its Initial Translation  Implementing an FPGA Design  Using the Report Browser  Implementing an EPLD Design  Exporting Revision Data  Translating the Design After Schematic Changes                                                                                                                                                                              | 5-3<br>5-10<br>5-16<br>5-17<br>5-20                                 |

| Chapter 6 | Timing Simulation                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |

|           | Simulation Procedure                                                                                                                                                                                                                                                                                                                                                                                                           | 6-2<br>6-8<br>6-8<br>6-9<br>6-12<br>6-13                            |

#### Chapter 7 **Design and Simulation Techniques** Primitives and Macros ...... 7-1 X-BLOX...... 7-2 Merging Non-Schematic-Based Modules ...... 7-4 XNF Files ...... 7-4 XEPLD Behavioral Modules ...... 7-5 PINTYPE ...... 7-7 Power and Ground Signals ...... 7-11 EPLD Design Issues ...... 7-11 Inputs, Outputs, and Bidirectionals ...... 7-11 Clocks and Global Control Nets ...... 7-11 Output and Tristate Buffers ...... 7-13 On-Chip Tristate Multiplexing ...... 7-16 Counters ...... 7-19 Arithmetic Components ...... 7-19 Using MemGen...... 7-20 Using X-BLOX ...... 7-21 Interfacing X-BLOX and PROcapture or ViewDraw Buses 7-22 Simulating OSC and GXTL (XC2000 and XC3000 Only) ...... 7-23 Simulating OSC4 (XC4000)...... 7-24 Simulating EPLD Designs ...... 7-25 Initialization Using PRLD and MRESET ...... 7-25 Node Visibility During EPLD Timing Simulation...... 7-26 Creating Stimulus Files in PROwave ...... 7-28 **Chapter 8** Manual Translation Design Flows ...... 8-1 Design Procedure ...... 8-2 Automatic Programs ...... 8-3

| Using XSimMake to Create Functional Simulation Data | 8-3  |

|-----------------------------------------------------|------|

| FPGA Designs                                        |      |

| Designs Containing Special Components               | 8-6  |

| Designs Containing User-Created Hard Macros         | 8-6  |

| Designs Containing FILE Attributes                  | 8-7  |

| Designs Containing X-BLOX Components                |      |

| Designs Containing Xilinx ABEL Components           | 8-9  |

| Designs Containing MemGen Components                | 8-10 |

| Designs Containing CLB and IOB Primitives (XC2000,  |      |

| XC3000, and XC3100 Only)                            | 8-11 |

| Invoking XSimMake                                   |      |

| EPLD Designs                                        | 8-12 |

| Invoking XSimMake                                   |      |

| Using XMake and XEMake to Implement Designs         | 8-13 |

| FPGA Designs                                        | 8-14 |

| Invoking XMake                                      |      |

| EPLD Designs                                        | 8-17 |

| Invoking XEMake                                     |      |

| Using XSimMake to Create Timing Simulation Data     |      |

| FPGA Designs                                        | 8-20 |

| Designs Containing Special Components               |      |

| Invoking XSimMake                                   |      |

| EPLD Designs                                        |      |

| Invoking XSimMake                                   |      |

| Running XSimMake from Windows                       |      |

| Individual Programs                                 |      |

| Creating a Xilinx Netlist Format (XNF) File         |      |

| WIRZXNF                                             |      |

| Syntax                                              |      |

| Input File                                          |      |

| Output File                                         |      |

| Options                                             |      |

| Warning and Error Messages                          |      |

| Rule Checking                                       |      |

| XNFMerge                                            |      |

| Syntax                                              |      |

| Input Files                                         |      |

| Output Files                                        |      |

| Options                                             |      |

| Creating a Functional Simulation (VSM) File         |      |

| FPI D Designs                                       |      |

Xilinx Development System

| FPGA Designs                                         | 8-28 |

|------------------------------------------------------|------|

| Creating VSM Files for Designs Containing No Special |      |

| Components                                           | 8-31 |

| Translating XFF Files to VSM Files                   | 8-31 |

| Translating XG Files to VSM Files                    | 8-32 |

| Translating Designs Containing IOB or CLB Primitives |      |

| to VSM Files                                         | 8-34 |

| Translating LCA Files to VSM Files                   | 8-34 |

| Creating an Implemented Design File                  | 8-36 |

| FPGA Designs                                         | 8-36 |

| EPLD Designs                                         | 8-36 |

| Creating a Timing Simulation (VSM) File              | 8-36 |

| FPGA Designs                                         | 8-36 |

| EPLD Designs                                         |      |

| Translation Programs for Simulation                  | 8-40 |

| XNF2WIR                                              |      |

| Invoking XNF2WIR                                     | 8-40 |

| Input File                                           | 8-41 |

| Output File                                          | 8-41 |

| VSM                                                  | 8-41 |

| Invoking VSM                                         | 8-41 |

| Input Files                                          | 8-42 |

| Output Files                                         | 8-42 |

| Example                                              | 8-42 |

| VSMUPD                                               | 8-42 |

| Invoking VSMUPD                                      | 8-43 |

| Input Files                                          | 8-43 |

| Output File                                          | 8-43 |

| VMH2XNF                                              |      |

| Invoking VMH2XNF                                     | 8-44 |

| Input File                                           | 8-44 |

| Output File                                          | 8-44 |

| ViewGen                                              | 8-44 |

| Purpose                                              | 8-45 |

| Preliminary Requirements                             | 8-45 |

| Schematic Format                                     | 8-45 |

| Connectivity                                         | 8-45 |

| Placement and Visibility                             | 8-45 |

| Invoking ViewGen                                     | 8-46 |

| Input File                                           |      |

| Output File                                          | 8-46 |

Chapter 9

| Sheet Symbols               | 8-47   |

|-----------------------------|--------|

| Contents                    |        |

| Attributes                  | 8-47   |

| Options                     | 8-48   |

| Multiple WIR Files          | 8-49   |

| PROcapture Commands         |        |

| Menus                       | 9-1    |

| File Menu                   |        |

| Edit Menu                   | 9-2    |

| View Menu                   | 9-2    |

| Add Menu                    | 9-3    |

| Change Menu                 | 9-3    |

| Tools Menu                  | 9-4    |

| Info Menu                   | 9-4    |

| Window Menu                 | 9-5    |

| Help Menu                   | 9-5    |

| Commands                    | 9-6    |

| About (Help Menu)           |        |

| Arc (Add Menu)              |        |

| Arrange Icons (Window Menu) |        |

| Array (Add Menu)            |        |

| BOM (Tools Menu)            |        |

| Box (Add Menu)              |        |

| Bus (Add Menu)              |        |

| Cascade (Window Menu)       |        |

| Check (Tools Menu)          |        |

| Circle (Add Menu)           |        |

| Clear (Edit Menu)           |        |

| Close (File Menu)           |        |

| Close All (Window Menu)     |        |

| Component (Add Menu)        |        |

| Component (Change Menu)     |        |

| Copy (Edit Menu)            |        |

| Cut (Edit Menu)             |        |

| Exit (File Menu)            |        |

| Fill Style (Change Menu)    |        |

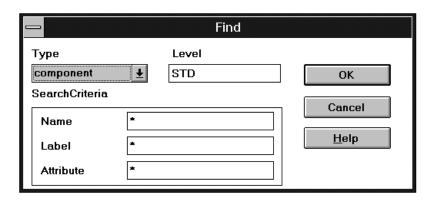

| Find (Edit Menu)            |        |

| From EDIF (Tools Menu)      |        |

| Full (View Menu)            |        |

|                             | M= 1 / |

| Hostid (Help Menu)                  | 9-12 |

|-------------------------------------|------|

| In (View Menu)                      | 9-12 |

| LDRC (Tools Menu)                   | 9-12 |

| Line (Add Menu)                     | 9-12 |

| Link to PROsim (Tools Menu)         | 9-13 |

| Link to Spice (Tools Menu)          | 9-13 |

| Memory Directory (Info Menu)        | 9-13 |

| Move (Edit Menu)                    | 9-13 |

| Net (Add Menu)                      | 9-14 |

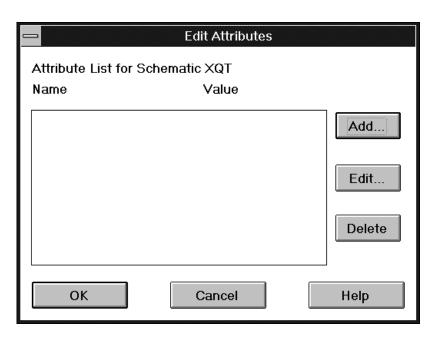

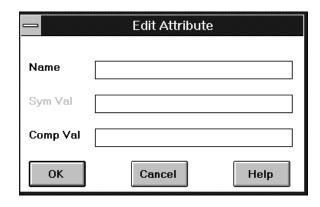

| Object Attribute (Add Menu)         | 9-14 |

| Object Attributes (Change Menu)     | 9-14 |

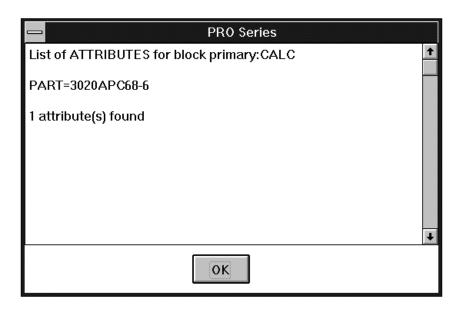

| Object Attributes (Info Menu)       |      |

| Object Color (Change Menu)          |      |

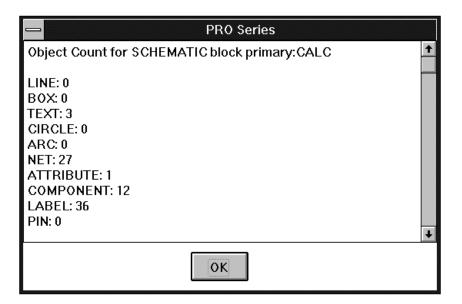

| Object Count (Info Menu)            | 9-17 |

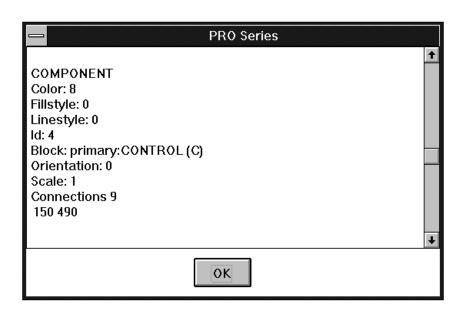

| Object Detail (Info Menu)           |      |

| Object Label (Add Menu)             | 9-18 |

| Object Label (Change Menu)          | 9-18 |

| Object Labels (Info Menu)           |      |

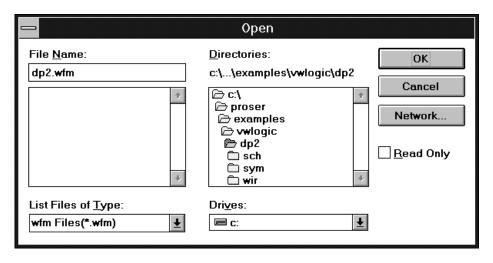

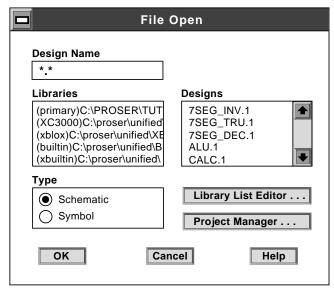

| Open (File Menu)                    |      |

| Out (View Menu)                     | 9-22 |

| Paste (Edit Menu)                   |      |

| PCB Interfaces (Tools Menu)         | 9-22 |

| Pin (Add Menu)                      |      |

| Pin Sense (Change Menu)             | 9-23 |

| Pop (View Menu)                     | 9-23 |

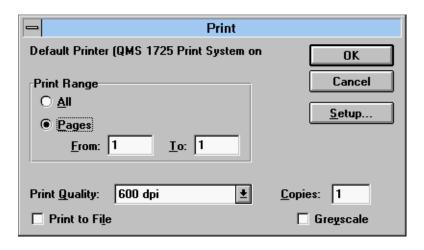

| Print (File Menu)                   | 9-24 |

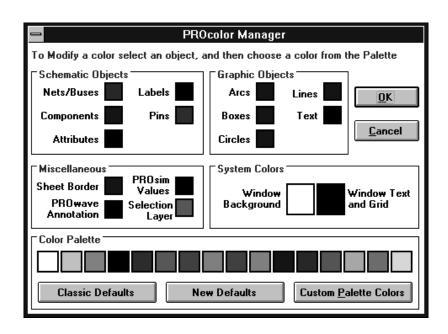

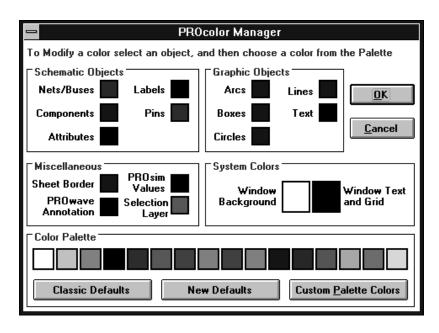

| PROcapture Colors (Change Menu)     | 9-24 |

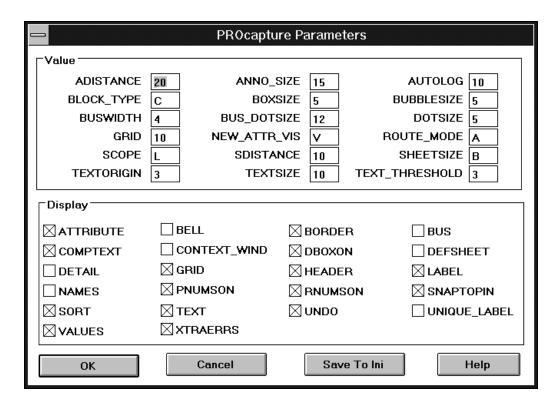

| PROcapture Parameters (Change Menu) | 9-25 |

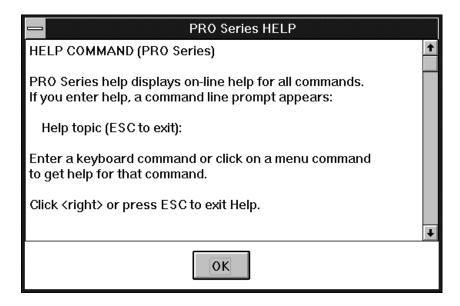

| PROhelp (Help Menu)                 |      |

| PROwave Annotation (View Menu)      | 9-27 |

| Push Into Schematic (View Menu)     | 9-27 |

| Push Into Symbol (View Menu)        | 9-27 |

| Push Next Sheet (View Menu)         | 9-27 |

| Refdes (Tools Menu)                 | 9-28 |

| Refresh (View Menu)                 | 9-28 |

| Region (View Menu)                  |      |

| Save (File Menu)                    | 9-28 |

| Save As (File Menu)                 | 9-28 |

| Schematic Directory                 |      |

| Select (Edit Menu)                  |      |

| Selected (View Menu)                | 9-30 |

|    | Sheet Size (Change Menu)     | 9-30 |

|----|------------------------------|------|

|    | Slot (Change Menu)           | 9-31 |

|    | Status (Info Menu)           | 9-31 |

|    | Symbol Directory (Info Menu) | 9-32 |

|    | Symbol Type (Change Menu)    | 9-32 |

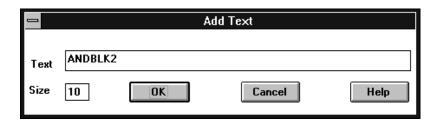

|    | Text (Add Menu)              | 9-33 |

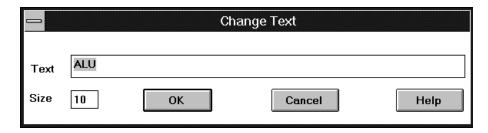

|    | Text (Change Menu)           |      |

|    | Tile (Window Menu)           | 9-33 |

|    | To EDIF (Tools Menu)         |      |

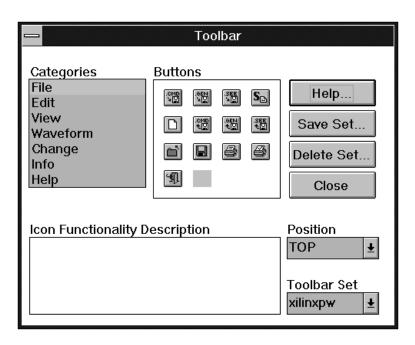

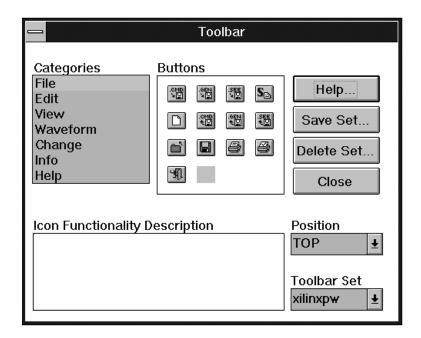

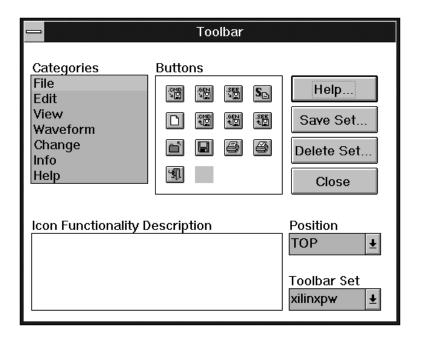

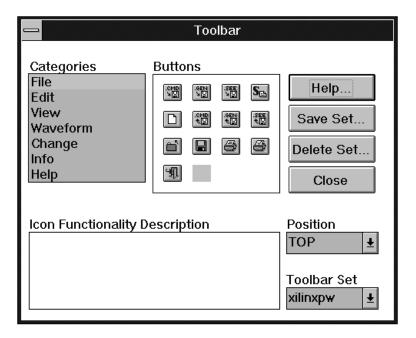

|    | Toolbar (View Menu)          | 9-33 |

|    | Transform (Change Menu)      |      |

|    | Undo (Edit Menu)             | 9-35 |

|    | XREF (Tools Menu)            | 9-36 |

| То | olbar Icons                  |      |

|    | Clear Icon                   | 9-36 |

|    | Open Icon                    | 9-36 |

|    | Close Icon                   | 9-37 |

|    | Save As Icon                 | 9-37 |

|    | Print Icon                   | 9-37 |

|    | Cut Icon                     | 9-37 |

|    | Edit Copy Icon               | 9-38 |

|    | Paste Icon                   | 9-38 |

|    | Undo Icon                    | 9-38 |

|    | Component Icon               | 9-39 |

|    | Array Icon                   | 9-39 |

|    | Text Icon                    | 9-39 |

|    | Attribute Icon               | 9-39 |

|    | Push Into Schematic Icon     | 9-40 |

|    | Push Into Symbol Icon        | 9-40 |

|    | Pop Schematic Icon           | 9-41 |

|    | In Icon                      | 9-41 |

|    | Out Icon                     | 9-41 |

|    | Full Icon                    | 9-42 |

|    | Help Icon                    | 9-42 |

|    | Move Icon                    | 9-42 |

|    | Copy Icon                    |      |

|    | Net Icon                     |      |

|    | Bus Icon                     |      |

|    | Pin Icon                     |      |

|    | Circle Icon                  |      |

|    | Poyleon                      |      |

xvi

|            | Arc Icon                     | 9-44  |

|------------|------------------------------|-------|

|            | Line Icon                    | 9-45  |

|            | Stretch Icon                 | 9-45  |

|            | Reflect Icon                 | 9-45  |

| Chapter 10 | PROsim Commands              |       |

|            | Menus                        | 10-1  |

|            | File Menu                    | 10-1  |

|            | Edit Menu                    | 10-1  |

|            | View Menu                    |       |

|            | Simulate Menu                |       |

|            | Values Menu                  |       |

|            | Help Menu                    |       |

|            | Commands                     |       |

|            | About PROsim (Help Menu)     | 10-3  |

|            | Assign (Values Menu)         | 10-3  |

|            | Breakpoints (Simulate Menu)  |       |

|            | Close (File Menu)            |       |

|            | Changes (View Menu)          | 10-5  |

|            | Command File (Simulate Menu) | 10-5  |

|            | Continue (Simulate Menu)     | 10-5  |

|            | Cycle (Simulate Menu)        | 10-5  |

|            | Defaults (Edit Menu)         | 10-5  |

|            | Defaults (View Menu)         | 10-6  |

|            | Delete (Edit Menu)           | 10-6  |

|            | Display (Values Menu)        | 10-8  |

|            | Exit                         | 10-8  |

|            | Force (Values Menu)          |       |

|            | Help (Help Menu)             |       |

|            | Hostid (Help Menu)           |       |

|            | Log File (Simulate Menu)     |       |

|            | Node/Vector (View Menu)      |       |

|            | Open (File Menu)             |       |

|            | Path (View Menu)             |       |

|            | PROhelp (Help Menu)          |       |

|            | PROwave (View Menu)          |       |

|            | Release (Values Menu)        |       |

|            | Report (View Menu)           |       |

|            | Restart (Simulate Menu)      |       |

|            | Run (Simulate Menu)          |       |

|            | Setup (Values Menu)          | 10-13 |

Chapter 11

| Sim (Simulate Menu)         | 10-17 |

|-----------------------------|-------|

| Toolbar (View Menu)         | 10-17 |

| Watchlist (View Menu)       | 10-19 |

| Toolbar Icons               | 10-19 |

| Open Icon                   | 10-19 |

| Exit Icon                   | 10-19 |

| Command File Icon           | 10-20 |

| Breakpoint Icon             | 10-20 |

| Continue Icon               |       |

| Simulate Icon               | 10-21 |

| Run Icon                    | 10-21 |

| Cycle Icon                  | 10-21 |

| Force Low Icon              | 10-22 |

| Force High Icon             | 10-22 |

| Force X Icon                | 10-22 |

| Help Icon                   | 10-23 |

| DDOwers Commande            |       |

| PROwave Commands            |       |

| Menus                       | 11-1  |

| File Menu                   | 11-1  |

| Edit Menu                   | 11-2  |

| View Menu                   | 11-2  |

| Waveform Menu               | 11-2  |

| Change Menu                 | 11-3  |

| Info Menu                   | 11-4  |

| Window Menu                 | 11-4  |

| Help Menu                   | 11-4  |

| Commands                    | 11-5  |

| About PROwave (Help Menu)   | 11-5  |

| Add (Waveform Menu)         | 11-5  |

| Annotate On (Change Menu)   | 11-5  |

| Annotate Off (Change Menu)  |       |

| Append (Change Menu)        |       |

| Arrange Icons (Window Menu) | 11-6  |

| Cascade (Window Menu)       | 11-6  |

| Close (File Menu)           | 11-6  |

| Close All (Window Menu)     | 11-6  |

| Copy (Edit Menu)            |       |

| Copy (Waveform Menu)        |       |

| Copy (Change Menu)          |       |

| Create Text (Waveform Menu) |       |

| ` '                         |       |

xviii

Xilinx Development System

| Cut (Edit Menu)                | 11-7  |

|--------------------------------|-------|

| Cut (Change Menu)              | 11-7  |

| Delete (Edit Menu)             | 11-8  |

| Delete Text (Waveform Menu)    |       |

| Display Params (Waveform Menu) | 11-8  |

| Edit Off (Edit Menu)           | 11-10 |

| Exit (File Menu)               |       |

| Full (View Menu)               | 11-10 |

| Grid (View Menu)               | 11-10 |

| Help (Help Menu)               | 11-11 |

| Hostid (Help Menu)             |       |

| Insert (Edit Menu)             |       |

| Modify Signal (Edit Menu)      |       |

| New (File Menu)                |       |

| Open (File Menu)               | 11-13 |

| Pan (View Menu)                |       |

| Paste (Edit Menu)              | 11-14 |

| Paste (Change Menu)            | 11-14 |

| Print (File Menu)              |       |

| PROhelp (Help Menu)            |       |

| Range (View Menu)              | 11-16 |

| Refresh (View Menu)            |       |

| Remove (Waveform Menu)         | 11-16 |

| Rename (Waveform Menu)         | 11-16 |

| Repeat (Edit Menu)             | 11-16 |

| Replace (Edit Menu)            | 11-17 |

| Save (File Menu)               | 11-17 |

| Save As (File Menu)            | 11-17 |

| Set Radix (Waveform Menu)      | 11-17 |

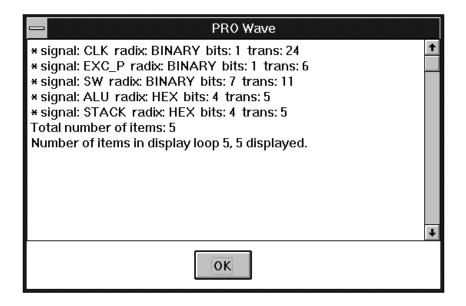

| Signals (Waveform Menu)        | 11-18 |

| Snap On (Change Menu)          | 11-19 |

| Snap Off (Change Menu)         | 11-19 |

| Status (Info Menu)             |       |

| Subst (Change Menu)            | 11-20 |

| Tile (Window Menu)             |       |

| TLimit (Change Menu)           | 11-21 |

| Toolbar (View Menu)            |       |

| TStep (Change Menu)            |       |

| Zoom In (View Menu)            | 11-22 |

| Zoom Out (View Menu)           | 11-23 |

|            | Toolbar Icons          | 11-23 |

|------------|------------------------|-------|

|            | Open Icon              | 11-23 |

|            | Close Icon             | 11-23 |

|            | Save As Icon           | 11-24 |

|            | New Icon               | 11-24 |

|            | Print Icon             | 11-24 |

|            | Exit Icon              | 11-24 |

|            | Cut Icon               | 11-25 |

|            | Copy Icon              | 11-25 |

|            | Paste Icon             | 11-25 |

|            | Annotate Icon          | 11-26 |

|            | Color Icon             | 11-26 |

|            | Schematic Signal Icon  | 11-26 |

|            | Binary Radix Icon      | 11-27 |

|            | Octal Radix Icon       |       |

|            | Decimal Radix Icon     | 11-27 |

|            | Hexadecimal Radix Icon | 11-27 |

|            | Help Icon              | 11-28 |

| Appendix A | Glossary               |       |

|            | Annotation             | Δ-1   |

|            | Attribute              |       |

|            | Back-Annotation        |       |

|            | Block                  |       |

|            | Breakpoint             |       |

|            | Bus                    |       |

|            | Command File           |       |

|            | Component              |       |

|            | Dangling Bus           |       |

|            | Dangling Net           |       |

|            | Label                  |       |

|            | Net.                   |       |

|            | Netlist                |       |

|            | Node                   |       |

|            | Period                 |       |

|            | Pin                    |       |

|            | Radix                  | _     |

|            | Schematic              |       |

|            | Sheet                  |       |

|            |                        |       |

|            | Signal                 | A-4   |

|            | Simulation Network | A-4        |

|------------|--------------------|------------|

|            | Step               | A-4        |

|            | Step Size          | A-4        |

|            | Symbol             | A-4        |

|            | Tick               | A-4        |

|            | Vector             | A-5        |

|            | Watch List         | A-5        |

|            | Waveform           | A-5        |

|            | Wire               | A-5        |

| Appendix B | Program Options    |            |

|            | XNF2WIR Options    | B-1        |

|            | -b                 |            |

|            | -с                 |            |

|            | -1                 | _ :        |

|            | -m                 | B-2        |

|            | -r                 | B-2        |

|            |                    | B-2        |

|            | _X                 | B-2        |

|            | VSM Options        |            |

|            | -d                 |            |

|            | _f                 |            |

|            | _h                 | _ :        |

|            | −ı<br>−s           |            |

|            | _t                 |            |

|            |                    |            |

|            | VSMUPD Options     | B-4        |

|            | -b                 |            |

|            | _0                 |            |

|            | _X                 |            |

|            | VMH2XNF Options    |            |

|            | -I 4, -I 5         |            |

|            | −0                 |            |

|            | FITNET Options     |            |

|            | -i                 |            |

|            | _ı                 |            |

|            |                    |            |

|            | ViewGen Options    | Б-о<br>В-6 |

|            | ·                  | Б-6        |

|            | -Cholp             |            |

|            | –help              |            |

|            | −i                 | D-0        |

|    | -makesym       | B-7  |

|----|----------------|------|

|    | -noschem       | B-7  |

|    | -0             | B-7  |

|    | -quiet         | B-7  |

|    | -sheet         | B-7  |

|    | -sheet         | B-8  |

|    | -sheetsym      |      |

| ٩d | vanced Options |      |

|    | -busname       | B-9  |

|    | -compcomp      |      |

|    | -compnet       |      |

|    | -comptext      |      |

|    | -flatten       |      |

|    | -gridsize      |      |

|    | -heightlimit   |      |

|    | -helpadv       |      |

|    | -inpin         |      |

|    | -latchfblevel  |      |

|    | -levellimit    |      |

|    | -loadlevel     |      |

|    | -netnet        |      |

|    | -outfblevel    |      |

|    | -outpin        |      |

|    | -permute       |      |

|    | -permuteinputs |      |

|    | -pinIbIsize    |      |

|    | -restart       |      |

|    | -symatt        |      |

|    | -symattsize    |      |

|    | -sympinIth     |      |

|    | -sympinspc     |      |

| Эt | her Options    |      |

|    | -analyze       |      |

|    | -complabels    |      |

|    | -deletenet     |      |

|    | -labelpos      |      |

|    | -latchsym      |      |

|    | -maxsheet      |      |

|    | -minsheet      |      |

|    | _visattr       | R-16 |

xxii

Xilinx Development System

|            | WIR2XNF Options                          | B-16 |

|------------|------------------------------------------|------|

|            | –p                                       | B-16 |

|            | -b                                       | B-16 |

|            | -od                                      | B-17 |

| Appendix C | Warning and Error Messages               |      |

|            | XNF2WIR                                  | C-1  |

|            | Warning Messages                         |      |

|            | VSM                                      |      |

|            | Warning Messages                         |      |

|            | Error Messages                           |      |

|            | VSMUPD                                   |      |

|            | Warning Messages                         | C-13 |

|            | Error Messages                           | C-13 |

|            | ViewGen                                  | C-14 |

|            | Error Messages                           | C-14 |

|            | WIR2XNF                                  | C-20 |

|            | Warning Messages                         | C-20 |

|            | Error Messages                           | C-22 |

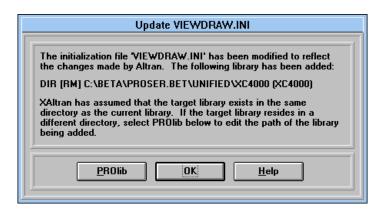

| Appendix D | Altran                                   |      |

|            | Library Aliases                          | D-1  |

|            | In Viewdraw.ini File                     |      |

|            | In WIR File                              | D-2  |

|            | Library Privileges                       | D-3  |

|            | Updating or Changing Aliases             | D-3  |

|            | Removing Aliases                         | D-4  |

|            | Options                                  | D-5  |

|            | –p                                       | D-5  |

|            | –all                                     | D-5  |

|            | -1                                       | D-6  |

|            | −n                                       | D-6  |

|            | -S                                       |      |

|            | –nocheck                                 |      |

|            | _V                                       |      |

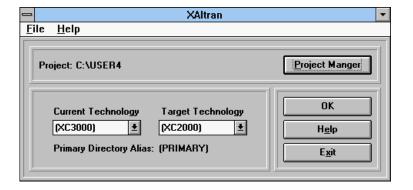

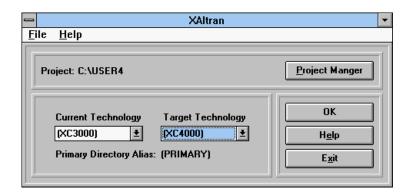

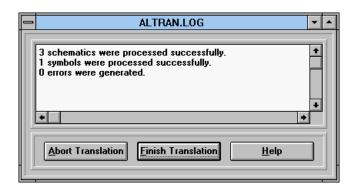

|            | Using XC3000 Drawings for XC4000 Designs | D-7  |

xxiv

# Introduction

# **Chapter 1**

# Introduction

This chapter describes the programs that comprise the Viewlogic interface, the Xilinx devices that Viewlogic's flow manager supports, and Viewlogic's design flow for FPGAs and EPLDs.

# **Viewlogic Interface Programs**

The Viewlogic interface programs support all of the Viewlogic systems: PRO Series, Powerview, and Workview PLUS. However, only PRO Series and some aspects of Powerview are discussed in this manual.

#### **PRO Series**

The PRO Series software is a windows-based system with a graphical user interface. It is available on PCs only.

This release supports PRO Series version 6.x and later.

#### **Workview PLUS**

Workview PLUS is windows-based Viewlogic software with a graphical user interface similar to Powerview's. It is available on PCs only.

#### **Powerview**

For workstations, Viewlogic offers Powerview, which contains enhancements in the graphical user interface.

# **PROcapture**

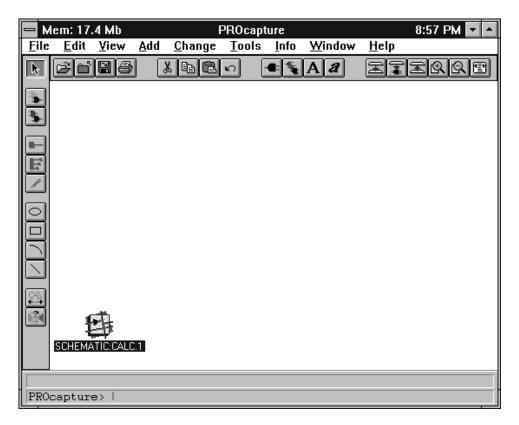

PROcapture is Viewlogic's schematic entry tool for PRO Series.

#### **PROsim**

PROsim is Viewlogic's interactive logic simulator.

#### **PROwave**

PROwave is a waveform viewer and editor.

#### **PROgen**

PROgen is a utility that generates a PROcapture schematic from a WIR file.

## **PROsynthesis**

PROsynthesis is Viewlogic's VHDL synthesis tool for the PC. It includes the VHDL designer and analyzer for synthesizing and simulating VHDL. PROsynthesis supports behavioral, RTL, and structural VHDL design styles and a number of design entry methods.

You can use PROsynthesis with XC2000, XC3000, XC3100, XC4000, XC5200, and XC7000 FPGAs.

The PROsynthesis software is available in the Viewlogic Stand-alone Extended packages from Xilinx or Viewlogic.

# **Xilinx Device Support**

The Viewlogic flow manager supports XC2000/L, XC3000/A/L, XC3100/A, XC4000/A/H/D, XC5200, XC7200, and XC7300 devices. XC7200 and XC7300 are EPLD devices, and the other families are FPGA devices.

# **Design Flow**

Viewlogic Interface Guide

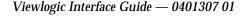

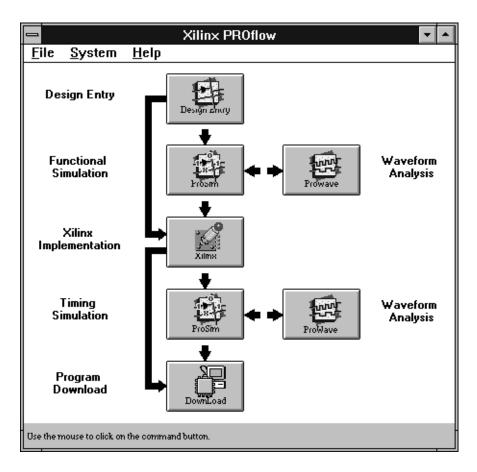

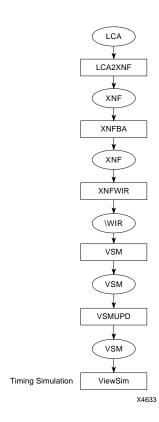

Creating FPGA and EPLD designs with Viewlogic PRO Series involves the following steps.

- Enter your design with the PROcapture schematic editor, making sure that you observe the Xilinx design requirements noted in this manual.

- 2. Test the functionality of your design by creating a functional simulation network (VSM file) and loading it into PROsim to simulate the design. You can use PROwave to view the waveforms generated by the simulation.

- 3. Implement your FPGA or EPLD design using the Xilinx Design Manager.

- 4. Verify the timing of your design by creating a timing simulation network (VSM file) and loading it into PROsim to simulate the design. You can use PROwave to view the waveforms generated by the simulation.

- 5. Download the design and verify the board.

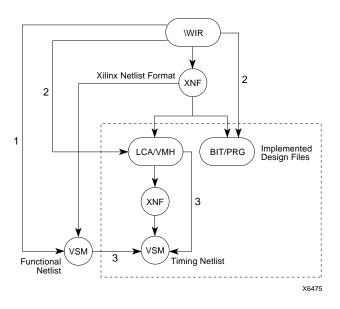

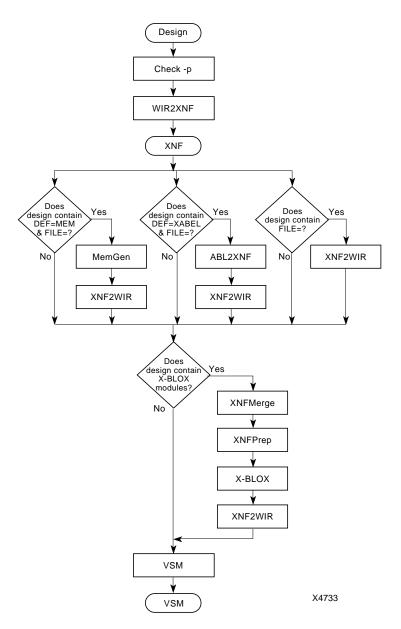

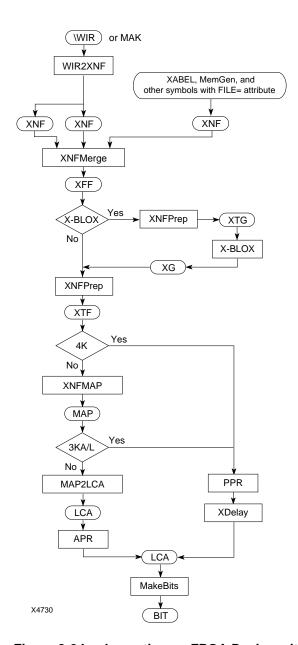

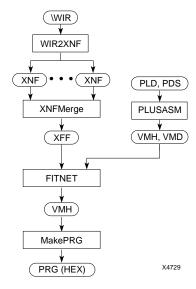

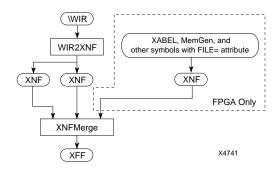

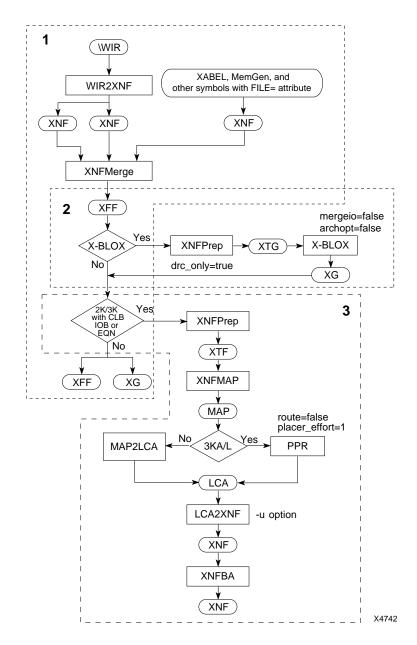

Figure 1-1 illustrates the design methodology for both FPGAs and EPLDs.

Figure 1-1 Viewlogic Design Methodology

# **Tutorials**

The *Viewlogic Tutorials* manual contains tutorials that illustrate how to use PROcapture, PROsim, and PROwave for design entry and simulation. It also contains tutorials describing how to use PRO Series with Xilinx ABEL, X-BLOX, XACT-Performance, and the Timing Analyzer.

**Getting Started**

# **Chapter 2**

# **Getting Started**

This chapter discusses how to configure your system to use PRO Series on PCs. It also briefly discusses how to use the Xilinx interface with Powerview on workstations.

## **PRO Series**

For examples showing how to set up your PRO Series software, see the *Viewlogic Tutorials* manual.

**Note:** The instructions in this manual are written for the PRO Series user, and the PRO Series 6.*x* environment is shown in the figures of this document. However, you can use the Xilinx interface programs with any current Viewlogic software, including Powerview V5.3.*x* or Workview PLUS V6.*x*. Workview 4.1.3a is also supported but does not run under the Windows environment.

# **Required Software**

To run PRO Series, you will need the following versions of the development software:

- PRO Series release 6.0 or later

- Xilinx/Viewlogic Interface and Libraries: WIR2XNF V6.0.x and XNF2WIR V6.0.x or later

- XACTstep Development System Software: DS-502 V6.0.x or later for FPGAs on PCs; DS502 V5.2.x for FPGAs on workstations; DS-550 V6.0.x or later for EPLDs on PCs; DS-550 V5.2.x or later for EPLDs on workstations.

## Installing the Software

Before you can use the PRO Series software, you must set up your PC to use the Viewlogic and XACT*step* Development System software.

- 1. Verify that your system is properly configured. Consult the Xilinx *Getting Started & Installation Guide* for instructions on setting up your machine to run the software.

- 2. Install one of the following sets of software. Each of these options includes Viewlogic PRO Series, the Xilinx/Viewlogic Interface and Libraries, and an XACTstep Development System.

- Base (DS-VLS-BAS-PC1), Standard (DS-VLS-STD-PC1), or Extended (DS-VLS-EXT-PC1) Stand-Alone (/S) Package Solutions for Viewlogic

or

Viewlogic PROcapture Schematic Editor, Interface, and Libraries (DS-390), PROsim Simulator (DS-290), and XACTstep Development System (DS-502) for FPGAs, and/or XACTstep Development System (DS-550) for EPLDs

or

Viewlogic PRO Series V6.x or later

and

Viewlogic Interface and Libraries (DS-391), and XACTstep Development System (DS-502) for FPGAs and/or XACTstep Development System (DS-550) for EPLDs; or Base (DS-VL-BAS-PC1) or Standard (DS-VL-STD-PC1) Interface Package Solution for Viewlogic

- 3. Verify that the following variables are set in your autoexec.bat file. It is assumed that you have loaded the software noted in the previous step to the c:\proser and c:\xact directories on your PC. If the software has been installed in different areas, modify the following Set statements accordingly. See the Xilinx *Getting Started & Installation Guide* for additional information on system setup.

- The PATH variable sets the overall executable search path. It

must include the directories where the PRO Series and

XACTstep Development System software have been installed.

Use the following syntax.

#### PATH=other\_paths; c:\XACT; c:\PROSER; other\_paths

**Note:** The PATH variable cannot include any previous version of either the XACT*step* or Viewlogic software. Be sure to remove all paths to older software.

The XACT variable is used by the XACTstep and PRO Series software to locate data files. It must include the directory where the XACTstep Development System resides and the directory that contains the \unified directory, where the Unified Libraries reside. Use this syntax:

#### SET XACT=C:\XACT;C:\PROSER

**Note:** As with the PATH variable, you can set XACT to multiple directories using a semicolon (;) between the paths. In the syntax just given, the XACT*step* software is located in c:\xact, and the \unified directory is located in c:\proser. Because both paths are needed, they have been concatenated into a single path using a semicolon.

The WDIR variable sets the data file search path for the PRO Series software. It must include a directory in which you can write. Use this syntax:

#### SET WDIR=C:\PROSER\STANDARD

The SYSPLT variable sets the PRO Series plotting directory. It must include a directory in which you can write. Use this syntax:

SET SYSPLT=C:\PROSER\STANDARD

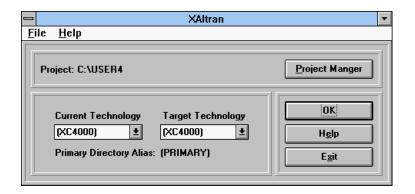

# **Starting Xilinx PROflow**

Xilinx PROflow is a flow manager that guides you through all the steps involved in processing a design with PRO Series. On the basis of information such as the design type, part type, family, and the components used, PROflow determines which options are available and which programs it must run to process the design correctly. Every tool and process step is executed by or invoked from PROflow. In addition to managing the processing of your design, PROflow also seamlessly integrates all the tools needed to enter, implement, simulate, and download your design.

PROflow also handles design maintenance. When you initially select a design within PROflow, it creates a design project and defines the associated libraries.

1. To open Xilinx PROflow, double-click on the Xilinx PROflow icon, shown in Figure 2-1, in the Program Manager XACT*step* program group.

Figure 2-1 Xilinx PROflow Icon

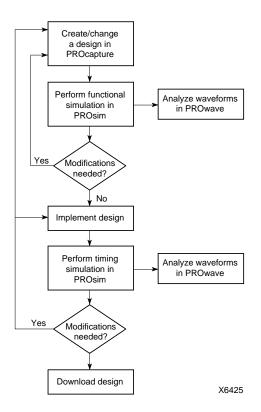

Selecting the Xilinx PROflow icon for the first time may bring up a warning message, shown in Figure 2-2, stating that a project is not defined.

Figure 2-2 Project Verification Warning Message

2. Click on OK.

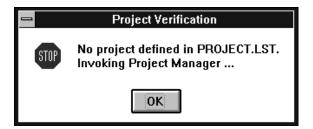

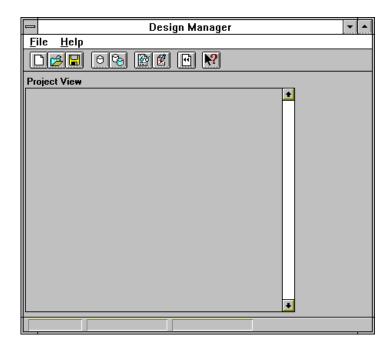

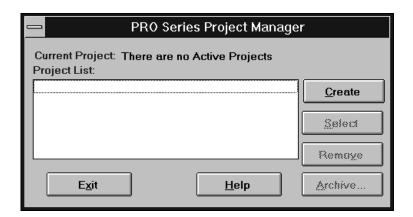

The message box closes, and the PRO Series Project Manager appears, as shown in Figure 2-3. The next describes how to use the Project Manager to create a project.

Figure 2-3 PRO Series Project Manager

## **Creating a Project**

The Viewlogic tools use the concept of projects to keep track of designs. A project is a working directory that contains the sub-directories and data files for a given design. Projects can even contain several designs of the same type, for example, a single project containing several XC3000A designs; however, it is recommended that each project contain only one design. The project containing the design actively being processed is known as the current project.

The PRO Series Project Manager allows you to select, create, and remove projects.

1. Click on Create in the PRO Series Project Manager.

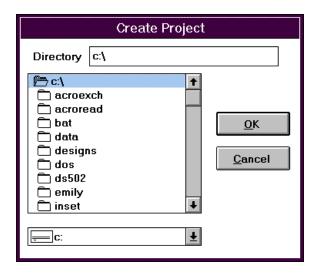

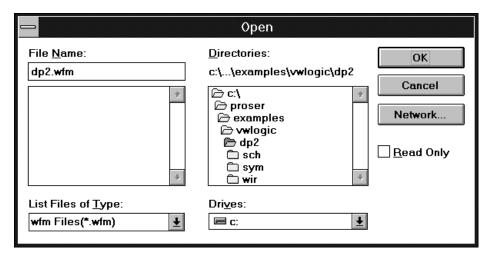

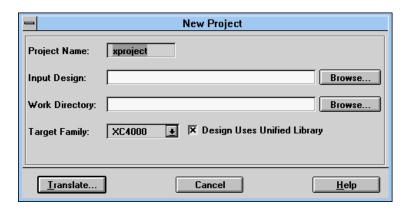

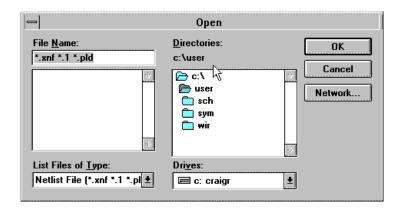

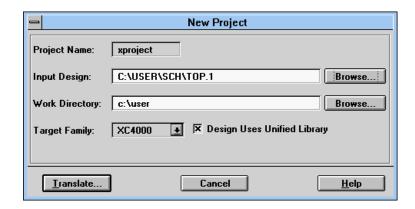

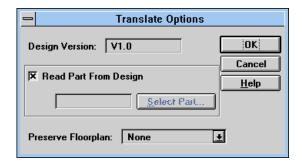

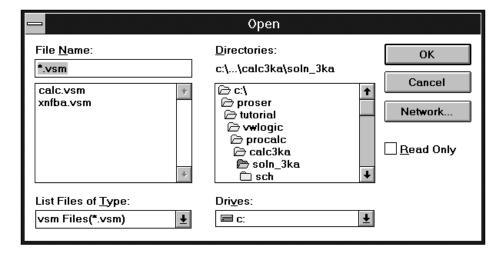

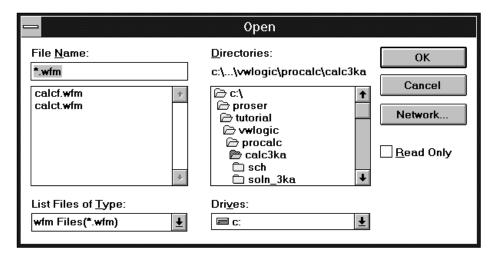

The Create Project dialog box appears displaying the drive on which the software was loaded in the Directory field; Figure 2-4 shows an example.

Figure 2-4 Create Project Dialog Box

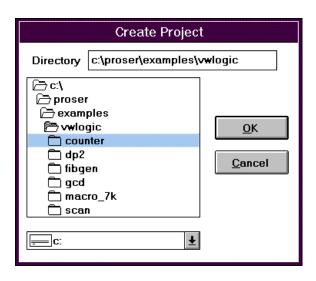

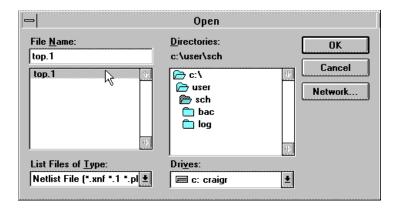

2. Select the directory by double-clicking in the Directory list box until the Directory field is correctly updated, as illustrated in Figure 2-5.

Figure 2-5 Updated Create Project Dialog Box

#### 3. Click on OK.

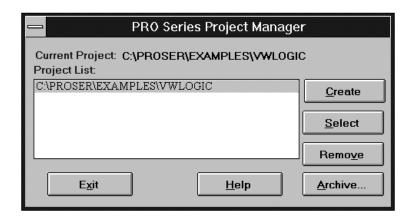

The Create Project dialog box closes, and the PRO Series Project Manager opens showing the selected directory in the Project List box, as indicated in Figure 2-6.

**Note:** If you are using a pre-existing project, the Project Manager displays a dialog box asking if the current project setup should be kept. In most cases, the current settings in the viewdraw.ini file should be kept.

For new projects, the Project Manager automatically creates the necessary initialization files when you create the new project.

Figure 2-6 Updated PRO Series Project Manager

- 4. Click on Select.

- To close the PRO Series Project Manager, click on Exit.

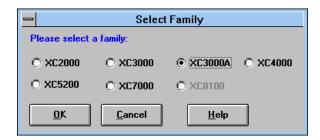

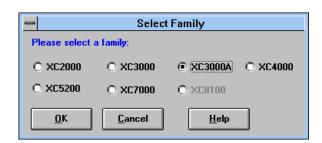

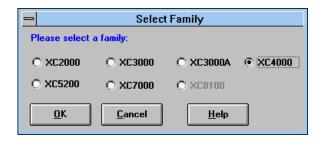

When you close the PRO Series Project Manager, the Select Family dialog box appears, as shown in Figure 2-7.

Figure 2-7 Select Family Dialog Box

- 6. Select the desired family for the project.

- 7. Click on OK.

The Xilinx PROflow window appears, as shown in Figure 2-8.

Figure 2-8 Xilinx PROflow Window

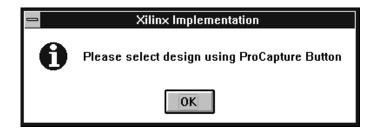

To guide you through the processing, PROflow only allows you to enter stages if the files that are needed for that step are present. For instance, if you click on the Xilinx Implementation icon, the message shown in Figure 2-9 appears.

Figure 2-9 Xilinx Implementation Warning Message

Because the design to be processed has not been defined, PROflow does not allow you to invoke the Xilinx Implementation section.

## **Obtaining Design Status**

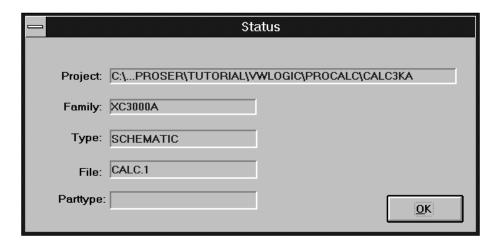

To see PROflow's initial project status, follow these steps.

1. Select the File  $\rightarrow$  Status command.

This command displays the Status dialog box, shown in Figure 2-10, which displays the currently known information about the design. As you enter and process the design, additional information appears in the remaining fields.

Figure 2-10 Status Dialog Box

#### 2. Click on OK.

The Status dialog box closes.

# **Customizing Your Environment and Library Search Order**

The viewdraw.ini file is the PROcapture initialization file. It contains the setup parameters for PROcapture as well as the libraries being used for the designs in the project. You must keep a copy of the viewdraw.ini file in each project directory so you can customize the library search order for each project. The viewdraw.ini file in \proser\standard is overwritten each time that you update the software, so any changes that you made to that file are lost.

PROflow creates a standard viewdraw.ini file automatically when a project is defined. The following sections describe how to change this standard setup to include user-created libraries and references to other projects.

## **Library Sequential Search Order**

The library sequential search order format allows you to specify an unlimited number of directories, with only one primary directory, and the order in which you want the library directories searched. The search order is determined by the order in which the directories are listed in the viewdraw.ini file.

It is strongly recommended that you place the primary directory first in the search path order. The directories are categorized as follows:

- p Primary directory

- w Secondary read/write directories

- r Secondary read-only directories

- m Megafile read-only directories

Library directories should conform to the search order shown in Table 2-1.

**Table 2-1 Library Search Order**

| Туре | Directory                | Library  |

|------|--------------------------|----------|

| р    | \project_directory       |          |

| m    | \proser\shm4000          | shm4000  |

| m    | \proser\unified\xc2000   | xc2000   |

| m    | \proser\unified\xc3000   | xc3000   |

| m    | \proser\unified\xc4000   | xc4000   |

| m    | \proser\unified\xc5200   | xc5200   |

| m    | \proser\unified\xc7000   | xc7000   |

| m    | \proser\unified\xblox    | xblox    |

| m    | \proser\unified\builtin  | builtin  |

| m    | \proser\unified\xbuiltin | xbuiltin |

**Note:** The Xilinx Viewlogic library package includes the builtin library, which is a simplified version of the complete builtin library sold by Viewlogic. You should use only the Xilinx-supplied builtin library (\proser\unified\builtin) in any Xilinx project directory.

You must add the builtin and xbuiltin libraries to the viewdraw.ini file if you simulate, and they must be specified *last*. These libraries are the Viewlogic simulation model libraries. If you do not specify them, you cannot simulate or push into the primitives to view the simulation models. Neither the builtin nor the xbuiltin libraries can be used to generate a user-created primitive library.

Ensure that the libraries associated with only one family appear in your viewdraw.ini file when you are entering a design. See the "Modifying the Viewdraw.ini File" section later in this chapter for information on how to modify the libraries.

**Note:** Different family libraries cannot be mixed in the same project directory. Specify libraries from only one Xilinx family in the viewdraw.ini file for each project directory.

For an XC4000 design on a PC, the library definition section should look like the following example.

| DIR | [p]   | •                        | (primary)  |

|-----|-------|--------------------------|------------|

| DIR | [ m ] | \proser\shm4000          | (shm4000)  |

| DIR | [ m ] | \proser\unified\xc2000   | (xc2000)   |

| DIR | [ m ] | \proser\unified\xc3000   | (xc3000)   |

| DIR | [ m ] | \proser\unified\xc4000   | (xc4000)   |

| DIR | [ m ] | \proser\unified\xc5200   | (xc5200)   |

| DIR | [ m ] | \proser\unified\xc7000   | (xc7000)   |

| DIR | [ m ] | \proser\unified\xblox    | (xblox)    |

| DIR | [ m ] | \proser\unified\builtin  | (builtin)  |

| DIR | [ m ] | \proser\unified\xbuiltin | (xbuiltin) |

| DIR | [ m ] | \proser\unified\xc2000o  | (xc2000o)  |

| DIR | [ m ] | \proser\unified\xc3000o  | (xc3000o)  |

| DIR | [ m ] | \proser\unified\xc4000o  | (xc40000)  |

| DIR | [ m ] | \proser\unified\xc5200o  | (xc5200o)  |

| DIR | [ m ] | \proser\unified\xc7000o  | (xc7000o)  |

**Note:** Specify the xcxx000 libraries only if you would like to know which components in the Unified Libraries replaced the components in the libraries pre-dating the Unified Libraries. The xcxx000 libraries are merely "notes" describing the current component names.

## **Specifying Library Aliases**

When specifying the library search order, you must also add a library alias to each library directory. A library alias is a name that identifies a specific library directory along with the parts that it contains. The alias distinguishes identically named components from different libraries. You must specify in the viewdraw.ini file the aliases for each Xilinx library for proper netlist translation.

Using library aliases, you can distinguish symbols with the same name from different libraries on a single schematic. Since only components from Xilinx libraries can be placed in a Xilinx schematic, you use this feature only when you have a custom library or when you are creating a system-level schematic containing different kinds of chips.

The library alias must be specified in parentheses in the viewdraw.ini file. Do not substitute any other aliases, because these alias names are used in the macro schematics within each library. XC3000, XC3000A/L, and XC3100A families use the XC3000 alias; XC4000 and XC4000A/D/H families use the XC4000 alias; XC5200 families use the XC5200 alias, and XC7200 and XC7300 families use the

XC7000 alias. Following are the libraries to use with each of the Xilinx families; notice the aliases specified for each library.

#### XC2000

- DIR [m] \proser\unified\xc2000 (xc2000)

- DIR [m] \proser\unified\builtin (builtin)

- DIR [m] \proser\unified\xbuiltin (xbuiltin)

- DIR [m] \proser\unified\xc2000o (xc2000o)

#### XC3000

- DIR [m] \proser\unified\xc3000 (xc3000)

- DIR [m] \proser\unified\xblox (xblox)

- DIR [m] \proser\unified\builtin (builtin)

- DIR [m] \proser\unified\xbuiltin (xbuiltin)

- DIR [m] \proser\unified\xc3000o (xc3000o)

#### XC4000

- DIR [m] \proser\shm4000 (shm4000)

- DIR [m] \proser\unified\xc4000 (xc4000)

- DIR [m] \proser\unified\xblox (xblox)

- DIR [m] \proser\unified\builtin (builtin)

- DIR [m] \proser\unified\xbuiltin (xbuiltin)

- DIR [m] \proser\xc4000o (xc4000o)

#### • XC5200

- DIR [m] \proser\unified\xc5200 (xc5200)

- DIR [m] \proser\unified\xblox (xblox)

- DIR [m] \proser\unified\builtin (builtin)

- DIR [m] \proser\unified\xbuiltin (xbuiltin)

- DIR [m] \proser\xc5200o (xc5200o)

#### XC7000

- DIR [m] \proser\unified\xc7000 (xc7000)

- DIR [m] \proser\unified\builtin (builtin)

- DIR [m] \proser\unified\xbuiltin (xbuiltin)

- DIR [m] \proser\xc7000o (xc7000o)

On a PC, you can add drive designators to the library paths, if necessary. Otherwise, the drive on which the viewdraw.ini file resides is assumed.

## Modifying the Viewdraw.ini File

When you initially create your project, PROflow creates the viewdraw.ini file for you. However, you may want to customize your viewdraw.ini file in certain cases, for example, when you have created a library containing macros that you want to use on a schematic. The Library List Editor is a utility that makes updating the viewdraw.ini file easier.

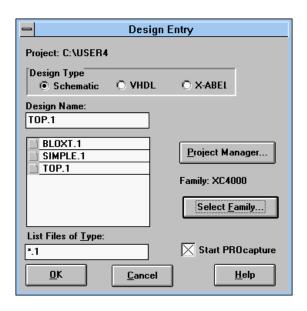

## **Invoking the Library List Editor**

To invoke the Library List Editor, follow these instructions.

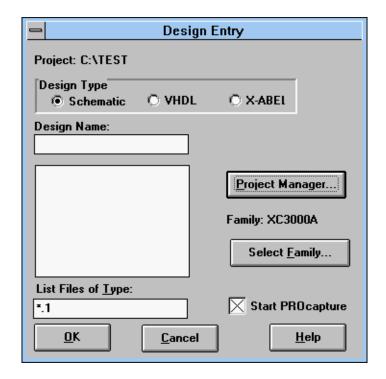

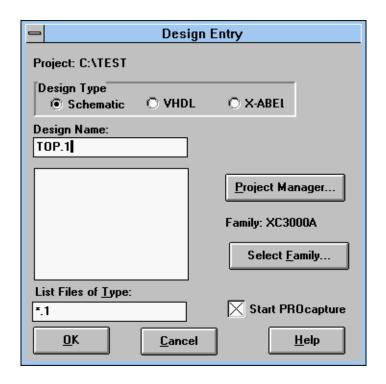

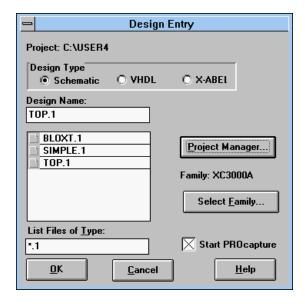

In PROflow, click on the Design Entry icon.

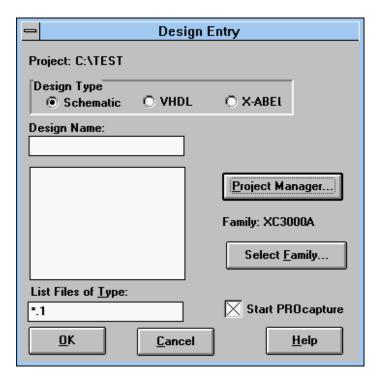

The Design Entry dialog box appears, as shown in Figure 2-11.

Figure 2-11 Design Entry Dialog Box

- 2. Enter the name of the design in the Design Name field.

- 3. Click on OK.

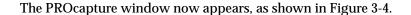

The PROcapture window now appears.

- 4. Select the File → Close command to close the current schematic.

- 5. In PROcapture, click on File → Library List Editor.

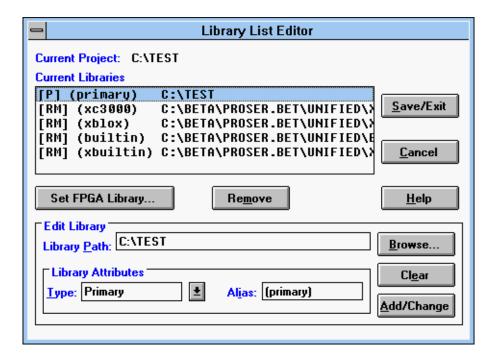

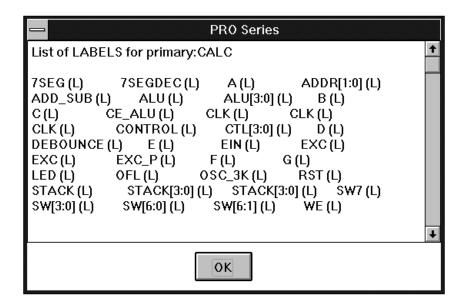

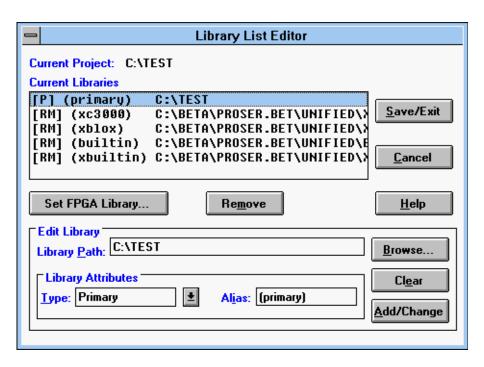

The Library List Editor appears, as illustrated by the example in Figure 2-12. In the Current Libraries list box, the first column displays the format, the second shows the aliases, and the third lists the library path names. The following section explains the syntax of the viewdraw.ini file.

Figure 2-12 Library List Editor

## Viewdraw.ini File Syntax

Near the end of the viewdraw.ini file is a series of lines defining the path names for each component library directory. These lines have the following syntax:

DIR [format] path (alias)

- Format indicates the library directory format; it can be one of the following.

- [m] indicates that the library is compressed into a megafile format. Megafiles are read-only by default. The Xilinx-supplied libraries are in megafile format for the PC.

- [r] indicates a read-only directory.

- [w] indicates a read-write directory.

- [p] denotes the primary or project directory. All symbols and schematics that you create are saved here.

- Path is the full path specification of the library. Specifying a period

(.) as the path name for the primary ([p]) directory causes PRO

Series to use the project directory as the base directory for all new schematics, user-generated symbols, netlists, and related simulation files.

- *Alias* is the library name associated with each component that you place in your schematic.

## Adding Xilinx Libraries

Now you are ready to modify the viewdraw.ini file.

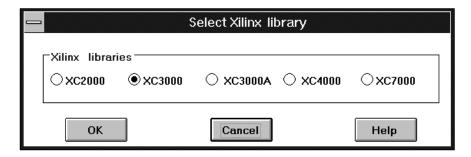

1. To add the standard Xilinx libraries to your project, click on Set FPGA Library.

The Select Xilinx Library dialog box appears, as shown in Figure 2-13.

Figure 2-13 Select Xilinx Library Dialog Box

- 2. Click on the desired FPGA family.

- 3. Click on OK.

## Adding and Removing Libraries

You can optionally add your own libraries to the viewdraw.ini file.

- To add an individual library, highlight the line above the location of the library to be added, and use either of the following methods.

- Type the library path name in the Library Path field, the format in the Type field, and the library alias in the Alias field. You must include the parentheses when typing in the alias.

- Alternatively, you can click on Browse, select the desired library, and click on OK. The Type and Alias fields are automatically updated.

- 2. Click on Add/Change.

- 3. Use the **Remove** button to delete any libraries that are out of order, and repeat steps 1 and 2 to add them in the correct order.

- 4. Click on Save/Exit to save your changes to the viewdraw.ini file and exit the Library List Editor dialog box.

**Note:** You can use the Clear button to clear the three fields in the Edit Library panel.

## **Powerview**

This section describes how to set up your Powerview environment.

## **Required Software**

To run Powerview, you will need the following versions of the development software:

• Viewlogic Interface and Libraries, DS-391: V6.0.x or later.

## **Installing the Software**

Before you can use the Powerview software, you must set up your workstation to use the Viewlogic and XACT*step* Development System software.

- 1. Verify that your system is properly configured. Consult the Xilinx *Getting Started & Installation Guide* for instructions on setting up your machine to run the software.

- 2. Install the DS-391 package or the DS-VL Standard package.

# **Creating a Project**

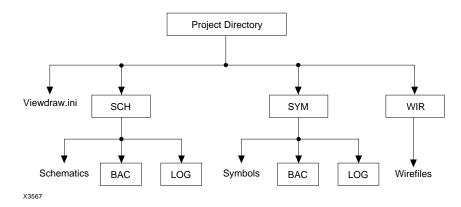

You can create a Viewlogic project directory anywhere on your system, but you must follow a standard structure within that directory. Each project directory must contain the sch, sym, and wir subdirectories.

- The sch directory contains files with graphic descriptions of your schematic.

- The sym directory contains files with graphic descriptions of the symbols that you create and save.

- The wir directory contains files with netlist descriptions of schematics.

The Viewlogic project directory structure is shown in Figure 2-14.

Figure 2-14 PROcapture Directory Structure

Before creating a design, you can optionally use ViewFile, a project management utility, to create a project directory in which the design files will reside.

You can create several project directories. If you are using a machine on which someone else has already used ViewFile, there will already be other project directories.

# **Customizing Your Environment and Library Search Order**

Like PRO Series, Powerview uses the viewdraw.ini file to set up the ViewDraw environment. This file also contains the path and directory search order for your libraries. You must keep a copy of the viewdraw.ini file in each project directory, so you can customize the library search order for each project. The viewdraw.ini file in /powerview\_path/standard is overwritten each time that you update the software, so any changes that you made to that file are lost.

## **Library Sequential Search Order**

The library sequential search order format allows you to specify an unlimited number of directories, with only one primary directory, and the order that you want the library directories to be searched. The search order is specified by the order in which the directories are listed in the viewdraw.ini file.

It is strongly recommended that you place the primary directory first in the search path order. The directories are categorized as follows:

p — Primary directory

w — Secondary read/write directories

r — Secondary read-only directories

m — Megafile read-only directories

Library directories should conform to the search order shown in Table 2-2.

Table 2-2 Library Search Order

| Туре | Directory                        | Library  |

|------|----------------------------------|----------|

| р    | /project_directory               |          |

| r    | /powerview_path/shm4000          | shm4000  |

| r    | /powerview_path/unified/xc2000   | xc2000   |

| r    | /powerview_path/unified/xc3000   | xc3000   |

| r    | /powerview_path/unified/xc4000   | xc4000   |

| r    | /powerview_path/unified/xc5200   | xc5200   |

| r    | /powerview_path/unified/XC7000   | xc7000   |

| r    | /powerview_path/unified/xblox    | xblox    |

| r    | /powerview_path/unified/builtin  | builtin  |

| r    | /powerview_path/unified/xbuiltin | xbuiltin |

**Note:** The Xilinx Viewlogic library package includes the builtin library, which is a simplified version of the complete builtin library sold by Viewlogic. You should use only the Xilinx-supplied builtin library (/powerview\_path/unified/builtin) in any Xilinx project directory.

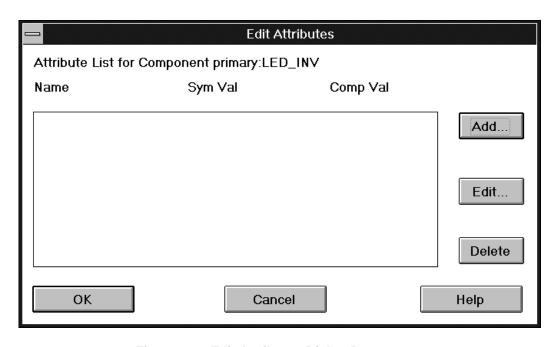

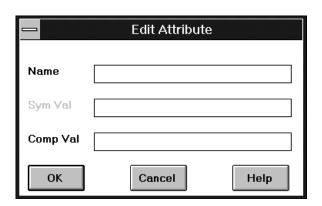

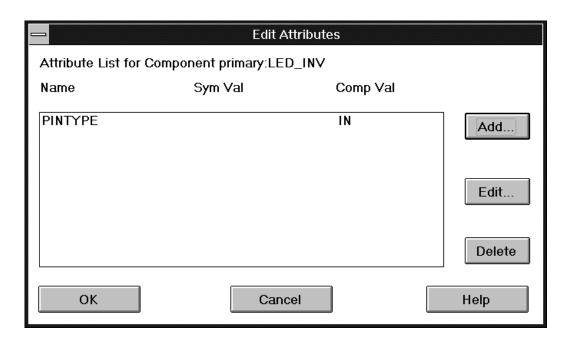

You must add the builtin and xbuiltin libraries to the viewdraw.ini file if you simulate, and they must be specified *last*. These libraries are the Viewlogic simulation model libraries. If you do not specify them, you cannot simulate or push into the primitives to view the simulation models. Neither the builtin nor the xbuiltin libraries can be used to generate a user-created primitive library.