# Viewlogic Tutorials

PROcapture and PROsim Tutorial

X-BLOX Tutorial

Xilinx ABEL Tutorial

XACT-Performance and Timing Analyzer Tutorial **₹XILINX**°, XACT, XC2064, XC3090, XC4005, and XC-DS501 are registered trademarks of Xilinx. All XC-prefix product designations, XACT-Floorplanner, XACT-Performance, XAPP, XAM, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, XPP, XSI, BITA, Configurable Logic Cell, CLC, Dual Block, FastCLK, HardWire, LCA, Logic Cell, LogicProfessor, MicroVia, PLUSASM, SMARTswitch, UIM, VectorMaze, VersaBlock, VersaRing, and ZERO+ are trademarks of Xilinx. The Programmable Logic Company and The Programmable Gate Array Company are service marks of Xilinx.

IBM is a registered trademark and PC/AT, PC/XT, PS/2 and Micro Channel are trademarks of International Business Machines Corporation. DASH, Data I/O and FutureNet are registered trademarks and ABEL, ABEL-HDL and ABEL-PLA are trademarks of Data I/O Corporation. SimuCad and Silos are registered trademarks and P-Silos and P/C-Silos are trademarks of SimuCad Corporation. Microsoft is a registered trademark and MS-DOS is a trademark of Microsoft Corporation. Centronics is a registered trademark of Centronics Data Computer Corporation. PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc. UNIX is a trademark of AT&T Technologies, Inc. CUPL, PROLINK, and MAKEPRG are trademarks of Logical Devices, Inc. Apollo and AEGIS are registered trademarks of Hewlett-Packard Corporation. Mentor and IDEA are registered trademarks and NETED, Design Architect, QuickSim, QuickSim II, and EXPAND are trademarks of Mentor Graphics, Inc. Sun is a registered trademark of Sun Microsystems, Inc. SCHEMA II+ and SCHEMA III are trademarks of Omation Corporation. OrCAD is a registered trademark of OrCAD Systems Corporation. Viewlogic, Viewsim, and Viewdraw are registered trademarks of Viewlogic Systems, Inc. CASE Technology is a trademark of Digital Equipment Corporation. Synopsys is a registered trademark of Synopsys, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc.

Xilinx does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,853,626; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277;5,267,187;5,291,079;5,295,090;5,302,866;5,319,252;5,319,254;5,321,704;5,329,174;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,329,181;5,325,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; RE 34,363, RE 34,444, and RE 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

# **Preface**

### **About This Manual**

This manual is a series of tutorials illustrating how to use the PRO Series PROcapture, PROsim, and PROwave programs. It also shows you how to use these programs with X-BLOX, Xilinx ABEL, XACT-Performance, and the Timing Analyzer.

Before using this manual, you should be familiar with the operations that are common to all of Xilinx's software tools: how to bring up the system, select a tool for use, specify operations, and manage design data. These topics are covered in the *Development System Reference Guide*.

Other publications that you can consult for related information are the Viewlogic Interface Guide, the Xilinx ABEL User Guide, the X-BLOX Reference/User Guide, the Design Manager/Flow Engine Reference/User Guide, the Timing Analyzer Reference/User Guide, and the PRO Series manuals from Viewlogic.

## **Manual Contents**

This manual covers the following topics.

• Chapter 1, "PROcapture and PROsim Tutorial," guides you through a typical design procedure from schematic entry to completion of a functioning device using Viewlogic's PROcapture schematic editor. It steps through both a functional simulation and a timing simulation using Viewlogic's PROsim and PROwave programs. It also describes how use the Xilinx Design Manager to implement the design.

- Chapter 2, "X-BLOX Tutorial," shows you how to incorporate X-BLOX modules into your FPGA design. X-BLOX is an advanced library and a synthesis tool that allows you to shorten design entry time, increase design speed, and use a device more efficiently.

- Chapter 3, "Xilinx ABEL Tutorial," shows you how to incorporate Xilinx ABEL modules into your FPGA design. Xilinx ABEL enables you to define logic in terms of text-based Boolean equations, truth tables, and state machine descriptions using the ABEL Hardware Description Language (HDL).

- Chapter 4, "XACT-Performance and Timing Analyzer Tutorial," shows you how to use XACT-Performance and the Timing Analyzer on an FPGA design in the Viewlogic environment. XACT-Performance consists of a set of library primitives that allow timing requirements to be placed on a schematic. The implementation tools use this timing information during mapping, placing, and routing of the design. The Timing Analyzer is a Windows-based tool that performs a static timing analysis of a routed FPGA design.

# **Conventions**

The following conventions are used in this manual's syntactical statements.

| Courier font regular | System messages or program files appear in regular Courier font.                                                           |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|

| Courier font bold    | Literal commands that you must enter in syntax statements are in bold Courier font.                                        |

| italic font          | Variables that you replace in syntax statements are in italic font.                                                        |

| [ ]                  | Square brackets denote optional items or parameters. However, in bus specifications, such as bus [7:0], they are required. |

| { }                  | Braces enclose a list of items from which you must choose one or more.                                                     |

| · .                  | A vertical ellipsis indicates material that has been omitted.                                                              |

|                      | A horizontal ellipsis indicates that the preceding can be repeated one or more times.                                      |

| 1                    | A vertical bar separates items in a list of choices.                                                                       |

| <b>↓</b>             | This symbol denotes a carriage return.                                                                                     |

# **Contents**

# **Chapter 1** PROcapture and PROsim Tutorial

| Introduction                           | 1-1  |

|----------------------------------------|------|

| Devices                                | 1-1  |

| Length                                 | 1-1  |

| Design Description                     | 1-2  |

| Getting Started                        | 1-3  |

| Required Software                      |      |

| Before Beginning the Tutorial          | 1-4  |

| Installing the PRO Series Tutorial     |      |

| Starting Xilinx PROflow                | 1-6  |

| Defining the Calc Project              | 1-8  |

| Creating the Calc Project              | 1-8  |

| Obtaining Design Status                | 1-12 |

| Selecting the CALC.1 Schematic         |      |

| Navigating in PROcapture               | 1-17 |

| Mouse Buttons                          | 1-17 |

| Function Keys                          | 1-17 |

| Starting PROcapture                    | 1-18 |

| Changing the PROcapture Window Colors  | 1-20 |

| Moving Around the Screen               | 1-22 |

|                                        |      |

| Zooming                                | 1-23 |

| Making Icons of Schematics and Symbols | 1-27 |

| PROcapture Command Summary             |      |

| Creating Symbols                       | 1-31 |

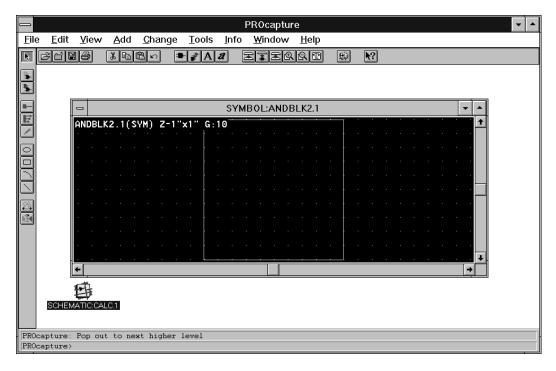

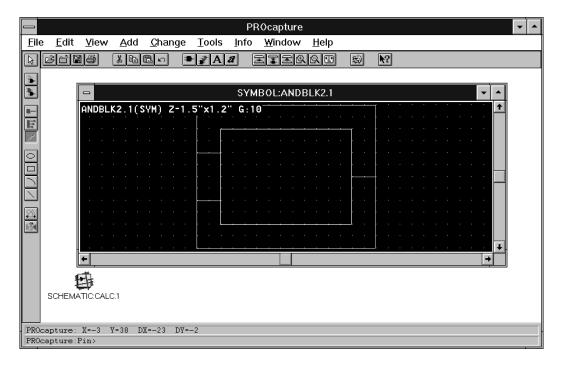

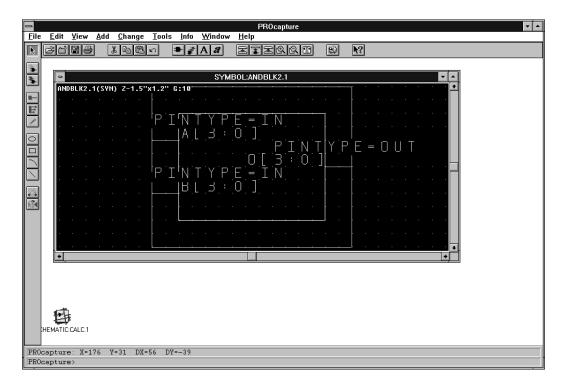

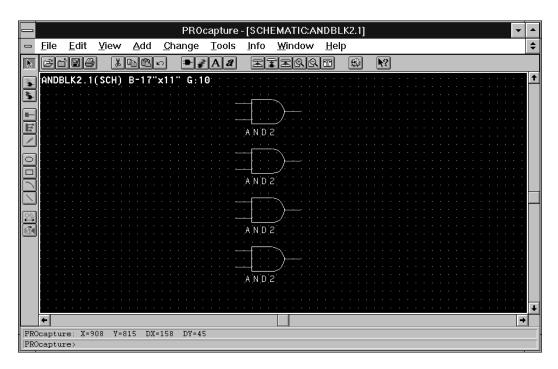

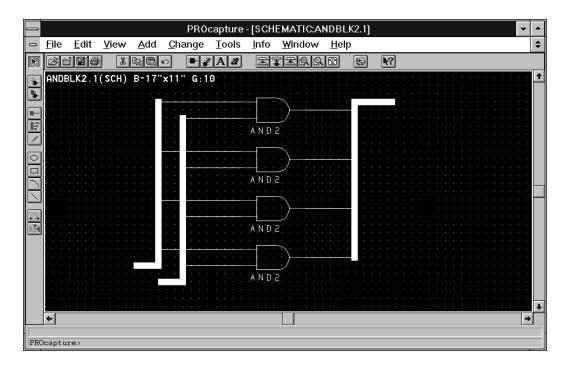

| Creating the ANDBLK2 Symbol            | 1-31 |

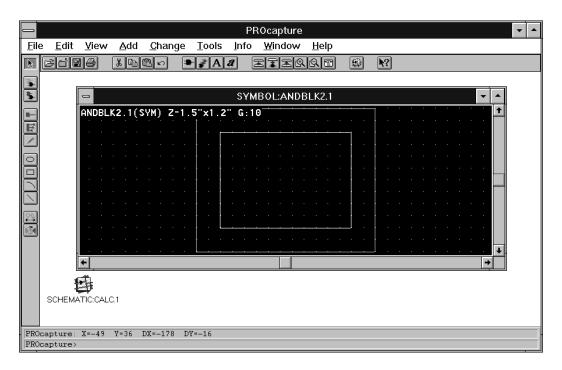

| Changing the Size of the Symbol        | 1-34 |

|                                        |      |

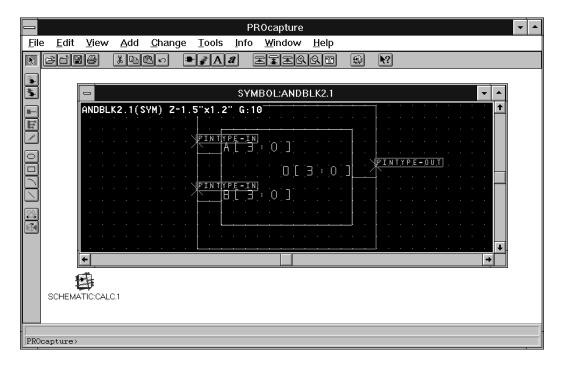

| Adding Pins                            | 1-36 |

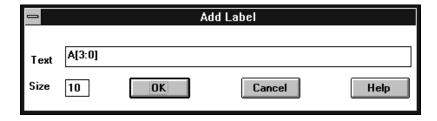

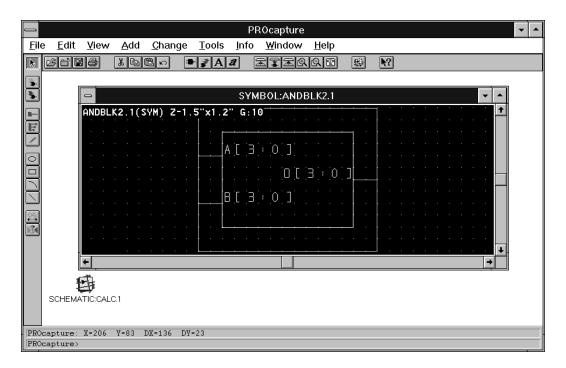

| Adding Pin Labels                      | 1-37 |

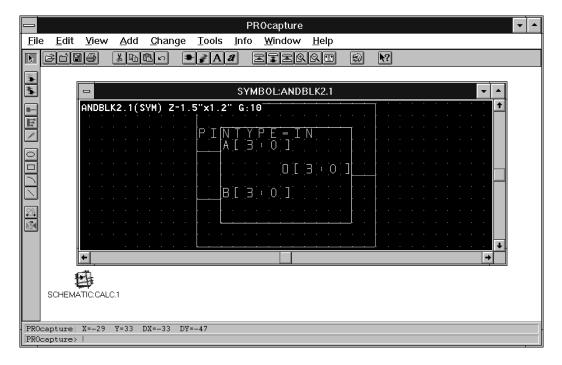

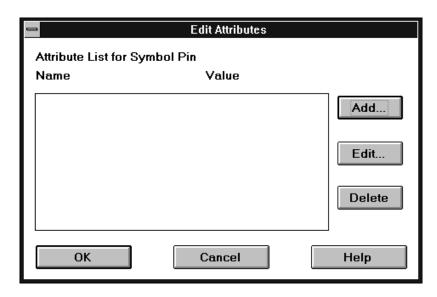

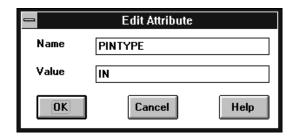

| Adding Pin Attributes                  |      |

| Using the Add Object Attribute Command |      |

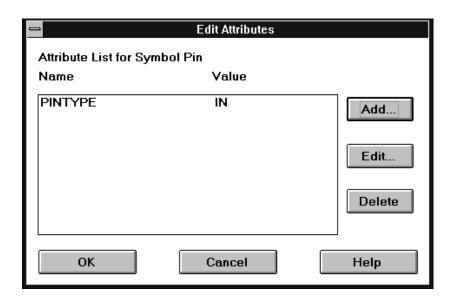

| Editing Pin Attributes                 |      |

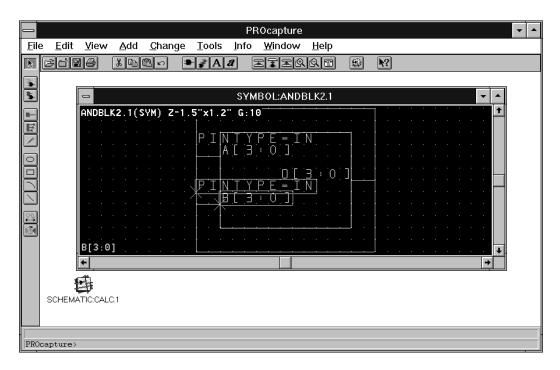

| Adding Other PINTYPE Attributes        | 1-44 |

| Changing Attribute Size                    | 1-45  |

|--------------------------------------------|-------|

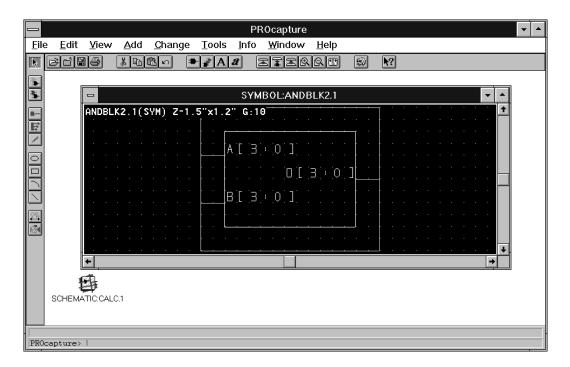

| Controlling Attribute Visibility           | 1-47  |

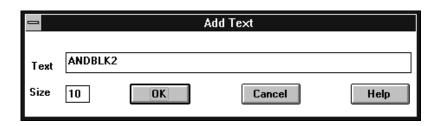

| Adding Symbol Text                         | 1-48  |

| Changing Symbol Text Size                  | 1-50  |

| Moving Text and Objects                    | 1-50  |

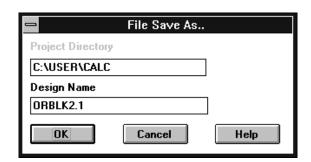

| Saving the ANDBLK2 Symbol                  | 1-52  |

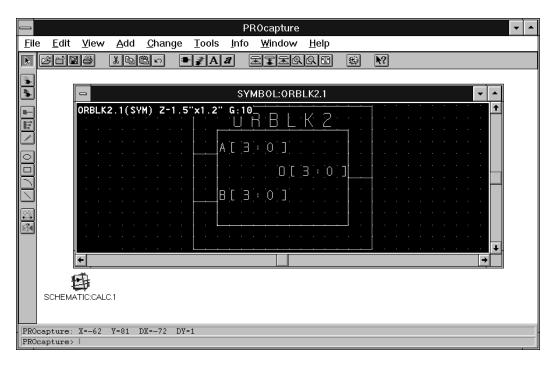

| Creating the ORBLK2 Symbol                 | 1-53  |

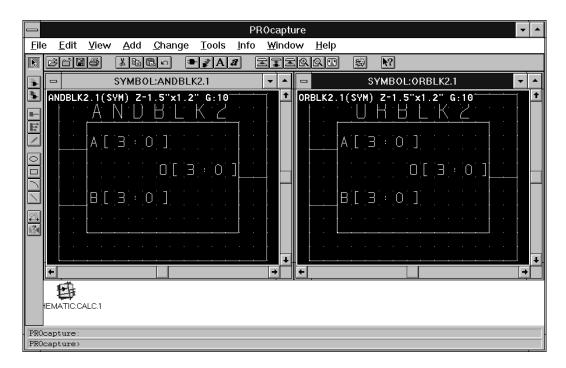

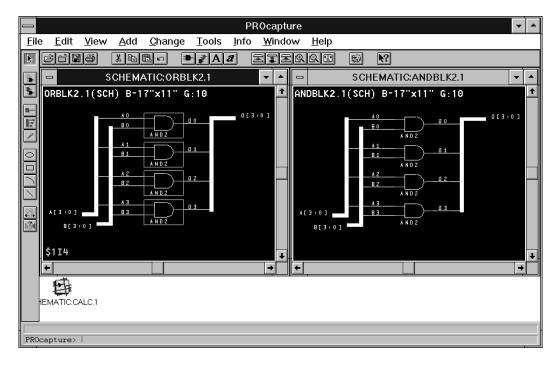

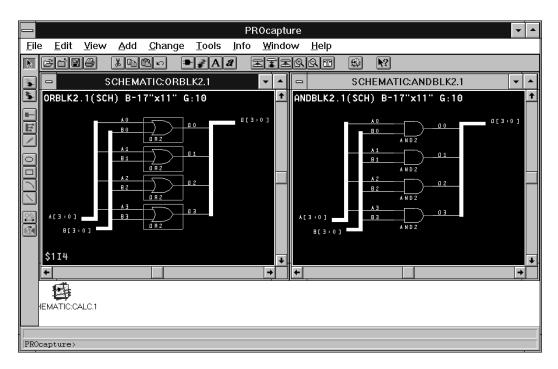

| Viewing Symbols Simultaneously             |       |

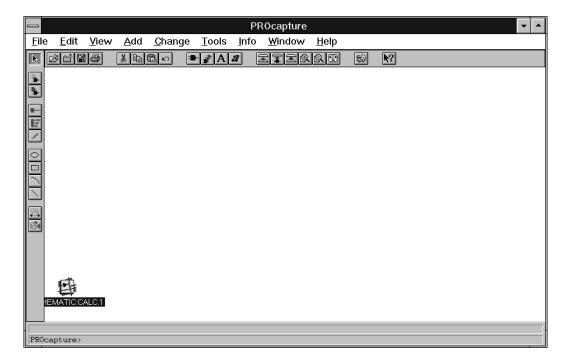

| Closing Symbol Windows                     |       |

| Creating Schematics                        |       |

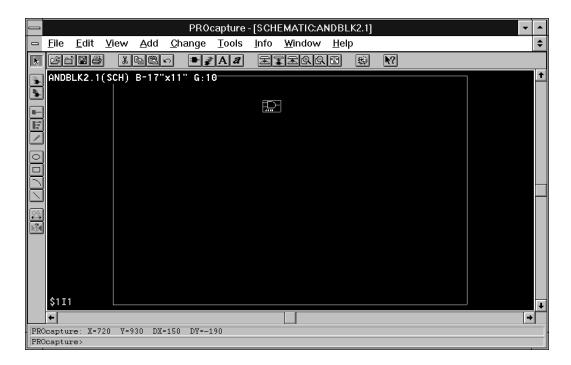

| Opening a Schematic Sheet                  |       |

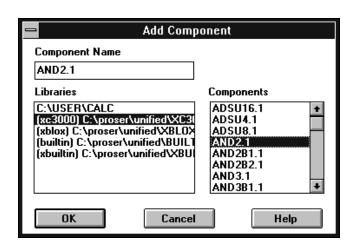

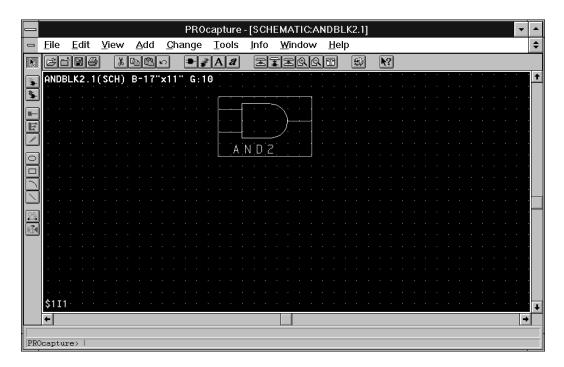

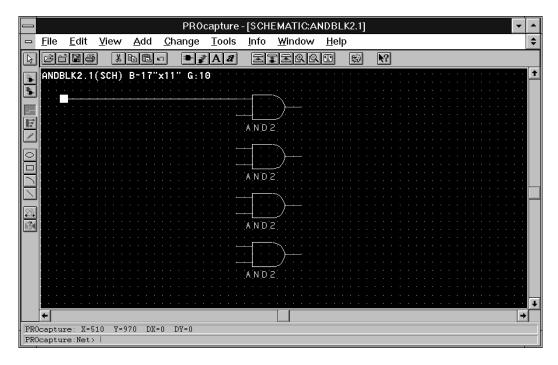

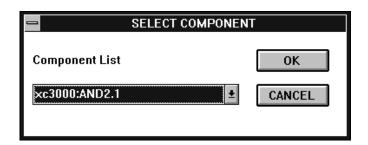

| Adding Components                          |       |

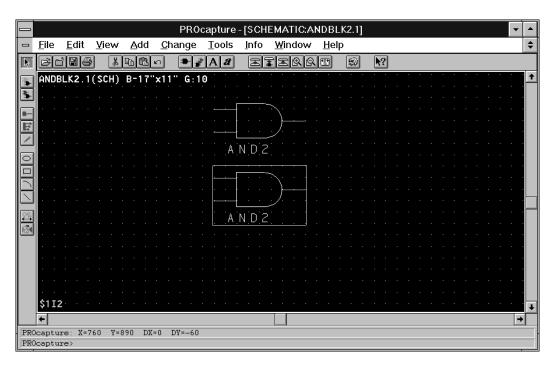

| Copying Components                         |       |

| Moving Components                          |       |

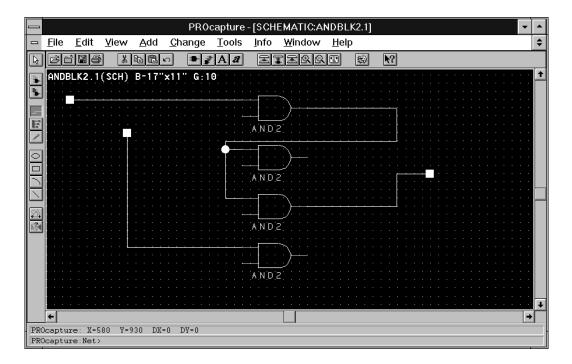

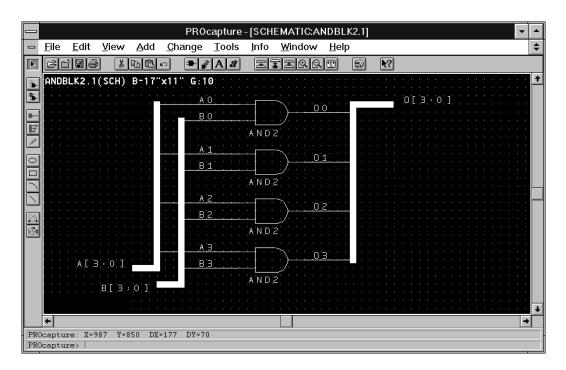

| Adding Nets                                |       |

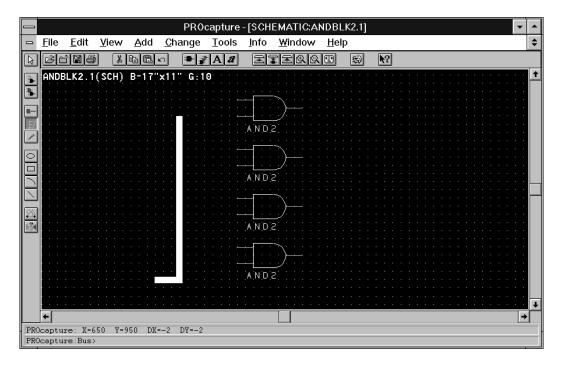

| Adding Buses                               |       |

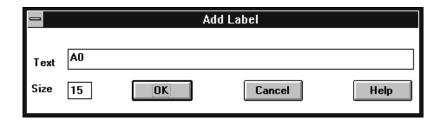

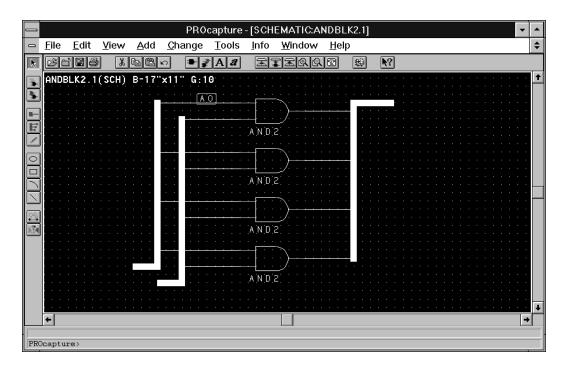

| Adding Labels                              |       |

| Saving the Schematic                       |       |

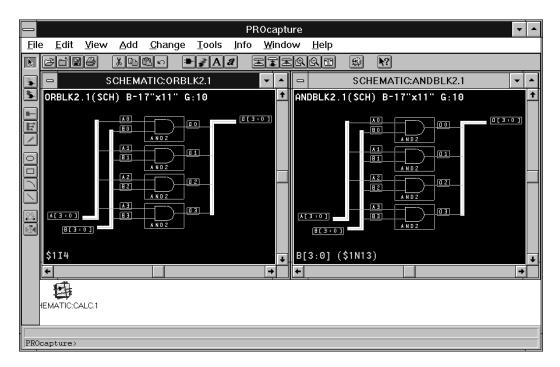

| Creating the ORBLK2 Schematic              | 1-78  |

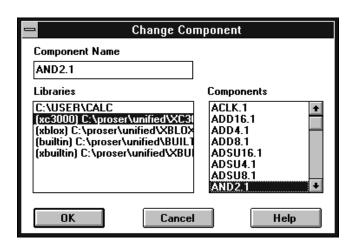

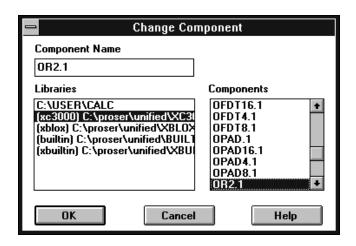

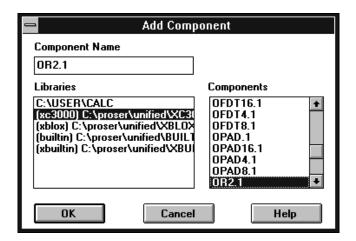

| Changing AND2 Components to OR2 Components | 1-82  |

| Saving the ORBLK2 Schematic                |       |

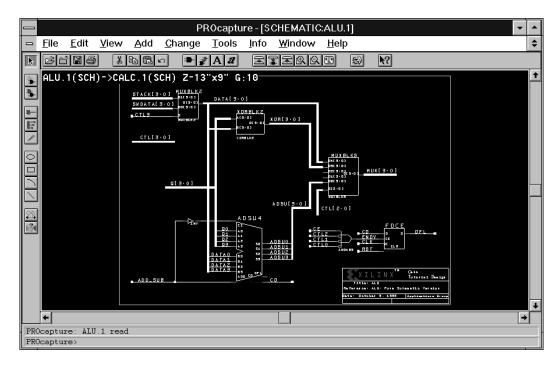

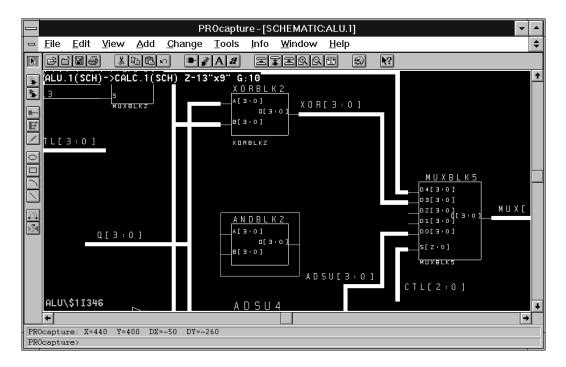

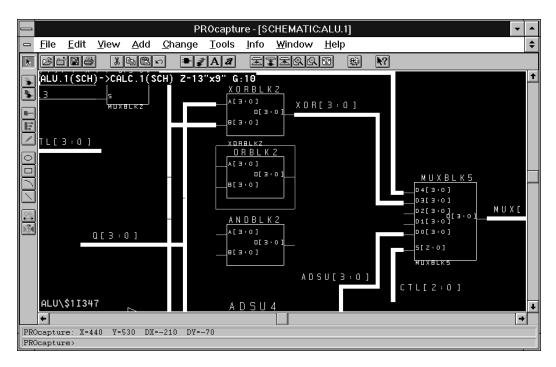

| Completing the ALU Schematic               | 1-87  |

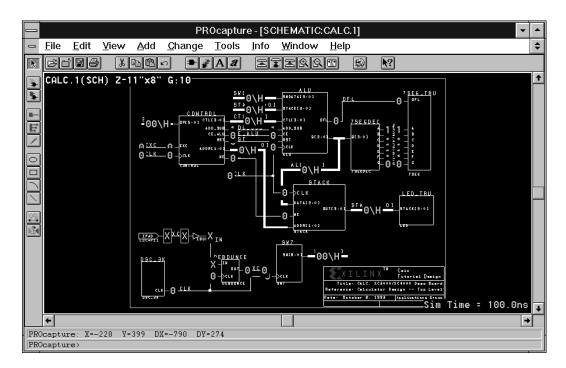

| Making the CALC.1 Schematic Visible        |       |

| Pushing into the ALU Symbol's Schematic    | 1-89  |

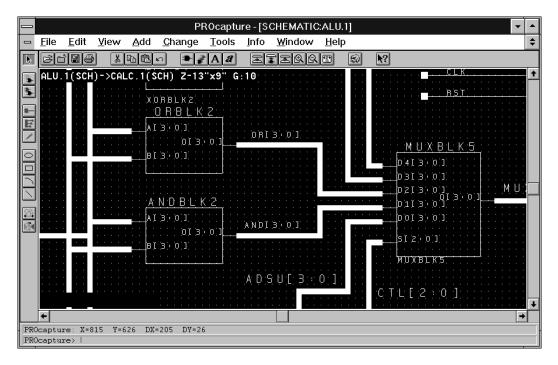

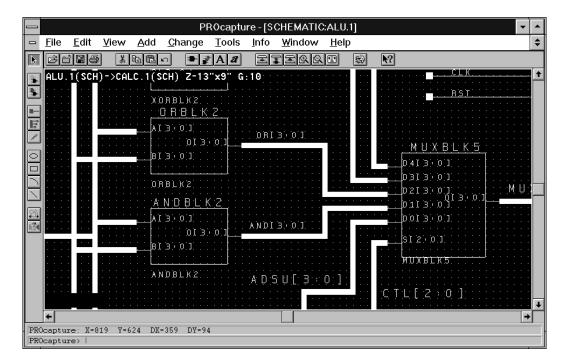

| Placing the ANDBLK2 and ORBLK2 Symbols     | 1-90  |

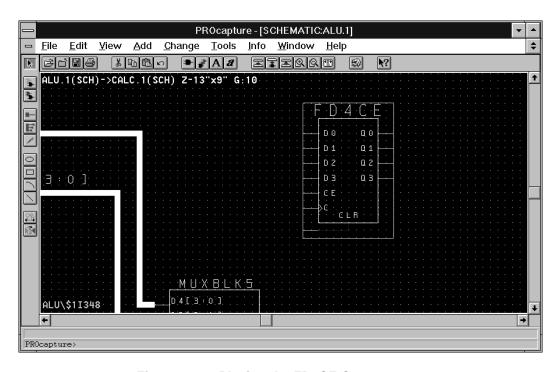

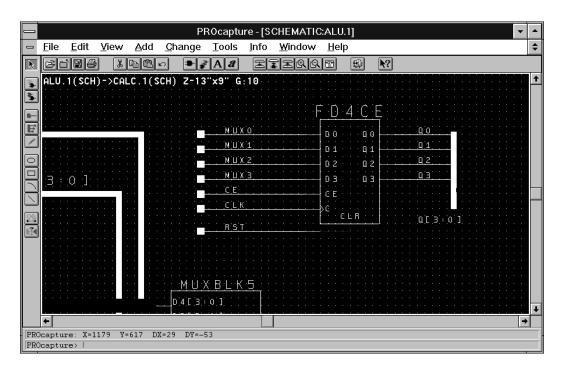

| Placing the FD4CE Component                | 1-94  |

| Adding Nets, Buses, and Labels             | 1-96  |

| Adding Symbol Labels                       | 1-97  |

| Saving the ALU.1 Schematic                 |       |

| Viewing the OSC_3K or OSC_7K Schematic     | 1-100 |

| Exchanging Components                      | 1-103 |

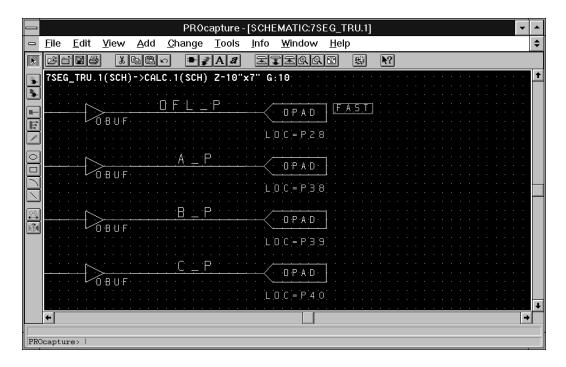

| Controlling Layout from the Schematic      | 1-104 |

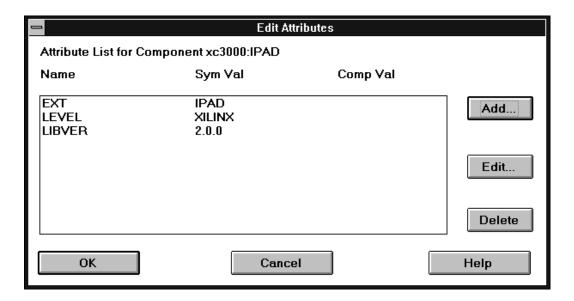

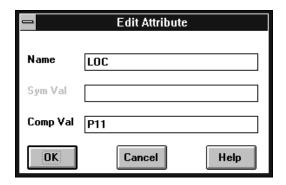

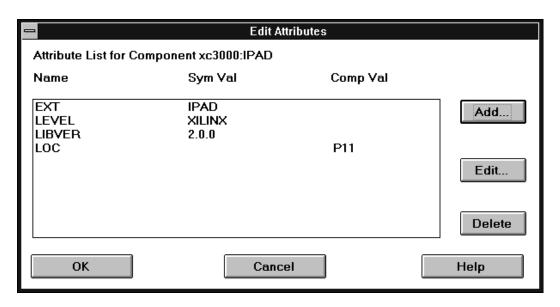

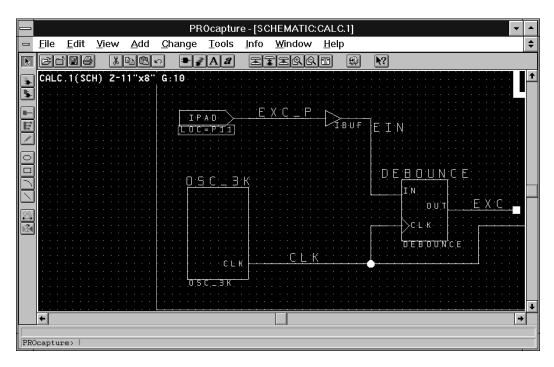

| Adding the LOC Attribute                   | 1-105 |

| Adding Flags to Nets                       | 1-108 |

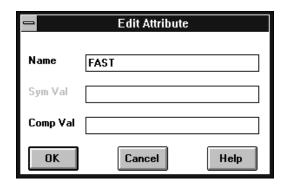

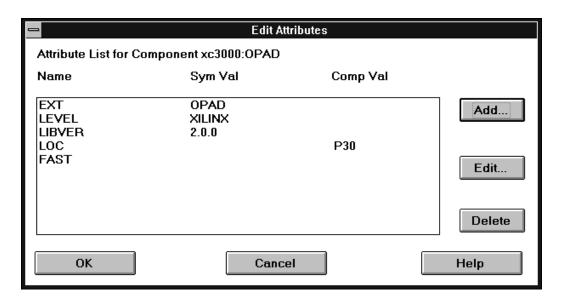

| Adding the FAST and SLOW Attributes        | 1-111 |

| Using IOB Flip-Flops                       | 1-114 |

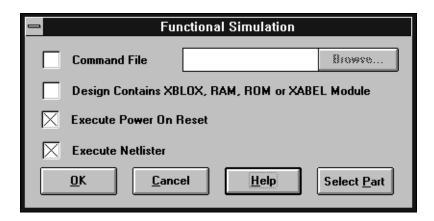

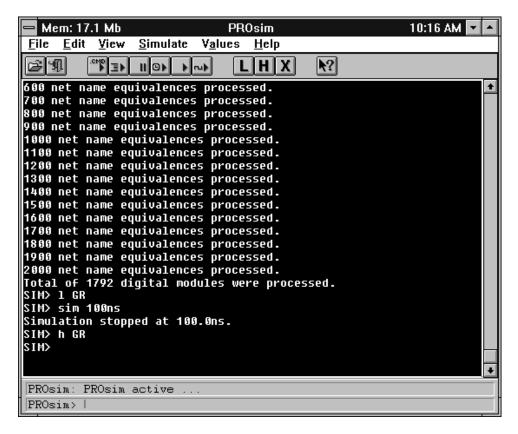

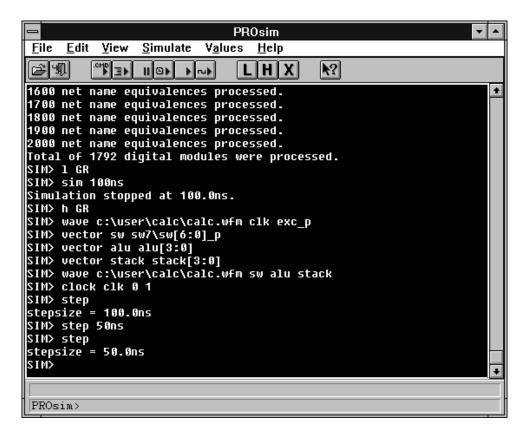

| Functional Simulation                      |       |

| Creating the Simulation Network            |       |

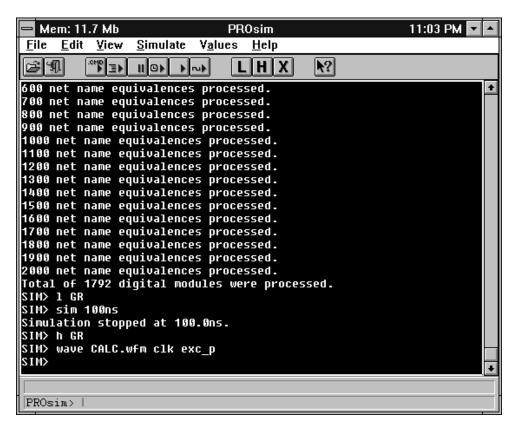

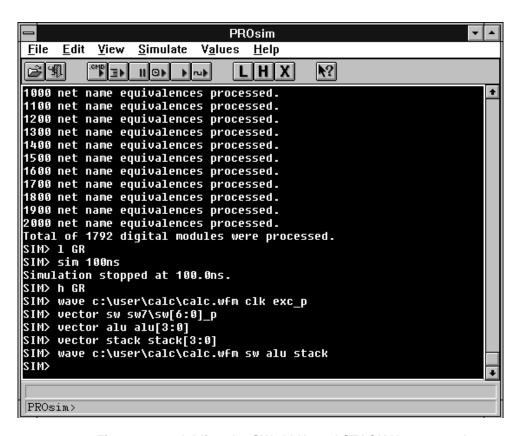

| Adding Signals and Vectors to the Waveform |       |

| Adding Signals to the Waveform             |       |

| Adding Vectors to the Waveform             |       |

| Defining the Design Inputs                           | 1-123 |

|------------------------------------------------------|-------|

| Defining a Clock                                     |       |

| Defining Input Values                                |       |

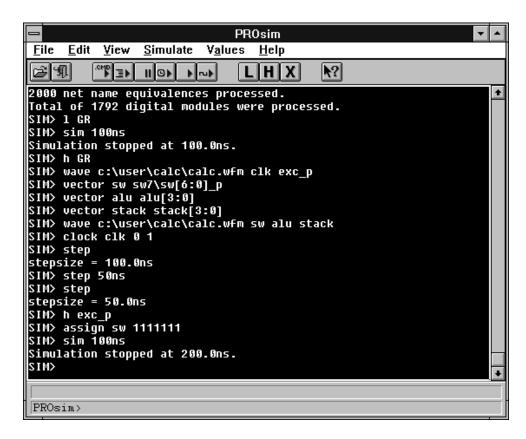

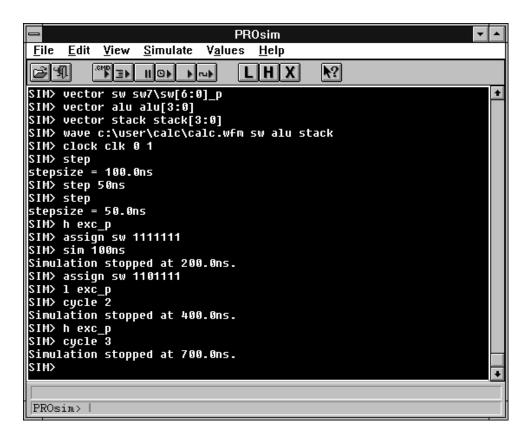

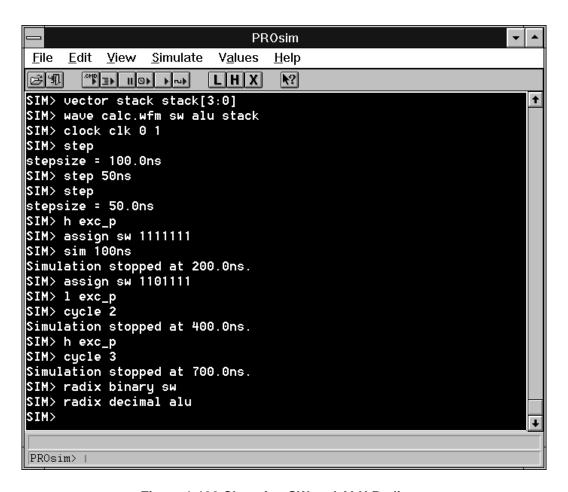

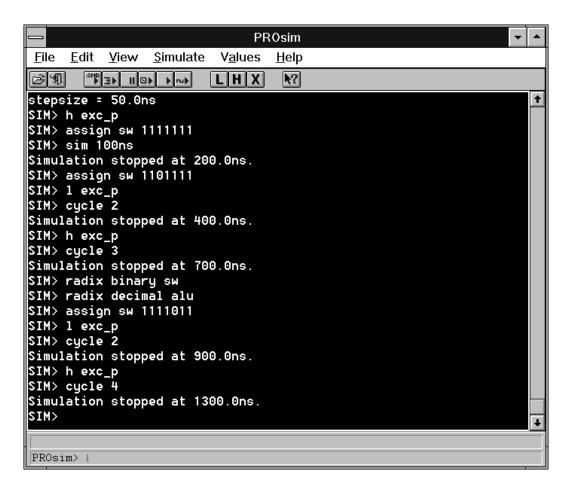

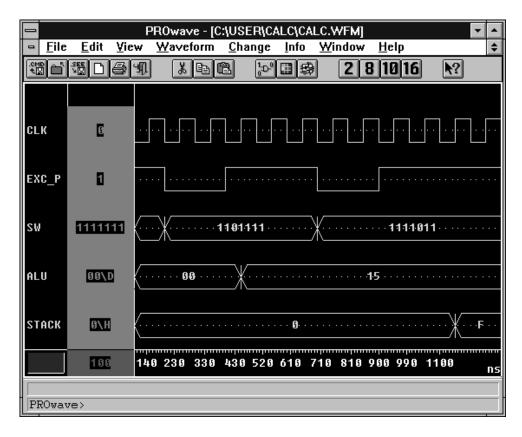

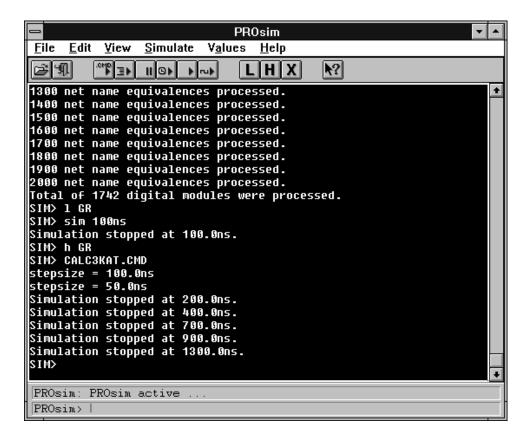

| Simulating the Design Inputs                         | 1-125 |

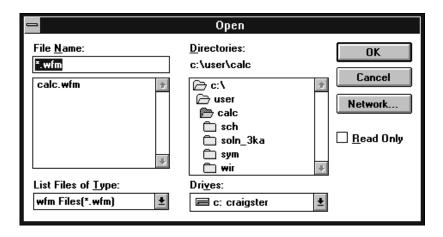

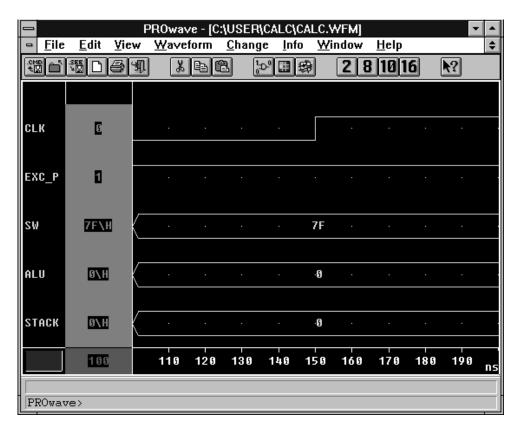

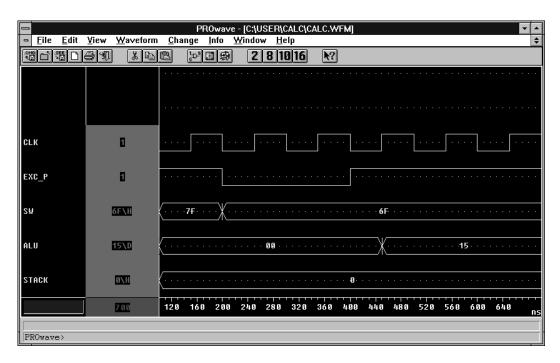

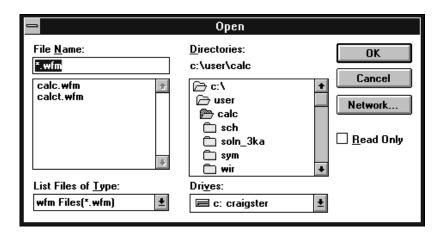

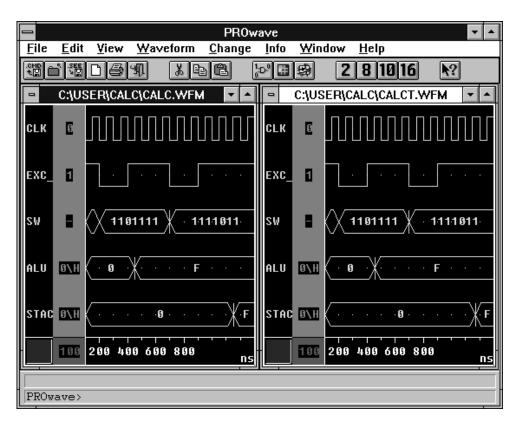

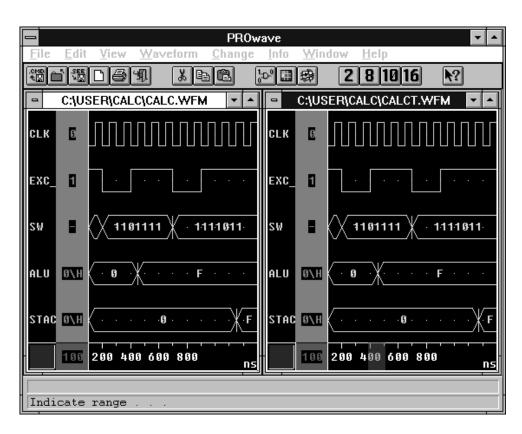

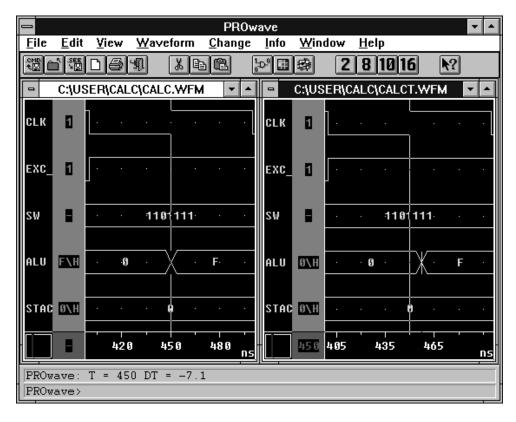

| Invoking PROwave                                     | 1-127 |

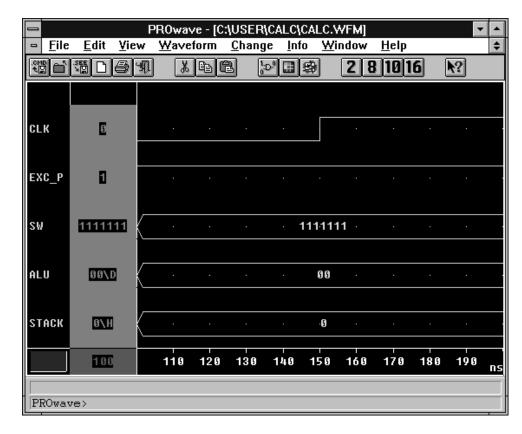

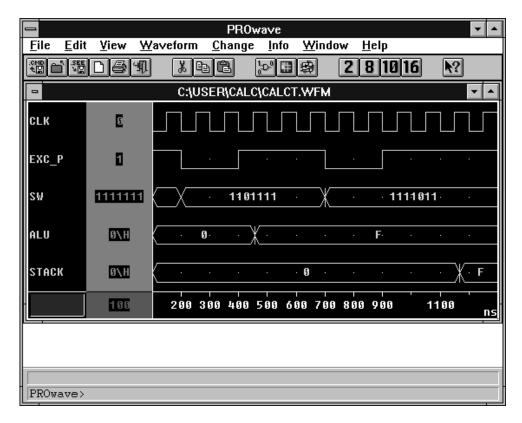

| Changing the Display Radix                           | 1-129 |

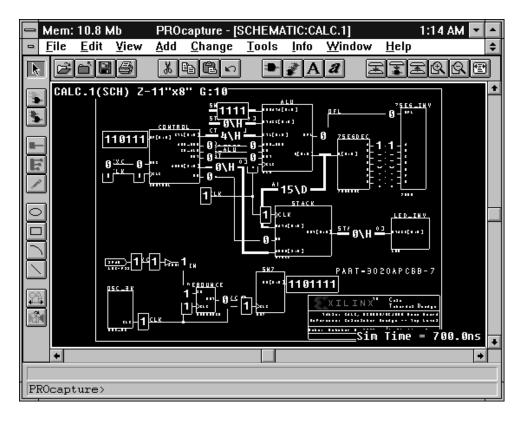

| Simulating the Calc Design                           | 1-131 |

| Loading 1111 to the ALU Register                     | 1-132 |

| Changing the Radices for PROcapture Display          |       |

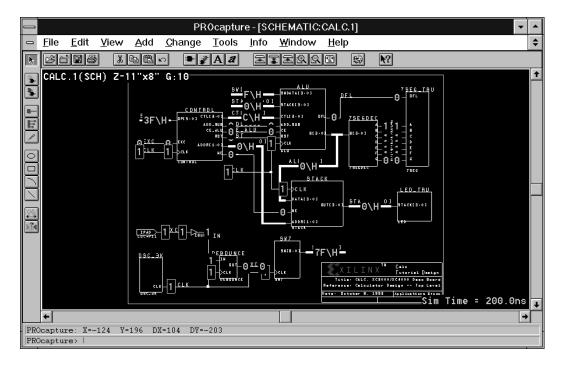

| Pushing 1111 to the STACK Register                   |       |

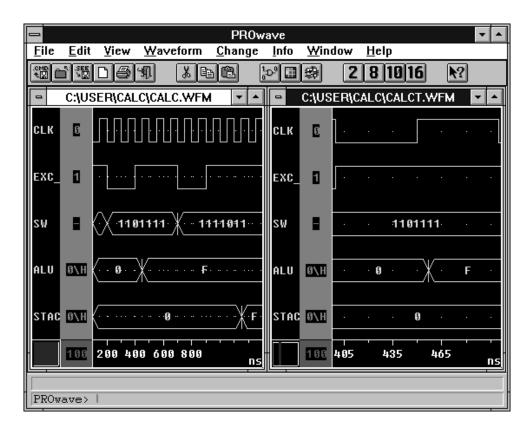

| Viewing the Waveforms                                |       |

| Re-Creating Previous Simulation                      |       |

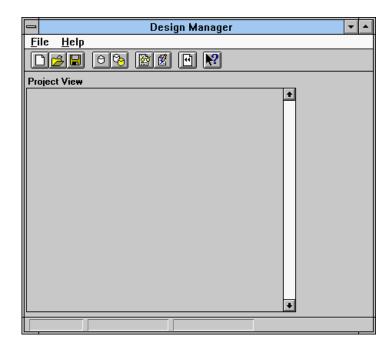

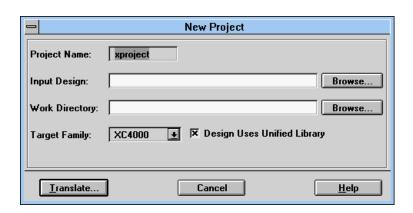

| Implementing the Calc Design                         |       |

| Invoking the Design Manager                          |       |

| Creating the Calc Implementation Project and Its     |       |

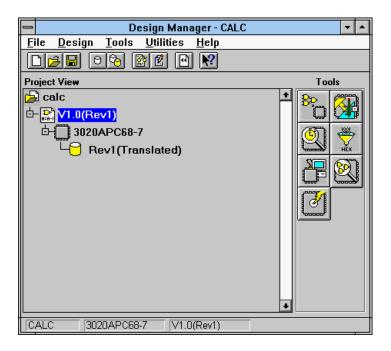

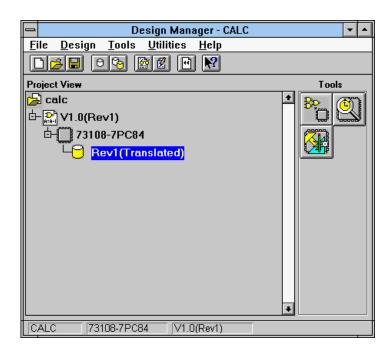

| Initial Translation                                  | 1-142 |

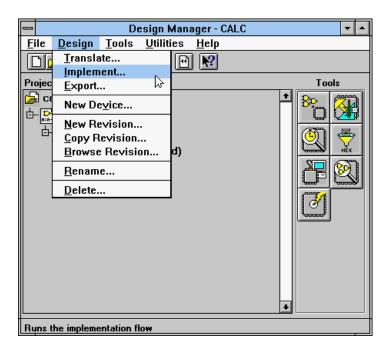

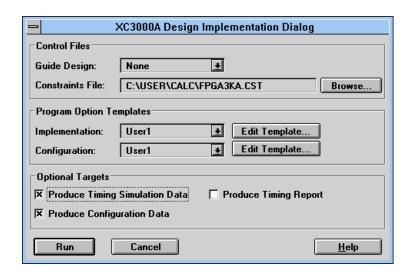

| Implementing the FPGA Design                         |       |

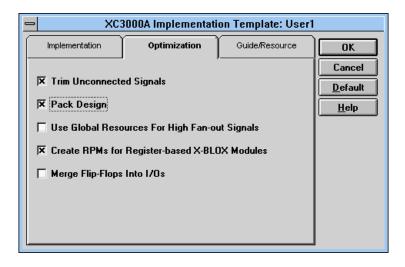

| Setting General FPGA Options                         |       |

| Setting Advanced FPGA Options                        |       |

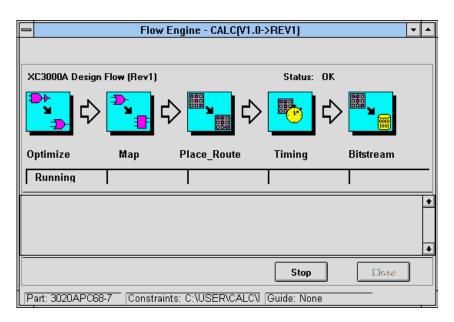

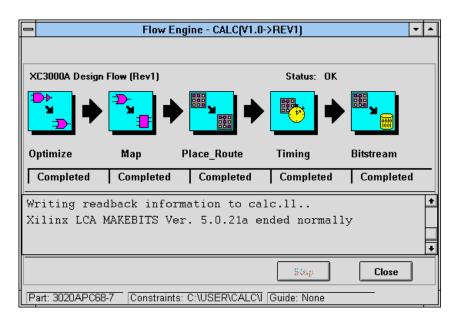

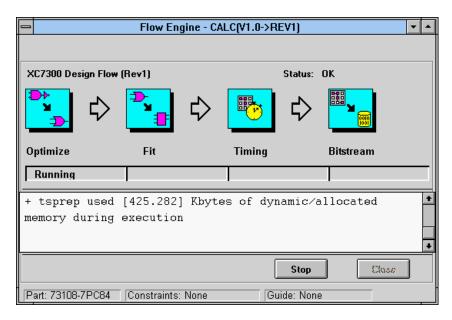

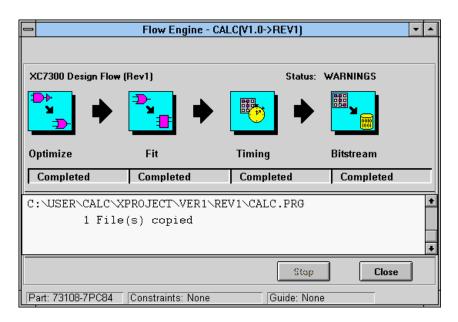

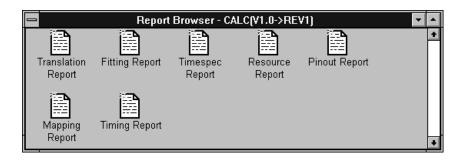

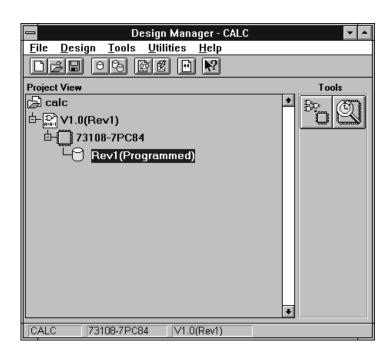

| Invoking the Flow Engine                             |       |

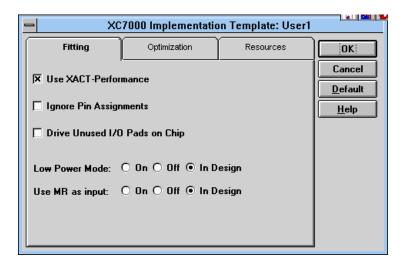

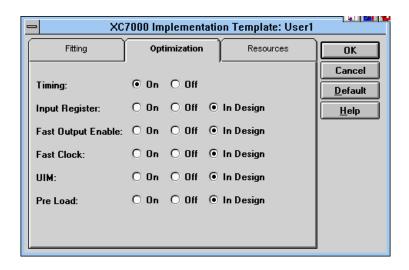

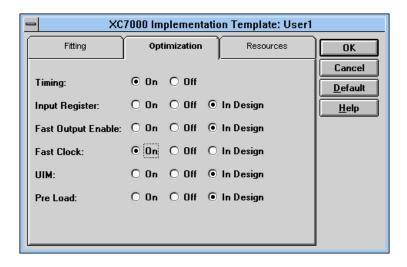

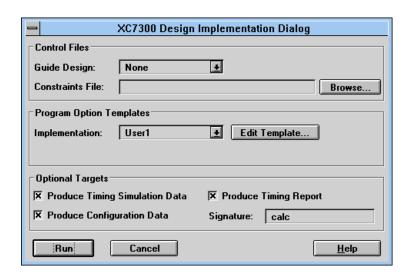

| Implementing the EPLD Design                         |       |

| Setting Advanced EPLD Options                        |       |

| Invoking the Flow Engine                             |       |

| Timing Simulation                                    |       |

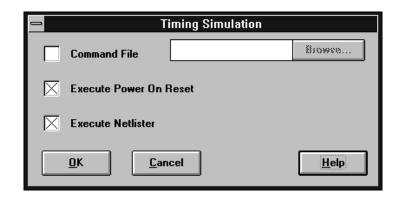

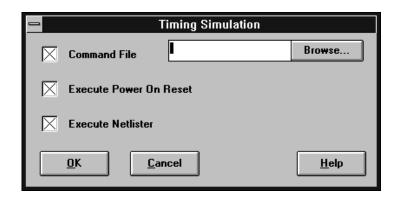

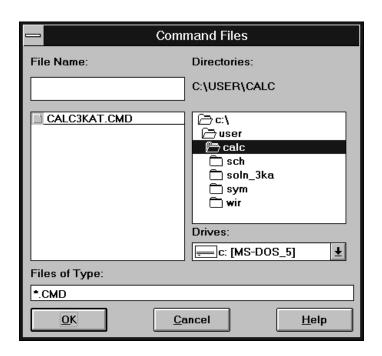

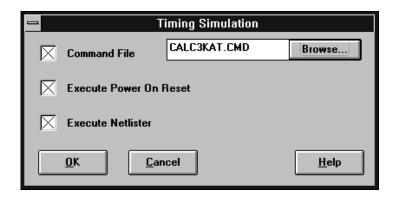

| Creating the Simulation Network File                 |       |

| Invoking PROwave                                     |       |

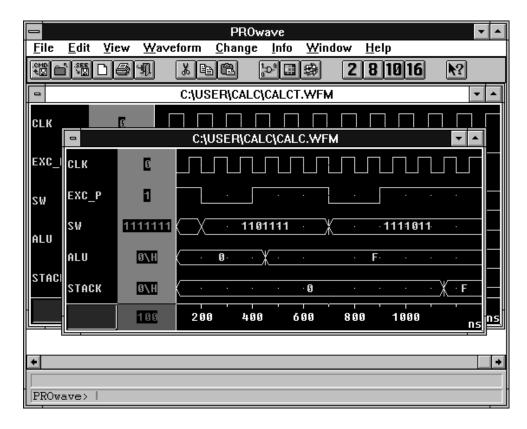

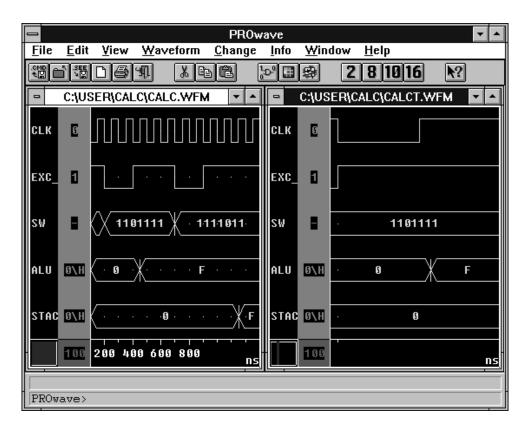

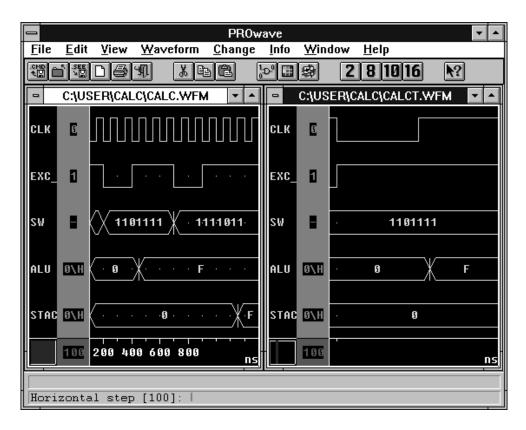

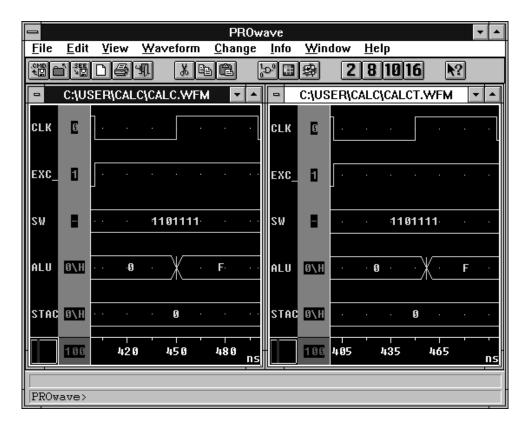

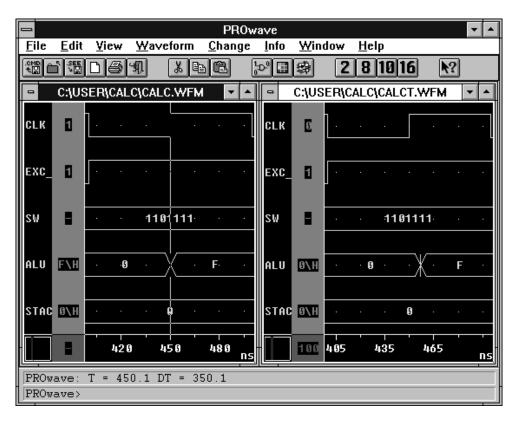

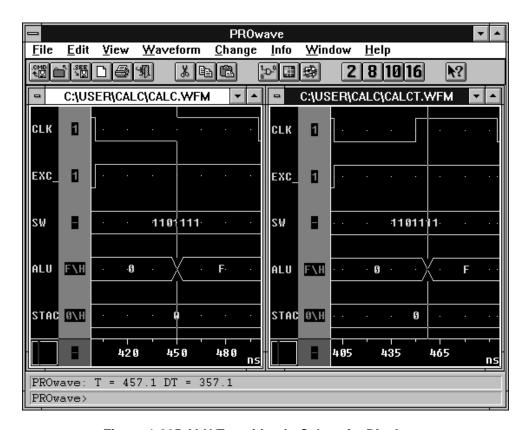

| Comparing the Functional and Timing Simulation Files |       |

| Zooming the Waveform Files                           |       |

| Obtaining a Transition Time                          |       |

| In the Calc.wfm File                                 |       |

| In the Calct.wfm File                                |       |

| Obtaining a Delta Time                               |       |

| Downloading an FPGA Design                           |       |

| Using a Demonstration Board                          |       |

| Connecting the Cable for Download                    |       |

| FPGA Demonstration Board                             |       |

| XC3000A Demonstration Board                          |       |

| Downloading the Bitstream                            |       |

| Testing the Design                                   |       |

| resuring the Design                                  | 1-190 |

Viewlogic Tutorials vii

| Chapter 2 | X-BLOX Tutorial                            |      |

|-----------|--------------------------------------------|------|

|           | Before Beginning the Tutorial              | 2-1  |

|           | Required Software                          |      |

|           | Preparing the Design                       | 2-2  |

|           | Modifying the Design                       | 2-3  |

|           | Adding X-BLOX Modules to CALC              | 2-3  |

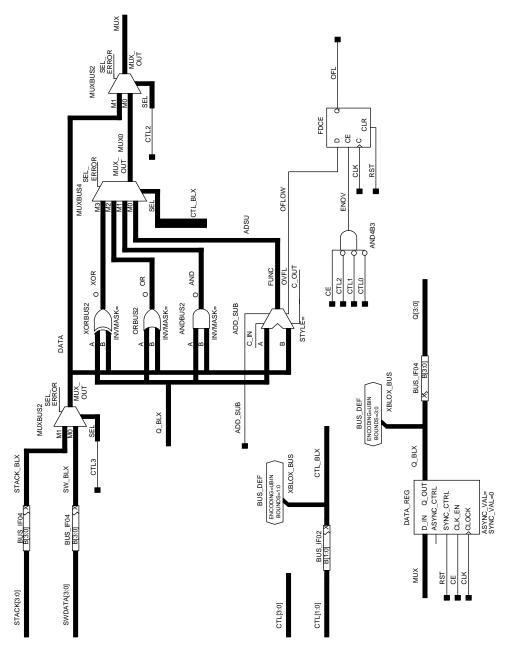

|           | Viewing the ALU_BLOX Schematic             | 2-3  |

|           | Completing the ALU_BLOX Schematic          | 2-5  |

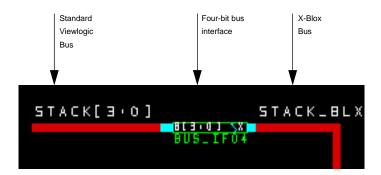

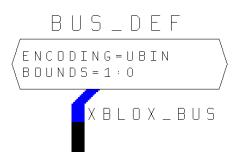

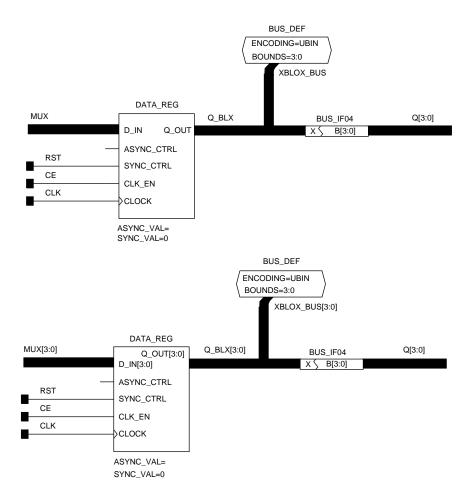

|           | Understanding X-BLOX Buses                 | 2-5  |

|           | Using BUS_DEF Symbols                      |      |

|           | Completing the Bus Definition              |      |

|           | Saving Your Changes                        |      |

|           | X-BLOX Symbol Library                      |      |

|           | X-BLOX Symbol Examples                     |      |

|           | X-BLOX Schematics                          |      |

|           | Functional Simulation                      |      |

|           | Creating the Simulation Schematic          |      |

|           | Examining XSimMake Output                  |      |

|           | Performing a Functional Simulation         |      |

|           | Implementing the Calc Design               |      |

|           | Translating the Netlist                    |      |

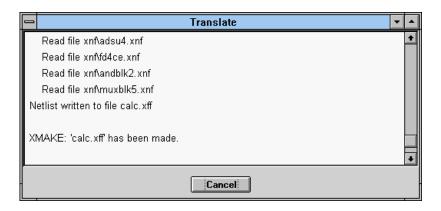

|           | Examining XMake Netlist Translation Output |      |

|           | Creating a Routed Design                   |      |

|           | Examining the Flow Engine History File     |      |

|           | Timing Simulation                          |      |

|           | Creating the Simulation Network            |      |

|           | Examining XSimMake Output                  |      |

|           | Performing a Timing Simulation             |      |

|           | Verifying CALC on the Demonstration Board  |      |

|           | Further Reading                            | 2-23 |

| Chapter 3 | Xilinx ABEL Tutorial                       |      |

|           | Before Beginning the Tutorial              | 3-1  |

|           | Required Software                          |      |

|           | Preparing the Design                       |      |

|           | Viewing Stat_abl.abl                       |      |

|           | Simulating Within Xilinx ABEL              |      |

|           | Compiling STAT_ABL.ABL                     |      |

|           | Including STAT_ABL in the CALC Design      |      |

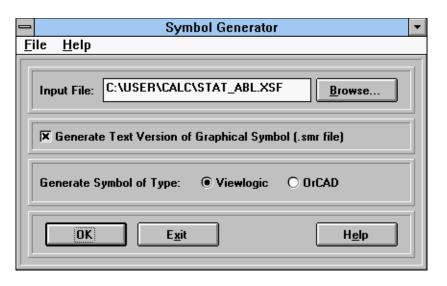

|           | Creating a Symbol for STAT_ABL             |      |

|           |                                            |      |

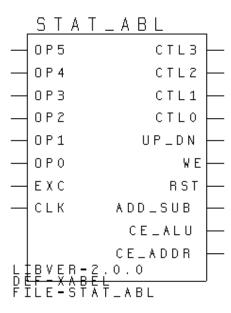

| Viewing the STAT_ABL Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-14                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Viewing the STAT_ABL Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-14                                                                             |

| Verifying the Symbol Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-15                                                                             |

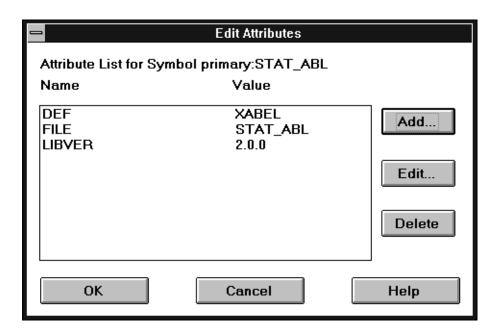

| Verifying the Symbol Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Functional Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| Creating the Simulation Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-18                                                                             |

| Examining XSimMake Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Performing a Functional Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Implementing the CALC Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Translating the Netlist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Examining XMake Netlist Translation Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Creating a Routed Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Examining the Flow Engine History File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| Timing Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Creating the Simulation Netlist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Examining XSimMake Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Performing a Timing Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Verifying CALC on the Demonstration Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Further Reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| Chapter 4 XACT-Performance and Timing Analyzer Tuto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oriai                                                                            |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Before Beginning the Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-2                                                                              |

| Before Beginning the Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2<br>4-2                                                                       |

| Before Beginning the Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2<br>4-2<br>4-2                                                                |

| Before Beginning the Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2<br>4-2<br>4-2<br>4-3                                                         |

| Before Beginning the Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-2<br>4-2<br>4-3<br>4-4                                                         |

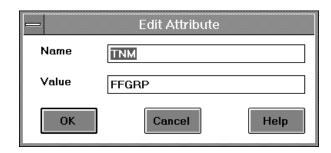

| Before Beginning the Tutorial  Required Software  Preparing the Design  Understanding XACT-Performance  Grouping Symbols with TNM Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-2<br>4-2<br>4-3<br>4-4                                                         |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops Grouping Symbols by Predefined Groups Simplifying Symbol Grouping                                                                                                                                                                                                                                                                         | 4-2<br>4-2<br>4-2<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5                      |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops Grouping Symbols by Predefined Groups Simplifying Symbol Grouping                                                                                                                                                                                                                                                                         | 4-2<br>4-2<br>4-2<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5                      |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops Grouping Symbols by Predefined Groups                                                                                                                                                                                                                                                                                                     | 4-2<br>4-2<br>4-2<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5<br>4-5<br>4-6        |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops. Grouping Symbols by Predefined Groups Simplifying Symbol Grouping. Combining Groups with the TIMEGRP Symbol                                                                                                                                                                                                                              | 4-2<br>4-2<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5<br>4-6<br>4-6               |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops. Grouping Symbols by Predefined Groups Simplifying Symbol Grouping. Combining Groups with the TIMEGRP Symbol Joining Two or More Groups into One                                                                                                                                                                                          | 4-2<br>4-2<br>4-3<br>4-3<br>4-4<br>4-4<br>4-5<br>4-5<br>4-5<br>4-6<br>4-6        |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops Grouping Symbols by Predefined Groups Simplifying Symbol Grouping. Combining Groups with the TIMEGRP Symbol Joining Two or More Groups into One Using the EXCEPT Statement                                                                                                                                                                | 4-2<br>4-2<br>4-3<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5<br>4-5<br>4-6<br>4-6<br>4-7 |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops Grouping Symbols by Predefined Groups Simplifying Symbol Grouping. Combining Groups with the TIMEGRP Symbol Joining Two or More Groups into One Using the EXCEPT Statement Triggering on RISING or FALLING Clock Edges                                                                                                                    | 4-2 4-2 4-2 4-3 4-4 4-4 4-4 4-5 4-5 4-6 4-6 4-7                                  |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops Grouping Symbols by Predefined Groups Simplifying Symbol Grouping. Combining Groups with the TIMEGRP Symbol Joining Two or More Groups into One Using the EXCEPT Statement. Triggering on RISING or FALLING Clock Edges. Forming Groups by Output Net Name                                                                                | 4-2                                                                              |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops. Grouping Symbols by Predefined Groups Simplifying Symbol Grouping. Combining Groups with the TIMEGRP Symbol Joining Two or More Groups into One Using the EXCEPT Statement. Triggering on RISING or FALLING Clock Edges. Forming Groups by Output Net Name Attaching Timing Specifications with the TIMESPEC Statement.                  | 4-2                                                                              |

| Before Beginning the Tutorial Required Software Preparing the Design Understanding XACT-Performance Grouping Symbols with TNM Attributes TNMs on Logic Primitives TNMs on Higher-Level Macro Symbols TNMs on Nets to Tag Flip-Flops Grouping Symbols by Predefined Groups Simplifying Symbol Grouping. Combining Groups with the TIMEGRP Symbol Joining Two or More Groups into One Using the EXCEPT Statement Triggering on RISING or FALLING Clock Edges Forming Groups by Output Net Name Attaching Timing Specifications with the TIMESPEC Symbol To Use XACT-Performance | 4-2                                                                              |

| Adding Timing Constraints to Specific Paths     | 4-14 |

|-------------------------------------------------|------|

| Defining TNM Groups                             |      |

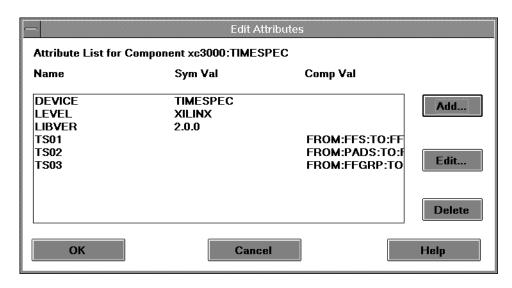

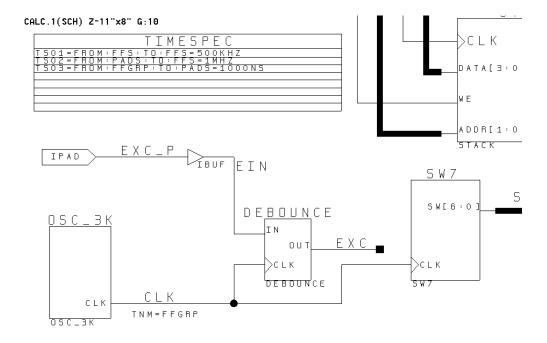

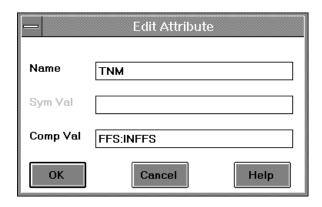

| Defining the INFFS Group                        | 4-14 |

| Defining the STACKER Group (XC4000 Family Only) | 4-15 |

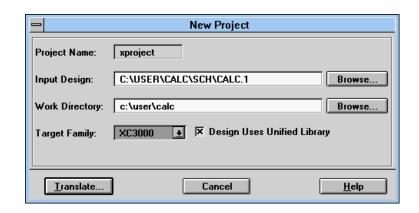

| Defining the STACKER Group (XC3000A Only)       | 4-16 |

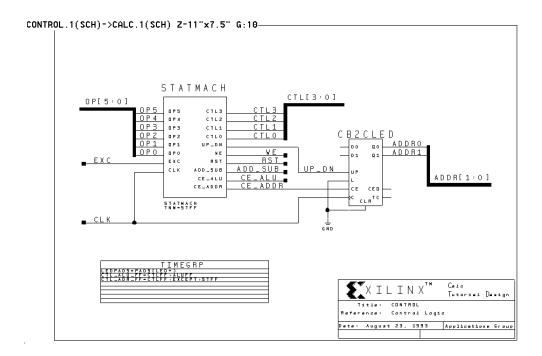

| Defining the ALUFF Group                        | 4-17 |

| Defining the CTLFF Group                        | 4-17 |

| Defining the STFF Group                         | 4-18 |

| Grouping Using TIMEGRP                          | 4-18 |

| Specifying TIMESPEC Constraints                 | 4-20 |

| Making a Final Check                            | 4-21 |

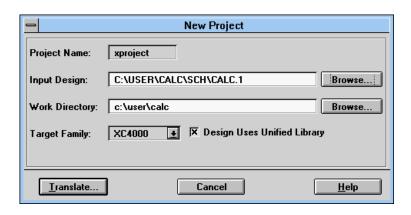

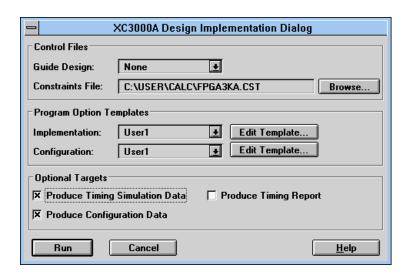

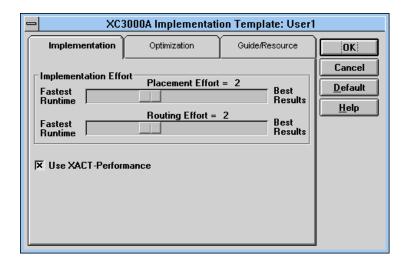

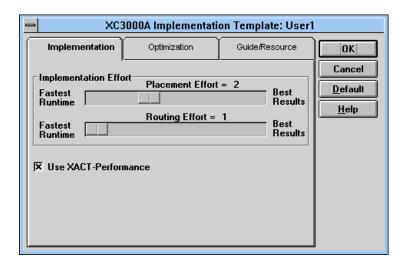

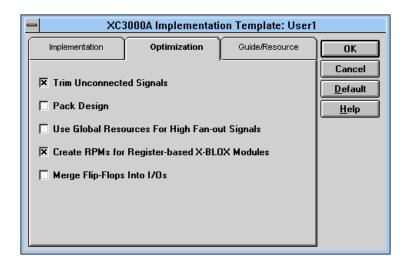

| Implementing the Calc Design                    | 4-23 |

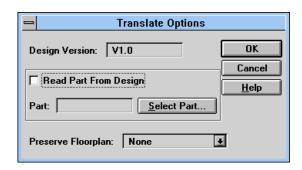

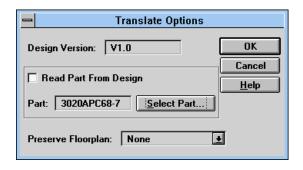

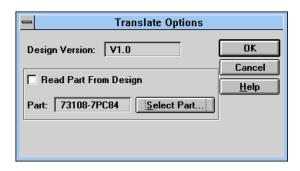

| Translating the Netlist                         | 4-24 |

| Examining Translation Output                    | 4-24 |

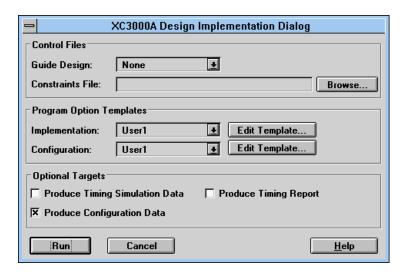

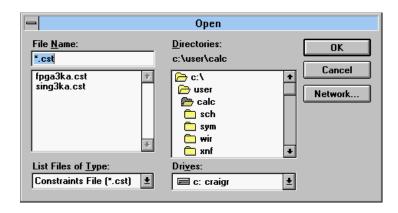

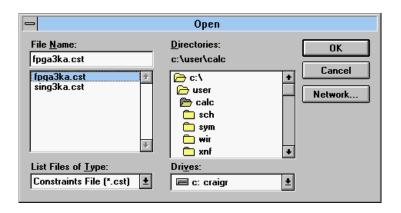

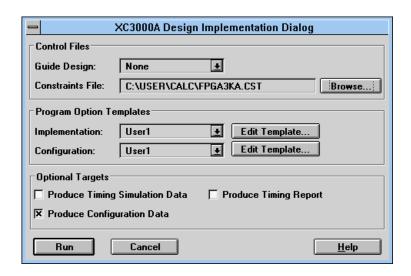

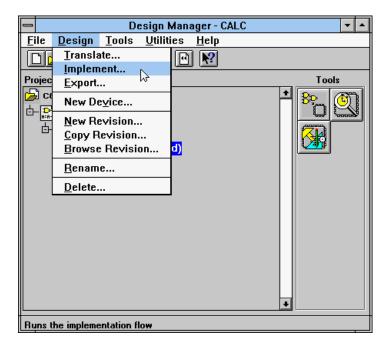

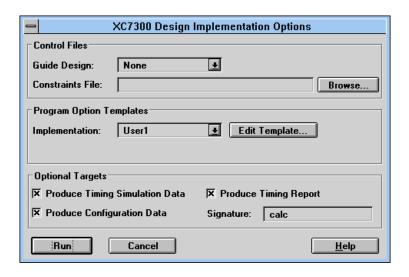

| Creating a Routed Design                        | 4-25 |

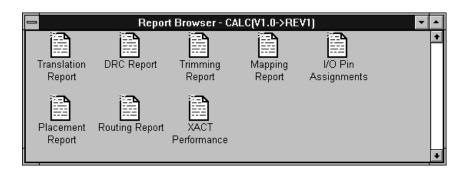

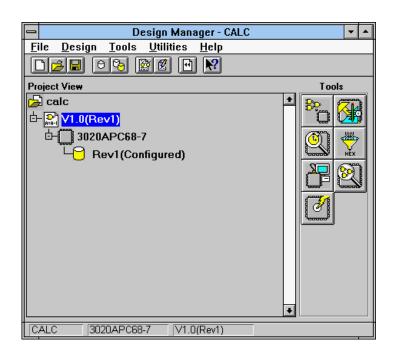

| Examining the Implementation Output             | 4-26 |

| Using the Timing Analyzer                       | 4-27 |

| Analyzing the Calc Design                       | 4-29 |

| Invoking the Timing Analyzer                    | 4-29 |

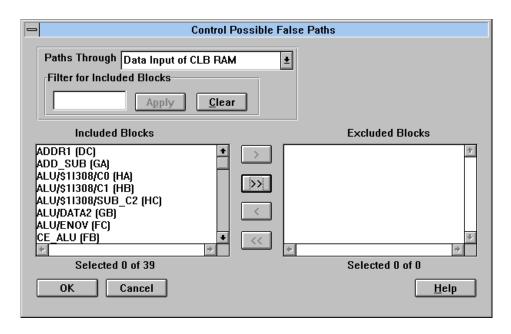

| Disabling False Paths                           | 4-29 |

| Resetting Path Filters                          | 4-31 |

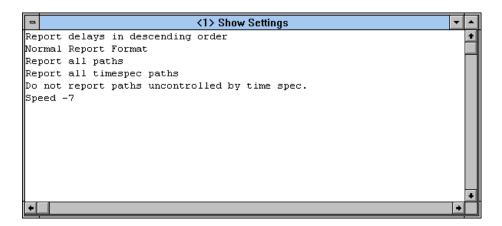

| Displaying Current Settings                     | 4-32 |

| Generating a Performance Summary Report         | 4-32 |

| Generating a Performance to TimeSpecs Report    | 4-33 |

| Generating a Detailed Path Report               | 4-39 |

| Reporting by Path Type                          | 4-40 |

| Reporting by Sources and Destinations           | 4-42 |

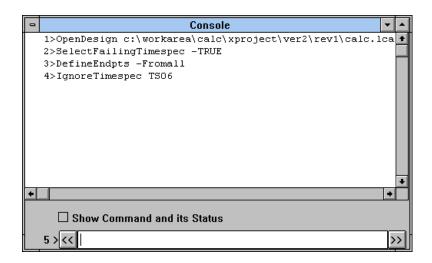

| Using the Console Window                        | 4-44 |

| Creating Macros                                 | 4-44 |

| Further Reading                                 | 4-45 |

# Viewlogic Tutorials

# PROcapture and PROsim Tutorial

# **Chapter 1**

# **PROcapture and PROsim Tutorial**

This tutorial guides you through a typical field-programmable gate array (FPGA) and erasable programmable logic device (EPLD) design procedure from schematic entry to completion of a functioning device. It uses PRO Series, Viewlogic's Windows-based toolset for design entry and simulation on personal computers (PCs). The tutorial uses a design called Calc, a 4-bit processor with a stack. In the first part of the tutorial, you use PROcapture, the PRO Series schematic entry tool, to create the schematics and symbols for the Calc design. Next, you use PROsim, the PRO Series simulator, to perform a functional simulation on it. In the third step, you use the Xilinx Design Manager to implement the design. Finally, you verify the design in PROsim using worst-case delays.

To install the tutorial, see the "Getting Started" section in this chapter.

# Introduction

This section provides you with some basic information about the tutorial: the devices to which it applies, approximately how long it will take to complete, and a description of the Calc design.

#### **Devices**

The procedures described in this tutorial apply to both FPGAs and EPLDs; differences are noted where applicable. Although the tutorial describes how to create both FPGA and EPLD designs, all figures illustrate the FPGA version of Calc except where noted.

# Length

Performed without interruption, the tutorial takes approximately five or six hours to complete. If you need to stop the tutorial at any time,

be sure to save the work that you have done by selecting the File → Save command. Then exit PRO Series either by selecting File → Exit from the menu or by typing quit. I at the command line.

### **Design Description**

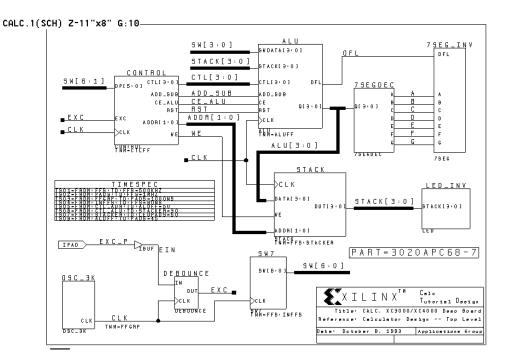

The processor in the Calc design performs functions between an internal register and either the top of the stack or data input from external switches. The results of the various operations are stored in the register and displayed in hexadecimal on a 7-segment display. The top value in the stack is displayed in binary on bar LEDs.

The design consists of nine basic functional blocks:

#### ALU

The arithmetic functions of the processor are performed in this block.

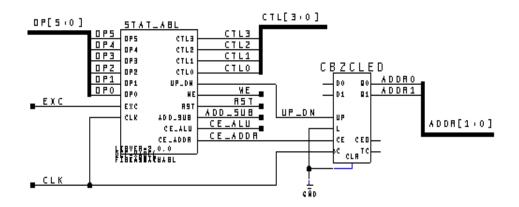

#### CONTROL

The opcodes are decoded into control lines for the stack and ALU in this module.

#### STACK

The stack is a four-nibble storage device implemented with flip-flops in the device-independent design.

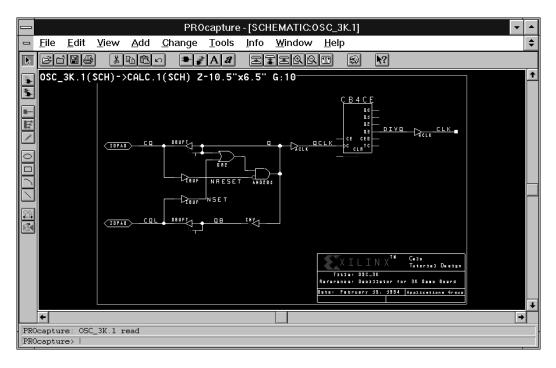

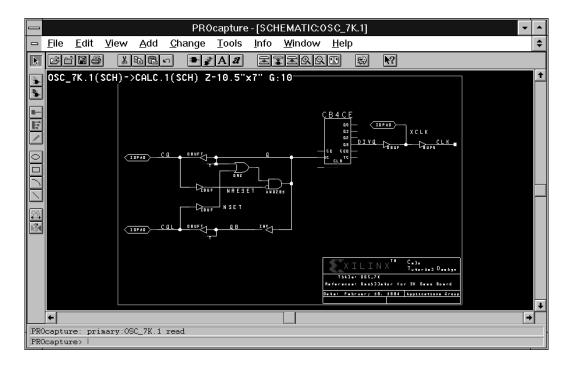

#### • OSC 3K, OSC 7K

These modules are used in XC3000A and XC7000 designs, respectively. OSC\_3K generates a clock signal using the RC oscillator circuit on the FPGA (XC3000A/XC4000) and XC3000A demonstration boards. OSC\_7K is the equivalent oscillator block for EPLDs.

#### DEBOUNCE

This circuit debounces the Execute switch, providing a one-shot output.

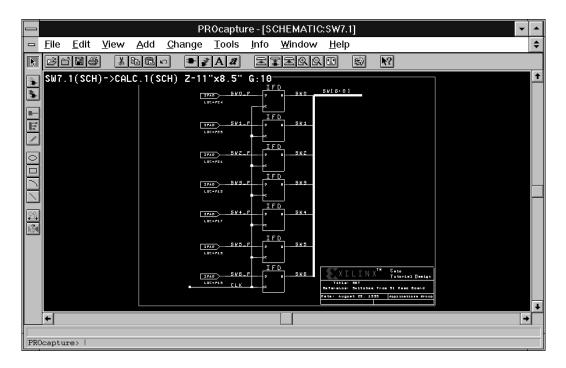

#### • SW7

The switch connections for opcode and data input are implemented within this module.

#### 7SEGDEC

This block decodes the output of the ALU for display on the 7-segment decoder.

7SEG\_TRU

This module implements the connections to the 7-segment display on the XC3000A demonstration board.

• LED\_TRU

The value at the top of the stack is displayed in binary on the LED bank of the XC3000A demonstration board.

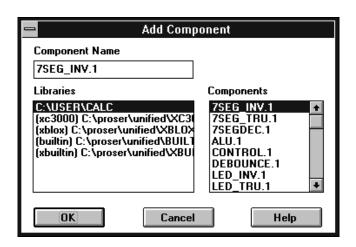

7SEG\_INV

This module implements the connections to the 7-segment display on the FPGA demonstration board.

LED\_INV

The value at the top of the stack is displayed in binary on the LED bank of the FPGA demonstration board.

# **Getting Started**

This section describes how to configure your PC to use the PRO Series tutorial, install the tutorial, start Xilinx PROflow, and set up the directories and initialization files for the Calc project.

# **Required Software**

This tutorial assumes that you are using the following versions of the development software:

- PRO Series release 6.0 or later

- Xilinx/Viewlogic Interface and Libraries: WIR2XNF V6.0.x and XNF2WIR V6.0.x or later

- XACTstep Development Software: DS-502 V6.0.x or later for FPGAs; DS-550 V6.0.x for EPLDs on PCs; DS-550 V5.2.x for EPLDs on workstations

**Note:** The instructions in this tutorial are written for the PRO Series user, and the PRO Series environment is shown in the figures of this document. However, you can use the Xilinx interface programs with

any current Viewlogic software, including Powerview V5.x or Workview PLUS V5.x. Workview 4.1.3a is also supported but does not run under the Windows environment.

## **Before Beginning the Tutorial**

Before beginning the tutorial, you must set up your PC to use the Viewlogic and XACTstep Development System software.

- 1. Verify that your system is properly configured. Consult the *Getting Started & Installation Guide* for instructions on setting up your machine to run the software.

- 2. Install one of the following sets of software. Each of these options includes Viewlogic PRO Series, the Xilinx/Viewlogic Interface and Libraries, and an XACTstep Development System.

- Base (DS-VLS-BAS-PC1), Standard (DS-VLS-STD-PC1), or Extended (DS-VLS-EXT-PC1) Stand-Alone (/S) Package Solutions for Viewlogic

or

Viewlogic PROcapture Schematic Editor, Interface, and Libraries (DS-390); and/or PROsim Simulator (DS-290); and XACTstep Development System (DS-502) for FPGAs, and/or XACTstep Development System (DS-550) for EPLDs

or

Viewlogic PRO Series V6.0 or later

and

Viewlogic Interface and Libraries (DS-391) and XACTstep Development System (DS-502) for FPGAs and/or XACTstep Development System (DS-550) for EPLDs; or Base (DS-VL-BAS-PC1) or Standard (DS-VL-STD-PC1) Interface Package Solution for Viewlogic

3. Verify that the following variables are set in your autoexec.bat file. It is assumed that you have loaded the software noted in the previous step to the c:\proser and c:\xact directories on your PC. If the software has been installed in different areas, modify the following Set statements accordingly. See the *Getting Started & Installation Guide* for additional information on system setup.

The PATH variable sets the overall executable search path. It

must include the directories where the PRO Series and

XACTstep Development System software have been installed.

Use this syntax:

PATH=other\_paths;c:\XACT;c:\PROSER;other\_paths

**Note:** The PATH variable cannot include any previous version of either the XACT*step* or Viewlogic software. Be sure to remove all paths to older software.

The XACT variable is used by the XACTstep and PRO Series software to locate data files. It must include the directory where the XACTstep Development System resides and the directory that contains the \unified directory, where the Unified Libraries reside. Use the following syntax:

SET XACT=C:\XACT;C:\PROSER

**Note:** As with the PATH variable, you can set multiple paths using a semicolon (;) between the paths. In the syntax just given, the XACTstep software is located in c:\xact, and the \unified directory is located in c:\proser. Because both paths are needed, they have been concatenated into a single path using a semicolon.

The WDIR variable sets the data file search path for the PRO Series software. It must include a directory to which you can write. Use this syntax:

SET WDIR=C:\PROSER\STANDARD

• The SYSPLT variable sets the PRO Series plotting directory. Use this syntax:

SET SYSPLT=C:\PROSER\STANDARD

# Installing the PRO Series Tutorial

The tutorial files are optionally installed when you install the Xilinx PRO Series software. This tutorial can be used with either XC3000A or XC7000 designs. If you have already installed the software but are not sure whether you specified the tutorial installation, check for the \calc3ka directory for XC3000A designs or the \calc7k directory for XC7000 designs under the c:\proser\tutorial\vwlogic\procalc directory. The \calc3ka directory contains the tutorial files needed to perform the tutorial for XC3000A designs, and the \calc7k directory

contains the files needed to perform the tutorial for XC7000 designs. It is recommended that you copy these files into another directory before performing the tutorial to preserve the original files.

For XC3000A designs, use the Windows File Manager to copy the \calc3ka directory to another directory such as c:\user\calc. For XC7000 designs, copy the \calc7k directory to this other directory.

**Note:** The rest of the tutorial refers to the c:\user\calc directory as the design directory.

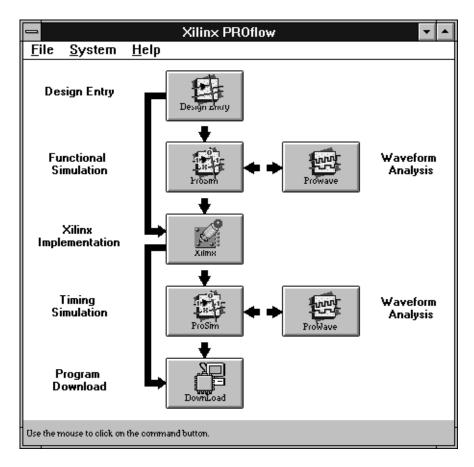

### **Starting Xilinx PROflow**

This tutorial uses Xilinx PROflow to implement the Calc design. On the basis of information such as the design type, part type, family, and the schematic components used, PROflow determines which options are available and which programs it must run to process the design correctly. Every tool and process step is executed by or invoked from PROflow. In addition to managing the processing of your design, PROflow also seamlessly integrates all the tools needed to enter, implement, simulate, and download your design.

PROflow even handles design maintenance. When you initially select the tutorial design within PROflow, it creates a Viewlogic design project and defines the associated libraries.

1. To open Xilinx PROflow, double-click on the Xilinx PROflow icon, shown in Figure 1-1, in the Program Manager XACT*step* program group.

Figure 1-1 Xilinx PROflow Icon

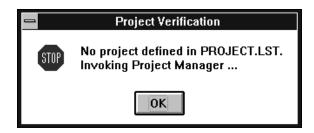

Selecting the Xilinx PROflow icon for the first time brings up a warning message, shown in Figure 1-2, stating that there is no project defined.

**Figure 1-2 Project Verification Warning Message**

#### 2. Click on OK.

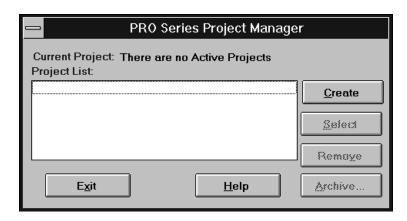

The message box closes, and the PRO Series Project Manager appears, as shown in Figure 1-3. The next section describes how to use it to create the Calc project.

Figure 1-3 PRO Series Project Manager

### **Defining the Calc Project**

The Viewlogic tools use the concept of projects to keep track of designs. A project is a working directory that contains the subdirectories and data files for a given design. Projects can even contain several designs of the same type, for example, a single project containing several XC3000A designs; however, it is recommended that each project contain only one design. The project containing the design actively being processed is known as the current project.

The definition of the Calc project involves three steps: creating a project in the c:\user\calc directory, generating the needed program initialization files and profiles, and selecting the CALC.1 schematic as the top-level schematic used when processing.

### Creating the Calc Project

The PRO Series Project Manager allows you to select, create, and remove projects. You must add the tutorial directory c:\user\calc to the Project List box and then select it.

$1. \ \ \, \text{Click on $\tt Create$ in the PRO Series Project Manager}.$

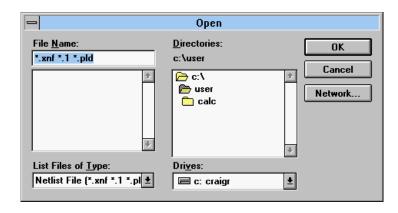

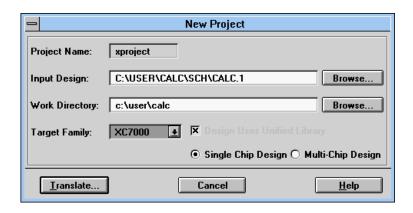

The Create Project dialog box appears, as shown in Figure 1-4.

1-8

Figure 1-4 Create Project Dialog Box

- 2. Select the c:\user\calc tutorial directory by double-clicking in the Directory list box until the field is correctly updated, as illustrated in Figure 1-4.

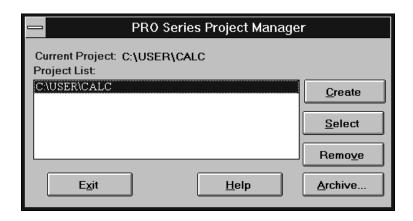

- 3. Click on OK.

The Create Project dialog box closes, and the PRO Series Project Manager opens showing the c:\user\calc directory in the Project List box. Figure 1-5 displays the updated Project Manager.

Figure 1-5 Updated PRO Series Project Manager

Now that you have created an entry for the tutorial directory, all that remains to do is to select it as the current project.

- 4. Click on Select, or double-click on the project name.

When you select c:\user\calc, the PRO Series Project Manager automatically creates the necessary initialization files.

- To close the PRO Series Project Manager, click on Exit.

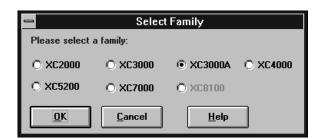

When you close the PRO Series Project Manager, the Select Family dialog box appears, as shown in Figure 1-6.

Figure 1-6 Select Family Dialog Box

6. Select **xC3000A** if you are performing the FPGA tutorial or **xC7000** if you are performing the EPLD tutorial.

#### 7. Click on OK.

Xilinx PROflow comes up, as shown in Figure 1-7.

Figure 1-7 Xilinx PROflow Window

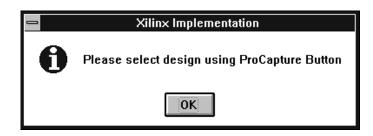

To guide you through processing your design, PROflow only allows you to enter stages in the design flow if the files that are needed for that step are present. For instance, if you were to click on the Xilinx Implementation icon, you would receive the message shown in Figure 1-8.

Figure 1-8 Xilinx Implementation Warning Message

Because the design to be processed has not been specified, PROflow does not allow you to enter the Xilinx Implementation section.

### **Obtaining Design Status**

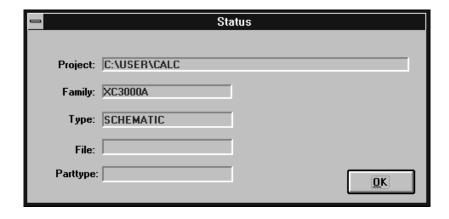

To see PROflow's initial design status, follow these steps.

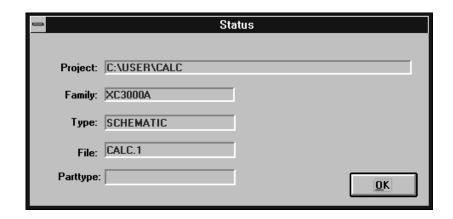

1. Select the File  $\rightarrow$  Status command.

This command displays the Status dialog box, shown in Figure 1-9, which displays the currently known information about the design. As you enter and process the Calc design, additional information appears in the remaining fields.

Figure 1-9 Status Dialog Box

#### 2. Click on OK.

The Status dialog box closes.

### **Selecting the CALC.1 Schematic**

In the previous sections, you defined the Calc project and created the necessary initialization files. Now you must select the Calc design's top-level schematic, CALC.1, as the current design.

1. In PROflow, click on the Design Entry icon, shown in Figure 1-10.

Figure 1-10 Design Entry Icon

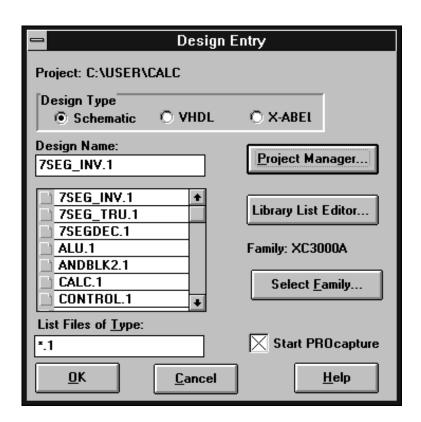

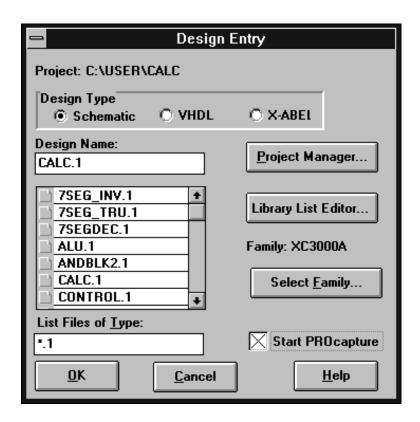

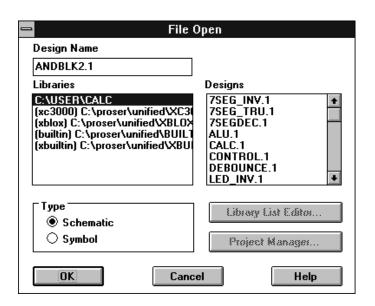

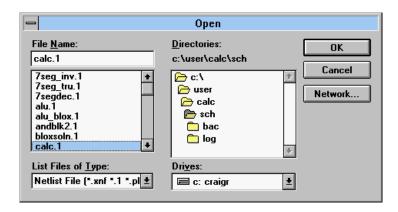

The Design Entry dialog box now appears, as shown in Figure 1-11.

Figure 1-11 Design Entry Dialog Box

The project displayed at the top of the dialog box is c:\user\calc. The List Files of Type field displays the default filter, \*.1.

Viewlogic allows a schematic to contain multiple sheets. The sheets are saved to the project directory's sch directory, where each sheet is a separate file. The extension of the file is the actual sheet number. If Calc's top-level schematic had two sheets, the sch directory would contain a CALC.1 and a CALC.2 file. The current string in the List Files of Type field in the Design Entry dialog box restricts the display to only the first sheet of each schematic. If you wanted to see all the second sheets, you could change the List Files of Type field to \*.2. To see all sheets, you could enter \*.\* in the List Files of Type field.

**Note:** The default of the Design Type field is Schematic. You can also process VHDL designs if the PROsynthesis package is installed or XABEL designs if the XABEL package is installed. The Calc tutorial focuses on processing straight schematic designs.

There are two ways to select the top-level schematic, CALC.1: you can either type the name directly in the Design Name field, or click on the file in the design list box.

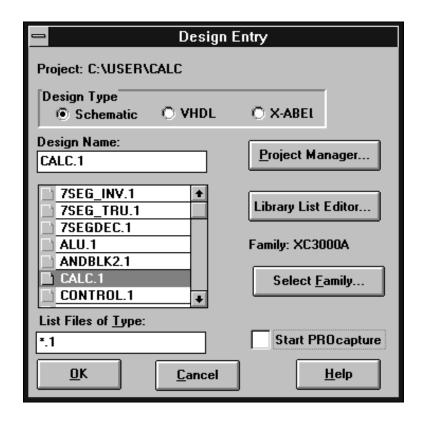

- Click on the CALC.1 file in the design list box.The CALC.1 file now appears in the Design Name field.

- 3. Click in the Start PROcapture check box to deselect it, as shown in Figure 1-12.

Figure 1-12 Disabling the Start PROcapture Check Box

Clicking on the Start PROcapture check box determines whether or not PROcapture is invoked when you click on the OK button. By default, Start PROcapture is selected. For now, you only want to select the design, so you must deselect the Start PROcapture check box.

4. Click on OK.

Because Start PROcapture is disabled, selecting OK closes the Design Entry dialog box and reactivates PROflow.

5. Select the File → Status command to display the Status dialog box, shown in Figure 1-13.

Figure 1-13 Status Dialog Box

Now the File field contains the selected design, CALC.1.

6. Click on OK to close the Status dialog box.

# **Navigating in PROcapture**

In creating a design, you typically use hierarchical levels to divide the design into more manageable sections. The top-level schematic for the Calc tutorial, CALC.1, has already been created for you. In this tutorial, you will add schematic information to the lower levels using the Viewlogic PROcapture program to create all schematics and symbols for a design. This section describes how to access PROcapture, adjust the colors of the PROcapture window, and move around the screen.

#### **Mouse Buttons**

Mouse buttons perform the following functions in PRO Series:

- The left mouse button selects objects.

- The right mouse button cancels the current command mode. In addition, you use it to select multiple items; select the first item with the left mouse button and subsequent items with the right mouse button.

# **Function Keys**

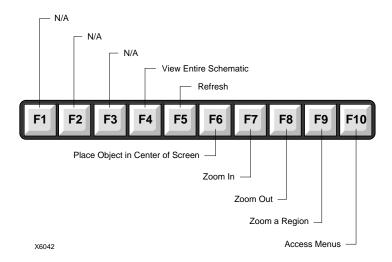

The function keys in PRO Series are labeled F1, F2, F3, and so forth on your keyboard. They are assigned the functions shown in Figure 1-14.

Figure 1-14 Default Function Keys

# **Starting PROcapture**

To open the CALC.1 schematic in PROcapture, follow these steps.

1. In PROflow, click on the Design Entry icon, shown in Figure 1-15.

Figure 1-15 Design Entry Icon

2. As demonstrated in Figure 1-16, click in the box next to the Start PROcapture field.

Figure 1-16 Selecting the Start PROcapture Check Box

3. Click on OK.

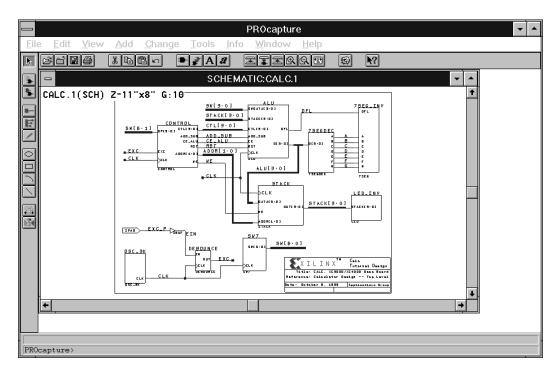

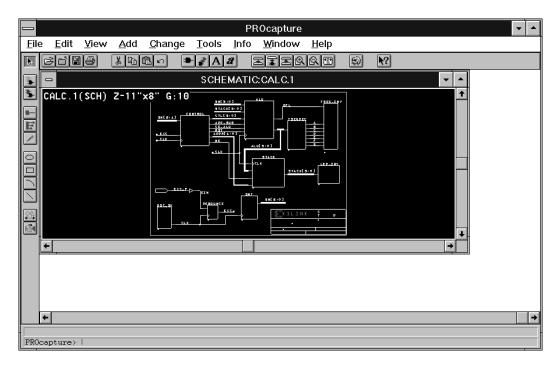

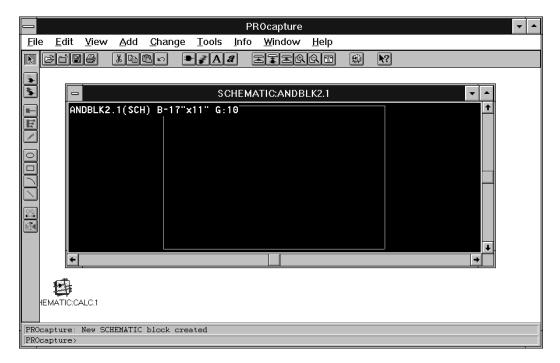

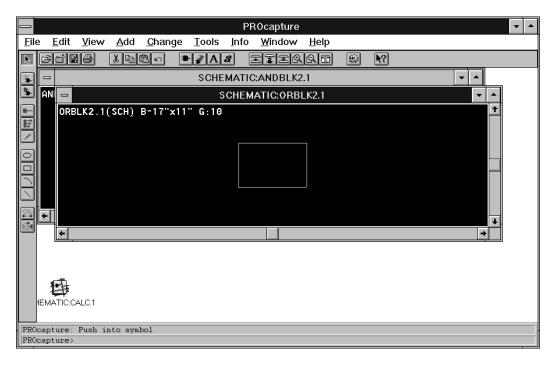

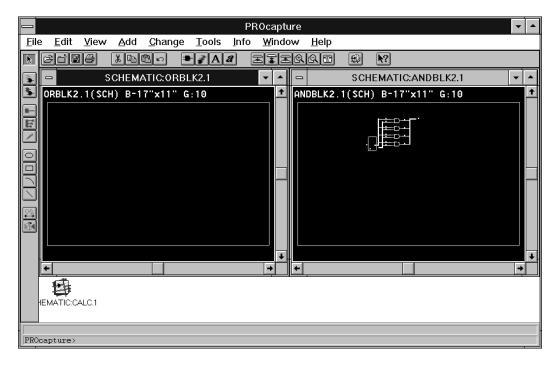

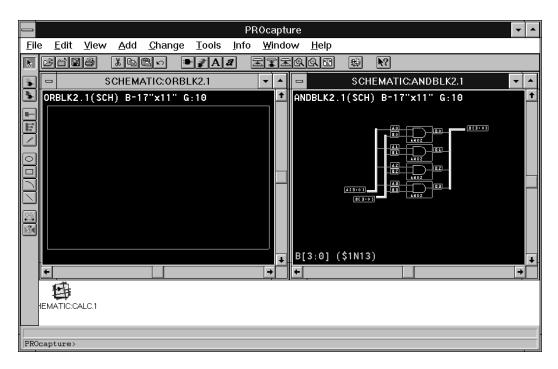

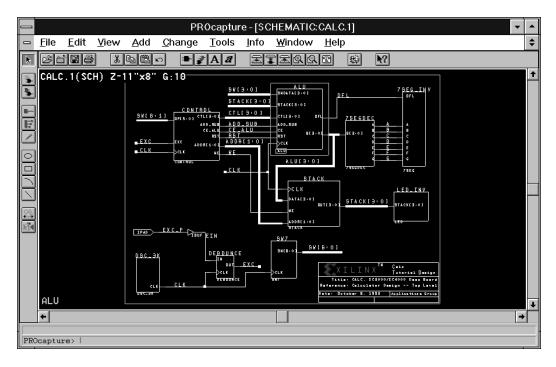

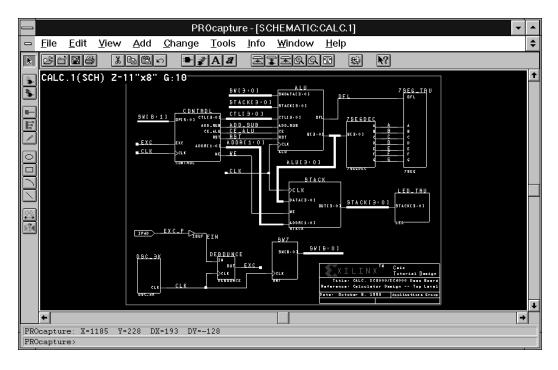

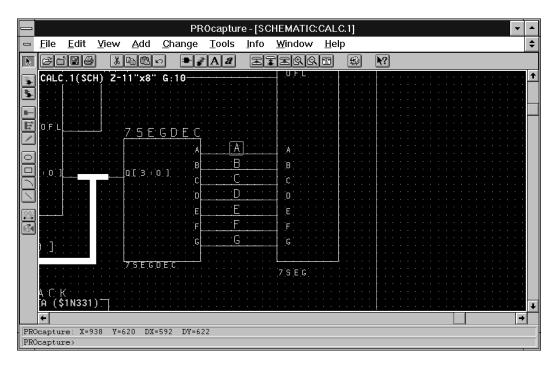

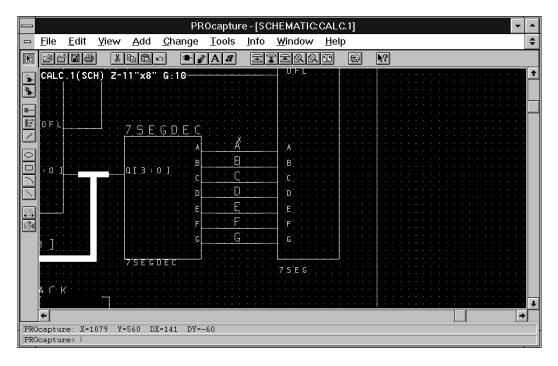

Because you enabled Start PROcapture, clicking on OK closes the Design Entry dialog box and invokes PROcapture on the selected CALC.1 schematic, as shown in Figure 1-17.

Figure 1-17 CALC.1 Schematic in PROcapture Window

# **Changing the PROcapture Window Colors**

You can change the PROcapture color settings so that viewing a schematic will be easier. If the background of your schematic is white and you want to change the color palette, proceed with the steps in this section; otherwise, skip to the next section.

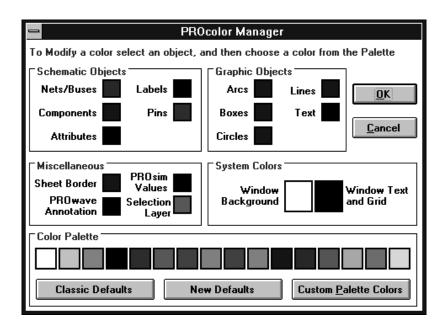

To change the color palette, select Change → PROcapture Colors.

The PROcolor Manager dialog box appears, as shown in Figure 1-18.

Figure 1-18 PROcolor Manager Dialog Box

2. Click on Classic Defaults.

This setting changes the color configuration for the various objects. The window background, window text, and grid toggle from white to black and vice versa.

3. Click on OK to close the PROcolor Manager dialog box and reactivate PROcapture.

An information dialog box comes up to inform you that the changes to the color palette will not take effect until you close all schematics and symbols.

- 4. Select File → Close to close the CALC.1 schematic.

- 5. Select **File** → **Open** to re-open the CALC.1 schematic.

The schematic should resemble the one shown in Figure 1-19. The colors onscreen are now changed.

Figure 1-19 CALC.1 Schematic in PROcapture Window

# **Moving Around the Screen**

PROcapture works like any other Windows program; it allows you to view and work in several different designs. The concept of working in several documents at once is known as the Multiple Document Interface, or MDI. MDI enables you to bring up multiple schematic windows and arrange them in the workspace in any fashion.

You can also zoom and pan around a schematic in PROcapture. Zooming allows you to view an entire schematic or focus on a particular section. You can select the zoom commands from the View menu, from the toolbar, or by pressing the designated function key.

You can also make icons of schematics when the schematics are not needed. Making an icon of a schematic does not close the schematic; it merely turns the window into an icon. Later, when you need the schematic, you can double-click on the icon to re-display it.

Table 1-1 at the end of this chapter summarizes the PRO Series functions, toolbar icons, menu commands, command line shortcuts, and function keys used in the rest of the tutorial.

#### **Panning**

You can familiarize yourself with the CALC.1 schematic by panning around the window. Panning is the process of obtaining a panoramic view of the screen by using one point as the center of the view.

To pan across the screen, first move the cursor to the location that will become the center of the new view, then press the **F6** function key. This step centers the edit area around the location of the cursor but does not move the cursor. Repeat moving the cursor and pressing F6 to move around the screen.

### Zooming

Zooming magnifies or shrinks the view onscreen. You can either view the entire schematic or focus on one portion of it. All of the zoom commands are dynamic, which means you can use them while you are in the middle of another command.

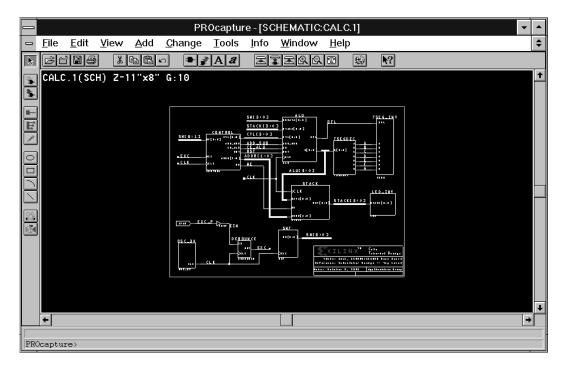

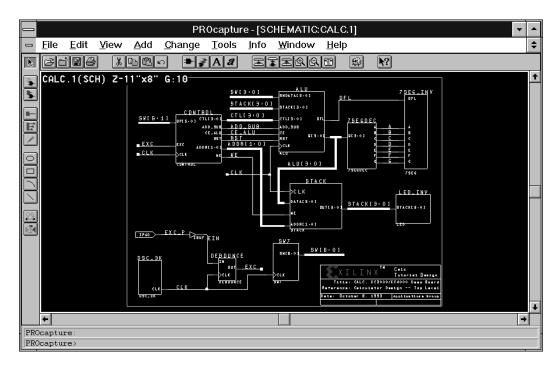

Click on the up arrow, shown in Figure 1-20, in the upper right corner of the CALC.1 schematic window to fill the entire workspace with the CALC.1 schematic window. Figure 1-21 shows the expanded window.

Figure 1-20 Up Arrow on the CALC.1 Schematic Window

Figure 1-21 Expanded Schematic Window

Notice that when the window is enlarged to fill the work space, the schematic does not fill the entire area of the new schematic window.

• To view the entire sheet — that is, to expand the schematic to fill the entire window — select the View → Full command.

*Keyboard Shortcut:* You can execute the View → Full command by pressing the **F4** function key.

*Toolbar Shortcut:* You can execute the View → Full command by clicking on the Full toolbar icon, shown in Figure 1-22.

#### Figure 1-22 Full Toolbar Icon

To zoom in, or magnify the view of the design, select the View → In command.

*Keyboard Shortcut:* You can execute the View → In command by pressing the **F7** function key.

*Toolbar Shortcut:* You can execute the View → In command by clicking on the In toolbar icon, shown in Figure 1-23.

#### Figure 1-23 In Toolbar Icon

To zoom out, or shrink the view of the design, select the View →

Out command.

*Keyboard Shortcut:* You can execute the View → Out command by pressing the **F8** function key.

*Toolbar Shortcut:* You can execute the View → Out command by clicking on the Out toolbar icon, shown in Figure 1-24.

#### Figure 1-24 Out Toolbar Icon

• To zoom a particular region, select the View → Region command. Define the area to be zoomed by pressing and holding the left mouse button in the upper left corner of the area and the left mouse button in the lower right corner. Release the left mouse button.

*Keyboard Shortcut:* You can execute the View  $\rightarrow$  Region command by pressing the **F9** function key. You define the upper left corner when you select the command and the lower right corner when you press the left mouse button.

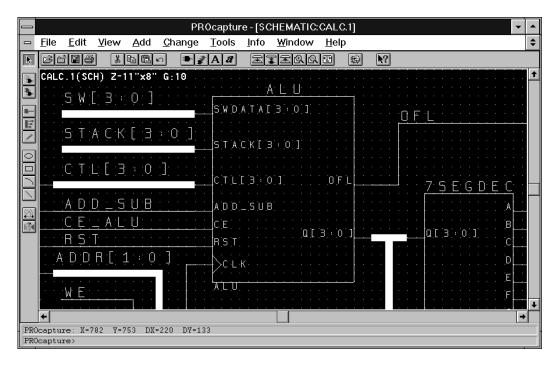

Practice these functions by magnifying the ALU block in the center of the screen, as shown in Figure 1-25.

- 1. To place the ALU block in the center of the screen, point the mouse at the middle of the ALU block and press the F6 function key.

- 2. Use the View → In and View → Out commands to magnify the ALU block until it fills the schematic. You can also use the View → Region command.

Figure 1-25 Zoomed ALU Block

## **Making Icons of Schematics and Symbols**

Use the following procedure to make an icon of the CALC.1 schematic window.

- When the schematic window occupies the entire screen, the name

of the schematic is shown in the PROcapture title bar. You can

reduce the size of the CALC.1 schematic by pressing the up/

down arrow button to the right of the Help menu.

- 2. Make an icon of the CALC.1 schematic window by pressing the down arrow button in the upper right of the CALC.1 schematic window. Figure 1-26 illustrates the resulting icon.

To re-open the CALC.1 schematic window, you can double-click on the icon; however, for this part of the tutorial, leave the CALC.1 schematic window as an icon.

Figure 1-26 CALC.1 Icon

# **PROcapture Command Summary**

The following table summarizes the commands used in this chapter and in the rest of the tutorial.

**Table 1-1 PROcapture Commands**

| Description                       | Toolbar Icon | Menu Command                  | Function<br>Key | Command<br>Line Entry |

|-----------------------------------|--------------|-------------------------------|-----------------|-----------------------|

| Obtain context-<br>sensitive help | <b>\</b> ?   | Help → Help                   | None            | help↓                 |

| Cancel current command            | No.          | None                          | None            | Esc key               |

| View entire<br>schematic          | <b>=</b>     | View → Full                   | F4              | full↓                 |

| Zoom in                           | <b>(2</b> )  | View → In                     | F7              | in₊∣                  |

| Zoom out                          | <u>s</u>     | View → Out                    | F8              | out₊                  |

| Zoom region                       | None         | View → Region                 | F9              | zoom₊                 |

| Place object in center of screen  | None         | None                          | F6              | None                  |

| Refresh screen                    | None         | View → Refresh                | F5              | refresh↓              |

| Push into schematic view          | <b>=</b>     | View → Push Into<br>Schematic | None            | psc↓                  |

| Description                          | Toolbar Icon | Menu Command                           | Function<br>Key | Command<br>Line Entry                  |

|--------------------------------------|--------------|----------------------------------------|-----------------|----------------------------------------|

| Push into<br>symbol view             | <b>=</b>     | View → Push Into<br>Symbol             | None            | psy₊                                   |

| Pop out of<br>schematic or<br>symbol | <b></b>      | View → Pop                             | None            | рор₊Ј                                  |

| Open a file                          |              | File → Open                            | None            | symil for symbols schil for schematics |

| Save a file                          | None         | File → Save                            | None            | wri↓                                   |

| Save a file as                       |              | File → Save As                         | None            | writeto↓                               |

| Close the active window              |              | File → Close                           | None            | wc1.J                                  |

| Add a box                            |              | Add → Box                              | None            | box₊                                   |

| Add a symbol pin                     | P            | Add → Pin                              | None            | pin₊                                   |

| Add a label                          | None         | Add → Object Label                     | None            | la₊                                    |

| Change an attribute                  | a            | Change → Object<br>Attributes → Dialog | None            | at₊                                    |

| Description                               | Toolbar Icon | Menu Command                                                  | Function<br>Key | Command<br>Line Entry |

|-------------------------------------------|--------------|---------------------------------------------------------------|-----------------|-----------------------|

| Add text                                  | Α            | Add → Text                                                    | None            | text↓                 |

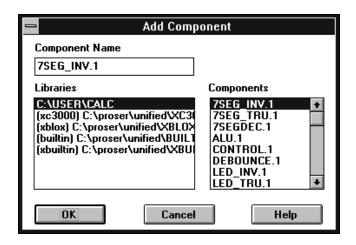

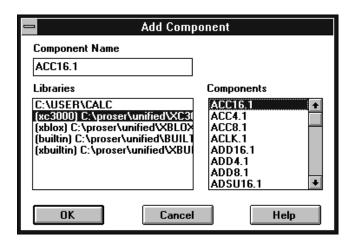

| Add a<br>component                        | -            | Add → Component                                               | None            | com₊                  |

| Add a net                                 |              | Add → Net                                                     | None            | ne₊                   |

| Add a bus                                 | F            | Add → Bus                                                     | None            | bu₊∣                  |

| Make attributes invisible                 | None         | Change → Object<br>Attributes → Visibility<br>→ All Attrs Off | None            | ain₊                  |

| Make attributes<br>visible                | None         | Change → Object<br>Attributes → Visibility<br>→ All Attrs On  | None            | avi₊                  |

| Select components                         | None         | Edit → Select                                                 | None            | sco₊l                 |

| Move an object                            |              | Edit → Move                                                   | None            | ml                    |

| Copy selected<br>objects to the<br>buffer |              | Edit → Copy                                                   | None            | bcop₊                 |

| Description                    | Toolbar Icon | Menu Command       | Function<br>Key | Command<br>Line Entry |

|--------------------------------|--------------|--------------------|-----------------|-----------------------|

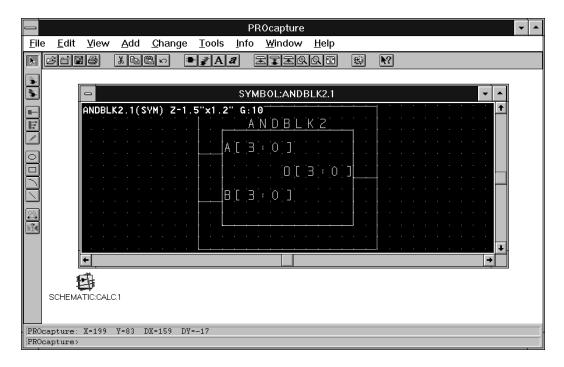

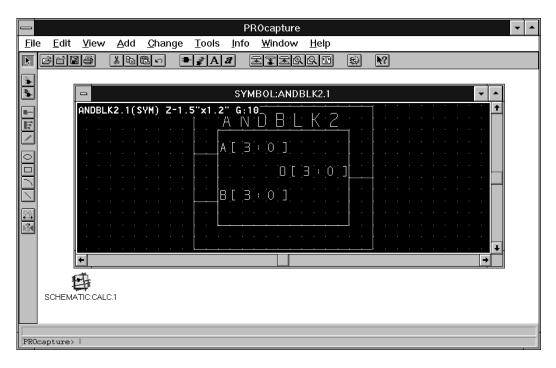

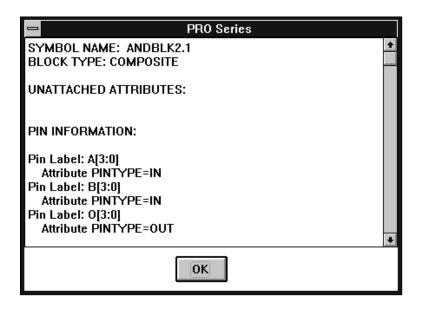

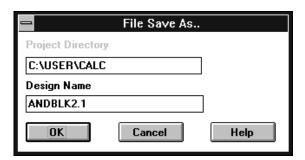

| Paste objects from the buffer  |              | Edit → Paste       | None            | bpa₊                  |