## **PCMCIA Library R1.2**

May 25, 1997

**Product Specification**

Formerly Mobile Media Research, Inc.

3550 Mowry Ave., Suite 101 Fremont, CA 94538 USA Phone: +1 800-799-6674

+1 510-795-2212 Fax: +1 510-795-2219

E-mail: sales@digitalobjects.com URL: www.digitalobjects.com

#### **Features**

- Simple building blocks for user customization

- · Built-in PCMCIA Interface

- Support for Function Configuration Registers (FCR)

- Support for external CIS EEPROM

- · FCR bit decode implemented by user

- Includes a test primitive which can be used to test socket

## **General Description**

The PCMCIA Library is a library of very simple PCMCIA interface primitives that can be fully customized for a specific user application. The Function Configuration Register (FCR) bits are not decoded and can be implemented in any way necessary. These primitives provide a generic PCMCIA interface and can be customized to work with any I/O device on the PC Card. The library includes a test primitive to help test the PCMCIA socket.

| AllianceCORE™ Facts                             |                               |                 |

|-------------------------------------------------|-------------------------------|-----------------|

| Core Specifics                                  |                               |                 |

| Device Family                                   | XC3x00A                       |                 |

| CLBs Used                                       | 20-30, see block descriptions |                 |

| IOBs Used                                       | 32/33 <sup>1</sup>            |                 |

| System Clock f <sub>max</sub>                   | 10 MHz                        |                 |

| Device Features Used                            | Not Applicable                |                 |

| Supported Devices/Resources Remaining           |                               |                 |

|                                                 | I/O                           | CLBs            |

| XC3x42A TQ100                                   | 50/49 <sup>2</sup>            | 114-124         |

| Provided with Core                              |                               |                 |

| Documentation                                   | User Documentation            |                 |

| Design File Formats                             | ViewLogic Schematic           |                 |

| Constraint Files                                | Not Applicable                |                 |

| Verification Tool                               | ViewSim Command Files         |                 |

| Schematic Symbols                               | Viewlogic                     |                 |

| Evaluation Model                                | Prototyping board             |                 |

|                                                 |                               | Available extra |

| Reference designs &                             |                               | None            |

| application notes                               |                               |                 |

| Additional Items                                |                               | None            |

| Design Tool Requirements                        |                               |                 |

| Xilinx Core Tools                               | XACTstep 5.2.1/6.0.1          |                 |

| Entry/Verification Tools ViewLogic Schematic    |                               |                 |

| Support                                         |                               |                 |

| Support provided by Digital Objects Corporation |                               |                 |

#### Notes:

IOB count is for CIS, PCMCG1 (both 33 I/O) and PCMCG1 (32 I/O) primitives only; test primitive uses 58 I/O; I/O counts assume all signals are routed off-chip.

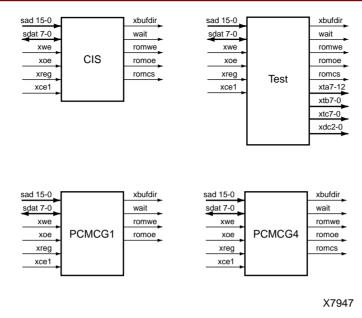

Figure 1. Xilinx PCMCIA Library Primitives

## **Functional Description**

The PCMCIA Library consists of four primitives, as shown in Figure 1, and described below.

## CIS Primitive (20 CLBs)

This primitive provides an interface to PCMCIA and allows the host to read/write directly to the CIS ROM on the PC Card. It implements all four Function Configuration Registers without implementing any specific bit decodes. The registers occupy addresses 100h, 102h, 104h and 106h in attribute memory and are read/write.

## **Test Primitive (28 CLBs)**

This primitive is similar to the CIS primitive except that some bits of all four of the PCMCIA Function Configuration Registers are brought out and available for decode and verification. The individual bits of the registers are not decoded but are read/write

## PCMCG1 Primitive (20 CLBs)

This primitive is similar to the CIS primitive except that it only implements one Function Configuration Register and CIS accesses are not supported.

## PCMCG4 Primitive (30 CLBs)

This primitive is similar to PCMCG1 except that it implements four FCRs

#### **Pinout**

The pinout of each primitive has not been fixed to specific FPGA I/O, allowing flexibility with a users application. Signal names are provided for each primitive shown in Figure 1, and Table 1 below.

**Table 1. PCMCIA Library Primitives Signal Pinout**

|                                                  | Signal    |                                                  |  |

|--------------------------------------------------|-----------|--------------------------------------------------|--|

| Signal                                           | Direction |                                                  |  |

| Common Signals for all Primitives                |           |                                                  |  |

| sad 15-0                                         | Input     | Host address                                     |  |

| sdat 7-0                                         | In/Out    | Host data                                        |  |

| xwe                                              | Input     | Write Enable                                     |  |

| xoe                                              | Input     | Output Enable                                    |  |

| xreg                                             | Input     | Attribute Memory Select from host                |  |

| xce1                                             | Input     | Card Enable from host                            |  |

| xbufdir                                          | Output    | Controls direction of data buffer                |  |

| wait                                             | Output    | Inserts delay in completion of cycle to the host |  |

| romwe                                            | Output    | Write enable to CIS EE-PROM                      |  |

| romoe                                            | Output    | Output Enable to CIS EE-PROM                     |  |

| Additional Signals for CIS and PCMCG4 Primitives |           |                                                  |  |

| romcs                                            | Output    | Chip Select to CIS EEPROM                        |  |

| Additional Signals for Test Primitive            |           |                                                  |  |

| romcs                                            | Output    | Chip Select to CIS EEPROM                        |  |

| xta 7-2                                          | Output    | FCR 0 bits 7-2                                   |  |

| xtb 7-1                                          | Output    | FCR 1 bits 7-1                                   |  |

| xtc 7-0                                          | Output    | FCR 2 bits 7-0                                   |  |

| xdc 2-0                                          | Output    | FCR 3 bits 2 -0                                  |  |

# **Verification Methods**

The primitives have been fully tested for compatibility with all major applications and Card Services. They have recently been upgraded to use the latest Xilinx unified library elements.

# **Recommended Design Experience**

Designers should be familiar with the PCMCIA specification, ViewLogic schematic entry and Xilinx design flows.

## **Available Support Products**

Support products available from Digital Objects:

- PCMCIA Prototyping Card

- PCMCIA Card Debugger/Exerciser software

- · CIS Generator 1.2 software

## **Ordering Information**

To purchase or make further inquiries about this or other Digital Objects products, contact Digital Objects directly.

#### Related Information

# Personal Computer Memory Card International Association

The PCMCIA publishes PC-Card specifications and related documents. For information, contact:

**PCMCIA Headquarters**

2635 North First Street, Suite 209

San Jose, CA 95134 USA

Phone: +1 408-433-CARD (2273)

Fax: +1 408-433-9558

BBS: +1 408-433-2270

E-mail: office@pcmcia.org

URL: www.pc-card.com

PCMCIA European Chapter

Avenue Marcel Thirty 204

B-1200 Brussels, Belgium

Phone: +32 2-774-9620

Fax: +32 2-774-9690

## Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx. Inc.

2100 Logic Drive

San Jose, CA 95124

Phone: +1 408-559-7778 Fax: +1 408-559-7114 URL: www.xilinx.com

For general Xilinx literature, contact:

Phone: +1 800-231-3386 (inside the US)

+1 408-879-5017 (outside the US)

E-mail: literature@xilinx.com

For AllianceCORE<sup>TM</sup> specific information, contact:

Phone: +1 408-879-5381

E-mail: alliancecore@xilinx.com

URL: www.xilinx.com/products/logicore/alliance/

tblpart.htm