# Design Manager/ Flow Engine Guide

**Introduction**

**Getting Started**

Using the Design Manager and Flow Engine

Glossary

Xilinx Development System

The Xilinx logo shown above is a registered trademark of Xilinx, Inc.

ASYL, FPGA Architect, FPGA Foundry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Timing Wizard, TRACE, XACT, XILINX, XC2064, XC3090, XC4005, XC5210, and XC-DS501 are registered trademarks of Xilinx, Inc.

The shadow X shown above is a trademark of Xilinx, Inc.

All XC-prefix product designations, A.K.A Speed, Alliance Series, AllianceCORE, BITA, CLC, Configurable Logic Cell, CoolRunner, CORE Generator, CoreLINX, Dual Block, EZTag, FastCLK, FastCONNECT, FastFLASH, FastMap, Fast Zero Power, Foundation, HardWire, IRL, LCA, LogiBLOX, Logic Cell, LogiCORE, LogicProfessor, MicroVia, MultiLINX, PLUSASM, PowerGuide, PowerMaze, QPro, RealPCI, RealPCI, 64/66, SelectI/O, SelectRAM, SelectRAM+, Silicon Xpresso, Smartguide, Smart-IP, SmartSearch, Smartspec, SMARTSwitch, Spartan, TrueMap, UIM, VectorMaze, VersaBlock, VersaRing, Virtex, WebFitter, WebLINX, WebPACK, XABEL, XACT*step*, AACT*step* Advanced, XACT*step* Foundry, XACT-Floorplanner, XACT-Performance, XAM, XAPP, X-BLOX, X-BLOX plus, XChecker, XDM, XDS, XEPLD, Xilinx Foundation Series, XPP, XSI, and ZERO+ are trademarks of Xilinx, Inc.

All other trademarks are the property of their respective owners.

Xilinx, Inc. does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx, Inc. reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx, Inc. will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx, Inc. devices and products are protected under one or more of the following U.S. Patents: 4,642,487; 4,695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,455,525; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; 5,504,439; 5,506,518; 5,506,523; 5,506,878; 5,513,124; 5,517,135; 5,521,835; 5,521,837; 5,523,963; 5,523,971; 5,524,097; 5,526,322; 5,528,169; 5,528,176; 5,530,378; 5,530,384; 5,546,018; 5,550,839; 5,550,843; 5,552,722; 5,553,001; 5,559,751; 5,561,367; 5,561,629; 5,561,631; 5,563,527; 5,563,528; 5,563,529; 5,563,827; 5,565,792; 5,566,123; 5,570,051; 5,574,634; 5,574,655; 5,578,946; 5,581,198; 5,581,199; 5,581,738; 5,583,450; 5,583,452; 5,592,105; 5,594,367; 5,598,424; 5,600,263; 5,600,264; 5,600,271; 5,600,597; 5,608,342; 5,610,536; 5,610,790; 5,610,829; 5,612,633; 5,617,021; 5,617,041; 5,617,327; 5,617,573; 5,623,387; 5,627,480; 5,629,637; 5,629,886; 5,631,577; 5,631,583; 5,635,851; 5,636,368; 5,640,106; 5,642,058; 5,646,545; 5,646,547; 5,646,564; 5,646,903; 5,648,732; 5,648,913; 5,650,672; 5,650,946; 5,652,904; 5,654,631; 5,656,950; 5,657,290; 5,659,484; 5,661,660; 5,661,685; 5,670,896; 5,670,897; 5,672,966; 5,673,198; 5,675,262; 5,675,270; 5,675,589; 5,677,638; 5,682,107; 5,689,133; 5,689,516; 5,691,907; 5,691,912; 5,694,047; 5,694,056; 5,724,276; 5,694,399; 5,696,454; 5,701,091; 5,701,441; 5,703,759; 5,705,932; 5,705,938; 5,708,597; 5,712,579; 5,715,197; 5,717,340; 5,719,506; 5,719,507; 5,724,276; 5,726,484; 5,726,584; 5,734,866; 5,734,868; 5,737,234; 5,737,235;

5.737.631: 5.742.178: 5.742.531: 5.744.974: 5.744.979: 5.744.995: 5.748.942: 5.748.979: 5.752.006: 5.752.035: 5,754,459; 5,758,192; 5,760,603; 5,760,604; 5,760,607; 5,761,483; 5,764,076; 5,764,534; 5,764,564; 5,768,179; 5,770,951; 5,773,993; 5,778,439; 5,781,756; 5,784,313; 5,784,577; 5,786,240; 5,787,007; 5,789,938; 5,790,479; 5,790,882; 5,795,068; 5,796,269; 5,798,656; 5,801,546; 5,801,547; 5,801,548; 5,811,985; 5,815,004; 5,815,016; 5,815,404; 5,815,405; 5,818,255; 5,818,730; 5,821,772; 5,821,774; 5,825,202; 5,825,662; 5,825,787; 5,828,230; 5,828,231; 5,828,236; 5,828,608; 5,831,448; 5,831,460; 5,831,845; 5,831,907; 5,835,402; 5,838,167; 5,838,901; 5,838,954; 5,841,296; 5,841,867; 5,844,422; 5,844,424; 5,844,829; 5,844,844; 5,847,577; 5,847,579; 5,847,580; 5,847,993; 5,852,323; 5,861,761; 5,862,082; 5,867,396; 5,870,309; 5,870,327; 5,870,586; 5,874,834; 5,875,111; 5,877,632; 5,877,979; 5,880,492; 5,880,598; 5,880,620; 5,883,525; 5,886,538; 5,889,411; 5,889,413; 5,889,701; 5,892,681; 5,892,961; 5,894,420; 5,896,047; 5,896,329; 5,898,319; 5,898,320; 5,898,602; 5,898,618; 5,898,893; 5,907,245; 5,907,248; 5,909,125; 5,909,453; 5,910,732; 5,912,937; 5,914,514; 5,914,616; 5,920,201; 5,920,202; 5,920,223; 5,923,185; 5,923,602; 5,923,614; 5,928,338; 5,931,962; 5,933,023; 5,933,025; 5,933,369; 5,936,415; 5,936,424; 5,939,930; 5,942,913; 5,944,813; 5,945,837; 5,946,478; 5,949,690; 5,949,712; 5,949,983; 5,949,987; 5,952,839; 5,952,846; 5,955,888; 5,956,748; 5,958,026; 5,959,821; 5,959,881; 5,959,885; 5,961,576; 5,962,881; 5,963,048; 5,963,050; 5,969,539; 5,969,543; 5,970,142; 5,970,372; 5,971,595; 5,973,506; 5,978,260; 5,986,958; 5,990,704; 5,991,523; 5,991,788; 5,991,880; 5,991,908; 5,995,419; 5,995,744; 5,995,988; 5,999,014; 5,999,025; 6,002,282; and 6,002,991; Re. 34,363, Re. 34,444, and Re. 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx, Inc. assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx, Inc. will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1991-2000 Xilinx, Inc. All Rights Reserved.

# **About This Manual**

This manual describes the Xilinx Design Manager and Flow Engine, tools that manage and process your design implementation. This manual describes the use of these tools with the Xilinx Alliance Series software. Because the Design Manager and Flow Engine are closely integrated in the Alliance Series, this manual covers both software applications in detail and also covers how to access other tools from the Design Manager.

In the Xilinx Foundation Series software, the Project Manager, rather than the Design Manager, is the top level software tool that is closely integrated with the Flow Engine. For information on the Foundation Series Flow Engine, refer to this manual. For information on the Project Manager, see the *Foundation Series User Guide*.

The Design Manager software documented in this manual is available as a standalone tool from the Foundation Series software. Use the Xilinx Foundation Series  $\rightarrow$  Accessories  $\rightarrow$  Design Manager command to access the standalone Design Manager.

Note This Xilinx software release is certified as Year 2000 compliant.

# **Manual Contents**

This manual covers the following topics.

• Chapter 1, "Introduction," describes the Design Manager and Flow Engine main functions, their place in the Xilinx design flow, key features, inputs and outputs, and supported architectures. It also outlines the basic procedure for using the tools.

- Chapter 2, "Getting Started," describes how to start and exit the Design Manager and Flow Engine; how to use the menus, icons, and dialog boxes; and how to use online help.

- Chapter 3, "Using the Design Manager and Flow Engine," explains how to perform Design Manager and Flow Engine functions.

- "Glossary," defines important words, terms, concepts, and ideas used in this manual.

# **Additional Resources**

For additional information, go to http://support.xilinx.com. The following table lists some of the resources you can access from this Web site. You can also directly access these resources using the provided URLs.

| Resource             | Description/URL                                                                                                                                                                                                                                                          |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tutorials            | Tutorials covering Xilinx design flows, from design entry to verification<br>and debugging<br>http://support.xilinx.com/support/techsup/tutorials/<br>index.htm                                                                                                          |  |

| Answers<br>Database  | Current listing of solution records for the Xilinx software tools<br>Search this database using the search function at<br>http://support.xilinx.com/support/searchtd.htm                                                                                                 |  |

| Application<br>Notes | Descriptions of device-specific design techniques and approaches<br>http://support.xilinx.com/apps/appsweb.htm                                                                                                                                                           |  |

| Data Book            | Pages from <i>The Programmable Logic Data Book</i> , which contain device-<br>specific information on Xilinx device characteristics, including readback,<br>boundary scan, configuration, length count, and debugging<br>http://support.xilinx.com/partinfo/databook.htm |  |

| Xcell Journals       | Quarterly journals for Xilinx programmable logic users<br>http://support.xilinx.com/xcell/xcell.htm                                                                                                                                                                      |  |

| Technical Tips       | Latest news, design tips, and patch information for the Xilinx design<br>environment<br>http://support.xilinx.com/support/techsup/journals/<br>index.htm                                                                                                                 |  |

# Conventions

This manual uses the following conventions. An example illustrates each convention.

# Typographical

The following conventions are used for all documents.

• Courier font indicates messages, prompts, and program files that the system displays.

speed grade: - 100

• Courier bold indicates literal commands that you enter in a syntactical statement. However, braces "{}" in Courier bold are not literal and square brackets "[]" in Courier bold are literal only in the case of bus specifications, such as bus [7:0].

rpt\_del\_net=

**Courier bold** also indicates commands that you select from a menu.

${\tt File} \ \rightarrow \ {\tt Open}$

- *Italic font* denotes the following items.

- Variables in a syntax statement for which you must supply values

edif2ngd design\_name

• References to other manuals

See the *Development System Reference Guide* for more information.

• Emphasis in text

If a wire is drawn so that it overlaps the pin of a symbol, the two nets are *not* connected.

• Square brackets "[]" indicate an optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required.

```

edif2ngd [option_name] design_name

```

• Braces "{}" enclose a list of items from which you must choose one or more.

```

lowpwr ={on|off}

```

• A vertical bar " | " separates items in a list of choices.

lowpwr ={on|off}

• A vertical ellipsis indicates repetitive material that has been omitted.

```

IOB #1: Name = QOUT'

IOB #2: Name = CLKIN'

.

.

```

• A horizontal ellipsis "...." indicates that an item can be repeated one or more times.

allow block block\_name loc1 loc2locn;

# **Online Document**

The following conventions are used for online documents.

• Red-underlined text indicates an interbook link, which is a crossreference to another book. Click the red-underlined text to open the specified cross-reference. • Blue-underlined text indicates an intrabook link, which is a cross-reference within a book. Click the blue-underlined text to open the specified cross-reference.

# Contents

#### **About This Manual**

| Manual Contents      | i  |

|----------------------|----|

| Additional Resources | ii |

#### Conventions

| Typographical   | . iii |

|-----------------|-------|

| Online Document | . iv  |

#### Chapter 1 Introduction

| Overview                          |      |

|-----------------------------------|------|

| Design Flow                       | 1-2  |

| Inputs and Outputs                |      |

| Architecture Support              |      |

| Design Manager Fundamentals       |      |

| Projects                          |      |

| Design Versions                   |      |

| Implementation Revisions          |      |

| Design Management Basic Procedure |      |

| Flow Engine Fundamentals          |      |

| Design Implementation             |      |

| Translate                         | 1-11 |

| Map (FPGA)                        | 1-12 |

| Place&Route (FPGA)                |      |

| Fit (CPLD)                        |      |

| Timing (Sim)                      |      |

| Configure (FPGA)                  | 1-14 |

| Bitstream (CPLD)                  |      |

| Smart Flow Engine                 |      |

| 5                                 |      |

#### Chapter 2 Getting Started

| Preparing the Input Design File         | 2-1 |

|-----------------------------------------|-----|

| Starting and Exiting the Design Manager | 2-1 |

| Starting as a Standalone Tool           | 2-2 |

| Starting from the Command Line          | 2-2 |

| Exiting the Design Manager              | 2-2 |

| Starting and Exiting the Flow Engine    | 2-2 |

| Starting from the Alliance Series       | 2-3 |

| Starting from the Foundation Series     | 2-3 |

| Exiting the Flow Engine                 | 2-3 |

| Using the Interface                     | 2-3 |

| Main Window                             | 2-3 |

| Design Manager Window                   | 2-4 |

| Flow Engine Window                      | 2-5 |

| Title Bar                               | 2-7 |

| Menu Bar                                | 2-7 |

| Toolbar Buttons                         | 2-7 |

| Toolbox Buttons                         | 2-7 |

| Status Bar                              | 2-7 |

| Dialog Boxes                            | 2-7 |

| Common Fields                           | 2-8 |

| Using Help                              | 2-8 |

| Help Menu                               | 2-8 |

| Toolbar Help Button                     | 2-9 |

| F1 Key                                  | 2-9 |

| Help Button in Dialog Boxes             | 2-9 |

#### Chapter 3 Using the Design Manager and Flow Engine

| Creating a New Project                              | . 3-2  |

|-----------------------------------------------------|--------|

| Creating a New Design Version                       | . 3-3  |

| Creating a New Implementation Revision              | . 3-6  |

| Setting a Part                                      | . 3-9  |

| Deleting Items from the Project View                | . 3-11 |

| Specifying Implementation Flow Options              | . 3-12 |

| Implementing a Design from the Design Manager       | . 3-15 |

| Implementing a Design Automatically                 | . 3-16 |

| Re-Implementing a Design                            | . 3-17 |

| Copying Constraints, Guide, and Floorplan File Data | . 3-17 |

| Setting a Constraints File                          | . 3-17 |

| Setting a Guide File                                | . 3-19 |

| Setting Floorplan Files                             | . 3-22 |

| Viewing Reports                                     | . 3-23 |

| Producing Timing Reports                            | . 3-24 |

| Generating Pin Locking Constraints             | 3-25 |

|------------------------------------------------|------|

| Producing Timing Simulation Data               |      |

|                                                | 3-30 |

|                                                | 3-30 |

| •                                              |      |

|                                                | 3-32 |

| Implementing a Design in Separate Steps        | 3-32 |

| Setting the State of the Flow                  | 3-33 |

| Enabling Flashing Icons                        | 3-34 |

| Setting a Run Target                           |      |

| Updating the Flow                              | 3-35 |

| Placing and Routing Non-Timing Driven Designs  | 3-35 |

| Running Multiple Place and Route Passes        | 3-36 |

| Running Re-Entrant Routing on FPGAs            | 3-39 |

| Working with Templates                         | 3-41 |

| Starting the Template Manager                  | 3-42 |

| Creating a New Template                        | 3-43 |

| Creating a Template Based on a Xilinx Template | 3-44 |

| Editing a Template                             | 3-44 |

| Setting Custom Template Options                | 3-45 |

| Using a Template                               | 3-47 |

| Restoring a Template                           | 3-50 |

# **Chapter 1**

# Introduction

This chapter briefly describes the Design Manager and Flow Engine. It describes their main functions, their place in the design flow, major features, inputs and outputs, and supported device architectures. It also outlines the basic procedure for using these tools. This chapter contains the following sections.

- "Overview"

- "Design Flow"

- "Inputs and Outputs"

- "Architecture Support"

- "Design Manager Fundamentals"

- "Flow Engine Fundamentals"

- "Smart Flow Engine"

#### Overview

The Design Manager is the top level software module in the Xilinx Alliance Series Development System. Use the Xilinx Development System tool suite to implement a design into a Xilinx device. The Design Manager provides access to all the tools you need to read a design file from a design entry tool and implement it in a Xilinx device. The Design Manager performs the following functions.

- Organizes and manages your design implementation data

- Creates multiple design versions for management of design changes

- Creates multiple implementation revisions for management of implementation strategies

- Provides access to reports

- Manages data for and provides access to the following tools. The tools differ for Field Programmable Gate Array (FPGA) and Complex Programmable Logic Device (CPLD) families.

- Flow Engine (FPGA and CPLD)

- Timing Analyzer (FPGA and CPLD)

- Floorplanner (All XC4000 families and Virtex, Virtex-E, Virtex-II, Spartan, SpartanXL, and Spartan-II FPGAs only)

- PROM File Formatter (FPGA)

- Hardware Debugger (FPGA)

- FPGA Editor (FPGA)

- ChipViewer (CPLD)

- JTAG Programmer (All CPLD families, all XC4000 families, and XC5200, Virtex, Virtex-E, Virtex-II, Spartan, SpartanXL, and Spartan-II FPGAs only)

The Design Manager manages your Xilinx designs. The Flow Engine implements your designs. The Flow Engine is closely integrated with the Design Manager, sharing many of the same menus and dialog boxes. You can use the Design Manager and Flow Engine together to perform the following functions.

- Target different devices

- Generate and export timing simulation data for external simulation tools

- Generate and export configuration data

See the "Implementation Tools Tutorial" chapter of the *Alliance Series* 3.1i Quick Start Guide or the "Basic Tutorial" chapter of the Foundation Series 3.1i Quick Start Guide for information on running through a typical implementation flow with Xilinx tools.

# **Design Flow**

You can use a variety of schematic and HDL tools for design entry. The netlist formats supported as inputs to the Design Manager are listed in the "Inputs and Outputs" section. After design entry, you can use the Design Manager and Flow Engine to process your design in the following basic steps.

- 1. Implementation of your design for a specific target device

- 2. Report generation showing the status of your design

- 3. Timing analysis for design verification

- 4. Export of your design for timing simulation and programming

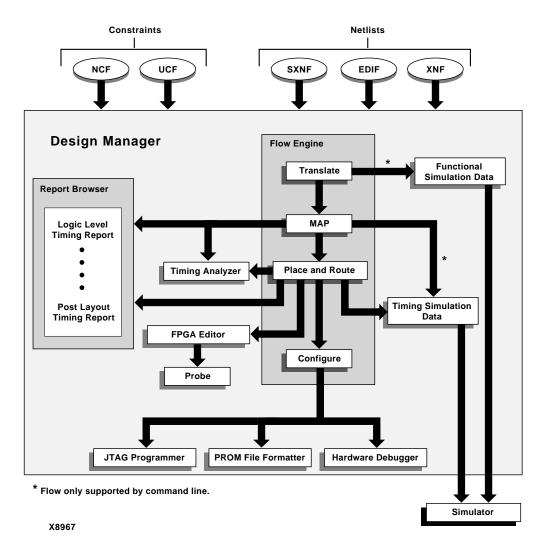

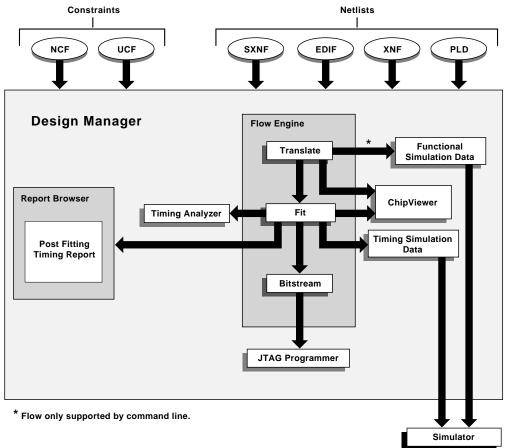

The following figures illustrate the processing steps through the Design Manager and Flow Engine for FPGAs and CPLDs.

# **Inputs and Outputs**

The Design Manager accepts the following file types as inputs.

| .edf, .edn,<br>.edif, .sedif | EDIF netlist file                |

|------------------------------|----------------------------------|

| .pld                         | PLUSASM file (CPLD only)         |

| .xnf, .xtf, .sxnf            | Xilinx hierarchical netlist file |

The Design Manager and Flow Engine output report, timing simulation, and programming files.

# **Architecture Support**

The Design Manager and Flow Engine support the following architecture families in this release. The XC9500 families compose the CPLD families. All other device families compose the FPGA families.

- Spartan<sup>™</sup>/XL/-II

- $Virtex^{TM}/-E/-II$

- XC9500<sup>TM</sup>/XL/XV

- $XC4000^{TM}E/L/EX/XL/XV/XLA$

- XC3000<sup>TM</sup>A/L

- XC3100<sup>™</sup>A/L

- XC5200<sup>TM</sup>

# **Design Manager Fundamentals**

You can perform multiple functions from within the Design Manager, such as launching Xilinx tools and managing your projects, design versions, and implementation revisions.

# **Projects**

The Design Manager window displays all Xilinx data related to a single project. When you create a project, a design version and implementation revision are automatically created so you always have a revision on which to run the software tools. A project includes all design versions and implementation revisions that are created as you implement your design. You can work with multiple projects, but only one is active at a time. The hierarchical structure in the Design Manager project view shows the relationships of the data elements to each other.

# **Design Versions**

You create your design using third party front-end tools that support schematic and Hardware Description Language (HDL) entry. The Design Manager reads in the design netlist and creates a design version in the Design Manager project view. If the design netlist changes, the Design Manager reads in the modified design and creates a new design version.

You can try modified versions of your design and easily keep track of them. Each new set of changes becomes a new design version and is assigned a design version name by the Design Manager. You can choose any one of the available design versions for processing.

When you create a new design version, a new implementation revision is automatically created. Each design version can contain multiple implementation revisions.

**Note** The Design Manager saves design versions in the Xilinx database format, not in the format of the front-end editor.

#### **Implementation Revisions**

After you create a design version, you can try different implementation strategies on your design. The data associated with each of these implementation strategies is called an implementation revision. Each implementation revision contains the data files and reports that are created based on a specific set of implementation strategies.

This method allows you to vary how your design is implemented in order to achieve your design objectives. For example, you can maximize speed and density in your design by controlling the implementation flow settings or by targeting a different device family better suited for your design.

**Note** If you are using an HDL flow, it is strongly recommended that you create a new synthesis netlist when you change FPGA or CPLD families. This ensures that the tools make the best use of the target device.

When you create a new revision either manually or automatically, the data from the "last" revision is copied to the new revision by default. The "last" revision is bottommost in the Design Manager project view. You can copy data from other revisions by setting options in the Copy Persistent Data field of the New Version or New Revision dialog box. You can also copy data from other revisions by using the Set Constraint File, Set Guide File(s), and Set Floorplan File(s) menu commands after the revision is created. If you want to change any of the implementation flow options, use the Options command.

Because you must always have an implementation revision on which to run the tools, at least one revision must always exist for each version in the Design Manager. If only one revision exists inside a version, you can only delete the revision by deleting the version.

### **Design Management Basic Procedure**

The typical procedure for managing a design is as follows.

- 1. In your design entry tool, create a design.

- 2. In your design entry tool, output your design as an EDF, EDIF, EDN, SEDIF, PLD, SXNF, XNF, or XTF file.

Note The PLD format is supported for CPLDs only.

- 3. In the Design Manager, open an existing project or create a new project in which to implement your logic design.

- 4. Implement your design.

- If necessary, choose a different target device in which to implement your design. The initial target device is specified in the input design or when you create a new implementation revision.

- Select implementation, simulation, and configuration options. You can use the default settings, an existing set of options, or set new options.

- Run your design implementation and create timing simulation files and a device programming file.

- 5. Review your design reports to verify that your design fits within the target device and that your timing requirements are met.

- 6. If your design requirements are not met, you can do any of the following and process your design again.

- Change your logic design.

- Choose a different target device, package, or speed grade.

- Define a different set of implementation, simulation, or configuration options.

# **Flow Engine Fundamentals**

The Flow Engine allows you to easily process and control the implementation of your design.

#### **Design Implementation**

When you process your design, the Flow Engine translates the design file into the Xilinx Native Generic Database (NGD) format. The Flow Engine then implements your design and generates bitstream data.

The Flow Engine allows you to control the implementation of your design in different ways. For example, if you are new to Xilinx software or want to quickly check your design, you can run the *automatic* Flow Engine using the Design Manager's Design  $\rightarrow$  Implement command. However, if you are an experienced user, you can open the Flow Engine from the Design Manager Tools menu and use the *interactive* Flow Engine to execute steps separately.

You can also fine tune your design by modifying your implementation, simulation, and configuration options. You can access these options through the Design Manager's Design  $\rightarrow$  Options command or the Flow Engine's Setup  $\rightarrow$  Options command. Use the Design Manager Options command with the automatic Flow Engine and the Flow Engine Options command with the interactive Flow Engine.

**Note** For more information on setting implementation, simulation, and configuration options, see the "Specifying Implementation Flow Options" section of the "Using the Design Manager and Flow Engine" chapter.

If you use the interactive Flow Engine, you can control how far to process your design using the Flow Engine's Setup  $\rightarrow$  Stop After command. In the Stop After dialog box, select a step as your target break point. For example, if you want to map, place, and route your design but not create device programming file, select Stop After Place&Route. A stop sign indicates where the process flow will stop.

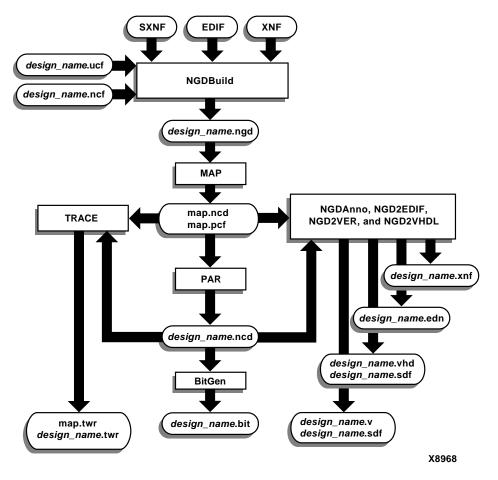

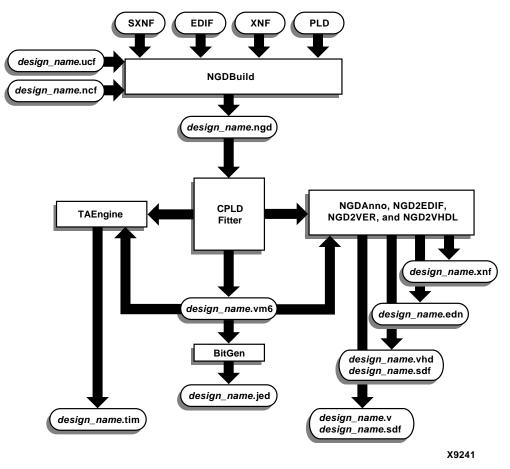

The following sections describe the steps run by the Flow Engine. The following figures shows these steps in detail for FPGAs and CPLDs.

Figure 1-3 Flow Engine Steps (FPGA)

Figure 1-4 Flow Engine Steps (CPLD)

#### Translate

During this step, the Flow Engine merges all of the input netlists. You can control aspects of the Translate step by setting implementation options using the Options command from the Design Manager or Flow Engine. The Flow Engine accomplishes this step by running NGDBuild, which is described in the "NGDBuild" chapter of the *Development System Reference Guide*.

The Translation Report is generated during this step. It contains warning and error messages from the three translation processes: conversion of the EDIF or XNF style netlist to the Xilinx NGD netlist, timing specification checks, and logical design rule checks. The report lists the following.

- Hierarchical blocks that are missing or cannot be translated

- Invalid or incomplete timing constraints

- Output contention, loadless outputs, and sourceless inputs

#### Map (FPGA)

During this step, the Flow Engine maps a logical design to a Xilinx FPGA. The input is an NGD file, which contains a logical description of the design and macro library (NMC) files. The Flow Engine first performs a logical Design Rule Check (DRC) on the design in the NGD file. It then maps the logic to the components in the target Xilinx FPGA. The output design is a Native Circuit Description (NCD) file that physically represents the design mapped to the components in the Xilinx FPGA. You can control aspects of the Map step by setting implementation options using the Options command from the Design Manager or Flow Engine. The Flow Engine accomplishes the Map step by running the MAP program, which is described in the "MAP—The Technology Mapper" chapter of the Development System Reference Guide.

The Map Report is generated during this step. It contains warning and error messages detailing logic optimization and logic mapping to physical resources. The report lists the following information.

- Removed logic

- Added or expanded logic due to speed optimization

- Number and percentage of used CLBs, IOBs, flip-flops, and latches

- Use of architecture-specific resources such as global buffers and boundary scan logic

The Logic Level Timing Report can also be generated during this step. This report provides a summary analysis of your timing constraints based on block delays and absolute minimum route delays. You can use this report to determine whether you need to revise the timing constraints in your design or create more efficient logic. This feature provides a useful analysis of your timing constraints without the wait required for place and route. To obtain a detailed analysis, use the Timing Analyzer tool after you place and route your design.

#### Place&Route (FPGA)

During this step, the Flow Engine takes the NCD file produced during Map and places and routes the design to produce a routed NCD file. The output NCD file can also act as a guide file if you place and route the design again. You can control aspects of the Place and Route step by setting implementation options using the Options command from the Design Manager or Flow Engine. To accomplish this step, the Flow Engine runs the PAR program, which is described in the "PAR—Place and Route" chapter of the *Development System Reference Guide*.

The Place and Route Report is generated during this step. It contains the following information.

- Design score

- Number of signals not completely routed

- Timing performance

The Pad Report is generated during this step. It lists your design's pinout sorted by signal name, and then by pin number.

By default, the Post Layout Timing Report is also generated during this step. Depending on the report settings chosen, this report provides an analysis of the maximum clock speed and constraint information for a placed and routed design. To obtain a detailed analysis, use the Timing Analyzer tool.

The Asynchronous Delay Report is also generated during this step. This report lists all nets in the design and the delays of all loads on the net.

#### Fit (CPLD)

During Fit, the Flow Engine launches the CPLD Fitter to minimize and collapse the combinatorial logic of your design so that it requires the least number of macrocell and product term resources. It also partitions and maps your design to fit within the architecture of the CPLD. You can control aspects of this step by setting implementation options using the Options command from the Design Manager or Flow Engine.

A Post Fitting Timing Report can also be generated during this step. The timing report provides a brief analysis of the maximum clock speed for the design after it is fitted. To obtain a detailed analysis, use the Timing Analyzer tool.

### Timing (Sim)

The Flow Engine runs this step to produce timing simulation data. The data that is produced depends on the simulation options you set using the Options command from the Design Manager or Flow Engine. To accomplish this step, the Flow Engine runs NGDAnno and one of the following tools, all of which are described in the *Development System Reference Guide*.

- NGD2EDIF

- NGD2VER

- NGD2VHDL

### **Configure (FPGA)**

After the design has been completely routed, the Flow Engine configures the device so that it can execute the desired function. Using a fully routed NCD file as input, it produces a configuration bitstream, a binary file with a .bit extension. The BIT file contains all of the configuration information from the NCD file defining the internal logic and interconnections of the FPGA, plus device-specific information from other files associated with the target device. The binary data in the BIT file can then be downloaded into the FPGA's memory cells, or it can be used to create a PROM file. You can control aspects of this step by setting configuration options using the Options command from the Design Manager or Flow Engine. The Flow Engine accomplishes this step by running BitGen, which is described in the "BitGen" chapter of the *Development System Reference Guide*.

# Bitstream (CPLD)

During this step, the Flow Engine produces a JED programming file. The JTAG Programmer uses this file to configure CPLD devices. You can control aspects of this step by setting implementation options using the Options command from the Design Manager or Flow Engine.

# **Smart Flow Engine**

When the Flow Engine is first invoked, it automatically looks for changes made to certain files. If the Flow Engine detects changes, it restarts the flow for the implementation revision as follows. This feature is called the Smart Flow Engine.

- If a previously set target break point has already been reached at the time you launch the Flow Engine, the Smart Flow Engine removes the break point and implements the next process in the flow.

- If any of the following changes are made, the Smart Flow Engine determines which process to rerun.

- Changes to implementation flow options from the Options dialog box or Template Manager

- Changes to design, constraints, guide, or output files

The following table shows which flow process the Flow Engine reruns if you make changes to a particular file.

Table 1-1 Smart Flow Engine Change Detection

| File Changed                                                                     | Process Rerun       |

|----------------------------------------------------------------------------------|---------------------|

| design_name.ucf (or custom<br>constraints file)<br>design_name.ncf               | Translate           |

| <i>design_name</i> .ngd<br><i>design_name</i> .mfp (or custom<br>floorplan file) | Map (FPGA)          |

| map.ncd<br>guide.ncd (or custom guide file)                                      | Place&Route (FPGA)  |

| design_name.ngd<br>design_name.gyd                                               | Fit (CPLD)          |

| <i>design_name</i> .ncd                                                          | Timing (Sim) (FPGA) |

| design_name.vm6                                                                  | Timing (Sim) (CPLD) |

| File Changed    | Process Rerun    |

|-----------------|------------------|

| design_name.ncd | Configure (FPGA) |

| design_name.vm6 | Bitstream (CPLD) |

Table 1-1 Smart Flow Engine Change Detection

The Smart Flow Engine notifies the Design Manager of the state and status of your implementation revision and the Design Manager updates the information in the main window.

The Flow Engine checks for changes related to successfully completed processes. If a process did not complete successfully, the Flow Engine does not look for changes related to this process but automatically restarts the flow at this process or, if appropriate, at a previous process. If the Flow Engine is already open and you want to check for changes, use the Setup  $\rightarrow$  Update Flow command.

# Chapter 2

# **Getting Started**

This chapter leads you through the basic operation of the Design Manager and Flow Engine. This chapter contains the following sections.

- "Preparing the Input Design File"

- "Starting and Exiting the Design Manager"

- "Starting and Exiting the Flow Engine"

- "Using the Interface"

# Preparing the Input Design File

Create the input design in your design entry tool and save it in one of acceptable formats described in the "Inputs and Outputs" section of the "Introduction" chapter.

# Starting and Exiting the Design Manager

The Design Manager runs on PCs and workstations. You can start the Design Manager as a standalone tool on the PC or from the command line. Use the following procedures to start and exit the Design Manager.

# Starting as a Standalone Tool

If you installed the Design Manager as a standalone tool on a PC, click the Design Manager icon (shown in the following figure) on the Windows desktop or select dsgnmgr.exe from the Windows  $98^{\text{@}}$ , Windows  $2000^{\text{@}}$ , or Windows NT<sup>®</sup> Start button.

# Starting from the Command Line

To start the Design Manager from the  $\text{UNIX}^{(\!\!R\!)}$  or  $\text{DOS}^{^{\text{TM}}}$  command prompt, enter one of the following commands.

- dsgnmgr

- xilinx

# **Exiting the Design Manager**

To exit the Design Manager, select the  $\texttt{File} \rightarrow \texttt{Exit}$  menu command. A confirmation box appears. Click **Yes** to exit the Design Manager.

# Starting and Exiting the Flow Engine

The Flow Engine runs on PCs and workstations. Use the following procedures to start and exit the Flow Engine.

# **Starting from the Alliance Series**

To launch the Flow Engine from the Alliance Design Manager, select an implementation revision and do one of the following.

- Select Tools  $\rightarrow$  Flow Engine.

- Click the Flow Engine toolbox button, shown in the following figure.

# **Starting from the Foundation Series**

To launch the Flow Engine from the Foundation Project Manager, select the Implementation phase button on the project flow chart, shown in the following figure.

**Note** For more information about accessing and using the Flow Engine from the Foundation Project Manager, see the "Design Implementation" chapter of the *Foundation Series User Guide*.

# **Exiting the Flow Engine**

To exit the Flow Engine, select the  $Flow \rightarrow Close$  command.

# Using the Interface

This section describes the elements that compose the Design Manager and Flow Engine interfaces and how to use them.

# **Main Window**

This section describes the Design Manager and Flow Engine main windows, their menus, toolbar, and status bar. By default, the main

window displays a menu bar and toolbar at the top and status bar at the bottom of the window. You can hide the toolbar or status bar from view by selecting the Toolbar or the Status Bar commands, respectively, from the View menu. In the Design Manager, the toolbox also appears by default. You can hide it from view by selecting the Toolbox command from the View menu.

#### **Design Manager Window**

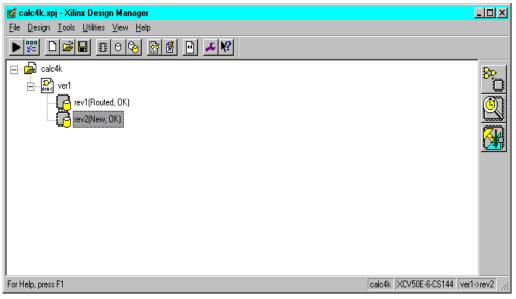

To work with the Design Manager, you must create a project. See the "Creating a New Project" section of the "Using the Design Manager and Flow Engine" chapter for information. After you create a project, the Design Manager window appears configured for the loaded design, as shown in the following figure.

#### Figure 2-1 Design Manager Window

The Design Manager project view displays design version and implementation revision icons. The toolbox allows you to launch Xilinx tools. You can select Design Manager commands from the menus and toolbar.

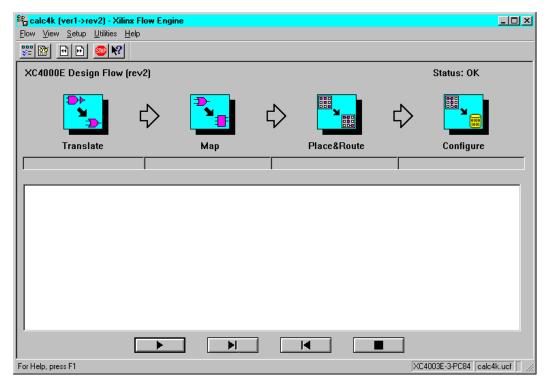

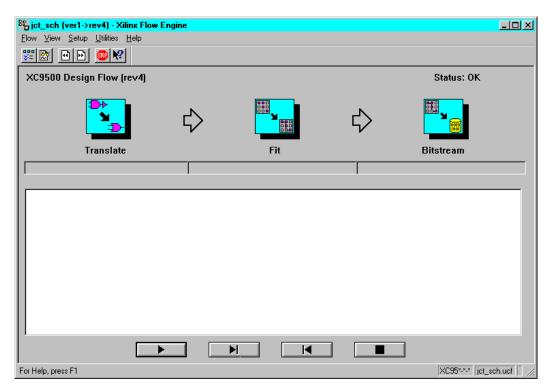

#### **Flow Engine Window**

You can open the Flow Engine automatically through the Design Manager implementation process or manually from the Design Manager Tools menu or toolbox. See the "Implementing a Design from the Design Manager" or "Implementing a Design from the Flow Engine" section of the "Using the Design Manager and Flow Engine" chapter for descriptions of the different ways to open the Flow Engine and implement a design. When you open the Flow Engine, the Flow Engine window appears as shown in the following figures.

Figure 2-2 Flow Engine Window (FPGA)

#### Figure 2-3 Flow Engine Window (CPLD)

Process indicators in the Flow Engine main window show which step in the design flow is currently processing. The arrows between each step turn black after the previous step is completed. Below each process indicator, a progress field shows the status of each processing step, whether Running, Completed, Aborted, or Failed. During the Place&Route process, the progress field shows additional information about the processing step, whether Running, Placing, Routing, Improving, or Reporting.

**Note** For small designs, Place&Route may complete before all of the additional processing step information can be displayed. Reporting is only shown if you selected the Post Layout Timing Report setting in the Timing Report tab of the Implementation Options dialog box. See the online help for more information on this setting.

You can control each step in the processing of your design by using the run control buttons at the bottom of the Flow Engine main window. Select Flow Engine commands from the menus and toolbar.

#### Title Bar

The title bar displays the program name and the name of the currently loaded design.

#### Menu Bar

All of the Design Manager commands are available in the pull-down menus of the Design Manager window after a design is loaded. Flow Engine commands are available in the pull-down menus of the Flow Engine window.

#### **Toolbar Buttons**

You can access frequently used commands by clicking the appropriate toolbar button. See the online help for an explanation of each toolbar button.

#### **Toolbox Buttons**

You can access the available set of Xilinx interactive tools from the Design Manager Tools menu or from the toolbox. To launch a tool from the toolbox, click the appropriate toolbox button. See the online help for a detailed explanation of the toolbox.

#### Status Bar

By default, the status bar appears at the bottom of the main window. When you select a menu command, a brief description of the command's function appears in the status bar. As the software processes, status messages are dynamically updated and displayed.

### **Dialog Boxes**

Many menu commands display dialog boxes in which you can enter information and set options.

#### **Common Fields**

The fields shown in the following table are common to most dialog boxes.

| Dialog Box Field | Function                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------|

| ОК               | Closes the dialog box and implements the<br>intended action according to the settings in<br>the dialog box |

| Cancel           | Closes the dialog box without effecting any action                                                         |

| Help             | Displays information on the dialog box                                                                     |

Table 2-1 Common Dialog Box Fields

### **Using Help**

The Design Manager and Flow Engine contain context-sensitive help and a Help menu. You can obtain help on commands and procedures with the Help menu or by selecting the Help toolbar button. In addition, the dialog boxes associated with many commands have a Help button that you can click to obtain context-sensitive help.

**Note** The online help includes information on menu commands, dialog boxes, and implementation options.

#### Help Menu

Use the following Help menu commands to obtain help.

- The Help Topics command opens Help and lists the online help topics available. From the Contents page, you can jump to command information or step-by-step instructions. After you open help, you can click the Help Topics button in the Help window whenever you want to return to the help topic list.

- The Online Documentation command provides access to the Software Manuals Online.

- The Xilinx on the Web command provides access to the support.xilinx.com page and the Xilinx home page on the Web.

- The About Design Manager command opens a popup window that displays the registration and version number of the Design Manager software and a copyright notice.

• The About Flow Engine command opens a popup window that displays the registration and version number of the Flow Engine software and a copyright notice.

#### **Toolbar Help Button**

You can obtain context-sensitive help from the toolbar as follows.

1. Click the Help button in the toolbar.

The cursor changes to a question mark.

2. With the left mouse button, click the menu item or toolbar button for which you want help.

Help appears for the selected command or option.

Note You can also press shift F1 to obtain context-sensitive help.

#### F1 Key

Pressing the F1 key on a dialog box displays help on that dialog box. Pressing the F1 key is the same as selecting Help  $\rightarrow$  Help Topics, if no dialog boxes are displayed.

#### Help Button in Dialog Boxes

Many of the dialog boxes have a Help button that you can click to obtain help for the dialog box with which you are working. You can also press **Alt H** on your keyboard while positioned over the dialog box to obtain help.

# **Chapter 3**

# Using the Design Manager and Flow Engine

This chapter shows you how to perform common design tasks in the Design Manager and Flow Engine. These procedures are described in the following sections.

- "Creating a New Project"

- "Creating a New Design Version"

- "Creating a New Implementation Revision"

- "Setting a Part"

- "Deleting Items from the Project View"

- "Specifying Implementation Flow Options"

- "Implementing a Design from the Design Manager"

- "Copying Constraints, Guide, and Floorplan File Data"

- "Viewing Reports"

- "Producing Timing Reports"

- "Generating Pin Locking Constraints"

- "Producing Timing Simulation Data"

- "Exporting Design Data"

- "Archiving a Project"

Following are advanced procedures you can use after you are comfortable with the preceding basic procedures. The advanced procedures may help improve your run time and design performance.

- "Implementing a Design from the Flow Engine"

- "Placing and Routing Non-Timing Driven Designs"

- "Running Multiple Place and Route Passes"

- "Running Re-Entrant Routing on FPGAs"

- "Working with Templates"

**Note** Most commands run from the Design Manager require that an implementation revision be selected.

## **Creating a New Project**

When you open the Design Manager for the first time, you must create a new project for your design before you can use the Design Manager. A project includes all design versions, implementation revisions, reports, and any other Xilinx data created while you work with a design.

The Design Manager graphically displays information about these items in the project view. When you create a new project, you specify a design to open and a directory for the project. You can create as many projects as you want, but you can only work with one at a time. The following procedure explains how to create a new project by importing a design.

1. In the Design Manager, select  $File \rightarrow New$  Project or click the New Project toolbar button.

| New Project      |           | ×            |

|------------------|-----------|--------------|

| Input Design:    | []        | Browse       |

| Work Directory:  |           | Browse       |

| <u>C</u> omment: |           |              |

|                  | OK Cancel | <u>H</u> elp |

The dialog box shown in the following figure appears.

#### Figure 3-1 New Project Dialog Box

- 2. In the Input Design field, specify a design file to open, or click the **Browse** button to select a file from the Open dialog box. Use only the file formats listed in the "Inputs and Outputs" section of the "Introduction" chapter.

- 3. To change the default work directory, type a path in the Work Directory field or use **Browse** to select a directory.

**Note** The Design Manager automatically creates a subdirectory named xproj under the input design directory and uses it as the work directory. The Design Manager uses the xproj subdirectory to store all the data files for the project.

- 4. Enter any comments in the Comment field. Use this field to note options and strategies.

- 5. In the New Project dialog box, click OK.

After your design is loaded, the Design Manager is configured for the loaded design.

## **Creating a New Design Version**

While working on a project, you may need to modify the initial input design and bring these changes into an existing project in the Design Manager. You can do this with the New Version command. The Design Manager automatically assigns a name for the design version, but you can enter a different name in the New Version dialog box. A new implementation revision is automatically created when you create a new version.

**Note** When implementing your design, the New Version dialog box appears automatically if you made changes to your design netlist.

1. In the Design Manager, select  $\texttt{Design} \rightarrow \texttt{New Version}$ .

The dialog box shown in the following figure appears.

| New Version                                           | × |

|-------------------------------------------------------|---|

| Both the new version and new revision will be created |   |

| ⊻ersion Name: ver2                                    |   |

| Version <u>C</u> omment:                              |   |

| Part: XC4003E-3-PC84 Select                           |   |

| Revision <u>N</u> ame: rev1                           |   |

| Revision Comment:                                     |   |

| Copy Persistent Data                                  |   |

| Constraints File: Last Revision(ver1->rev1)           | ] |

| Floorplan File(s): None                               | ] |

| Guide File(s): None                                   | ] |

| OK Cancel <u>H</u> elp                                |   |

Figure 3-2 New Version Dialog Box

2. Enter a name in the Version Name field if you do not want to use the default name. Use the characters A through Z, a through z, 0 through 9, period (.), underscore (\_), or hyphen (-) only. The name should be unique within the project.

- 3. Enter any comments in the Version Comment field. Use this field to note options and strategies.

- 4. To choose a device from the Part Selector dialog box, click **Select**.

The dialog box shown in the following figure appears.

| Part Selector    | ×            |

|------------------|--------------|

| Family: C9500XV  | ОК           |

| Device: All      | Cancel       |

| Package: All     | <u>H</u> elp |

| Speed Grade: All |              |

|                  |              |

#### Figure 3-3 Part Selector Dialog Box

- 5. Specify the desired settings in the Family, Device, Package, and Speed Grade drop-down list boxes.

- 6. Click OK.

- 7. Enter the name for the new implementation revision in the Revision Name field. Use the characters A through Z, a through z, 0 through 9, period (.), underscore (\_), or hyphen (-) only. The name should be unique within the design version.

- 8. Enter any comments in the Revision Comment field. Use this field to note options and strategies.

- To copy data to your new revision from another revision or from a custom file, use the settings in the Copy Persistent Data field. Select None if you do not want to copy data.

**Note** By default, the Design Manager copies floorplan and constraints file data from the "last" revision. The "last" revision is the bottommost revision in the Design Manager project view. When initially creating a project, the Design Manager copies constraints file data from the project directory to the revision directory.

10. Click **ok** in the New Version dialog box.

The Design Manager displays a new design version and implementation revision icon in the project view.

## **Creating a New Implementation Revision**

After you create a design version, you can try different implementation strategies on that design. For instance, you can reduce area, increase speed, and vary placement effort. Each set of implementation strategies makes up a new implementation revision. Generating new implementation revisions allows you to vary how your design is implemented in order to achieve your design objectives.

You can select new options or target a new device to change the way your design is implemented. Targeting a new device allows you to try your design in various devices to determine the most suitable fit. For example, if a particular device proves to be too large or too slow for your needs, you can select a smaller or faster target device from a different family.

**Note** If you are using an HDL flow, it is strongly recommended that you create a new synthesis netlist when you change FPGA or CPLD families. This ensures that the tools make the best use of the target device.

When you create an implementation revision, an implementation revision icon is placed in the Design Manager project view. Each time you create a new implementation revision, a default revision name and the part used in the "last" revision are automatically selected. If you want to change these default values, you can enter your own revision name and change the target part. The implementation revision name, implementation state, implementation status, and any user comments for the implementation revision are indicated next to its icon in the project view when you process the implementation. Replace or delete implementation revisions that are no longer useful.

- 1. In the Design Manager project view, select a design version icon.

- 2. Choose  $Design \rightarrow New Revision$  from the Design Manager menu or click the New Revision toolbar button.

| New Revision                                          | × |

|-------------------------------------------------------|---|

| The new revision will be created in specified version |   |

| Version Name: Ver1                                    |   |

| Version <u>C</u> omment:                              |   |

| Part: XC4003E-3-PC84 Select                           |   |

| Revision <u>N</u> ame: rev2                           |   |

| Revision Comment:                                     |   |

| Copy Persistent Data                                  |   |

| Constraints File: Last Revision(ver1->rev1)           | • |

| Floorplan File(s): None                               | • |

| Guide File(s): None                                   | • |

| OK Cancel <u>H</u> elp                                |   |

The dialog box shown in the following figure appears.

Figure 3-4 New Revision Dialog Box

3. To choose a device from the Part Selector dialog box, click **Select**.

| Part Selector    | ×            |

|------------------|--------------|

| Family: C9500XV  | ОК           |

| Device: All      | Cancel       |

| Package: All     | <u>H</u> elp |

| Speed Grade: All |              |

|                  |              |

The dialog box shown in the following figure appears.

#### Figure 3-5 Part Selector Dialog Box

- 4. Specify the desired settings in the Family, Device, Package, and Speed Grade drop-down list boxes.

- 5. Click OK.

- 6. Enter a name for the new implementation revision in the Revision Name field. Use the characters A through Z, a through z, 0 through 9, period (.), underscore (\_), or hyphen (-) only. The name should be unique within the design version.

- 7. Enter any comments in the Revision Comment field. Use this field to note options and strategies.

- To copy data to your new revision from another revision or from a custom file, use the settings in the Copy Persistent Data field. Select None if you do not want to copy data.

**Note** By default, the Design Manager copies floorplan and constraints file data from the "last" revision. The "last" revision is the bottommost revision in the Design Manager project view. When initially creating a project, the Design Manager copies constraints file data from the project directory to the revision directory.

9. In the New Revision dialog box, click OK.

The Design Manager creates a new implementation revision and displays its icon in the project view.

## Setting a Part

Use the Set Part command to set the part number for a new implementation revision. You can change the part number to select the device best suited for your design.

**Note** You cannot change the part number of an existing implementation revision.

1. In the Design Manager, select  $\texttt{Design} \rightarrow \texttt{Set Part}$  or click the Set Part toolbar button.

| Set Part                                              | × |

|-------------------------------------------------------|---|

| The new revision will be created in specified version |   |

| Version Name: ver1                                    |   |

| Version <u>C</u> omment:                              |   |

| Part: XC4003E-3-PC84 Select                           |   |

| Revision <u>N</u> ame: rev2                           |   |

| Revision C <u>o</u> mment:                            |   |

| Copy Persistent Data                                  |   |

| Constraints File: Last Revision(ver1->rev1)           |   |

| Floorplan File(s): None                               | ⊡ |

| Guide File(s): None                                   | ⊡ |

| OK Cancel <u>H</u> elp                                |   |

The dialog box shown in the following figure appears.

Figure 3-6 Set Part Dialog Box

2. Click Select to choose a device from the Part Selector dialog box.

| Part Selector    | ×            |

|------------------|--------------|

| Family: XC9500XV | OK           |

| Device: All      | Cancel       |

| Package: All     | <u>H</u> elp |

| Speed Grade: All |              |

|                  |              |

The dialog box shown in the following figure appears.

Figure 3-7 Part Selector Dialog Box

- 3. Specify the desired settings in the Family, Device, Package, and Speed Grade drop-down list boxes.

- 4. Click or.

- 5. In the Set Part dialog box, click OK.

The Design Manager displays the new implementation revision in the project view and the part number in the status bar.

## **Deleting Items from the Project View**

#### \rm Warning

When deleting an item from the project view, the Design Manager deletes the item and all accompanying data. Deleted data cannot be recovered.

Use the Delete command to delete a project, design version, or implementation revision from the project view.

- 1. In the Design Manager project view, select the icon of the project, design version, or implementation revision that you want to delete.

- 2. Select  $\texttt{Design} \rightarrow \texttt{Delete}$ .

- 3. A confirmation box appears asking if you want to delete the selected item. Click OK.

## **Specifying Implementation Flow Options**

You can specify options that control how the Flow Engine implements a design, configures a device, creates netlist files, and generates reports, timing data, and configuration data. The available options depend on the target device family.

You can specify these options by choosing settings within the Options dialog box. You can set implementation, simulation, and configuration options. The implementation options control how the software translates, maps, places, routes, and optimizes an FPGA design and how it translates and fits a CPLD design. The simulation options control the creation of netlists in terms of Xilinx primitives, allowing you to perform simulation and back-annotation. The configuration options define the initial configuration parameters of a device, the startup sequence, and readback capabilities. See the online help for information on each implementation, simulation, and configuration option.

Changes you make in the Options dialog box are applied to the implementation revision that was selected when you invoked the dialog box. The Flow Engine picks up changes after the currently running step is finished if a flow is running, or when you implement your design if no flow is running.

- 1. Open the Options dialog box using one of the following methods.

- From the Design Manager, select  $\texttt{Design} \rightarrow \texttt{Options}$ .

- From the Flow Engine, select  $\texttt{Setup} \rightarrow \texttt{Options}$ .

- Click the Set Options toolbar button.

| Options                    |          |    |       |                        |

|----------------------------|----------|----|-------|------------------------|

| Place & Route Effort Leve  | el       |    |       |                        |

| <u>F</u> astest<br>Runtime | <u>'</u> | •  | · · · | <u>H</u> igh<br>Effort |

| Program Options            |          |    |       |                        |

| Implementation:            | Default  |    | •     | Edit Options           |

| Si <u>m</u> ulation:       | OFF      |    | •     | Edit Options           |

| <u>C</u> onfiguration:     | Default  |    | •     | Edit Options           |

|                            |          | OK | C.    | ancel <u>H</u> elp     |

If you are targeting an FPGA, the dialog box shown in the following figure appears.

Figure 3-8 Options Dialog Box (FPGA)

| Op | tions                      |                |                 |              |                       | × |

|----|----------------------------|----------------|-----------------|--------------|-----------------------|---|

|    | - Implementation Options - |                |                 |              |                       |   |

|    | CPLD Optimization Style    | e:             |                 |              |                       |   |

|    | O <u>D</u> ensity          | • Balanced     | ○ <u>S</u> peed | <u>○ U</u> : | ser Defined           |   |

|    |                            |                |                 |              |                       | . |

|    |                            | Balanced Optir | nization        | <b>V</b>     | Edit Options          |   |

|    |                            |                |                 |              |                       |   |

|    | - Simulation Options       |                |                 |              |                       |   |

|    | Si <u>m</u> ulation:       | OFF            |                 | •            | E <u>d</u> it Options | J |

|    |                            |                | ОК              | Cancel       | <u>H</u> elp          |   |

If you are targeting a CPLD, the dialog box shown in the following figure appears.

#### Figure 3-9 Options Dialog Box (CPLD)

- 2. If you are targeting an FPGA, do the following.

- a) Select a Place & Route Effort Level setting. A setting closer to High Effort provides better place and route results at the expense of longer run times.

- b) To modify the default implementation options, click the Edit Options button to the right of the Implementation field. These options affect the Translate, Map, and Place&Route steps in the implementation flow.

- c) To create timing simulation data, select one of the simulators in the drop-down list box next to the Simulation field. To edit the default option settings, click the Edit Options button to the right of the Simulation field. Select OFF if you do not want to generate simulation data.

**Note** The Edit Options button is disabled if you set Simulation to OFF.

d) To modify the default configuration options, click the Edit Options button to the right of the Configuration field. These options affect the Configure step in the implementation flow. Select JTAG if you want to program FPGAs using JTAG software and the JTAG port. Select OFF if you do not want to generate configuration data.

Note The Edit Options button is disabled if you set Configuration to OFF. For information on setting Express Mode configuration for the SpartanXL family, see http://support.xilinx.com/ techdocs/2328.htm.

- e) Click OK.

- 3. If you are targeting a CPLD, do the following.

- a) In the Implementation Options field, select Area, Balanced, or Speed for the CPLD Optimization Style, or select User Defined and choose a set of options to edit from the dropdown list box. To edit the options, click the Edit Options button. These options affect the Translate, Fit, and Bitstream steps in the implementation flow.

- b) To create timing simulation data, select one of the simulators in the drop-down list box next to the Simulation field. If you want to edit the default option settings, click the Edit Options button to the right of the Simulation field. Select OFF if you do not want to generate simulation data.

**Note** The Edit Options button is disabled if you set Simulation to OFF.

- c) Click OK.

- 4. Click **OK** to maintain your settings and exit the Options dialog box.

## Implementing a Design from the Design Manager

You can implement your design in an automatic step from the Design Manager. When you implement your design automatically, the Flow Engine implements your design to completion.

You can implement your design with default values set for copying guide, floorplan, and constraint file data and default values for implementation flow options, or you can set your own values. If you want to set your own values, follow the procedures described in the "Specifying Implementation Flow Options" and "Copying Constraints, Guide, and Floorplan File Data" sections before implementing your design.

### Implementing a Design Automatically

The following procedure describes how to implement a design automatically from the Design Manager.

1. Select  $\texttt{Design} \to \texttt{Implement}$  or click the Implement toolbar button.

One of the following occurs.

- If you altered your source design, the software opens the New Version dialog box. See the "Creating a New Design Version" section for information on setting the options in this dialog box. The Design Manager creates a new version and revision and the Flow Engine implements this new revision.

- If you did not alter the source design or part type, the Smart Flow Engine appears and implements your design starting with the appropriate step.

When processing is complete, the Smart Flow Engine closes and the Implement Status dialog box appears.

**Note** The Flow Engine is run on the "last" revision regardless of the currently selected revision. To implement a revision other than the "last" one, follow the procedure in the following section.

2. In the Implement Status dialog box, click **Reports** to view the reports generated by the Flow Engine or click **View Log File** to view the implementation log file.

**Note** At this point you can also perform timing simulation, if you set options as described in the "Producing Timing Simulation Data" section, and program the device. Timing simulation is described in the interface user guide for your system. Device programming is described in the programmer user guide for your system.

### **Re-Implementing a Design**

If you want to automatically implement an implementation revision that is not your "last" revision, use the following procedure.

- 1. Select an implementation revision.

- 2. Right-click the selected revision.

- 3. Select Re-Implement.

The Flow Engine determines where it should start running in the flow and implements your revision to completion.

## Copying Constraints, Guide, and Floorplan File Data

You can copy constraints, guide, and floorplan file data to an existing implementation revision. Copy this data to your implementation revision to control the implementation of your design. Specify the data you want to copy using the Design Manager. The following sections describe how to copy this data to an existing revision.

- "Setting a Constraints File"

- "Setting a Guide File"

- "Setting Floorplan Files"

**Note** The following procedures describe how to copy data to an existing implementation revision. If you want to copy data to a new design version or implementation revision, use the Copy Persistent Data option described in the "Creating a New Design Version" or "Creating a New Implementation Revision" section.

### Setting a Constraints File

You can use a user constraints (UCF) file to control the implementation of your design. The user constraints file can contain information on where to place I/O pins and blocks of logic and timing requirements for the design.

If you want to control the implementation of your design with a user constraints file, you can specify this file in the Set Constraints File dialog box. The software tries to implement your design to meet the specified timing requirements and other constraints. 1. In the Design Manager, select  $\texttt{Design} \rightarrow \texttt{Set Constraints}$ File to open the dialog box shown in the following figure.

| Set Constraints File                           | × |

|------------------------------------------------|---|

| Changes will affect the selected revision only |   |

| Copy Constraints Data From                     |   |

| Enable Constraints                             |   |

| OK Cancel <u>H</u> elp                         |   |

Figure 3-10 Set Constraints File Dialog Box

- 2. Make sure the Copy Constraints Data From and Enable Constraints options are selected.

- 3. In the drop-down list box, select one of the following.

- A revision that contains the user constraints file (UCF) you want to use for this implementation

- None if you do not want to copy constraints data

- Custom to guide from a specific file

If you select Custom, the following dialog box appears. Type the name of a specific file in the Constraints File field or click **Browse** to open a file selection dialog box in which you can choose an existing UCF file.

**Note** By default, the Copy the Constraints File to the Revision and Operate Using the Revision Copy option is enabled and the UCF file is automatically copied into each new revision directory. Each revision reads the UCF file in its local directory. If you want each revision to read the same UCF file stored in the project directory, deselect this option.

| Custom                                                                         | ×              |

|--------------------------------------------------------------------------------|----------------|

| Constraints File:                                                              |                |

| calc4k.uci                                                                     | <u>B</u> rowse |

| Copy the Constraints File to the revision and operate using the revision copy. |                |

| OK Cancel                                                                      | <u>H</u> elp   |

#### Figure 3-11 Set Constraints File Custom Dialog Box

4. In the Set Constraints File dialog box, click OK.

When you implement the design, the Flow Engine uses the copied data to constrain the implementation.

### Setting a Guide File

You can select a guide file or a previously routed or fitted implementation revision to use as a guide for implementation. The procedure for guiding your implementation is the same for FPGAs and CPLDs. However, the way the design is guided differs between the two.

When guiding an FPGA design, the software attempts to use the guide for placing logic and routing signals for the current implementation revision of the design. This can reduce the amount of time the software takes to place and route. Guiding a design for an FPGA works as follows.

- If a component in the new design has the same name as that of the guide design or file, it is placed as in the guide.

- If an unnamed component in the new design is the same type as a component within the guide, it is placed as in the guide.

- If the signals attached to a component in the new design match the signals attached to the component of the guide, the pins are swapped to match the guide, where possible.

- If the signal names in the input design match the guide, and have the same sources and loads, the routing information from the guide design is copied to the new design.

After these components and signals are placed and routed, the remainder of the logic is placed and routed. If you have made only

minor changes to your design and want the remaining logic placed and routed exactly as in your guide design, select the Match Guide Design Exactly option. This option locks the placement and routing of the matching logic so that it cannot change to accommodate additional logic.

**Note** Setting the Match Guide Design Exactly option is not recommended for synthesis-based designs.

For CPLDs, each time you implement your design, a guide (GYD) file is created which contains your pinout information. You can reuse this file in subsequent iterations of your design if you want to keep the same pinouts. If you select a valid implementation revision or guide file name, the pinouts from that file will be used when the design is processed.

**Note** You can override guide file locations by assigning locations in your design file or constraints file.

1. In the Design Manager, select  $Design \rightarrow Set$  Guide File(s) to open the dialog box shown in the following figure.

| Set Guide File(s)                                               | × |

|-----------------------------------------------------------------|---|

| Changes will affect the selected revision and all new revisions |   |

|                                                                 |   |

| 🔽 Copy Guide Data From: 🛛 None 💌                                |   |

|                                                                 |   |

| Enable Guide                                                    |   |

| Match Guide Design Exactly                                      |   |

| OK Cancel <u>H</u> elp                                          |   |

#### Figure 3-12 Set Guide File(s) Dialog Box

- 2. Make sure the Copy Guide Data From and Enable Guide options are selected.

- 3. In the drop-down list box, select one of the following.

- A revision that contains the guide file you want to use for this implementation

- None if you do not want to copy a guide file