# SmartGen Cores Reference Guide

#### Table of Contents

### Actel Corporation, Mountain View, CA 94043

© 2006 Actel Corporation. All rights reserved.

Part Number: 5-02-9108-16

Release: February 2006

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose.

Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

### Trademarks

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Acrobat Reader is a trademark of Adobe Systems, Inc.

Windows is a registered trademark of Microsoft in the U.S. and other countries.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

|    | Introduction                      | 5      |

|----|-----------------------------------|--------|

|    | Symbols                           |        |

|    | Your Comments                     |        |

|    | Online Help                       | 5      |

| 1  | Arithmetic Cores                  | 7<br>4 |

| 2  | Comparators                       |        |

| 3  | Converters                        | 5      |

| 4  | Linear Binary Counters            | 1      |

| 5  | Decoder                           | 9      |

| 6  | I/Os                              | 3      |

| 7  | Logic                             | 3      |

| 8  | Multiplexer                       | 7      |

| 9  | Minicores                         | 1      |

| 10 | PLLs and Clock Conditioning Cores |        |

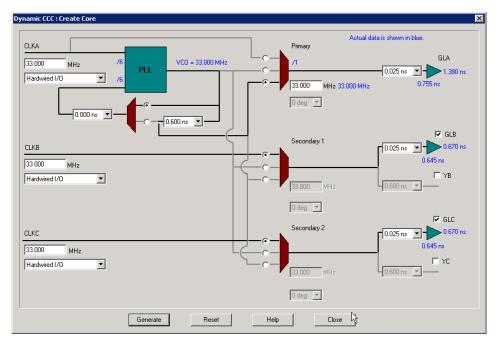

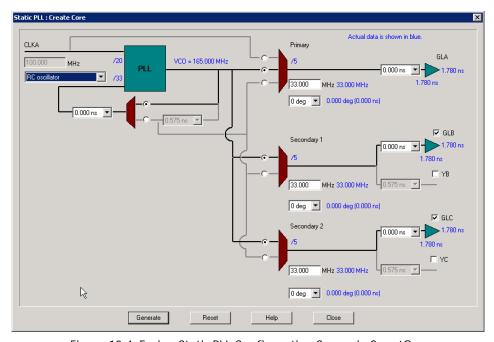

|    | Dynamic CCC Functionality         |        |

| 11 | Analog System Builder             | 5      |

| 12 | Flash Memory System Builder       | 5      |

### Table of Contents

| 13 | Register (Storage Elements)                                    |

|----|----------------------------------------------------------------|

| 14 | Memory Cores for Non-Axcelerator Families                      |

| 15 | Memory Cores for Axcelerator                                   |

| 16 | Memory Cores for ProASIC, ProASIC PLUS, and ProASIC3/E Devices |

| A  | Memory in ProASIC and ProASIC PLUS                             |

|    | Distributed Memory                                             |

|    | Timing for Distributed Memories                                |

|    | Using Multiple Memories in a Design                            |

| В  | Memory Core Algorithm Summary                                  |

| C  | Product Support                                                |

|    | Customer Service                                               |

|    | Actel Customer Technical Support Center                        |

|    | Actel Technical Support                                        |

|    | Website                                                        |

|    | Contacting the Customer Technical Support Center               |

# Introduction

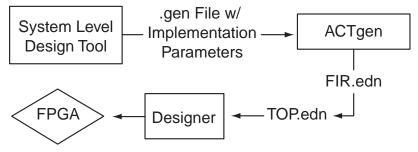

This guide provides descriptions of cores that you can generate using the Actel SmartGen core builder software. For more information about instantiating cores, refer to the *Actel HDL Coding Style Guide* and the SmartGen online help.

The Actel SmartGen core builder generates a large variety of commonly used functions. You can generate structural netlists in EDIF, VHDL, and Verilog. Furthermore, you can generate VHDL and Verilog behavioral models for most parameterized functions (the behavioral models may be used in a simulation environment).

#### Actel's parameterized cores:

- Reduce the development time of complex functions.

- Offer a large set of implementations for each type of function.

- · Offer a wide range of bit widths that provides a quick change of design definitions.

# **Document Conventions**

The following table describes the conventions that are used throughout this manual.

Table 1. Functional Description of Table Nomenclature

| Symbol                  | Definition                                                |

|-------------------------|-----------------------------------------------------------|

| X                       | Don't care                                                |

| 1                       | Logical 1 or high                                         |

| 0                       | Logical 0 or low                                          |

| -                       | Rising edge                                               |

| Ø                       | Falling edge                                              |

| Qn                      | Value of the signal Q before the active edge of the clock |

| $Q_{n+1}$               | Value of the signal Q after the active edge of the clock  |

| $Q_n$ [width-1: 0]      | $Q_{\mathbf{n}}$ is a width-bit bus                       |

| Q <sub>n</sub> [width-1 | Width-1 bit of Q <sub>n</sub>                             |

#### Introduction

Table 1. Functional Description of Table Nomenclature (Continued)

| Symbol | Definition                            |

|--------|---------------------------------------|

| m, n   | Binary pattern with width of function |

# **Symbols**

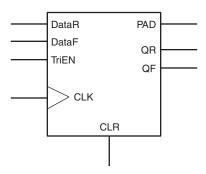

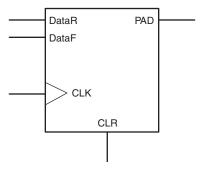

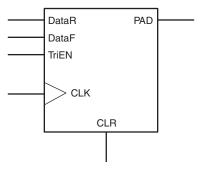

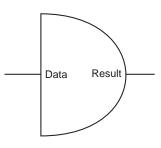

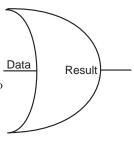

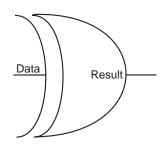

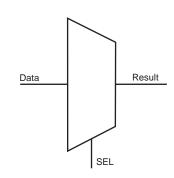

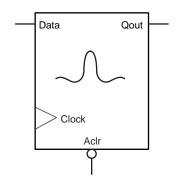

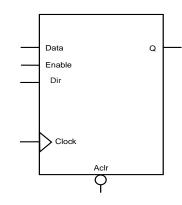

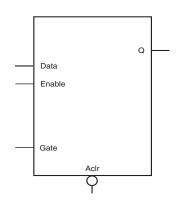

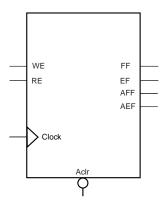

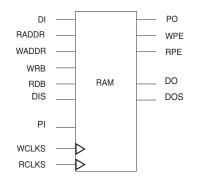

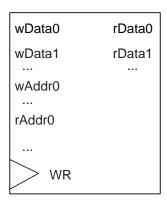

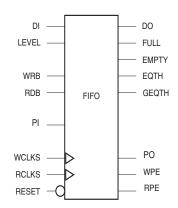

Each core symbol shows the input and output ports. Busses are highlighted with a bold line; scalar signals with a thin line. The actual symbols generated by SmartGen could look slightly different, depending on the particular CAE tool used. Some ports shown could be optional, as described in the port description tables. Default polarities are shown on the symbols.

# **Your Comments**

Actel Corporation strives to produce the highest quality online help and printed documentation. We want to help you learn about our products, so you can get your work done quickly. We welcome your feedback about this guide and our online help. Please send your comments to documentation@actel.com.

# **Online Help**

The Libero IDE and Designer software comes with online help. Online help specific to each software tool is available in the Libero IDE, Designer, SmartGen, Silicon Expert, Silicon Explorer II, and Silicon Sculptor. Please refer to the SmartGen online help (open SmartGen and from the Help menu, select SmartGen Help) for a complete explanation of how to use the SmartGen tool.

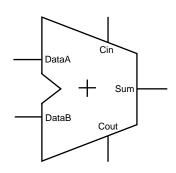

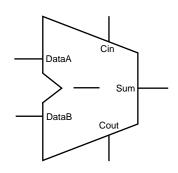

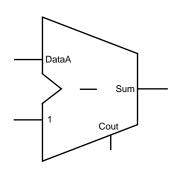

# Adder

### **Features**

- Parameterized word length

- Optional carry-in and carry-out signals

- Multiple gate-level implementations (speed/area tradeoffs)

- Behavioral simulation model in VHDL and Verilog

# **Family Support**

ACT 1, ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

Table 1-1. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function   |

|-----------|-------|--------|---------|------------|

| DataA     | WIDTH | Input  | Req.    | Input Data |

| DataB     | WIDTH | Input  | Req.    | Input Data |

| Cin       | 1     | Input  | Opt.    | Carry-in   |

| Sum       | WIDTH | Output | Req.    | Sum        |

| Cout      | 1     | Output | Opt.    | Carry-out  |

Table 1-2. Parameter Description

| Parameter                                                  | Family          | Value                                                      | Function                                                  |

|------------------------------------------------------------|-----------------|------------------------------------------------------------|-----------------------------------------------------------|

|                                                            | 500K, PA        | 2-128                                                      |                                                           |

| WIDTH <sup>a</sup>                                         | Axcelerator     | 2-156                                                      | Word length of DataA, DataB and Sum                       |

|                                                            | Other           | 2-32                                                       |                                                           |

| MAXFANOUT                                                  | FANOUT 500K, PA | 0                                                          | Automatic choice (function of WIDTH)                      |

| MAAFANOUT                                                  | 500K, FA        | 2-16                                                       | Manual setting of Max. Fanout                             |

| CI_POLARITY ALL 0                                          |                 | 012                                                        | Carry-in polarity (active low, active high, and not used) |

| CO_POLARITY ALL 012 Carry-out polarity (active low, active |                 | Carry-out polarity (active low, active high, and not used) |                                                           |

a. The Brent-Kung Adder extends the ranges from 32 to 128 bit for SX, SX-A and from 20 to 128 bit for 500K.

The Sklansky Adder enables you to clear the Automatic Max. Fanout check box and specify a value for max fanout. This makes SmartGen perform logic replication on high-fanout nets so that the maximum fanout for all the nets in the design is not more than the value specified. If it is set to automatic, SmartGen automatically makes the decision for logic replication based on the size of the design.

The MAXFANOUT parameter enables you to perform logic replication for all Flash Adders, Subtractors, Adder/Subtractors and Accumulators. Inherently only the Sklansky algorithm generates high-fanout nets (max. fanout = WIDTH/2), so you will see effects only for this algorithm. The area increases exponentially for MAXFANOUT approaching 2 and it flattens out for higher values, as shown in Figure 1-1.

Figure 1-1. Adder Area as a Function of MAX FANOUT

Performance is not always as predictable (as shown in Figure 1-2). When you select automatic logic replication, SmartGen automatically chooses a value for MAXFANOUT based on WIDTH. This value returns a good, but not necessarily the best, result for that particular value of WIDTH.

Figure 1-2. Adder Performance as a Function of MAX FANOUT Table 1-3. Implementation Parameters

| Parameter     | Family      | Value              | Description                         |

|---------------|-------------|--------------------|-------------------------------------|

| LPMTYPE       | ALL         | LPM_ADD_SUB        | Adder category                      |

|               |             | SKADD              | Sklansky model                      |

|               | 500K, PA    | FBKADD             | Fast Brent-Kung model               |

| LPM HINT      |             | BKADD              | (Compact) Brent-Kung model          |

| LFM_HIN1      | ALL         | FADD <sup>a</sup>  | Very fast carry select model        |

|               |             | MFADD <sup>a</sup> | Fast carry select model             |

|               |             | RIPADD             | Ripple carry model                  |

| LPMTYPE       | Axcelerator | LPM_FC_ADD_SU<br>B | Fast carry chain Adder category     |

| LPM HINT      | Axcelerator | FC_FADD            | Fast carry chain selct model        |

| T1 1/1_1111/1 | Axceletatol | FC_RIPADD          | Fast carry chain ripple carry model |

a. FADD and MFADD are NOT recommended for Flash devices.

Table 1-4. Functional Description

| DataA        | DataB        | Sum                       | Cout <sup>a</sup>    |

|--------------|--------------|---------------------------|----------------------|

| m[width-1:0] | n[width-1:0] | (m + n + Cin )[width-1:0] | (m + n + Cin)[width] |

a. Cin and Cout are assumed to be active high.

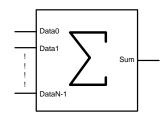

# Array Adder

### **Features**

- · Parameterized word length and number of input buses

- DADDA tree architecture with optional Final Adder

- · Optional pipeline for implementation with Final Adder

- · Behavioral simulation model in VHDL and Verilog

### **Family Support**

SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

### **Description**

The Array-Adder implements a Sum-Function over an array of buses:

Sum =

$$\sum Data(i)$$

where  $i = (0 \text{ to SIZE-1})$

In applications where designers have to add more than two operands at a time "Carry-Save-Techniques" might be used to build the final Sum. SmartGen makes these techniques available through the Array-Adder core, which is using a DADDA tree algorithm. Usually this algorithm is more compact and faster than using Adder trees consisting of multiple 2-operand adders, especially if the number of operands gets large and/or for large word widths.

An example could be the FIR-filter architecture using a "distributed arithmetic" as described in the Application Note from September 1997 *Designing FIR Filters with Actel FPGAs*. This architecture generates a large number of partial products, which need to be summed up. Summing them up in an Adder-Tree would both be slow and area-expensive. When this core was created, synthesis tools did not infer Multiple-Operand-Adders. Therefore making use of the Array-Adder in those types of applications might result in a significant gain in both speed and area.

The Array Adder comes with or without Final Adder. The version with Final Adder allows the designer to instantiate a pipeline stage between the DADDA-tree and the Final Adder. The output bitwidth for Sum can be calculated using this formula:

$$OUTWIDTH = log2((m*exp2(n)-1)+1) <= n + log2(m)$$

The version without Final Adder has two output ports: SumA and SumB, which added together will provide the Final Result. It is

SumA\_Width <= SumB\_Width <= OUTWIDTH

The differences are at most one bit. This variation of the Array-Adder is particularly useful for an application that would cascade the Array-Adder. In that case, only the last stage would need a Final Adder to build the result.

Table 1-5. Port Description

| Port<br>Name | Size     | Туре   | Req/Opt | Function                                           |

|--------------|----------|--------|---------|----------------------------------------------------|

| Data0        | WIDTH    | Input  | Req.    | Input Data (Operand 0)                             |

| Data1        | WIDTH    | Input  | Req.    | Input Data (Operand 1)                             |

| Data2        | WIDTH    | Input  | Req.    | Input Data (Operand 2)                             |

| Datax        | WIDTH    | Input  | Opt.    | Input Data (Operand X) X>2                         |

| Sum          | OUTWIDTH | Output | Req.    | $\sum Data(i) \rightarrow i = 0 \text{ to SIZE-1}$ |

| Clock        | 1        | Input  | Opt.    | Clock (if pipelined)                               |

Table 1-6. Parameter Description

| Parameter | Value     |                                    | Function              |

|-----------|-----------|------------------------------------|-----------------------|

| WIDTH     | width     | AX/Flash: 2-64<br>All others: 2-32 | Word length Data(i)   |

| SIZE      | size      | AX/Flash: 3-64<br>All others: 3-32 | Number of input buses |

| CKL_EDGE  | RISE FALL |                                    | Clock (if pipelined)  |

Table 1-7. Implementation Parameters

| Parameter       | Value   | Description                            |

|-----------------|---------|----------------------------------------|

| LPMTYPE         | DADDA   | Generic Array Adder category           |

| LPM_HINT ARRADD |         | Array Adder with Final Adder           |

|                 | ARRADDP | Pipelined Array Adder with Final Adder |

|                 | ARRADD2 | Array Adder without Final Adder        |

Table 1-8. Parameter Rules

| Family      | Variation        | Parameter Rules      |

|-------------|------------------|----------------------|

| ·V          | ARRADD / ARRADDP | WIDTH * SIZE <=870   |

| eX          | ARRADD2          | WIDTH * SIZE <= 930  |

| SX          | ARRADD / ARADDP  | WIDTH * SIZE <=110   |

| 3/          | ARRADD2          | WIDTH * SIZE <=144   |

| Axcelerator | ARRADD / ARADDP  | WIDTH * SIZE <= 1920 |

|             | ARRADD2          | WIDTH * SIZE <= 1856 |

# **Subtractor**

### **Features**

- · Parameterized word length

- · Optional carry-in and carry-out signals

- Multiple gate-level implementations (speed/area tradeoffs)

- Behavioral simulation model in VHDL and Verilog

### **Family Support**

ACT 1, ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

Table 1-9. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function   |

|-----------|-------|--------|---------|------------|

| DataA     | WIDTH | Input  | Req.    | Input Data |

| DataB     | WIDTH | Input  | Req.    | Input Data |

| Cin       | 1     | Input  | Opt.    | Carry-in   |

| Sum       | WIDTH | Output | Req.    | Sum        |

| Cout      | 1     | Output | Opt.    | Carry-out  |

Table 1-10. Parameter Description

| Parameter          | Family      | Value | Function                                                  |

|--------------------|-------------|-------|-----------------------------------------------------------|

|                    | 500K, PA    | 2-128 |                                                           |

| WIDTH <sup>a</sup> | Axcelerator | 2-156 | Word length of DataA, DataB and Sum                       |

|                    | Other       | 2-32  |                                                           |

| MAXFANOUT          | 500K, PA    | 0     | Automatic choice (function of WIDTH)                      |

| WAAFANOUT          | 2 2 2       | 2-16  | Manual setting of Max. Fanout                             |

| CI_POLARITY        | ALL         | 012   | Carry-in polarity (active low, active high, and not used) |

Table 1-10. Parameter Description (Continued)

| Parameter   | Family | Value | Function                                                   |

|-------------|--------|-------|------------------------------------------------------------|

| CO_POLARITY | ALL    | 012   | Carry-out polarity (active low, active high, and not used) |

a. The Brent-Kung Subtractor extends the ranges from 32 to 128 bit for SX, SX-A and from 20 to 128 bit for 500K.

Table 1-11. Implementation Parameters

| Parameter | Familiy                    | Value              | Description                          |

|-----------|----------------------------|--------------------|--------------------------------------|

| LPMTYPE   | ALL                        | LPM_ADD_SUB        | Subtracter category                  |

|           |                            | SKSUB              | Sklansky model                       |

|           | 500K, PA                   | FBKSUB             | Fast Brent-Kung model                |

| LPM HINT  |                            | BKSUB              | (Compact) Brent-Kung model           |

| LPM_HIN1  |                            | FSUB <sup>a</sup>  | Very fast carry select model         |

|           | ALL                        | MFSUB <sup>a</sup> | Fast carry select model              |

|           |                            | RIPSUB             | Ripple carry model                   |

| LPMTYPE   | Axcelerator LPM_FC_ADD_SUB |                    | Fast carry chain Subtractor category |

| LPM HINT  | Axcelerator                | FC_FSUB            | Fast carry chain selct model         |

| TEMT-LIMI | Axcelerator                | FC_RIPSUB          | Fast carry chain ripple carry model  |

a. FSUB and MFSUB are not recommended for Flash devices.

Table 1-12. Functional Description

| DataA        | DataB        | Sum                       | Cout <sup>a</sup>    |

|--------------|--------------|---------------------------|----------------------|

| m[width-1:0] | n[width-1:0] | (m - n - Cin) [width-1:0] | (m - n - Cin)[width] |

a. Cin and Cout are assumed to be active high.

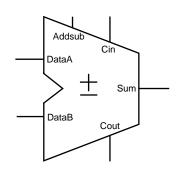

# Adder/Subtractor

### **Features**

- · Parameterized word length

- · Optional carry-in and carry-out signals

- Mulitiple gate-level implementations (speed/area tradeoffs)

- · Behavioral simulation model in VHDL and Verilog

### **Family Support**

ACT 1, ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

Table 1-13. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function                                             |

|-----------|-------|--------|---------|------------------------------------------------------|

| DataA     | WIDTH | Input  | Req.    | Input Data                                           |

| DataB     | WIDTH | Input  | Req.    | Input Data                                           |

| Cin       | 1     | Input  | Opt.    | Carry-in                                             |

| Sum       | WIDTH | Output | Req.    | Sum                                                  |

| Cout      | 1     | Output | Opt.    | Carry-out                                            |

| Addsub    | 1     | Input  | Req.    | Addition (AddSub = 1)<br>or subtraction (Addsub = 0) |

Table 1-14. Parameter Description

| Parameter          | Family      | Value | Function                             |  |

|--------------------|-------------|-------|--------------------------------------|--|

| WIDTH <sup>a</sup> | 500K, PA    | 2-128 |                                      |  |

|                    | Axcelerator | 2-156 | Word length of DataA, DataB and Sum  |  |

|                    | Other       | 2-32  |                                      |  |

| MAXFANOUT          |             | 0     | Automatic choice (function of WIDTH) |  |

|                    |             | 2-16  | Manual setting of Max. Fanout        |  |

Table 1-14. Parameter Description

| Parameter   | Family | Value | Function                                                   |

|-------------|--------|-------|------------------------------------------------------------|

| CI_POLARITY | ALL    | 0 1 2 | Carry-in polarity (active low, active high, and not used)  |

| CO_POLARITY | ALL    | 0 1 2 | Carry-out polarity (active low, active high, and not used) |

a. The Brent-Kung Adder/Subtractor extends the ranges from 32 to 128 bit for SX, SX-A and from 20 to 128 bit for 500K.

Table 1-15. Implementation Parameters

| Parameter | Family      | Value                 | Description                         |                            |

|-----------|-------------|-----------------------|-------------------------------------|----------------------------|

| LPMTYPE   | ALL         | LPM_ADD_SUB           | Adder/Subtracter category           |                            |

|           |             | SKADDSUB              | Sklansky model                      |                            |

|           | 500K, PA    | FBKADDSUB             | Fast Brent-Kung model               |                            |

| LPM HINT  |             | NIT                   | BKADDSUB                            | (Compact) Brent-Kung model |

| LPM_HIN1  |             | FADDSUB <sup>a</sup>  | Very fast carry select model        |                            |

|           | ALL         | MFADDSUB <sup>a</sup> | Fast carry select model             |                            |

|           |             | RIPADDSUB             | Ripple carry model                  |                            |

| LPMTYPE   | Axcelerator | LPM_FC_ADD_SUB        | Fast carry chain Adder category     |                            |

| LPM HINT  | Axcelerator | FC_FADDSUB            | Fast carry chain selct model        |                            |

| LPM_HIN1  | Axcelerator | FC_RIPADDSUB          | Fast carry chain ripple carry model |                            |

a. FADDSUB and MFADSUBB are not recommended for Flash devices.

Table 1-16. Functional Description

| DataA        | DataB        | Addsub                    | Sum                  | Cout <sup>a</sup> |

|--------------|--------------|---------------------------|----------------------|-------------------|

| m[width-1:0] | n[width-1:0] | (m + n + Cin )[width-1:0] | (m + n + Cin)[width] | m[width-1:0]      |

| m[width-1:0] | n[width-1:0] | (m - n - Cin) [width-1:0] | (m - n - Cin)[width] | m[width-1:0]      |

a. Cin and Cout are assumed to be active high.

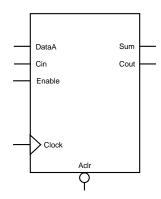

# Accumulator

### **Features**

- · Parameterized word length

- Optional carry-in and carry-out signals

- · Asynchronous reset

- · Accumulator enable

- Multiple gate-level implementations (speed/area tradeoffs)

- · Behavioral simulation model in VHDL and Verilog

# **Family Support**

ACT 1, ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, PA, 500K, Axcelerator, ProASIC3/E

Table 1-17. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function              |

|-----------|-------|--------|---------|-----------------------|

| DataA     | WIDTH | Input  | Req.    | Input Data            |

| Cin       | 1     | Input  | Opt.    | Carry-in              |

| Sum       | WIDTH | Output | Req.    | Sum                   |

| Cout      | 1     | Output | Opt.    | Carry-out             |

| Enable    | 1     | Input  | Opt     | Enable                |

| Clock     | 1     | Input  | Req.    | Clock                 |

| Aclr      | 1     | Input  | Opt     | Asynchronous<br>Reset |

Table 1-18. Parameter Description

| Parameter           | Family           | Value          | Function                                                   |

|---------------------|------------------|----------------|------------------------------------------------------------|

| 50                  | 500K, PA         | 2-128          |                                                            |

| WIDTH <sup>a</sup>  | Axcelerator      | 2-156          | Word length of DataA, DataB and Sum                        |

|                     | Other            | 2-32           |                                                            |

| MANDANOLUE          | ZOOK DA          | 0              | Automatic choice (function of WIDTH)                       |

| MAXFANOUT 500K, PA  | 500K, PA         | 2-16           | Manual setting of Max. Fanout                              |

| CI_POLARITY         | ALL              | 0 1 2          | Carry-in polarity (active low, active high, and not used)  |

| CO_POLARITY         | ALL              | 0 1 2          | Carry-out polarity (active low, active high, and not used) |

| CLR_POLARITY        | ALL              | 0 1 2          | Asynchronous reset (active high, active low, and not used) |

| EN_POLARITY         | ALL              | 012            | Accumulator enable (active high, active low, and not used) |

| FFTYPE <sup>b</sup> | ALL except Flash | REGULAR<br>TMR | FF type used (Regular, Triple Voting)                      |

| CLK_EDGE            | ALL              | RISE FALL      | Active High/Low                                            |

a. The Brent-Kung Accumulator extends the ranges from 32 to 128 bit for SX, SX-A and from 20 to 128 bit for 500K

Table 1-19. Fan-In Control Parameters

| Parameter | Value                                                   |  |  |

|-----------|---------------------------------------------------------|--|--|

| CLR_FANIN | AUTO MANUAL                                             |  |  |

| CLR_VAL   | <val> [default value for AUTO is 8, 1 for MANUAL]</val> |  |  |

| EN_FANIN  | AUTO MANUAL                                             |  |  |

| EN_VAL    | <val> [default value for AUTO is 6, 1 for MANUAL]</val> |  |  |

| CLK_FANIN | AUTO MANUAL                                             |  |  |

b. TMR is Triple Module Redundancy. Choosing this option makes SmartGen use TMR Flip-Flops that are used to avoid Single Event Upsets (SEUs) for Rad-hard Designs. Choosing this option causes the Sequential resource usage to be tripled in families where no TMR is implemented in silicon.

Table 1-19. Fan-In Control Parameters

| Parameter | Value                                                   |

|-----------|---------------------------------------------------------|

| CLK_VAL   | <val> [default value for AUTO is 8, 1 for MANUAL]</val> |

Table 1-20. Implementation Parameters

| Parameter     | Family      | Value              | Description                         |  |

|---------------|-------------|--------------------|-------------------------------------|--|

| LPMTYPE       |             | LPM_ADD_SUB        | Accumulator category                |  |

|               |             | SKACC              | Sklansky model                      |  |

|               | 500K, PA    | FBKACC             | Fast Brent-Kung model               |  |

| I DM LIINT    |             | BKACC              | (Compact) Brent-Kung model          |  |

| LPM_HINT      | ALL         | FACC <sup>a</sup>  | Very fast carry select model        |  |

|               |             | MFACC <sup>a</sup> | Fast carry select model             |  |

|               |             | RIPACC             | Ripple carry model                  |  |

| LPMTYPE       | Axcelerator | LPM_FC_ADD_SUB     | Fast carry chain Adder category     |  |

| I DA A LILAYT | Axcelerator | FC_FACC            | Fast carry chain selct model        |  |

| LPM_HINT      |             | FC_RIPACC          | Fast carry chain ripple carry model |  |

a. The FACC and MACC parameters are not recommended for Flash devices.

Table 1-21. Functional Description

| DataA        | Sumn <sub>+1</sub>                         | Cout <sup>a</sup>          |

|--------------|--------------------------------------------|----------------------------|

| m[width-1:0] | (m + Sum <sub>n</sub> + Cin )[width-1 : 0] | $(m + Sum_n + Cin)[width]$ |

a. Cin and Cout are assumed to be active high.

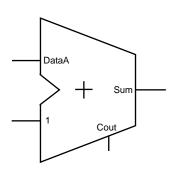

# Incrementer

### **Features**

- Parameterized word length

- Optional Carry-out signals

- One very fast gate-level implementation, FC High Speed and FC Ripple available

- Behavioral simulation model in VHDL and Verilog

# **Family Support**

ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Acelerator, ProASIC3/E

Table 1-22. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function   |

|-----------|-------|--------|---------|------------|

| DataA     | WIDTH | Input  | Req.    | Input Data |

| Sum       | WIDTH | Output | Req.    | Sum        |

| Cout      | 1     | Output | Opt.    | Carry-out  |

Table 1-23. Parameter Description

| Parameter   | Value                      | Function                                                   |

|-------------|----------------------------|------------------------------------------------------------|

| WIDTH       | 2-32<br>2-156 for FC Cores | Word length of DataA and Sum                               |

| CO_POLARITY | 012                        | Carry-out polarity (active low, active high, and not used) |

Table 1-24. Implementation Parameters

| Parameter | meter Value Descript        |                            |

|-----------|-----------------------------|----------------------------|

| LPMTYPE   | LPM_ADD_SUB                 | Incrementer category       |

| LPM_HINT  | FINC; FC_FINC,<br>FC_RIPINC | Very fast carry look ahead |

Table 1-25. Functional Description

| DataA | Sum   | Cout                           |

|-------|-------|--------------------------------|

| m     | m + 1 | $(m + 1) \ge 2^{\text{width}}$ |

# **Decrementer**

### **Features**

- Parameterized word length

- · Optional Carry-out signals

- One very fast gate-level implementation, FC High Speed and FC Ripple available

- · Behavioral simulation model in VHDL and Verilog

# **Family Support**

ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

Table 1-26. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function   |

|-----------|-------|--------|---------|------------|

| DataA     | WIDTH | Input  | Req.    | Input Data |

| Sum       | WIDTH | Output | Req.    | Sum        |

| Cout      | 1     | Output | Opt.    | Carry-out  |

Table 1-27. Parameter Description

| Parameter   | Value                                      | Function                                                   |

|-------------|--------------------------------------------|------------------------------------------------------------|

| WIDTH       | 2-32<br>2-156 for FC_FDEC<br>and FC_RIPDEC | Word length of DataA and Sum                               |

| CO_POLARITY | 012                                        | Carry-out polarity (active low, active high, and not used) |

Table 1-28. Implementation Parameters

| Parameter | Value                                           | Description                   |

|-----------|-------------------------------------------------|-------------------------------|

| LPMTYPE   | LPM_ADD_SUB                                     | Decrementer category          |

| LPM_HINT  | FDEC FC_FDEC and FC_RIPDEC, Fast Carry Versions | Very fast carry look<br>ahead |

Table 1-29. Functional Description

| DataA | DataB | Sum   | Cout      |

|-------|-------|-------|-----------|

| m     | n     | m - 1 | (m-1) < 0 |

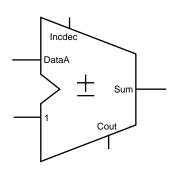

# Incrementer/Decrementer

### **Features**

- · Parameterized word length

- · Optional Carry-out signals

- One very fast gate-level implementation, FC High Speed and FC Ripple available

- Behavioral simulation model in VHDL and Verilog

## **Family Support**

ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

Table 1-30. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function                                         |

|-----------|-------|--------|---------|--------------------------------------------------|

| DataA     | WIDTH | Input  | Req.    | Input Data                                       |

| Sum       | WIDTH | Output | Req.    | Sum                                              |

| Cout      | 1     | Output | Opt.    | Carry-out                                        |

| Incdec    | 1     | Input  | Req.    | Increment (Incdec = 1) or decrement (Incdec = 0) |

Table 1-31. Parameter Description

| Parameter | Value                                            | Function                     |

|-----------|--------------------------------------------------|------------------------------|

| WIDTH     | 2-32<br>2-156 for FC_FINCDEC and<br>FC_RIPINCDEC | Word length of DataA and Sum |

Table 1-31. Parameter Description

| Parameter   | Value | Function                                                   |

|-------------|-------|------------------------------------------------------------|

| CO_POLARITY | 012   | Carry-out polarity (active low, active high, and not used) |

Table 1-32. Implementation Parameters

| Parameter | Value                                 | Description                      |

|-----------|---------------------------------------|----------------------------------|

| LPMTYPE   | LPM_ADD_SUB                           | Incrementer/Decrementer category |

| LPM_HINT  | FINCDEC<br>FC_FINCDEC<br>FC_RIPINCDEC | Very fast carry look ahead       |

Table 1-33. Functional Description

| DataA | Incdec | Sum   | Cout                         |

|-------|--------|-------|------------------------------|

| m     | 1      | m + 1 | $(m+1) \ge 2^{\text{width}}$ |

| m     | 0      | m - 1 | (m - 1) < 0                  |

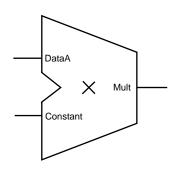

# Constant Multiplier

#### **Features**

- · Parameterized word lengths and constant values

- Unsigned and signed (Two's-Complement) data representation

- · Booth / Wallace architecture

- Behavioral simulation model (for non-pipelined multiplier only) in VHDL and Verilog

### **Family Support**

SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

### **Description**

The Constant Multiplier performs the multiplication of a data-input with a constant value. Area and performance of the Constant Multiplier depend on the value of the constant. Specifically, area and performance depend on the number of groups of 1s in the bit pattern of the constant. As a result, the worst-case constant has a bit pattern of alternating 1s and 0s (...010101...). However, even for that worst case, the area and performance of the Constant Multiplier is superior to a regular Multiplier.

The Constant Multiplier core output word length is always double the input word length. Depending on the value of the constant, some of the most significant bits might be sign-extension bits. You may be able to reduce hardware by calculating the actual number of bits needed and cutting all sign-extension bits. For example:

width =4, Constant = 1100, representation=signed

The worst case data for this example would be 1000 (-8) and therefore the worst case output data would be  $010\ 0000$  (-8 \* -4 = 32). So with that we know that Mult<8> is just a sign-extension bit (Mult<8> = Mult<7>).

Keep in mind that some constant multiplications might be generated even more effectively, e.g. constants to the power of 2 are just shift-operations, or constants like 3,5,7,9,10, etc. can be generated using shift operations and a simple addition/subtraction (2+1, 4+1, 8-1, 8+1, 8+2, etc.) For these constants, the implementation of the Constant Multiplier might not be as efficient as using shift operations and/or Adders/Subtractors.

Usually synthesis infers regular multipliers even for constant values. Therefore the use of the Constant Multiplier core in a design, which performs one or more multiplications with constant values, is expected to be very beneficial.

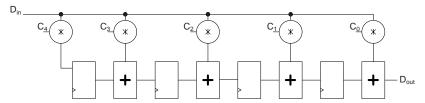

An application example might be FIR-filters with constant coefficients, where the computation is organized in the "transposed form" as indicated in Figure 1-3.

Figure 1-3. FIR-Filter Organized in the "Transposed Form" Using Constant Multipliers

Table 1-34. Port Description

| Port<br>Name | Size    | Туре   | Req/Opt | Function        |

|--------------|---------|--------|---------|-----------------|

| Data         | WIDTH   | Input  | Req.    | Input data      |

| Mult         | 2*WIDTH | Output | Req.    | Constant * Data |

Table 1-35. Parameter Description

| Parameter          | Value       | Function                         |

|--------------------|-------------|----------------------------------|

| WIDTH <sup>a</sup> | 2-64        | Word length Data                 |

| CONST              | Constant    | Constant value                   |

| RADIX              | HEX BIN DEC | Radix for constant value         |

| SIGN <sup>b</sup>  | 0 1         | Positive, negative constant sign |

a. For eX WIDTH is supported from 2-11

b. For signed constant multiplier

### Parameter Rules:

1. DataA is always binary and of the size of Width.

2. Constant must be of the selected Radix and be of the selected width for HEX/BIN. SmartGen automatically pads zeroes if they are missing.

e.g.: Radix: BIN, Width: 5, Constant: 00010

Radix Hex, Width:8, Constant: 0A

Table 1-36. Implementation Parameters

| Parameter | Value    | Description                  |

|-----------|----------|------------------------------|

| LPMTYPE   | LPM_MULT | Constant multiplier category |

| LPM_HINT  | UCMULT   | Unsigned constant multiplier |

|           | SCMULT   | Signed constant multiplier   |

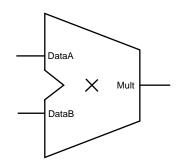

# Multiplier

### **Features**

- Parameterized word lengths

- Unsigned and signed (Two's-Complement) data representation

- Booth or array implementation

- · Optional pipelining

- Behavioral simulation model in VHDL and Verilog

## **Family Support**

ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

Table 1-37. Port Description

| Port Name | Size          | Туре   | Req/Opt | Function        |

|-----------|---------------|--------|---------|-----------------|

| DataA     | WIDTHA        | Input  | Req.    | Input data      |

| DataB     | WIDTHB        | Input  | Req.    | Input data      |

| Clock     | 1             | Input  | Opt.    | Clock           |

| Mult      | WIDTHA+WIDTHB | Output | Opt.    | DataA*DataB     |

| Mult0     | WIDTHA+WIDTHB | Output | Opt.    | Mult0 + Mult1 = |

| Mult1     | WIDTHA+WIDTHB | Output | Opt.    | DataA*DataB     |

Table 1-38. Parameter Description

| Parameter           | Family                   | Value                | Function                                                |

|---------------------|--------------------------|----------------------|---------------------------------------------------------|

|                     | 500K, PA,<br>Axcelerator | 2-64                 |                                                         |

| WIDTHA <sup>a</sup> | eX                       | 2-14                 | Word length of DataA                                    |

|                     | Other                    | 2-30                 |                                                         |

| WIDTHB              | Same as WIDTHA           |                      | Word length of DataB                                    |

| REPRESENTATION      |                          | UNSIGNED<br>SIGNED   | Data representation                                     |

| FFTYPE <sup>b</sup> | ALL except<br>Flash      | REGULAR<br>TMR<br>CC | FF Type Used (Default, Triple<br>Voting, Combinatorial) |

| CLK_EDGE            |                          | RISE FALL            | Clock (if pipelined)                                    |

a. For some of the multiplier variations there are small deviations from the limits mentioned to ensure that the multiplier fits in the largest device of the selected family.

b. TMR: Triple Module Redundancy. Choosing this option makes SmartGen use TMR Flip-Flops which are used to avoid Single Event Upsets (SEUs) for Rad-hard Designs. Choosing this option causes the Sequential resource usage to be tripled in families where no TMR is implemented in silicon.

CC: When combinatorial option is chosen for the Sequential Type, the FF is implemented using two Combinatorial Cells instead of one Sequential Cell. This is useful when no Sequential resources are available in the designs.

This option is applicable only to the pipelined multipliers.

Table 1-39. Functional Description

| DataA | DataB | Mult1 <sup>a</sup> |

|-------|-------|--------------------|

| m     | n     | m * n              |

a. If pipelined, the sum is correct (available) after <latency> cycles. Latency is a function of WIDTHA and WIDTHB, or the number of pipelined stages mentioned specifically (eg. one or two pipelines).

Table 1-40. Functional Description

| DataA | DataB | Mult0/1 <sup>a</sup>  |

|-------|-------|-----------------------|

| m     | n     | Mult1 + Mult2 = m * n |

a. Mult1<0> is always 0

Table 1-41. Parameter Rules<sup>a</sup>

| Family  | Variation   | Parameter rules                                |

|---------|-------------|------------------------------------------------|

| All     | All         | WIDTHA ≥ WIDTHB                                |

|         | BOOTHMULT/P | WIDTHA + WIDTHB <= 15 (signed) / 16 (unsigned) |

| eX      | BOOTHMULTP  | For TMR restrictions for WIDTHA, WIDTHB        |

|         | BOOTHMULT2  | WIDTHA + WIDTHB <= 17 (signed) / 18 (unsigned) |

| CV/CV A | BOOTHMULT/P | WIDTHA + WIDTHB <= 32                          |

| SX/SX-A | BOOTHMULT2  | WIDTHA + WIDTHB <= 55                          |

Table 1-41. Parameter Rules<sup>a</sup> (Continued)

| Family      | Variation     | Parameter rules        |

|-------------|---------------|------------------------|

|             | ARRAYMULT     | WIDTHA + WIDTHB <= 128 |

| Axcelerator | PARRAYMULT    | WIDTHA + WIDTHB <= 128 |

|             | FC_BOOTHMULT1 | WIDTHA + WIDTHB <= 106 |

|             | FC_BOOTHMULT1 | WIDTHA + WIDTHB <= 106 |

| 500K, PA    | All           | WIDTHA + WIDTHB <= 106 |

| Other       | All           | WIDTHA + WIDTHB <= 32  |

a. These are the most important parameter rules; additional rules may apply

Table 1-42. Implementation Parameters

| Parameter | Value                   | Description                                                                                                                                                                                      |  |

|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LPMTYPE   | LPM_MULT                | Multiplier category                                                                                                                                                                              |  |

|           | BOOTHMULT               | Booth multiplier                                                                                                                                                                                 |  |

| LPM_HINT  | BOOTHMULT2 <sup>a</sup> | Booth multiplier without final Adder                                                                                                                                                             |  |

|           | BOOTHMULTP              | Pipelined booth multiplier                                                                                                                                                                       |  |

|           | LPM_FC_MULT             | Fast Carry multiplier category (Axcelerator) <sup>b</sup>                                                                                                                                        |  |

| LPMTYPE   | PARRAYMULT              | Fast Carry array multipliers in parallel; each array multiplie consists of a 1-bit multiplier (MULT1); the rows of the arr use fast carry chains, but there is a regular routing between columns |  |

|           | BOOTHMULT1              | Booth-encoded Wallace-tree with Fast Carry final adder                                                                                                                                           |  |

|           | BOOTHMULT2              | Booth-encoded multiplier with n-bit Fast Carry adder tree                                                                                                                                        |  |

a. Available for SX, SX-A, eX, 500K & PA

b. For information on multiplier area and performance please refer to the latest Actel application note available at http://www.actel.com

Table 1-43. Axcelerator Multiplier Architecture Comparison Speed<sup>a</sup>

| Architecture \ Speed           | 1 (fastest)                                                    | 2                        | 3 (slowest)     |

|--------------------------------|----------------------------------------------------------------|--------------------------|-----------------|

| Parallel-2 Array<br>Multiplier | width <= 8 bit                                                 | 8 bit < width <= 10 bit  | width > 10 bit  |

| FC Booth-1                     | h-1 8 bit < width <= 20 bit   width <= 8 bit or width > 20 bit |                          |                 |

| FC Booth-2                     | width > 20 bit                                                 | 10 bit < width <= 20 bit | width <= 10 bit |

a. For simplicity's sake, the table assumes WIDTHA = WIDTHB = width

Table 1-44. Axcelerator Multiplier Architecture Comparison: Area

| Architecture \ Speed        | 1 (smallest) | 2      | 3 (largest) |

|-----------------------------|--------------|--------|-------------|

| Parallel-2 Array Multiplier | always       |        |             |

| FC Booth-1                  |              |        | always      |

| FC Booth-2                  |              | always |             |

# **Advanced Options**

Click the Advanced button (available for PA, 500K, and Axcelerator devices) to specify pipeline stages. If you are using a PA or 500K device, you can insert (default setting) or omit the final Adder stage.

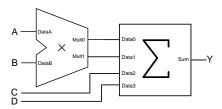

# **Omitting the Final Adder**

You can choose not to instantiate the final adder in the multiplier and add up the two buses Mult0 and Mult1 to the final result later in the design flow. This is often the most efficient implementation when a lot of partial results get summed up in a large summation network. Figure 1-

### **Advanced Options**

4 shows an example for  $Y = (A \times B) + C + D$  using the multiplier with two outputs in combination with the Array-Adder.

Figure 1-4. Efficient implementation using the two-output multiplier in combination with the Array-Adder

## **Multiplier Pipelining**

For 500K, PA, and Axcelerator devices, you can specify the number of pipeline stages (1, 2, or 3). However, three pipeline stages increases performance only for high bitwidth designs. Click the Advanced button in the GUI to access pipelining.

| Dinalina Stages | WidthB         |                 |  |

|-----------------|----------------|-----------------|--|

| Pipeline Stages | w/ Final Adder | w/o Final Adder |  |

| 1               | >= 2           | >= 5            |  |

| 2               | >= 5           | >= 7            |  |

| 3               | >= 7           | Not applicable  |  |

Table 1-45. Pipeline Stages

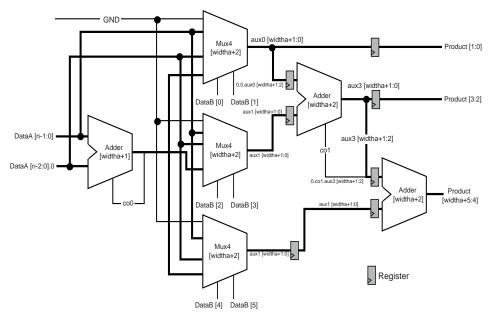

For ACT 2, ACT 3, 3200DX, MX, SX, SX-A, and eX, the multiplier architecture does not allow you to select the latency of the pipelined multiplier or the number of logic levels between the pipeline stages. Registers are automatically inserted between the major components of the architecture, primarily the multiplexer and adder cores, as shown in Figure 1-5.

Figure 1-5. Booth Multiplier Architecture (Pipeline)

The number of pipeline stages is a function of the width of the DataB input. The number of logic levels per pipeline stage is a function of the width of the DataA input. Therefore, the number of logic levels per pipeline stage is equal to the number of logic levels of the first adder (WIDTHA + 1) plus 1 for the 4 to 1 multiplexer, as shown in Figure 1-5.

Table 1-46. Pipeline Stages as a Function of WidthB

| WidthB Range | Pipeline Stages |

|--------------|-----------------|

| 2            | 0               |

| 3-4          | 1               |

| 5-8          | 2               |

| 9-16         | 3               |

Table 1-47. Logic Levels as a Function of WidthA

| WidthA Range | Logic Levels |

|--------------|--------------|

| 2-5          | 3            |

| 6-17         | 4            |

| 18-30        | 5            |

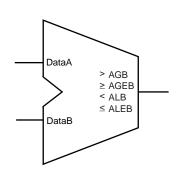

# Comparators

# Magnitude/Equality Comparator

#### **Features**

- · Parameterized word length

- Unsigned and signed (Two's-Complement) data comparison

- · One very fast gate-level implementation

- · Behavioral simulation model in VHDL and Verilog

## **Family Support**

ACT 1, ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

Note: For ProASIC devices, the Equality Comparator and the Magnitude Comparator are seperate. For all other devices they are the same core. There is a Fast Carry Magnitude Comparator available for Axcelerator.

## **Description**

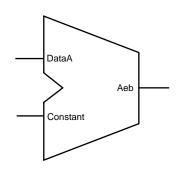

Table 2-1. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function                     |

|-----------|-------|--------|---------|------------------------------|

| DataA     | WIDTH | Input  | Req.    | Input data                   |

| DataB     | WIDTH | Input  | Req.    | Input data                   |

| AGB       | 1     | Output | Opt.    | Output comparison; A > B     |

| AGEB      | 1     | Output | Opt.    | Output comparison; $A \ge B$ |

| ALB       | 1     | Output | Opt.    | Output comparison; A < B     |

| ALEB      | 1     | Output | Opt.    | Output comparison; $A \le B$ |

| AEB       | 1     | Output | Opt.    | Output comparison; A = B     |

| ANEB      | 1     | Output | Opt.    | Output comparison; A ≠ B     |

Table 2-2. Parameter Description

| Parameter      | Value           | Function                                              |

|----------------|-----------------|-------------------------------------------------------|

| WIDTH          | 2-32            | Word length of DataA and DataB                        |

| REPRESENTATION | UNSIGNED SIGNED |                                                       |

| AGB_POLARITY   | 012             | AGB polarity (active high, active low, and not used)  |

| AGEB_POLARITY  | 0 1 2           | AGEB polarity (active high, active low, and not used) |

| ALB_POLARITY   | 012             | ALB polarity (active high, active low, and not used)  |

| ALEB_POLARITY  | 012             | ALEB polarity (active high, active low, and not used) |

| AEB_POLARITY   | 012             | AEB polarity (active high, active low, and not used)  |

| ANEB_POLARITY  | 0 1 2           | ANEB polarity (active high, active low, and not used) |

Table 2-3. Implementation Parameters

| Parameter           | Value          | Description                    |  |

|---------------------|----------------|--------------------------------|--|

| LPMTYPE LPM_COMPARE |                | Comparator category            |  |

| LEWITTE             | LPM_FC_COMPARE | Fast Comparator Category       |  |

| LPM_HINT            | COMPARE        | Very fast carry select         |  |

| LPM_HINI            | FC_MAGCOMP     | Very fast Magnitude Comparator |  |

### **Parameter Rules**

- 1. At lease one of the comparisons (AGB, AGEB, ALB, ALEB, AEB or ANEB) must be selected

- 2. Only one of the magnitude comparisons (AGB, AGEB, ALB or ALEB) can be selected at the same time

#### Comparators

3. Only one of the equality comparisons (AEB or ANEB) can be selected at the same time

Table 2-4. Functional Description

| DataA | DataB | AGB   | AGEB      | ALB   | ALEB      | AEB   | ANEB  |

|-------|-------|-------|-----------|-------|-----------|-------|-------|

| m     | n     | m > n | $m \ge n$ | m < n | $m \le n$ | m = n | m ≠ n |

Table 2-5. Implementation Parameters

| Implementation (LPM_HINT) | Description                    |

|---------------------------|--------------------------------|

| COMPARE                   | Very fast carry select model   |

| FC_MAGCOMP                | Very fast Magnitude Comparator |

#### **Parameter rules**

- 1. At least one of the comparisons (AGB, AGEB, ALB, ALEB, AEB or ANEB) must be selected

- 2. Only one of the magnitude comparisons (AGB, AGEB, ALB or ALEB) can be selected at the same time

- 3. Only one of the equality comparisons (AEB or ANEB) can be selected at the same time

## **Constant Decoder**

### **Features**

- · Parameterized word length

- DEC/BIN/HEX radices for constant

- Equal/Not Equal comparison

## **Family Support**

ACT 1, ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

## **Description**

Table 2-6. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function   |

|-----------|-------|--------|---------|------------|

| DataA     | WIDTH | Input  | Req.    | Input Data |

| Aeb       | 1     | Output | Req.    | Result     |

Table 2-7. Parameter Description

| Parameter    | Value                           | Function                                         |

|--------------|---------------------------------|--------------------------------------------------|

| WIDTH        | 2-32 <sup>a</sup>               | Word length of DataA and Constant                |

| Radix        | Dec/Bin/Hex                     | Base of Constant                                 |

| Constant     | Same as Width in selected Radix | The value with which input data will be compared |

| AEB_POLARITY | 0, 1                            | A equals B polarity (Active High, Active Low)    |

a. For Flash devices, width is 2-128

### Comparators

Table 2-8. Implementation Parameters

| Parameter | Value       | Description         |  |

|-----------|-------------|---------------------|--|

| LPM_TYPE  | LPM_COMPARE | Comparator category |  |

| LPM_HINT  | WDEC        | Very fast           |  |

#### Parameter Rules:

- 1. DataA is always binary and of the size of Width.

- 2. Constant must be of the selected Radix and be of the selected width for HEX/BIN.

e.g.: Radix: BIN, Width: 5, Constant: 00010

Radix Hex, Width:8, Constant: 0A

Table 2-9. Functional Description

|                  | Aeb |  |

|------------------|-----|--|

| DataA = Constant |     |  |

# Converters

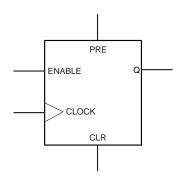

## **Gray Counter**

### **Features**

- · Parameterized for Data Width

- Asynchronous Clear, Asynchronous Preset

## **Family support**

SX, Axcelerator

## **Description**

SmartGen can generate Gray Counters parameterized for a specified Data Width and with a choice of Enable, Asynchronous Clear, and Asynchronous Preset signals.

Table 3-1. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function    |

|-----------|-------|--------|---------|-------------|

| Clock     | WIDTH | Input  | Req.    | Input Data  |

| Q         | WIDTH | Output | Req.    | Output Data |

| Clr       | 1     | Input  | Opt.    | Clear       |

| Pre       | 1     | Input  | Opt.    | Preset      |

| Enable    | 1     | Input  | Opt.    | Enable      |

Table 3-2. Parameter Description

| Parameter    | Value     | Function          |

|--------------|-----------|-------------------|

| GRAYCOUNT    | 2-99      | Output Data Width |

| CLR_POLARITY | 0,1,2     | Clear Polarity    |

| PRE_POLARITY | 0,1,2     | Preset Polarity   |

| EN_POLARITY  | 0,1       | Enable Polarity   |

| CLK_EDGE     | RISE,FALL | Clock Edge        |

Table 3-3. Implementation Parameters

| Parameter | Value            | Function     |  |

|-----------|------------------|--------------|--|

| LPMTYPE   | LPM_GRAY COUNTER | Gray Counter |  |

# Binary to Gray / Gray to Binary

### **Features**

· Parameterized for Data Width

## **Family support**

SX, Axcelerator

## **Description**

SmartGen can generate Binary to Gray and Gray to Binary Converters parameterized for a specified Data Width.

Table 3-4. Port Description

| Port Name | Size  | Туре   | Req/Opt | Function    |

|-----------|-------|--------|---------|-------------|

| Datain    | WIDTH | Input  | Req.    | Input Data  |

| Dataout   | WIDTH | Output | Req.    | Output Data |

Table 3-5. Parameter Description

| Parameter        | Value | Function                |  |

|------------------|-------|-------------------------|--|

| GRAYDECODE/WIDTH | 2-99  | Input/Output Data Width |  |

Table 3-6. Implementation Parameters

| Parameter | Value                         | Function                                       |

|-----------|-------------------------------|------------------------------------------------|

| LPMTYPE   | LPM_GRAYENCODE/ LPMGRAYDECODE | Binary to Gray and Gray to<br>Binary Converter |

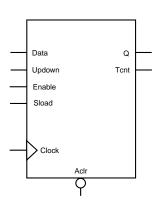

#### **Features**

- · Parameterized word length

- Up, Down and, Up/Down architectures

- · Asynchronous clear

- Asynchronous preset (available only for Flash devices)

- · Synchronous counter load

- Synchronous count enable

- Terminal count flag (not available for Axcelerator)

- Multiple gate-level implementations (area/speed tradeoffs)

- Behavioral simulation model in VHDL and Verilog

## **Family Support**

ACT 2, ACT 3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

## Description

The SmartGen binary counters are general purpose UP, DOWN, or UP/DOWN (direction) counters.

When the count value equals 2<sup>width</sup>-1, the signal *Tcnt* (terminal count), if used, is asserted high.

The counters are WIDTH bits wide and have 2<sup>width</sup> states from "000...0" to "111...1". The counters are clocked on the rising (RISE) or falling (FALL) edge of the clock signal *Clock* (CLK\_EDGE).

The *Clear* signal (CLR\_POLARITY), active low or high, provides an asynchronous reset of the counter to "000...0". You may choose to not implement the reset function. If you do not use the *Clear* signal, Actel recommends that you use *Sload* to set the initial counter contents to a known value.

In the case of an Up/Down counter, the *Updown* signal controls whether the counter counts up (Updown = 1) or down (Updown = 0).

The counter could be loaded with *Data*. The *Sload* signal (LD\_POLARITY), active high or low, provides a synchronous load operation with respect to the clock signal *Clock*. You can choose to not implement this function. If you do not use the *Sload* signal, Actel recommends that you use *Clear* to set the initial counter contents to a known value.

The SmartGen counters have a count enable signal *Enable* (EN\_POLARITY). *Enable* can be active high or low. When *Enable* is not active, the counter is disabled and the internal state is unchanged.

Table 4-1. Port Description

| Port<br>Name | Size  | Туре   | Req./<br>Opt. | Function                              |

|--------------|-------|--------|---------------|---------------------------------------|

| Data         | WIDTH | input  | Opt.          | Counter load input                    |

| Aclr         | 1     | input  | Opt.          | Asynchronous counter reset            |

| Enable       | 1     | input  | Req.          | Counter enable                        |

| Sload        | 1     | input  | Opt.          | Synchronous counter load              |

| Clock        | 1     | input  | Req.          | Clock                                 |

| Updown       | 1     | input  | Opt.          | UP (Updown = 1),<br>DOWN (Updown = 0) |

| Q            | WIDTH | output | Req.          | Counter output bus                    |

| Tent         | 1     | output | Opt.          | Terminal count (active high)          |

Table 4-2. Parameter Description

| Parameter     | Value          | Function                                          |

|---------------|----------------|---------------------------------------------------|

| WIDTH         | 2-32           | Word length of Data and Q                         |

| DIRECTION     | UP DOWN UPDOWN | Counter direction                                 |

| CLR_POLARITY  | 012            | Aclr can be active low, active high, or not used  |

| EN_POLARITY   | 01             | Enable can be active low, or active high          |

| LD_POLARITY   | 012            | Sload can be active low, active high, or not used |

| CLK_EDGE      | RISE FALL      |                                                   |

| TCNT_POLARITY | 12             | Tent can be active high or not used               |

Table 4-3. Fan-in Control Parameters

| Parameter | Value                                                   |

|-----------|---------------------------------------------------------|

| CLR_FANIN | AUTO MANUAL                                             |

| CLR_VAL   | <val> [default value for AUTO is 8, 1 for MANUAL]</val> |

| LD_FANIN  | AUTO MANUAL                                             |

| LD_VAL    | <val> [default value for AUTO is 6, 1 for MANUAL]</val> |

| CLK_FANIN | AUTO MANUAL                                             |

| CLK_VAL   | <val> [default value for AUTO is 8, 1 for MANUAL]</val> |

Table 4-4. Implementation Parameters

| Parameter | Value           | Description               | Family   |

|-----------|-----------------|---------------------------|----------|

| LPMTYPE   | LPM_COUNTE<br>R | Counter category          |          |

| LPM_HINT  | LLCNT           | Prescaled model           | A11      |

|           | TLACNT          | Register look ahead model | All      |

|           | FBCNT           | Fast Balanced model       | SX, SX-A |

|           | BCNT            | Balanced model            | A11      |

|           | LECNT           | Fast Enable Balanced      | A11      |

|           | COMPCNT         | Compact model             | All      |

|           | RIPPLE          | Ripple model              | All      |

| Data | AcIr | Enable | Sload | Clock | Up<br>down | Qn+1   | Tcnt n+1                     |

|------|------|--------|-------|-------|------------|--------|------------------------------|

| X    | 0    | X      | X     | X     | X          | 0's    | 0                            |

| X    | 1    | X      | X     | -     | X          | Qn     | $Qn+1==2^{\text{width}}-1$   |

| X    | 1    | 0      | 0     | 1     | X          | Qn     | $Qn+1==2^{\text{width}}-1$   |

| m    | 1    | X      | 1     | -     | X          | m      | $Qn+1==2^{\text{width}}-1$   |

| X    | 1    | 1      | 0     | 1     | 1          | Qn + 1 | $Qn+1==2^{\text{width}}-1$   |

| X    | 1    | 1      | 0     | 1     | 0          | Qn - 1 | Qn+1== 2 <sup>width</sup> -1 |

Table 4-5. Functional Description<sup>a</sup>

## **Implementations**

This section decribes the implementation of the Pre-Scaled Counter, Register Look Ahead Counter, Fast Balanced Counter and the Balanced Counter.

#### **Pre-Scaled Counter**

The pre-scaled counter achieves absolute maximum count and count enable performance by sacrificing synchronous load performance. This counter registers the two least significant bits and uses them as an enable for the upper bits. Count performance is limited only by the delay in the lower two bits and the enable path for the upper bits. Because the upper bits are only updated (enabled) every fourth cycle, they can accommodate more delay (up to one-fourth the clock frequency).

There are two limitations related to the use of the pre-scaled counter. The first is in analyzing the actual performance of the counter. The second is correctly performing data load functions; these two limitations are related. Two parameters must be measured to overcome these two limitations. The first parameter that must be measured is the worst internal delay inside the counter. The second parameter is the worst delay from Q0/Q1 to any upper bit. The minimum count period is then defined by the greater value of these two parameters.

The load function is a slave of the maximum internal path delay in the pre-scaled counter. The load function must be held for as many clock periods as required to exceed the maximum internal delay;

a. Assume Aclr is active low, Enable is active high, Sload is active high, Clock is rising, and Tent is active high

this ensures that all internal nodes are settled and that correct count operation can be performed. This requirement can be waived if you can guarantee that '0's will always be loaded in Q0 and Q1 (resulting in only a single load cycle).

The count path in pre-scaled counters without Sload or Enable functions only have a single logic level for ACT 2, ACT 3, 3200DX, MX SX, SX-A, and eX. All other combinations of pre-scaled counters have two logic levels in their count path. In these cases, given the two limitations mentioned previously related to the pre-scaled counter, use the Register Look Ahead or Fast Balanced counters.

#### **Register Look Ahead Counter**

This counter achieves the absolute maximum performance for the count, count enable, and synchronous load functions. The counter operates by registering intermediate count values providing "look-ahead" carry circuitry. As a result, this counter variation requires more flip-flops (sequential modules) than other counters.

#### **Fast Balanced Counter**

This counter is only available for the SX, SX-A, and eX families. It takes advantage of the architectural features of these families, including flip-flops with built-in enable and more powerful combinatorial cells. Using these two features, it is possible to build a very fast and compact binary counter without using "look-ahead" carry circuitry. This counter should be preferred over all the others available for this family.

#### **Balanced Counter**

This counter achieves high performance for both the count and enable functions using standard design approaches. Module count performance is sacrificed to maintain high speed. This counter is the result of the performance balance between the count/enable functions and the balance between the performance/cost in building this architecture. This counter should address most counter needs for the ACT 1, ACT 2, ACT 3, 3200DX, 40MX and MX families.

#### **Fast Enable Counter**

This compact counter is fully synchronous and has higher performance than the ripple counter. However, this counter should only be used in moderate performance applications, especially for large widths.

### **Ripple Counter**

The ripple counter is an asynchronous counter where the Q of each bit feeds the clock of the next bit; performance is sacrificed to build this variation. However, the ripple counter uses the least amount of logic resources. This counter should only be used in very low-performance applications or for very small counters.

Because of the asynchronous nature of the count function, this counter does not have a synchronous load function.

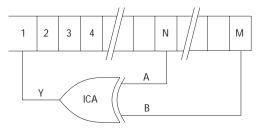

#### **Pseudo Random Counter**

A Pseudo Random Counter is available in SmartGen using a Linear Feedback Shift Register (LFSR) architecture. The LFSR offers an efficient architecture for building very fast Pseudo Random Counters.

Figure 4-1. Pseudo Random Counter Generic Architecture

The Pseudo Random core architecture core is a simple shift register chain that uses two taps (one logic level) for the following widths: 2-7, 9-11, 15, 17, 18, 20-23, 25, 28, 29, and 31. The SmartGen PRNG core uses five taps (three logic levels) for the following widths: 8, 12-14, 16, 19, 24, 26, 27, 30, and 32. The five-tap architecture operates slower than the two-tap implementation.

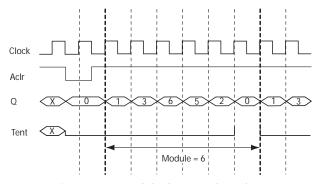

#### **Modulo Counter**

As counter size increases, the amount and complexity of support logic also increases. LFSR base counters achieve high performance using very few logic resources. The Modulo Counter is designed to provide two logic levels independently of the chosen modulo value. The architecture borrows some look-ahead techniques previously used in the register look-ahead counter.

The example below is based on a modulo-6 counter with the following characteristics:

- · Active-HIGH clock edge

- Active-LOW asynchronous clear

- · Active-HIGH synchronous clear

#### • No Enable

Figure 4-2. Modulo Counter Sample

## Decoder

## Decoder

#### **Features**

- Parameterized output size (DECODES)

- Behavioral simulation model in VHDL and Verilog

## **Family Support**

ACT 1, ACT 2, ACT 3, 3200DX, 40 MX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/  $_{\rm F}$

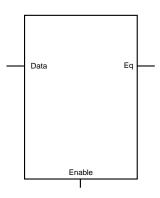

## **Description**

Table 5-1. Port Description

| Port Name | Size               | Туре   | Req/Opt | Function   |

|-----------|--------------------|--------|---------|------------|

| Data      | decln <sup>a</sup> | Input  | Req.    | Input data |

| Enable    | 1                  | Input  | Opt.    | Enable     |

| Eq        | DECODES            | Output | Req.    | output     |

a. decln is an integer and  $\log_2$  (DECODES) = decln d $\log_2$  (DECODES + 1. If decln is equal to 1, then Data is scalar, else Data is a bus.

Table 5-2. Parameter Description

| Parameter   | Value | Function                                              |  |

|-------------|-------|-------------------------------------------------------|--|

| DECODES     | 2-32  | Word length of Eq                                     |  |

| EN_POLARITY | 012   | Enable polarity (active high, active low or not used) |  |

Table 5-2. Parameter Description

| Parameter   | Value | Function                                |

|-------------|-------|-----------------------------------------|

| EQ_POLARITY | 01    | Eq polarity (active low or active high) |

Table 5-3. Functional Description<sup>a</sup>

| Data | Enable | Eq                                                                 |

|------|--------|--------------------------------------------------------------------|

| X    | 0      | 0's                                                                |

| m    | 1      | $dec^b$ (m)==decodes-1 &&c $dec$ (m)==decodes-2 && && $dec$ (m)==0 |

- a. Assume enable is active low and Eq is active high.

- b. dec(m) defines the decimal value of m

- c. && indicates bity concatenation

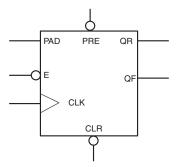

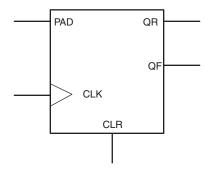

## I/Os

## **Input Buffers**

### **Features**

- · Parameterized for data width

- Choice of data buffers (Regular, Special, Pull-Up, Pull-Down)

## **Family support**

ACT2/1200XL, ACT3, 3200DX, MX, SX, SX-A, eX, 500K, PA, Axcelerator, ProASIC3/E

## **Description**

SmartGen generates different types of Input Buffers with specified data width.

Table 6-1. Port Description

| Port Name                                   | Size  | Туре   | Req/Opt | Function                       |

|---------------------------------------------|-------|--------|---------|--------------------------------|

| PAD                                         | WIDTH | Input  | Req.    | Input Data                     |

| PADP (LVDS and LVPECL,<br>Axcelerator Only) | WIDTH | Input  | Req.    | Input Data for LVDS and LVPECL |

| PADN(LVDS and LVPECL,<br>Axcelerator Only)  | WIDTH | Input  | Req.    | Input Data for LVDS and LVPECL |

| Y                                           | WIDTH | Output | Req.    | Output Data                    |

Table 6-2. Parameter Description

| Parameter           | Value                                         | Function                  |

|---------------------|-----------------------------------------------|---------------------------|

| WIDTH               | 1-99 (Limit may vary depending on the family) | Data Width                |

| PULLUP (Flash Only) | NO / YES                                      | Choice of Pull-up version |

Table 6-2. Parameter Description (Continued)

| Parameter                  | Value                                                                                                                                                                                                                  | Function                                                                  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| VOLT (Flash Only)          | 0,1,2                                                                                                                                                                                                                  | Choice of different voltage<br>levels. 3.3v, 2.5v* or 2.5v<br>(Low Power) |

| TYPE<br>(Axcelerator Only) | REG, LVCMOS25, LVCMOS18,<br>LVCMOS15, PCI, PCIX, GTLP25,<br>GTLP33, HSTL_I, HSTL_II, SSTL3_I,<br>SSTL3_II, SSTL2_I, SSTL2_II, LVDS,<br>LVPECL, LVCMOS25U, LVCMOS25D,<br>LVCMOS18U, LVCMOS18D,<br>LVCMOS15U, LVCMOS15D. | Type of Buffer                                                            |

<sup>\*</sup> Not available for ProASIC  $\underline{^{PLUS}}.$

Table 6-3. Implementation Parameters

| Parameter  | Value                       | Description             |

|------------|-----------------------------|-------------------------|

| LPMTYPE    | LPM_IO/ LPM_IB_IO (Flash)   | Input Buffers           |