# OpenSPARC Internals

OpenSPARC T1/T2

CHIP MULTITHREADED THROUGHPUT COMPUTING

www.OpenSPARC.net

# OpenSPARC™ Internals

OpenSPARC T1/T2 CMT Throughput Computing

David L. Weaver, Editor

Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95054 U.S.A. 650-960-1300

Copyright 2002-2008 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 USA. All rights reserved.

This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. For Netscape Communicator, the following notice applies: Copyright 1995 Netscape Communications Corporation. All rights reserved.

Sun, Sun Microsystems, the Sun logo, Solaris, OpenSolaris, OpenSPARC, Java, MAJC, Sun Fire, UltraSPARC, and VIS are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. or its subsidiaries in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

**RESTRICTED RIGHTS**: Use, duplication, or disclosure by the U.S. Government is subject to restrictions of FAR 52.227-14(g)(2)(6/87) and FAR 52.227-19(6/87), or DFAR 252.227-7015(b)(6/95) and DFAR 227.7202-3(a).

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

**ISBN 978-0-557-01974-8** First printing, October 2008

# Contents

|   | Pref | ace       |             |                                        | xiii |

|---|------|-----------|-------------|----------------------------------------|------|

| 1 | Intr | oducing   | Chip Mult   | ithreaded (CMT) Processors             | 1    |

| 2 | Ope  | nSPARC    | Designs .   |                                        | 7    |

|   | 2.1  | Acadeı    | mic Uses fo | or OpenSPARC                           | 8    |

|   | 2.2  |           |             | for OpenSPARC                          |      |

|   |      | 2.2.1     |             | nplementation                          |      |

|   |      | 2.2.2     |             | Minimization                           |      |

|   |      | 2.2.3     | _           | ssors                                  |      |

|   |      | 2.2.4     |             | ARC as Test Input to CAD/EDA Tools     |      |

| 3 | Arcl | nitecture | Overview    |                                        | 11   |

|   | 3.1  | The Ul    | traSPARC    | Architecture                           | 12   |

|   |      | 3.1.1     | Features    |                                        | 12   |

|   |      | 3.1.2     | Attribute   | es                                     | 13   |

|   |      |           | 3.1.2.1     | Design Goals                           | 14   |

|   |      |           | 3.1.2.2     | Register Windows                       |      |

|   |      | 3.1.3     | System (    | Components                             | 14   |

|   |      |           | 3.1.3.1     | Binary Compatibility                   | 14   |

|   |      |           | 3.1.3.2     | UltraSPARC Architecture MMU            | 15   |

|   |      |           | 3.1.3.3     | Privileged Software                    | 15   |

|   | 3.2  | Proces    | sor Archite | cture                                  | 15   |

|   |      | 3.2.1     | Integer U   | Jnit (IU)                              | 16   |

|   |      | 3.2.2     | Floating-   | Point Unit (FPU)                       | 16   |

|   | 3.3  | Instruc   | tions       |                                        | 17   |

|   |      | 3.3.1     | Memory      | Access                                 | 17   |

|   |      |           | 3.3.1.1     | Memory Alignment Restrictions          |      |

|   |      |           | 3.3.1.2     | Addressing Conventions                 |      |

|   |      |           | 3.3.1.3     | Addressing Range                       | 18   |

|   |      |           | 3.3.1.4     | Load/Store Alternate                   |      |

|   |      |           | 3.3.1.5     | Separate Instruction and Data Memories | 19   |

|   |      |           | 3.3.1.6     | Input/Output (I/O)                     | 20   |

|   |      |           | 3.3.1.7     | Memory Synchronization                 | 20   |

vi Contents

|   |     | 3.3.2  | Integer Arithmetic / Logical / Shift Instructions | 20 |

|---|-----|--------|---------------------------------------------------|----|

|   |     | 3.3.3  | Control Transfer                                  | 20 |

|   |     | 3.3.4  | State Register Access                             | 21 |

|   |     |        | 3.3.4.1 Ancillary State Registers                 | 21 |

|   |     |        | 3.3.4.2 PR State Registers                        | 21 |

|   |     |        | 3.3.4.3 HPR State Registers                       | 22 |

|   |     | 3.3.5  | Floating-Point Operate                            | 22 |

|   |     | 3.3.6  | Conditional Move                                  | 22 |

|   |     | 3.3.7  | Register Window Management                        | 22 |

|   |     | 3.3.8  | SIMD                                              | 22 |

|   | 3.4 | Traps  |                                                   | 23 |

|   | 3.5 | Chip-L | evel Multithreading (CMT)                         | 23 |

| 4 | Ope | nSPARC | T1 and T2 Processor Implementations               | 25 |

|   | 4.1 |        | ıl Background                                     |    |

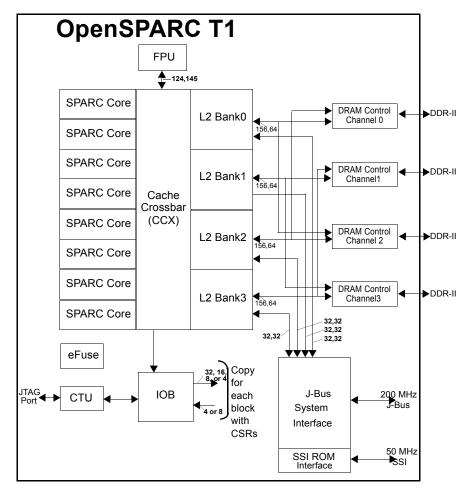

|   | 4.2 | OpenS  | PARC T1 Overview                                  | 27 |

|   | 4.3 | OpenS  | PARC T1 Components                                | 29 |

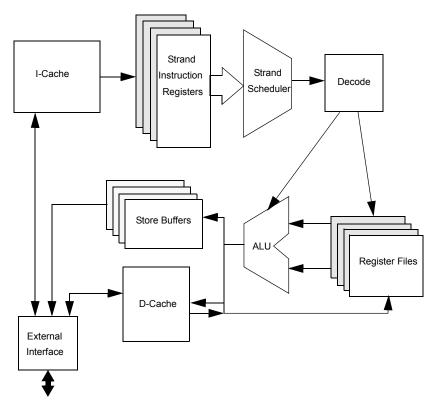

|   |     | 4.3.1  | OpenSPARC T1 Physical Core                        | 29 |

|   |     | 4.3.2  | Floating-Point Unit (FPU)                         |    |

|   |     | 4.3.3  | L2 Cache                                          |    |

|   |     | 4.3.4  | DRAM Controller                                   | 31 |

|   |     | 4.3.5  | I/O Bridge (IOB) Unit                             | 31 |

|   |     | 4.3.6  | J-Bus Interface (JBI)                             |    |

|   |     | 4.3.7  | SSI ROM Interface                                 | 32 |

|   |     | 4.3.8  | Clock and Test Unit (CTU)                         | 32 |

|   |     | 4.3.9  | EFuse                                             | 33 |

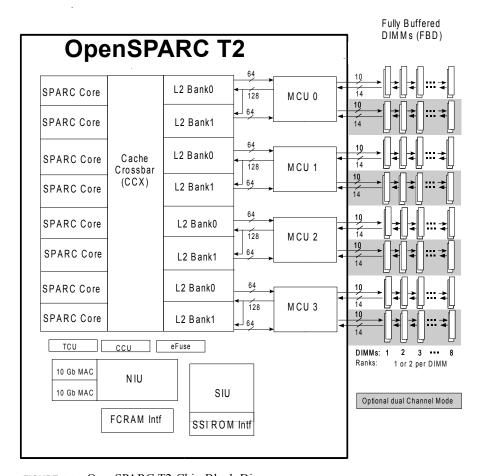

|   | 4.4 | OpenS  | PARC T2 Overview                                  | 33 |

|   | 4.5 | -      | PARC T2 Components                                |    |

|   |     | 4.5.1  | OpenSPARC T2 Physical Core                        |    |

|   |     | 4.5.2  | L2 Cache                                          |    |

|   |     | 4.5.3  | Memory Controller Unit (MCU)                      |    |

|   |     | 4.5.4  | Noncacheable Unit (NCU)                           |    |

|   |     | 4.5.5  | System Interface Unit (SIU)                       |    |

|   |     | 4.5.6  | SSI ROM Interface (SSI)                           |    |

|   | 4.6 | Summa  | ary of Differences Between OpenSPARC T1 and       |    |

|   |     |        | PARC T2                                           | 36 |

|   |     | 4.6.1  | Microarchitectural Differences                    | 37 |

|   |     | 4.6.2  | Instruction Set Architecture (ISA) Differences    | 37 |

|   |     | 4.6.3  | MMU Differences                                   |    |

|   |     | 4.6.4  | Performance Instrumentation Differences           |    |

|   |     | 4.6.5  | Error Handling Differences                        |    |

|   |     | 4.6.6  | Power Management Differences                      |    |

|   |     | 4.6.7  | Configuration, Diagnostic, and Debug Differences  |    |

|   |     |        |                                                   |    |

| 5 | Ope | nSPARC   | T2 Memory Subsystem — A Deeper Look                    | 43 |

|---|-----|----------|--------------------------------------------------------|----|

|   | 5.1 | Caches   |                                                        | 44 |

|   |     | 5.1.1    | L1 I-Cache                                             |    |

|   |     | 5.1.2    | L1 D-Cache                                             |    |

|   |     | 5.1.3    | L2 Cache                                               | 45 |

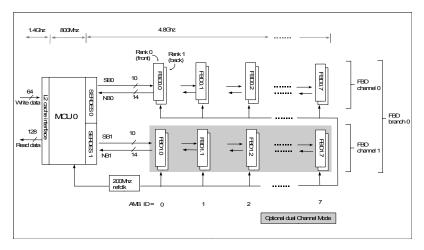

|   | 5.2 | Memor    | y Controller Unit (MCU)                                | 47 |

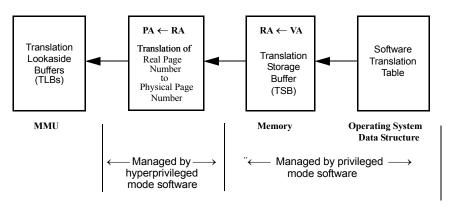

|   | 5.3 | Memor    | y Management Unit (MMU)                                | 50 |

|   |     | 5.3.1    | Address Translation Overview                           | 50 |

|   |     | 5.3.2    | TLB Miss Handling                                      | 51 |

|   |     | 5.3.3    | Instruction Fetching                                   | 52 |

|   |     | 5.3.4    | Hypervisor Support                                     | 53 |

|   |     | 5.3.5    | MMU Operations                                         |    |

|   |     |          | 5.3.5.1 TLB Operation Summary                          |    |

|   |     |          | 5.3.5.2 Demap Operations                               |    |

|   | 5.4 |          | heable Unit (NCU)                                      |    |

|   | 5.5 | System   | Interface Unit (SIU).                                  | 55 |

|   | 5.6 | Data M   | anagement Unit (DMU)                                   | 56 |

|   | 5.7 | Memor    | y Models                                               | 56 |

|   | 5.8 | Memor    | y Transactions                                         | 57 |

|   |     | 5.8.1    | Cache Flushing                                         | 58 |

|   |     | 5.8.2    | Displacement Flushing                                  |    |

|   |     | 5.8.3    | Memory Accesses and Cacheability                       | 59 |

|   |     | 5.8.4    | Cacheable Accesses                                     |    |

|   |     | 5.8.5    | Noncacheable and Side-Effect Accesses                  |    |

|   |     | 5.8.6    | Global Visibility and Memory Ordering                  |    |

|   |     | 5.8.7    | Memory Synchronization: MEMBAR and FLUSH               |    |

|   |     | 5.8.8    | Atomic Operations                                      |    |

|   |     | 5.8.9    | Nonfaulting Load                                       | 63 |

| 6 | Ope | nSPARC   | Processor Configuration                                | 65 |

|   | 6.1 | Selectir | ng Compilation Options in the T1 Core                  | 66 |

|   |     | 6.1.1    | FPGA_SYN                                               | 66 |

|   |     | 6.1.2    | FPGA_SYN_1THREAD                                       | 66 |

|   |     | 6.1.3    | FPGA_SYN_NO_SPU                                        | 66 |

|   |     | 6.1.4    | FPGA_SYN_8TLB                                          |    |

|   |     | 6.1.5    | FPGA_SYN_16TLB                                         |    |

|   |     | 6.1.6    | Future Options.                                        |    |

|   | 6.2 | Changi   | ng Level-1 Cache Sizes                                 |    |

|   |     | 6.2.1    | Doubling the Size of the I-cache                       |    |

|   |     | 6.2.2    | Doubling the Number of Ways in the I-cache             |    |

|   |     | 6.2.3    | Changing Data Cache Sizes.                             |    |

|   | 6.3 | _        | ng Number of Threads                                   |    |

|   | 6.4 |          | ing the Floating-Point Front-End Unit (FFU)            |    |

|   | 6.5 | Adding   | a Second Floating-Point Unit to the OpenSPARC T2 Core. | 73 |

viii Contents

|   | 6.6 | Changing Level-2 Cache Sizes                                   | . 74 |

|---|-----|----------------------------------------------------------------|------|

|   |     | 6.6.1 Changing the Number of L2 Banks                          | . 75 |

|   | 6.7 | Changing the Number of Cores on a Chip                         | . 75 |

|   | 6.8 | Cookbook Example 1: Integrating a New Stall Signaller Into the |      |

|   |     | T1 Thread Scheduler                                            | . 76 |

|   |     | 6.8.1 Background                                               | . 76 |

|   |     | 6.8.2 Implementation                                           | . 77 |

|   |     | 6.8.3 Updating the Monitor                                     | . 78 |

|   | 6.9 | Cookbook Example 2: Adding a Special ASI to the                |      |

|   |     | T1 Instruction Set.                                            | . 79 |

|   |     | 6.9.1 Background                                               |      |

|   |     | 6.9.2 Implementation                                           |      |

|   |     | 6.9.3 Caveats                                                  | . 83 |

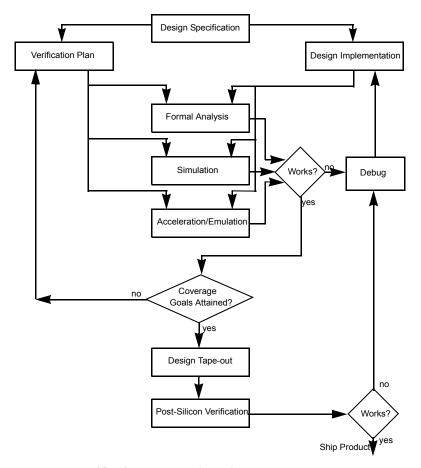

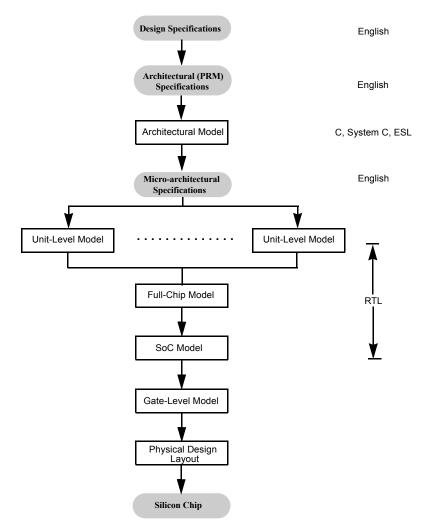

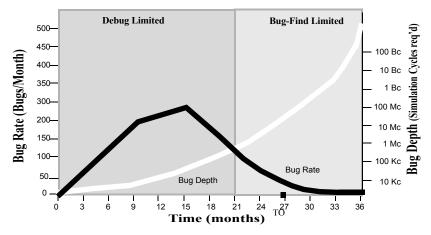

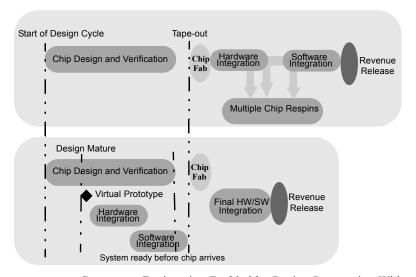

| 7 | Ope | nSPARC Design Verification Methodology                         | . 85 |

|   | 7.1 | Verification Strategy                                          |      |

|   | 7.2 | Models                                                         |      |

|   |     | 7.2.1 Architectural Model                                      |      |

|   |     | 7.2.2 Unit-Level Models                                        |      |

|   |     | 7.2.3 Full-Chip Model                                          |      |

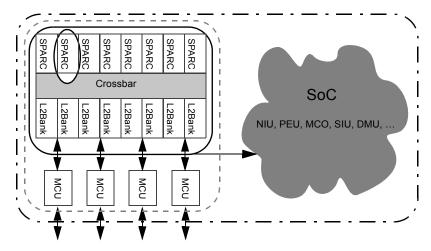

|   |     | 7.2.4 SoC-Level Model                                          | . 92 |

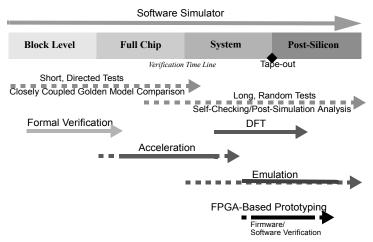

|   | 7.3 | Verification Methods                                           | . 92 |

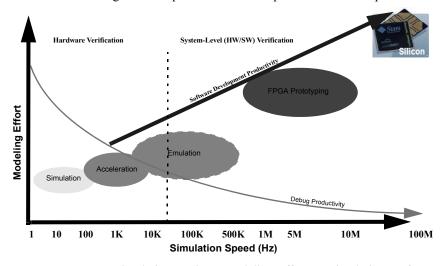

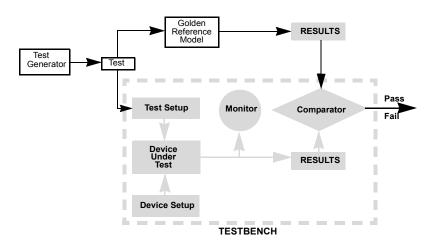

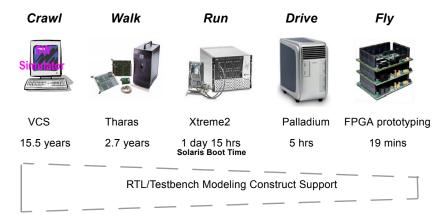

|   | 7.4 | Simulation Verification                                        | . 93 |

|   |     | 7.4.1 Testbench                                                | . 94 |

|   |     | 7.4.2 Assertions                                               | . 96 |

|   |     | 7.4.3 Coverage                                                 |      |

|   |     | 7.4.4 Directed Testing                                         |      |

|   |     | 7.4.5 Random Test Generation                                   |      |

|   |     | 7.4.6 Result Checking                                          |      |

|   | 7.5 | Formal Verification                                            |      |

|   |     | 7.5.1 Design Comparison                                        |      |

|   |     | 7.5.2 Property, or Model, Checking                             |      |

|   | 7.6 | 7.5.3 Symbolic Simulation                                      |      |

|   | 7.6 | Emulation Verification                                         |      |

|   |     | 7.6.1 Emulation Platforms                                      |      |

|   | 7.7 | 7.6.2 Emulation Deployment                                     |      |

|   | 7.7 | Debugging                                                      |      |

|   | 7.8 | Post-Silicon Verification                                      |      |

|   |     | 7.8.1 Silicon Validation                                       |      |

|   |     | 7.8.2 Silicon Debugging                                        |      |

|   | 7.9 | 7.8.3 Silicon Bug-Fix Verification                             |      |

|   |     | Summary                                                        |      |

| 8 | Ope | rating Systems for OpenSPARC T1                                | 121  |

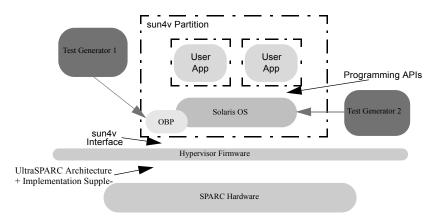

|   | 8.1 | Virtualization                                                 | 121  |

|    | 8.2   | sun4v A  | rchitecture. |                                                  | 122  |

|----|-------|----------|--------------|--------------------------------------------------|------|

|    | 8.3   | SPARC    | Processor E  | extensions                                       | 122  |

|    | 8.4   |          |              | orting                                           |      |

| 9  | Tools | for Deve | lopers       |                                                  | 125  |

|    | 9.1   | Compilia | ng Code      |                                                  | 125  |

|    |       | 9.1.1    |              | Applications With Sun Studio                     |      |

|    |       | 9.1.2    |              | Applications With GCC for SPARC Systems          |      |

|    |       | 9.1.3    |              | Performance With Profile Feedback                |      |

|    |       | 9.1.4    |              | r Cross-File Optimization                        |      |

|    |       | 9.1.5    |              | ΓLB Page Sizes                                   |      |

|    | 9.2   | Explorin | _            | Execution                                        |      |

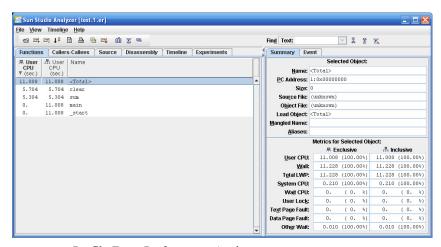

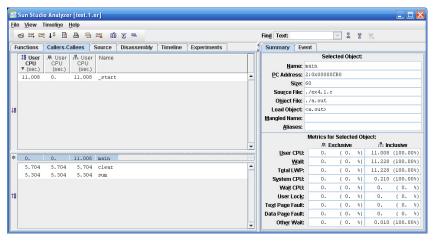

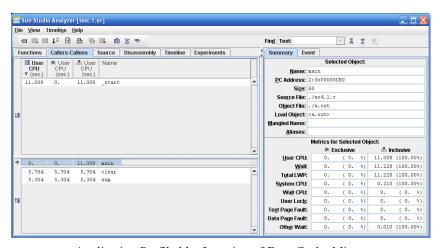

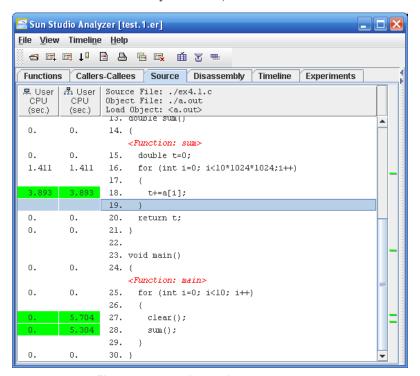

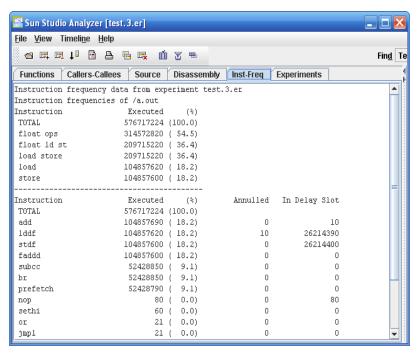

|    |       | 9.2.1    | Profiling V  | Vith Performance Analyzer                        | 132  |

|    |       | 9.2.2    | Gathering    | Instruction Counts With BIT                      | 137  |

|    |       | 9.2.3    | Evaluating   | Training Data Quality                            | 142  |

|    |       | 9.2.4    | Profiling V  | Vith SPOT                                        | 146  |

|    |       | 9.2.5    |              | g With dbx                                       |      |

|    |       | 9.2.6    | _            | cover to Locate Memory Access Errors             |      |

|    | 9.3   | Through  |              | ting                                             |      |

|    |       | 9.3.1    | _            | Processor Utilization                            | 153  |

|    |       | 9.3.2    | _            | Formance Counters to Estimate Instruction        |      |

|    |       |          |              | <b>8</b>                                         | 156  |

|    |       | 9.3.3    |              | Instruction Count Data                           |      |

|    |       | 9.3.4    |              | for Parallelization                              |      |

|    |       | 9.3.5    |              | ng Applications With POSIX Threads               |      |

|    |       | 9.3.6    |              | ng Applications With OpenMP                      |      |

|    |       | 9.3.7    | Using Auto   | oparallelization to Produce Parallel Application | 1S . |

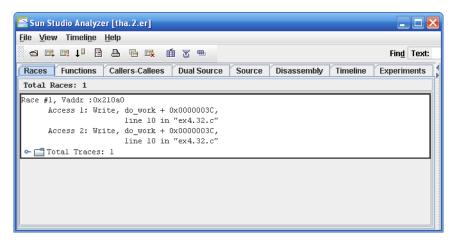

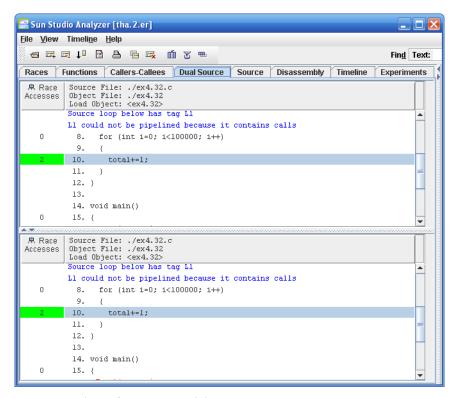

|    |       | 9.3.8    | Detecting    | Data Races With the Thread Analyzer              | 165  |

|    |       | 9.3.9    |              | Data Races                                       |      |

|    |       | 9.3.10   |              | ng Microparallelization                          |      |

|    |       | 9.3.11   | Programm     | ing for Throughput                               | 177  |

| 10 | Syste | m Simula | ation, Brin  | gup, and Verification                            | 179  |

|    | 10.1  | SPARC .  | Architectur  | e Model                                          | 180  |

|    |       | 10.1.1   | SPARC CI     | PU Model                                         | 181  |

|    |       | 10.1.2   | VCPU Inte    | erface                                           | 182  |

|    |       |          | 10.1.2.1     | Control Interface                                | 183  |

|    |       |          | 10.1.2.2     | System Interface                                 | 183  |

|    |       |          | 10.1.2.3     | Trace Interface                                  |      |

|    |       | 10.1.3   | Module M     | odel Interface                                   |      |

|    |       |          | 10.1.3.1     | SAM Configuration File                           |      |

|    |       |          | 10.1.3.2     | Module Loading and Unloading                     |      |

|    |       |          | 10.1.3.3     | Module Initialization                            | 185  |

**x** Contents

|    | 10.2 | System    | Configuration File                            | 186     |

|----|------|-----------|-----------------------------------------------|---------|

|    |      | 10.2.1    | The sysconf Directive Format                  | 186     |

|    |      | 10.2.2    | Examples                                      |         |

|    |      | 10.2.3    | Simulated Time in SAM                         | 189     |

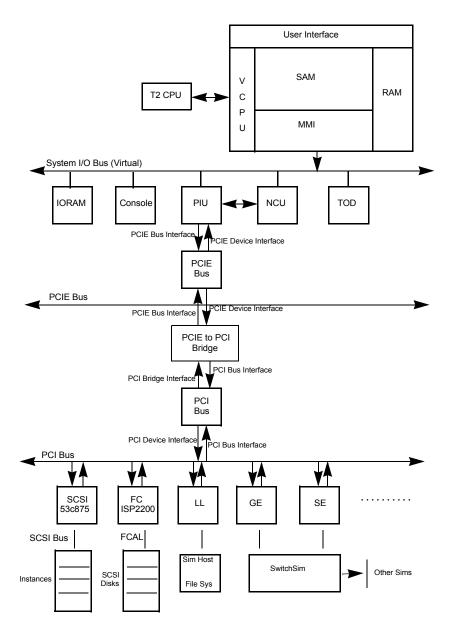

|    | 10.3 | SAM H     | uron Sim Architecture                         | 190     |

|    |      | 10.3.1    | Sample Configuration File for T2 Huron on SAM | 192     |

|    |      | 10.3.2    | Serial Device Module                          | 193     |

|    |      | 10.3.3    | NCU Module                                    | 196     |

|    |      | 10.3.4    | PIU Module                                    | 197     |

|    |      | 10.3.5    | IORAM Module                                  |         |

|    |      | 10.3.6    | Time-of-Day Module                            |         |

|    |      | 10.3.7    | PCI-E Bus Module                              |         |

|    |      | 10.3.8    | PCIE-PCI Bridge Module                        |         |

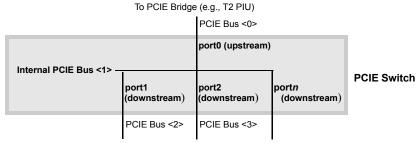

|    |      | 10.3.9    | PCIE-PCIE Bridge Module                       |         |

|    |      | 10.3.10   | Serially Attached SCSI Module.                |         |

|    |      | 10.3.11   | LLFS Module                                   |         |

|    | 10.4 |           | of a Root Disk Image File                     |         |

|    | 10.5 |           | ing With SAM                                  |         |

|    |      | 10.5.1    | Simulated State Access                        | 211     |

|    |      | 10.5.2    | Symbol Information                            |         |

|    |      | 10.5.3    | Breakpoints                                   |         |

|    |      | 10.5.4    | Debug Tracing                                 |         |

|    |      | 10.5.5    | Probes                                        |         |

|    | 10.6 | •         | ccurate Simulation                            |         |

|    |      | 10.6.1    | Trace-Driven Approach                         |         |

|    |      | 10.6.2    | Execution-Driven Approach                     |         |

|    |      | 10.6.3    | Submodule Approach                            |         |

|    |      | 10.6.4    | Conclusion.                                   |         |

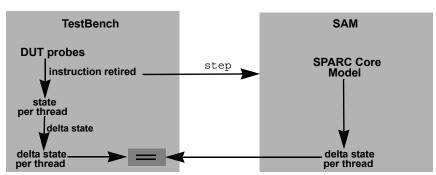

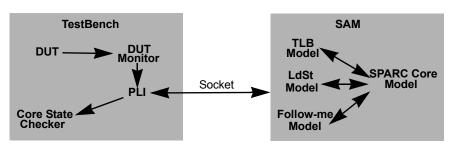

|    | 10.7 | Verificat | tion by Cosimulation                          |         |

|    |      | 10.7.1    | RTL Cosimulation                              |         |

|    |      |           | 10.7.1.1 TLB-Sync Model                       |         |

|    |      |           | 10.7.1.2 LdSt-Sync Model                      |         |

|    |      |           | 10.7.1.3 Follow-Me Model                      |         |

|    |      | 10.7.2    | RTL-SAM Cosimulation Summary                  | 226     |

| 11 | Open | SPARC     | Extension and Modification—Case Study         | 227     |

| A  | Over | view: Op  | enSPARC T1/T2 Source Code and Environment So  | etup239 |

|    | A.1  | OpenSP.   | ARC T1 Hardware Package                       | 239     |

|    |      | A.1.1     | T1 Hardware Package Structure                 | 240     |

|    |      | A.1.2     | Documentation                                 |         |

|    |      | A.1.3     | Design Source Code                            |         |

|    |      | A.1.4     | Xilinx Embedded Development Kit Project       |         |

|    |      | A.1.5     | Design Libraries                              |         |

|    |      | A.1.6     | Verification Environment                      | 242     |

|    |      | A.1.7     | Tools                                         | 243     |

|    |      |           |                                               |         |

|   | A.2  | OpenSP    | ARC T2 Ha    | ardware Package                            | 243 |

|---|------|-----------|--------------|--------------------------------------------|-----|

|   |      | A.2.1     |              | ation                                      |     |

|   |      | A.2.2     | Design So    | urce Code                                  | 244 |

|   |      | A.2.3     |              | braries                                    |     |

|   |      | A.2.4     |              | on Environment                             |     |

|   |      | A.2.5     | Tools        |                                            | 246 |

|   | A.3  | Setup fo  |              | PARC Environment                           |     |

| В | Over | view of ( | OpenSPAR     | C T1 Design                                | 249 |

|   | B.1  | SPARC     | Core         |                                            | 249 |

|   | B.2  | L2 Cach   | ne           |                                            | 251 |

|   |      | B.2.1     |              | Single Bank                                |     |

|   |      | B.2.2     | L2 Cache     | Instructions                               | 254 |

|   |      | B.2.3     |              | Pipeline                                   |     |

|   |      | B.2.4     |              | Memory Coherency and Instruction Ordering. |     |

|   | B.3  | Memory    |              |                                            |     |

|   | B.4  |           |              |                                            |     |

|   |      | B.4.1     | -            | Functions                                  |     |

|   |      | B.4.2     | IOB Misce    | ellaneous Functions                        | 259 |

|   |      | B.4.3     |              | aces                                       |     |

|   | B.5  | Floating  |              | (FPU)                                      |     |

|   |      | B.5.1     |              | oint Instructions                          |     |

|   |      | B.5.2     | Floating-P   | oint Unit Power Management                 | 263 |

|   |      | B.5.3     |              | oint Register Exceptions and Traps         |     |

|   | B.6  | J-Bus In  |              |                                            |     |

|   |      | B.6.1     |              | uests to the L2 Cache                      |     |

|   |      | B.6.2     | I/O Buffer   | Requests to the J-Bus                      | 265 |

|   |      | B.6.3     |              | rrupt Requests to the IOB                  |     |

| C | Over | view of C | OpenSPAR(    | C T2 Design                                | 267 |

|   | C.1  |           |              | esign and Features                         |     |

|   | C.2  |           |              |                                            |     |

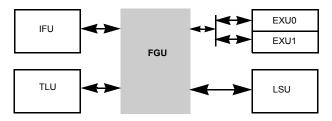

|   |      | C.2.1     |              | n Fetch Unit (IFU)                         |     |

|   |      | C.2.2     |              | Unit                                       |     |

|   |      | C.2.3     |              | e Unit (LSU)                               |     |

|   |      |           | C.2.3.1      | Changes From OpenSPARC T1                  |     |

|   |      |           | C.2.3.2      | Functional Units of the LSU                |     |

|   |      |           | C.2.3.3      | Special Memory Operation Handling          | 273 |

|   | C.3  | L2 Cach   | ne           |                                            | 275 |

|   |      | C.3.1     | L2 Function  | onal Units                                 | 275 |

|   |      | C.3.2     | L2 Cache     | Interfaces                                 | 277 |

|   |      | C.3.3     |              | Instructions                               |     |

|   | C.4  | Cache C   | Crossbar     |                                            | 280 |

|   | C.5  | Memory    | y Controller | Unit                                       | 280 |

|   |      | C.5.1     |              | o the OpenSPARC T2 MCU                     |     |

|   |      | C.5.2     | _            | nch Configuration                          |     |

**xii** Contents

|   |            | C.5.3 FBD Channel Configuration                  | 282 |

|---|------------|--------------------------------------------------|-----|

|   |            | C.5.4 SDRAM Initialization                       |     |

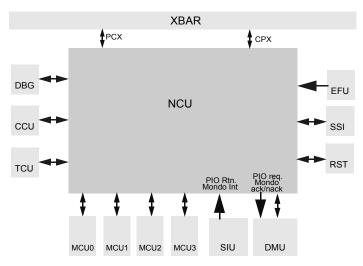

|   | C.6        | Noncacheable Unit (NCU)                          |     |

|   |            | C.6.1 Changes from OpenSPARC T1 I/O Bridge       |     |

|   |            | C.6.2 NCU Interfaces                             |     |

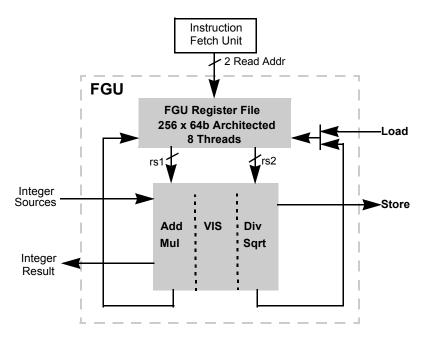

|   | C.7        | Floating-Point and Graphics Unit (FGU)           | 285 |

|   |            | C.7.1 FGU Feature Comparison of OpenSPARC T2 and |     |

|   |            | OpenSPARC T1                                     |     |

|   |            | C.7.2 Performance                                |     |

|   | C 0        | C.7.3 FGU Interfaces                             |     |

|   | C.8<br>C.9 | Trap Logic Unit (TLU)                            |     |

|   | C.9        | Reliability and Serviceability                   |     |

|   |            | C.9.2 Core Error Logging                         |     |

|   | C.10       | Reset                                            |     |

|   | C.11       | Performance Monitor Unit (PMU)                   |     |

|   | C.12       | Debugging Features                               |     |

|   | C.13       | Test Control Unit (TCU)                          |     |

|   | C.14       | System Interface Unit (SIU)                      |     |

| D | Open       | SPARC T1 Design Verification Suites              | 303 |

|   | D.1        | OpenSPARC T1 Verification Environment            |     |

|   | D.2        | Regression Tests.                                |     |

|   |            | D.2.1 The sims Command Actions                   |     |

|   |            | D.2.2 Running Regression With Other Simulators   | 307 |

|   | D.3        | Verification Code                                |     |

|   |            | D.3.1 Verilog Code Used for Verification         |     |

|   |            | D.3.2 Vera Code Used for Verification            |     |

|   | D.4        | PLI Code Used for the Testbench                  |     |

|   | D.5        | Verification Test File Locations                 |     |

|   | D.6        | Compilation of Source Code for Tools             |     |

|   | D.7        | Gate-Level Verification                          |     |

| E | Open       | SPARC T2 Design Verification Suites              |     |

|   | E.1        | System Requirements                              | 315 |

|   | E.2        | OpenSPARC T2 Verification Environment            |     |

|   | E.3        | Regression Tests.                                |     |

|   | E.4        | PLI Code Used For the Testbench                  |     |

|   | E.5        | Verification Test File Locations                 |     |

| F |            | SPARC Resources                                  |     |

| G | Open       | SPARC Terminology                                | 323 |

|   | Index      | · · · · · · · · · · · · · · · · · · ·            | 347 |

# **Preface**

Open-source software? Sure, everyone has heard of that. We all take advantage of it as we navigate through the Internet (OpenSolaris<sup>TM</sup>, Java<sup>TM</sup>, Linux, Apache, Perl, etc.) and even when we sit down to relax with TiVo (Linux) or watch a Blu-Ray disc (Java).

But open-source *hardware* ... eh? What is open-source *hardware*?! Small amounts of computer hardware Intellectual Property (IP) have been available for many years in open-source form, typically as circuit descriptions written in an RTL (Register Transfer Level) language such as Verilog or VHDL. However, until now, few large hardware designs have been available in open-source form. One of the most complex designs imaginable is for a complete microprocessor; with the notable exception of the LEON 32-bit SPARC® processor, *none* have been available in open-source form until recently.

In March 2006, the complete design of Sun Microsystems' UltraSPARC<sup>TM</sup> T1 microprocessor was released—in open-source form, it was named OpenSPARC<sup>TM</sup> T1. In early 2008, its successor, OpenSPARC<sup>TM</sup> T2, was also released in open-source form. These were the first (and still only) 64-bit microprocessors ever open-sourced. They were also the first (and still only) CMT (chip multithreaded) microprocessors ever open-sourced. Both designs are freely available from the OpenSPARC<sup>TM</sup> website, http://www.OpenSPARC.net, to anyone. These downloads include not only the processor design source code but also simulation tools, design verification suites, Hypervisor source code, and other helpful tools. Variants that easily synthesize for FPGA targets are also available.

**xiv** Preface

# Organization of Book

This book is intended as a sort of "tour guide" for those who have downloaded the OpenSPARC T1 or OpenSPARC T2 design, or might be considering doing so. •

- Chapter 1, *Introducing Chip Multithreaded (CMT) Processors*, addresses the question "why build a multithreaded processor?"

- Chapter 2, *OpenSPARC Designs*, describes some example uses for these designs.

- Chapter 3, *Architecture Overview*, backs up a step and describes the architecture on which OpenSPARC processors are based.

- Chapter 4, *OpenSPARC T1 and T2 Processor Implementations*, dives into the microarchitecture of both OpenSPARC T1 and OpenSPARC T2.

- Chapter 5, OpenSPARC T2 Memory Subsystem A Deeper Look, describes the memory system.

- Chapter 6, *OpenSPARC Processor Configuration*, explains how to configure a synthesized design from the actual RTL code and provides a couple of examples of useful modifications to the design.

- The design verification methodology used by Sun to verify the processors on which OpenSPARC is based is explained in Chapter 7, *OpenSPARC Design Verification Methodology*.

- Chapter 8, *Operating Systems for OpenSPARC T1*, lists operating systems that already run on OpenSPARC and gives an overview of how you can port your own operating system to run on top of Hypervisor on an OpenSPARC implementation.

- In Chapter 9, *Tools for Developers*, the emphasis shifts to software, as the chapter describes the tools that are available for developing high-performance software for OpenSPARC.

- Software is again the focus in Chapter 10, System Simulation, Bringup, and Verification, which discusses OpenSPARC system simulation, RTL, and cosimulation.

- Chapter 11, *OpenSPARC Extension and Modification—Case Study*, presents a real-world example of getting started with the OpenSPARC RTL and tools.

Notational Conventions xv

Appendix A, Overview: OpenSPARC T1/T2 Source Code and Environment Setup, gives an overview of the source code trees for OpenSPARC T1 and OpenSPARC T2 and describes how to set up a functional development environment around them.

- Appendix B and Appendix C provide "deep dives" into the OpenSPARC T1 and OpenSPARC T2 designs, respectively.

- Use of the Verification suites for OpenSPARC T1 and OpenSPARC T2 is found, respectively, in Appendix D and Appendix E.

- Appendix F, *OpenSPARC Resources*, lists URLs for OpenSPARC resources available on the World Wide Web.

- Lastly, Appendix G provides a glossary of terminology used in this book.

# **Notational Conventions**

Fonts are used as follows:

- *Italic* font is used for emphasis, book titles, and the first instance of a word that is defined.

- *Italic* font is also used for terms where substitution is expected, for example, "fccn", "virtual processor n", or "reg\_plus\_imm".

- *Italic sans serif* font is used for exception and trap names. For example, "The *privileged\_action* exception...."

- lowercase arial font is used for register field names (named bits) and instruction field names, for example: "The rs1 field contains...."

- UPPERCASE ARIAL font is used for register names; for example, FSR.

- TYPEWRITER (Courier) font is used for literal values, such as code (assembly language, C language, ASI names) and for state names. For example: %f0, ASI\_PRIMARY, execute\_state.

- When a register field is shown along with its containing register name, they are separated by a period ('.'), for example, "FSR.cexc".

Case, underscores, and hyphens are used as follows.

UPPERCASE words are acronyms or instruction names. Some common acronyms appear in the glossary in Appendix G, *OpenSPARC Terminology*.

Note: Names of some instructions contain both upper- and lower-case letters.

**xvi** Preface

An underscore character joins words in register, register field, exception, and trap names. Note: Such words may be split across lines at the underbar without an intervening hyphen. For example: "This is true whenever the integer\_condition\_ code field...."

A hyphen joins multiple words in a variable name; for example, "ioram-instance-name".

The following notational conventions are used:

- The left arrow symbol (←) is the assignment operator. For example, "PC ← PC + 1" means that the Program Counter (PC) is incremented by 1.

- Square brackets ([]) are used in two different ways, distinguishable by the context in which they are used:

- Square brackets indicate indexing into an array. For example, TT[TL]

means the element of the Trap Type (TT) array, as indexed by the

contents of the Trap Level (TL) register.

- Square brackets are also used to indicate optional additions/extensions to symbol names. For example, "ST[D|Q]F" expands to all three of "STF", "STDF", and "STQF". Similarly, ASI\_PRIMARY[\_LITTLE] indicates two related address space identifiers, ASI\_PRIMARY and ASI\_PRIMARY\_LITTLE. (Contrast with the use of angle brackets, below)

- Angle brackets ( < > ) indicate mandatory additions/extensions to symbol names. For example, "ST<D|Q>F" expands to mean "STDF" and "STQF". (Contrast with the second use of square brackets, above.)

- Curly braces ( { } ) indicate a bit field within a register or instruction. For example, CCR{4} refers to bit 4 in the Condition Code register.

- A consecutive set of values is indicated by specifying the upper and lower limit of the set separated by a colon (:), for example, CCR{3:0} refers to the set of four least significant bits of register CCR.

Notation for numbers is as follows.

- Numbers are decimal (base-10) unless otherwise indicated. Numbers in other bases are followed by a numeric subscript indicating their base (for example, 1001<sub>2</sub>, FFFF 0000<sub>16</sub>).

- Long binary and hexadecimal numbers within the text have spaces inserted every four characters to improve readability.

- Within C language or assembly language examples, numbers may be preceded by "0x" to indicate base-16 (hexadecimal) notation (for example, 0xFFFF0000).

Acknowledgments xvii

# Acknowledgments

*OpenSPARC Internals* is the result of collaboration among many contributors. I would particularly like to acknowledge the following people for their key contributions:

- Lawrence Spracklen, for contributing the text of Chapter 1

- Sreenivas Vadlapatla, for coordinating the content of Chapter 5

- Paul Jordan, for contributing portions of Chapter 5

- Tom Thatcher, for contributing the bulk of Chapter 6 and Appendix A

- **Jared Smolens**, for contributing the "cookbook" examples at the end of Chapter 6

- Jai Kumar, for contributing the text of Chapter 7

- **Kevin Clague**, for contributions to Chapter 7

- Gopal Reddy, for contributing the text of Chapter 8

- **Darryl Gove** (author of the *Solaris Application Programming* book), for contributing Chapter 9

- Alex Tsirfa, for contributing the text of Chapter 10

- Fabrizio Fazzino, for contributing the text of Chapter 11

- **Durgam Vahia**, for extracting the text of Appendix B through Appendix E from the sources listed below

The following people contributed to the quality of this book by providing meticulous reviews of its drafts and answers to critical questions: Paul Jordan, Jared Smolens, Jeff Brooks, and Aaron Wynn.

Last, but *far* from least, thanks to **Mary Lou Nohr**, for pulling it all together and making everyone else look good (yet *again*)

**xviii** Preface

# Sources

I would also like to acknowledge the sources, listed in the table below, from which Appendixes B through E were derived.

| App. | Source                                                                                                                 | Part # / Date / Rev                                                  |

|------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| В    | OpenSPARC T1 Microarchitecture<br>Specification                                                                        | 819-6650-10 Aug. 2006,<br>Rev. A                                     |

| С    | OpenSPARC T2 Microarchitecture<br>Specification<br>OpenSPARC T2 System-On-Chip (SoC)<br>Micrarchitecture Specification | 820-2545-10 July 2007,<br>Rev. 5<br>820-2620-05 July 2007,<br>Rev. 5 |

| D    | OpenSPARC T1 Design and Verification User's Guide (Chapter 3)                                                          | 819-5019-12, Mar 2007,<br>Rev. A                                     |

| Е    | OpenSPARC T2 Design and Verification User's Guide (Chapter 3)                                                          | 820-2729-10, Dec 2007,<br>Rev. A                                     |

# Editor's Note

We hope you find OpenSPARC Internals accurate, readable, and stimulating.

—David Weaver Editor, OpenSPARC Internals

Corrections and other comments regarding this book can be emailed to: OpenSPARC-book-editor@sun.com

# Introducing Chip Multithreaded (CMT) Processors

Much of the material in this chapter was leveraged from L. Spracklen and S. G. Abraham, "Chip Multithreading: Opportunities and Challenges," in 11th International Symposium on High-Performance Computer Architecture, 2005.

Over the last few decades microprocessor performance has increased exponentially, with processor architects successfully achieving significant gains in single-thread performance from one processor generation to the next. Semiconductor technology has been the main driver for this increase, with faster transistors allowing rapid increases in clock speed to today's multi-GHz frequencies. In addition to these frequency increases, each new technology generation has essentially doubled the number of available transistors. As a result, architects have been able to aggressively chase increased single-threaded performance by using a range of expensive microarchitectural techniques, such as; superscalar issue, out-of-order issue, on-chip caching, and deep pipelines supported by sophisticated branch predictors.

However, process technology challenges, including power constraints, the memory wall, and ever-increasing difficulties in extracting further instruction-level parallelism (ILP), are all conspiring to limit the performance of individual processors in the future. While recent attempts at improving single-thread performance through even deeper pipelines have led to impressive clock frequencies, these clock frequencies have not translated into significantly better performance in comparison with less aggressive designs. As a result, microprocessor frequency, which used to increase exponentially, has now leveled off, with most processors operating in the 2–4 GHz range.

This combination of the limited realizable ILP, practical limits to pipelining, and a "power ceiling" imposed by cost-effective cooling considerations have conspired to limit future performance increases within conventional processor cores. Accordingly, processor designers are searching for new ways to effectively utilize their ever-increasing transistor budgets.

The techniques being embraced across the microprocessor industry are chip multiprocessors (CMPs) and chip multithreaded (CMT) processors. CMP, as the name implies, is simply a group of processors integrated onto the same chip. The individual processors typically have comparable performance to their single-core brethren, but for workloads with sufficient thread-level parallelism (TLP), the aggregate performance delivered by the processor can be many times that delivered by a single-core processor. Most current processors adopt this approach and simply involve the replication of existing single-processor processor cores on a single die.

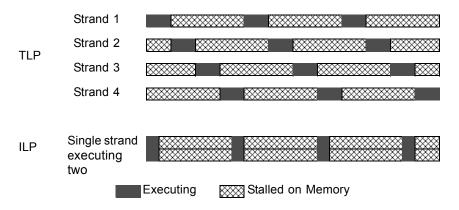

Moving beyond these simple CMP processors, chip multithreaded (CMT) processors go one step further and support many simultaneous hardware strands (or threads) of execution per core by simultaneous multithreading (SMT) techniques. SMT effectively combats increasing latencies by enabling multiple strands to share many of the resources within the core, including the execution resources. With each strand spending a significant portion of time stalled waiting for off-chip misses to complete, each strand's utilization of the core's execution resources is extremely low. SMT improves the utilization of key resources and reduces the sensitivity of an application to off-chip misses. Similarly, as with CMP, multiple cores can share chip resources such as the memory controller, off-chip bandwidth, and the level-2/level-3 cache, improving the utilization of these resources.

The benefits of CMT processors are apparent in a wide variety for application spaces. For instance, in the commercial space, server workloads are broadly characterized by high levels of TLP, low ILP, and large working sets. The potential for further improvements in overall single-thread performance is limited; on-chip cycles per instruction (CPI) cannot be improved significantly because of low ILP, and off-chip CPI is large and growing because of relative increases in memory latency. However, typical server applications concurrently serve a large number of users or clients; for instance, a database server may have hundreds of active processes, each associated with a different client. Furthermore, these processes are currently multithreaded to hide disk access latencies. This structure leads to high levels of TLP. Thus, it is extremely attractive to couple the high TLP in the application domain with support for multiple threads of execution on a processor chip.

Evolution of CMTs 3

Though the arguments for CMT processors are often made in the context of overlapping memory latencies, memory bandwidth considerations also play a significant role. New memory technologies, such as fully buffered DIMMs (FBDs), have higher bandwidths (for example, 60 GB/s/chip), as well as higher latencies (for example, 130 ns), pushing up their bandwidth-delay product to  $60 \text{ GB/s} \times 130 \text{ ns} = 7800 \text{ bytes}$ . The processor chip's pins represent an expensive resource, and to keep these pins fully utilized (assuming a cache line size of 64 bytes), the processor chip must sustain 7800/64 or over 100 parallel requests. To put this in perspective, a single strand on an aggressive out-of-order processor core generates less than two parallel requests on typical server workloads: therefore, a large number of strands are required to sustain a high utilization of the memory ports.

Finally, power considerations also favor CMT processors. Given the almost cubic dependence between core frequency and power consumption, the latter drops dramatically with reductions in frequency. As a result, for workloads with adequate TLP, doubling the number of cores and halving the frequency delivers roughly equivalent performance while reducing power consumption by a factor of four.

#### Evolution of CMTs

Given the exponential growth in transistors per chip over time, a rule of thumb is that a board design becomes a chip design in ten years or less. Thus, most industry observers expected that chip-level multiprocessing would eventually become a dominant design trend. The case for a single-chip multiprocessor was presented as early as 1996 by Kunle Olukotun's team at Stanford University. Their Stanford Hydra CMP processor design called for the integration of four MIPS-based processors on a single chip. A DEC/Compaq research team proposed the incorporation of eight simple Alpha cores and a two-level cache hierarchy on a single chip (code-named Piranha) and estimated a simulated performance of three times that of a single-core, next-generation Alpha processor for on-line transaction processing workloads.

As early as the mid-1990s, Sun recognized the problems that would soon face processor designers as a result of the rapidly increasing clock frequencies required to improve single-thread performance. In response, Sun defined the MAJC architecture to target thread-level parallelism. Providing well-defined support for both CMP and SMT processors, MAJC architecture was industry's first step toward general-purpose CMT processors. Shortly after publishing the MAJC architecture, Sun announced its first MAJC-compliant processor (MAJC-5200), a dual-core CMT processor with cores sharing an L1 data cache.

Subsequently, Sun moved its SPARC processor family toward the CMP design point. In 2003, Sun announced two CMP SPARC processors: Gemini, a dual-core UltraSPARC II derivative; and UltraSPARC IV. These first-generation CMP processors were derived from earlier uniprocessor designs, and the two cores did not share any resources other than off-chip datapaths. In most CMP designs, it is preferable to share the outermost caches, because doing so localizes coherency traffic between the strands and optimizes inter-strand communication in the chip—allowing very fine-grained thread interaction (microparallelism). In 2003, Sun also announced its second-generation CMP processor, UltraSPARC IV+, a follow-on to the UltraSPARC IV processor, in which the on-chip L2 and off-chip L3 caches are shared between the two cores.

In 2006, Sun introduced a 32-way CMT SPARC processor, called UltraSPARC T1, for which the entire design, including the cores, is optimized for a CMT design point. UltraSPARC T1 has eight cores; each core is a fourway SMT with its own private L1 caches. All eight cores share a 3-Mbyte, 12-way level-2 cache,. Since UltraSPARC T1 is targeted at commercial server workloads with high TLP, low ILP, and large working sets, the ability to support many strands and therefore many concurrent off-chip misses is key to overall performance. Thus, to accommodate eight cores, each core supports single issue and has a fairly short pipeline.

Sun's most recent CMT processor is the UltraSPARC T2 processor. The UltraSPARC T2 processor provides double the threads of the UltraSPARC T1 processor (eight threads per core), as well as improved single-thread performance, additional level-2 cache resources (increased size and associativity), and improved support for floating-point operations.

Sun's move toward the CMT design has been mirrored throughout industry. In 2001, IBM introduced the dual-core POWER-4 processor and recently released second-generation CMT processors, the POWER-5 and POWER-6 processors, in which each core supports 2-way SMT. While this fundamental shift in processor design was initially confined to the high-end server processors, where the target workloads are the most thread-rich, this change has recently begun to spread to desktop processors. AMD and Intel have also subsequently released multicore CMP processors, starting with dual-core CMPs and more recently quad-core CMP processors. Further, Intel has announced that its next-generation quad-core processors will support 2-way SMT, providing a total of eight threads per chip.

CMT is emerging as the dominant trend in general-purpose processor design, with manufacturers discussing their multicore plans beyond their initial quadcore offerings. Similar to the CISC-to-RISC shift that enabled an entire processor to fit on a single chip and internalized all communication between

pipeline stages to within a chip, the move to CMT represents a fundamental shift in processor design that internalizes much of the communication between processors to within a chip.

#### Future CMT Designs

An attractive proposition for future CMT design is to just double the number of cores per chip every generation since a new process technology essentially doubles the transistor budget. Little design effort is expended on the cores, and performance is almost doubled every process generation on workloads with sufficient TLP. Though reusing existing core designs is an attractive option, this approach may not scale well beyond a couple of process generations. Processor designs are already pushing the limits of power dissipation. For the total power consumption to be restrained, the power dissipation of each core must be halved in each generation. In the past, supply voltage scaling delivered most of the required power reduction, but indications are that voltage scaling will not be sufficient by itself. Though well-known techniques, such as clock gating and frequency scaling, may be quite effective in the short term, more research is needed to develop low-power, high-performance cores for future CMT designs.

Further, given the significant area cost associated with high-performance cores, for a fixed area and power budget, the CMP design choice is between a small number of high-performance (high frequency, aggressive out-of-order, large issue width) cores or multiple simple (low frequency, in-order, limited issue width) cores. For workloads with sufficient TLP, the simpler core solution may deliver superior chipwide performance at a fraction of the power. However, for applications with limited TLP, unless speculative parallelism can be exploited, CMT performance will be poor. One possible solution is to support heterogeneous cores, potentially providing multiple simple cores for thread-rich workloads and a single more complex core to provide robust performance for single-threaded applications.

Another interesting opportunity for CMT processors is support for on-chip hardware accelerators. Hardware accelerators improve performance on certain specialized tasks and off-load work from the general-purpose processor. Additionally, on-chip hardware accelerators may be an order of magnitude more power efficient than the general-purpose processor and may be significantly more efficient than off-chip accelerators (for example, eliminating the off-chip traffic required to communicate to an off-chip accelerator). Although high cost and low utilization typically make on-chip hardware accelerators unattractive for traditional processors, the cost of an accelerator can be amortized over many strands, thanks to the high degree of resource sharing associated with CMTs. While a wide variety of hardware

accelerators can be envisaged, emerging trends make an extremely compelling case for supporting on-chip network off-load engines and cryptographic accelerators. The future processors will afford opportunities for accelerating other functionality. For instance, with the increasing usage of XML-formatted data, it may become attractive to have hardware support XML parsing and processing.

Finally, for the same amount of off-chip bandwidth to be maintained per core, the total off-chip bandwidth for the processor chip must also double every process generation. Processor designers can meet the bandwidth need by adding more pins or increasing the bandwidth per pin. However, the maximum number of pins per package is only increasing at a rate of 10 percent per generation. Further packaging costs per pin are barely going down with each new generation and increase significantly with pin count. As a result, efforts have recently focused on increasing the per-pin bandwidth by innovations in the processor chip to DRAM memory interconnect through technologies such as double data rate and fully buffered DIMMs. Additional benefits can be obtained by doing more with the available bandwidth; for instance, by compressing off-chip traffic or exploiting silentness to minimize the bandwidth required to perform write-back operations. Compression of the on-chip caches themselves can also improve performance, but the (significant) additional latency that is introduced as a result of the decompression overhead must be carefully balanced against the benefits of the reduced miss rate, favoring adaptive compression strategies.

As a result, going forward we are likely to see an ever-increasing proportion of CMT processors designed from the ground-up in order to deliver ever-increasing performance while satisfying these power and bandwidth constraints.

# OpenSPARC Designs

Sun Microsystems began shipping the UltraSPARC T1 chip multithreaded (CMT) processor in December 2005. Sun surprised the industry by announcing that it would not only ship the processor but also *open-source* that processor—a first in the industry. By March 2006, UltraSPARC T1 had been open-sourced in a distribution called OpenSPARC T1, available on http://openSPARC.net.

In 2007, Sun began shipping its newer, more advanced UltraSPARC T2 processor, and open-sourced the bulk of that design as OpenSPARC T2.

The "source code" for both designs offered on OpenSPARC.net is comprehensive, including not just millions of lines of the hardware description language (Verilog, a form of "register transfer logic"—RTL) for these microprocessors, but also scripts to compile ("synthesize") that source code into hardware implementations, source code of processor and full-system simulators, prepackaged operating system images to boot on the simulators, source code to the Hypervisor software layer, a large suite of verification software, and thousands of pages of architecture and implementation specification documents.

This book is intended as a "getting started" companion to both OpenSPARC T1 and OpenSPARC T2. In this chapter, we begin that association by addressing this question: *Now that Sun has open-sourced OpenSPARC T1 and T2, what can they be used for?*

One thing is certain: the real-world uses to which OpenSPARC will be put will be infinitely more diverse and interesting than anything that could be suggested in this book! Nonetheless, this short chapter offers a few ideas, in the hope that they will stimulate even more creative thinking ...

# 2.1 Academic Uses for OpenSPARC

The utility of OpenSPARC in academia is limited only by students' imaginations.

The most common academic use of OpenSPARC to date is as a complete example processor architecture and/or implementation. It can be used in coursework areas such as computer architecture, VLSI design, compiler code generation/optimization, and general computer engineering.

In university lab courses, OpenSPARC provides a design that can be used as a known-good starting point for assigned projects.

OpenSPARC can be used as a basis for compiler research, such as for code generation/optimization for highly threaded target processors or for experimenting with instruction set changes and additions.

OpenSPARC is already in use in multiple FPGA-based projects at universities. For more information, visit:

```

http://www.opensparc.net/fpga/index.html

```

For more information on programs supporting academic use of OpenSPARC, including availability of the Xilinx OpenSPARC FPGA Board, visit web page: http://www.OpenSPARC.net/edu/university-program.html

Specific questions about university programs can be posted on the OpenSPARC general forum at:

http://forums.sun.com/forum.jspa?forumID=837 or emailed to OpenSPARC-UniversityProgram@sun.com.

Many of the commercial applications of OpenSPARC, mentioned in the following section, suggest corresponding academic uses.

# 2.2 Commercial Uses for OpenSPARC

OpenSPARC provides a springboard for design of commercial processors. By starting from a complete, known-good design—including a full verification suite—the time-to-market for a new custom processor can be drastically slashed.

Derivative processors ranging from a simple single-core, single-thread design all the way up through an 8-core, 64-thread design can rapidly be synthesized from OpenSPARC T1 or T2.

# 2.2.1 FPGA Implementation

An OpenSPARC design can be synthesized and loaded into a field-programmable gate array (FPGA) device. This can be used in several ways:

- An FPGA version of the processor can be used for product prototyping, allowing rapid design iteration

- An FPGA can be used to provide a high-speed simulation engine for a processor under development

- For extreme time-to-market needs where production cost per processor isn't critical, a processor could even be shipped in FPGA form. This could also be useful if the processor itself needs to be field-upgradable via a software download.

# 2.2.2 Design Minimization

Portions of a standard OpenSPARC design that are not needed for the target application can be stripped out, to make the resulting processor smaller, cheaper, faster, and/or with higher yield rates. For example, for a network routing application, perhaps hardware floating-point operations are superfluous—in which case, the FPU(s) can be removed, saving die area and reducing verification effort.

# 2.2.3 Coprocessors

Specialized coprocessors can be incorporated into a processor based on OpenSPARC. OpenSPARC T2, for example, comes with a coprocessor containing two 10 Gbit/second Ethernet transceivers (the network interface unit or "NIU"). Coprocessors can be added for any conceivable purpose, including (but hardly limited to) the following:

- Network routing

- Floating-point acceleration

- Cryptographic processing

- I/O compression/decompression engines

- Audio compression/decompression (codecs)

- Video codecs

- I/O interface units for embedded devices such as displays or input sensors

# 2.2.4 OpenSPARC as Test Input to CAD/ EDA Tools

The OpenSPARC source code (Verilog RTL) provides a large, real-world input dataset for CAD/EDA tools. It can be used to test the robustness of CAD tools and simulators. Many major commercial CAD/EDA tool vendors are already using OpenSPARC this way!

# Architecture Overview

OpenSPARC processors are based on a processor architecture named the UltraSPARC Architecture. The OpenSPARC T1 design is based on the UltraSPARC Architecture 2005, and OpenSPARC T2 is based on the UltraSPARC Architecture 2007. This chapter is intended as an overview of the architecture; more details can be found in the *UltraSPARC Architecture 2005 Specification* and the *UltraSPARC Architecture 2007 Specification*.

The UltraSPARC Architecture is descended from the SPARC V9 architecture and complies fully with the "Level 1" (nonprivileged) SPARC V9 specification.

The UltraSPARC Architecture supports 32-bit and 64-bit integer and 32-bit, 64-bit, and 128-bit floating-point as its principal data types. The 32-bit and 64-bit floating-point types conform to IEEE Std 754-1985. The 128-bit floating-point type conforms to IEEE Std 1596.5-1992. The architecture defines general-purpose integer, floating-point, and special state/status register instructions, all encoded in 32-bit-wide instruction formats. The load/store instructions address a linear, 2<sup>64</sup>-byte virtual address space.

As used here, the word *architecture* refers to the processor features that are visible to an assembly language programmer or to a compiler code generator. It does not include details of the implementation that are not visible or easily observable by software, nor those that only affect timing (performance).

The chapter contains these sections:

- The UltraSPARC Architecture on page 12

- Processor Architecture on page 15

- *Instructions* on page 17

- Traps on page 23

- Chip-Level Multithreading (CMT) on page 23

# 3.1 The UltraSPARC Architecture

This section briefly describes features, attributes, and components of the UltraSPARC Architecture and, further, describes correct implementation of the architecture specification and SPARC V9-compliance levels.

#### 3.1.1 Features

The UltraSPARC Architecture, like its ancestor SPARC V9, includes the following principal features:

- A linear 64-bit address space with 64-bit addressing.

- **32-bit wide instructions** These are aligned on 32-bit boundaries in memory. Only load and store instructions access memory and perform I/O.

- Few addressing modes A memory address is given as either "register + register" or "register + immediate".

- Triadic register addresses Most computational instructions operate on two register operands or one register and a constant and place the result in a third register.

- A large windowed register file At any one instant, a program sees 8 global integer registers plus a 24-register window of a larger register file.

The windowed registers can be used as a cache of procedure arguments, local values, and return addresses.

- **Floating point** The architecture provides an IEEE 754-compatible floating-point instruction set, operating on a separate register file that provides 32 single-precision (32-bit), 32 double-precision (64-bit), and 16 quad-precision (128-bit) overlayed registers.

- Fast trap handlers Traps are vectored through a table.

- **Multiprocessor synchronization instructions** Multiple variations of atomic load-store memory operations are supported.

- **Predicted branches** The branch with prediction instructions allows the compiler or assembly language programmer to give the hardware a hint about whether a branch will be taken.

- **Branch elimination instructions** Several instructions can be used to eliminate branches altogether (for example, Move on Condition). Eliminating branches increases performance in superscalar and superpipelined implementations.

• Hardware trap stack — A hardware trap stack is provided to allow nested traps. It contains all of the machine state necessary to return to the previous trap level. The trap stack makes the handling of faults and error conditions simpler, faster, and safer.

In addition, UltraSPARC Architecture includes the following features that were not present in the SPARC V9 specification:

- Hyperprivileged mode— This mode simplifies porting of operating systems, supports far greater portability of operating system (privileged) software, supports the ability to run multiple simultaneous guest operating systems, and provides more robust handling of error conditions. Hyperprivileged mode is described in detail in the Hyperprivileged version of the *UltraSPARC Architecture 2005 Specification* or the *UltraSPARC Architecture 2007 Specification*.

- Multiple levels of global registers Instead of the two 8-register sets of global registers specified in the SPARC V9 architecture, the UltraSPARC Architecture provides multiple sets; typically, one set is used at each trap level.

- Extended instruction set The UltraSPARC Architecture provides many instruction set extensions, including the VIS instruction set for "vector" (SIMD) data operations.

- More detailed, specific instruction descriptions UltraSPARC Architecture specifications provide many more details regarding what exceptions can be generated by each instruction, and the specific conditions under which those exceptions can occur, than did SPARC V9. Also, detailed lists of valid ASIs are provided for each load/store instruction from/to alternate space.

- Detailed MMU architecture Although some details of the UltraSPARC MMU architecture are necessarily implementation-specific, UltraSPARC Architecture specifications provide a blueprint for the UltraSPARC MMU, including software view (TTEs and TSBs) and MMU hardware control registers.

- Chip-level multithreading (CMT) The UltraSPARC Architecture provides a control architecture for highly threaded processor implementations.

#### 3 1 2 Attributes

The UltraSPARC Architecture is a processor *instruction set architecture* (ISA) derived from SPARC V8 and SPARC V9, which in turn come from a reduced instruction set computer (RISC) lineage. As an architecture, the UltraSPARC

Architecture allows for a spectrum of processor and system *implementations* at a variety of price/performance points for a range of applications, including scientific or engineering, programming, real-time, and commercial applications. OpenSPARC further extends the possible breadth of design possibilities by opening up key implementations to be studied, enhanced, or redesigned by anyone in the community.

#### 3.1.2.1 Design Goals

The UltraSPARC Architecture is designed to be a target for optimizing compilers and high-performance hardware implementations. The *UltraSPARC Architecture 2005* and *UltraSPARC Architecture 2007 Specification* documents provide design specs against which an implementation can be verified, using appropriate verification software.

#### 3.1.2.2 Register Windows

The UltraSPARC Architecture architecture is derived from the SPARC architecture, which was formulated at Sun Microsystems in 1984 through 1987. The SPARC architecture is, in turn, based on the RISC I and II designs engineered at the University of California at Berkeley from 1980 through 1982. The SPARC "register window" architecture, pioneered in the UC Berkeley designs, allows for straightforward, high-performance compilers and a reduction in memory load/store instructions.

Note that privileged software, not user programs, manages the register windows. Privileged software can save a minimum number of registers (approximately 24) during a context switch, thereby optimizing context-switch latency.

## 3.1.3 System Components

The UltraSPARC Architecture allows for a spectrum of subarchitectures, such as cache system, I/O, and memory management unit (MMU).

#### 3.1.3.1 Binary Compatibility

An important mandate for the UltraSPARC Architecture is compatibility across implementations of the architecture for application (nonprivileged) software, down to the binary level. Binaries executed in nonprivileged mode should behave identically on all UltraSPARC Architecture systems when those

systems are running an operating system known to provide a standard execution environment. One example of such a standard environment is the SPARC V9 Application Binary Interface (ABI).

Although different UltraSPARC Architecture systems can execute nonprivileged programs at different rates, they will generate the same results as long as they are run under the same memory model. See Chapter 9, *Memory*, in an UltraSPARC Architecture specification for more information.

Additionally, UltraSPARC Architecture 2005 and UltraSPARC Architecture 2007 are are upward-compatible from SPARC V9 for applications running in nonprivileged mode that conform to the SPARC V9 ABI and upward-compatible from SPARC V8 for applications running in nonprivileged mode that conform to the SPARC V8 ABI.

An OpenSPARC implementation may or may not maintain the same binary compatibility, depending on how the implementation has been modified and what software execution environment is run on it.

#### 3.1.3.2 UltraSPARC Architecture MMU

UltraSPARC Architecture defines a common MMU architecture (see Chapter 14, *Memory Management*, in any UltraSPARC Architecture specification for details). Some specifics are left implementation-dependent.

### 3.1.3.3 Privileged Software

UltraSPARC Architecture does not assume that all implementations must execute identical privileged software (operating systems) or hyperprivileged software (hypervisors). Thus, certain traits that are visible to privileged software may be tailored to the requirements of the system.

# 3.2 Processor Architecture

An UltraSPARC Architecture processor—therefore an OpenSPARC processor—logically consists of an integer unit (IU) and a floating-point unit (FPU), each with its own registers. This organization allows for implementations with concurrent integer and floating-point instruction execution. Integer registers are 64 bits wide; floating-point registers are 32, 64, or 128 bits wide. Instruction operands are single registers, register pairs, register quadruples, or immediate constants.

A *virtual processor* (synonym: *strand*) is the hardware containing the state for execution of a software thread. A *physical core* is the hardware required to execute instructions from one or more software threads, including resources shared among strands. A complete *processor* comprises one or more physical cores and is the physical module that plugs into a system.

An OpenSPARC virtual processor can run in *nonprivileged* mode, *privileged* mode, or *hyperprivileged* mode. In hyperprivileged mode, the processor can execute any instruction, including privileged instructions. In privileged mode, the processor can execute nonprivileged and privileged instructions. In nonprivileged mode, the processor can only execute nonprivileged instructions. In nonprivileged or privileged mode, an attempt to execute an instruction requiring greater privilege than the current mode causes a trap to hyperprivileged software.

# 3.2.1 Integer Unit (IU)

An OpenSPARC implementation's integer unit contains the general-purpose registers and controls the overall operation of the virtual processor. The IU executes the integer arithmetic instructions and computes memory addresses for loads and stores. It also maintains the program counters and controls instruction execution for the FPU.

An UltraSPARC Architecture implementation may contain from 72 to 640 general-purpose 64-bit R registers. This corresponds to a grouping of the registers into a number of sets of global R registers plus a circular stack of  $N_REG_WINDOWS$  sets of 16 registers each, known as register windows. The number of register windows present ( $N_REG_WINDOWS$ ) is implementation dependent, within the range of 3 to 32 (inclusive). In an unmodified OpenSPARC T1 or T2 implementation,  $N_REG_WINDOWS = 8$ .

# 3.2.2 Floating-Point Unit (FPU)

An OpenSPARC FPU has thirty-two 32-bit (single-precision) floating-point registers, thirty-two 64-bit (double-precision) floating-point registers, and sixteen 128-bit (quad-precision) floating-point registers, some of which overlap (as described in detail in UltraSPARC Architecture specifications).

If no FPU is present, then it appears to software as if the FPU is permanently disabled.

3.3 Instructions 17

If the FPU is not enabled, then an attempt to execute a floating-point instruction generates an fp\_disabled trap and the fp\_disabled trap handler software must either

- Enable the FPU (if present) and reexecute the trapping instruction, or

- Emulate the trapping instruction in software.

# 3.3 Instructions

Instructions fall into the following basic categories:

- · Memory access

- Integer arithmetic / logical / shift

- Control transfer

- State register access

- Floating-point operate

- Conditional move

- Register window management

- SIMD (single instruction, multiple data) instructions

These classes are discussed in the following subsections.

# 3.3.1 Memory Access

Load, store, load-store, and PREFETCH instructions are the only instructions that access memory. They use two R registers or an R register and a signed 13-bit immediate value to calculate a 64-bit, byte-aligned memory address. The integer unit appends an ASI to this address.

The destination field of the load/store instruction specifies either one or two R registers or one, two, or four F registers that supply the data for a store or that receive the data from a load.

Integer load and store instructions support byte, halfword (16-bit), word (32-bit), and extended-word (64-bit) accesses. There are versions of integer load instructions that perform either sign-extension or zero-extension on 8-bit, 16-bit, and 32-bit values as they are loaded into a 64-bit destination register. Floating-point load and store instructions support word, doubleword, and quadword<sup>1</sup> memory accesses.

<sup>1.</sup> OpenSPARC T1 and T2 processors do not implement the LDQF instruction in hardware; it generates an exception and is emulated in hyperprivileged software.

CASA, CASXA, and LDSTUB are special atomic memory access instructions that concurrent processes use for synchronization and memory updates.