# OpenSPARC™ T2 Processor Design and Verification User's Guide

Sun Microsystems, Inc. www.sun.com

Part No. 820-2729-10 May 2008, Revision B Copyright 2007 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, California 95054, U.S.A. All rights reserved.

Sun Microsystems, Inc. has intellectual property rights relating to technology that is described in this document. In particular, and without limitation, these intellectual property rights may include one or more of the U.S. patents listed at http://www.sun.com/patents and one or more additional patents or pending patent applications in the U.S. and in other countries.

This document and the product to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of the product or of this document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any.

Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, Java, AnswerBook2, docs.sun.com, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and in other countries.

All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and in other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and  $Sun^TM$  Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Sun Kerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Sun Kerox Graphical User Interface, which license also covers Sun is licensees who implement Sun LOOK Sun and otherwise comply with Sun is written license agreements.

U.S. Government Rights—Commercial use. Government users are subject to the Sun Microsystems, Inc. standard license agreement and applicable provisions of the FAR and its supplements.

DOCUMENTATION AND REGISTER TRANSFER LEVEL (RTL) ARE PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2007 Sun Microsystems, Inc., 4150 Network Circle, Santa Clara, Californie 95054, États-Unis. Tous droits réservés.

Sun Microsystems, Inc. possède les droits de propriété intellectuels relatifs à la technologie décrite dans ce document. En particulier, et sans limitation, ces droits de propriété intellectuels peuvent inclure un ou plusieurs des brevets américains listés sur le site http://www.sun.com/patents, un ou les plusieurs brevets supplémentaires ainsi que les demandes de brevet en attente aux les États-Unis et dans d'autres pays.

Ce document et le produit auquel il se rapporte sont protégés par un copyright et distribués sous licences, celles-ci en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a.

Tout logiciel tiers, sa technologie relative aux polices de caractères, comprise, est protégé par un copyright et licencié par des fournisseurs de Sun.

Des parties de ce produit peuvent dériver des systèmes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque déposée aux Etats-Unis et dans d'autres pays, licenciée exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, Java, AnswerBook2, docs.sun.com, et Solaris sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc. aux États-Unis et dans d'autres pays.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux États-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface utilisateur graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox dans la recherche et le développement du concept des interfaces utilisateur visuelles ou graphiques pour l'industrie informatique. Sun détient une license non exclusive de Xerox sur l'interface utilisateur graphique Xerox, cette licence couvrant également les licenciés de Sun implémentant les interfaces utilisateur graphiques OPEN LOOK et se conforment en outre aux licences écrites de Sun.

LA DOCUMENTATION EST FOURNIE "EN L'ÉTAT" ET TOUTES AUTRES CONDITIONS, DÉCLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES DANS LA LIMITE DE LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE À LA QUALITÉ MARCHANDE, À L'APTITUDE À UNE UTILISATION PARTICULIÈRE OU À L'ABSENCE DE CONTREFAÇON.

# Contents

### Preface ix

1. Quick Start 1-1

|    | 1.1  | System Requirements 1–1                   |

|----|------|-------------------------------------------|

|    | 1.2  | Running Simulations and Synthesis 1–3     |

| 2. | Open | SPARC T2 Design Implementation 2–1        |

|    | 2.1  | OpenSPARC T2 Design 2–1                   |

|    | 2.2  | OpenSPARC T2 Components 2–3               |

|    |      | 2.2.1 SPARC Physical Core 2–4             |

|    |      | 2.2.2 SPARC System-On Chip (SoC) 2–4      |

|    | 2.3  | Module Directory Structure 2–5            |

|    | 2.4  | Megacells 2–6                             |

| 3. | Open | SPARC T2 Verification Environment 3–1     |

|    | 3.1  | OpenSPARC T2 Verification Environment 3–1 |

|    | 3.2  | Running a Regression 3–3                  |

|    |      | 3.2.1 What the sims Command Does 3–4      |

|    | 3.3  | PLI Code Used For the Test Bench 3–5      |

|    | 3.4  | Verification Test File Locations 3–5      |

|    |      |                                           |

#### 4. OpenSPARC T2 Synthesis 4–1

- 4.1 Synthesis Flow for the OpenSPARC T2 Processor 4–1

- 4.2 Synthesis Output 4–3

#### A. Design and Verification Manual Pages A-1

- A.1 sims A-1

- A.2 midas help A–22

- A.3 regreport A-31

# Figures

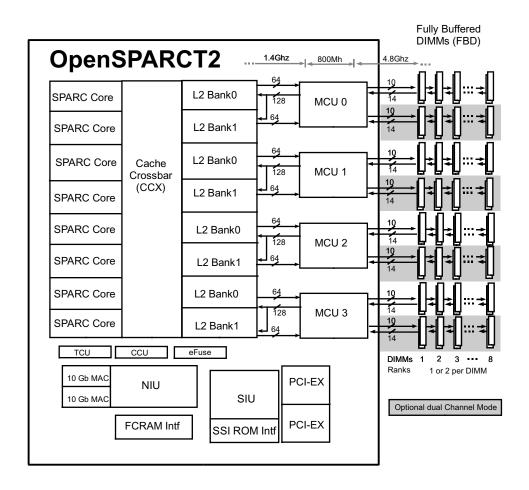

FIGURE 2-1 OpenSPARC T2 Chip Block Diagram 2–3

# **Tables**

| TABLE 1-1 | Disk Space Requirements 1–1                           |

|-----------|-------------------------------------------------------|

| TABLE 1-2 | Contents of the OpenSPARCT2 Directory 1–3             |

| TABLE 1-3 | Environment Variables in .cshrc File 1-4              |

| TABLE 2-1 | OpenSPARC T2 Top-Level Clusters 2–5                   |

| TABLE 3-1 | Source Code Types in the Verification Environment 3–2 |

| TABLE 3-2 | Details of Regression Groups 3–3                      |

| TABLE 3-3 | PLI Source Code and Object Libraries 3–5              |

| TABLE 3-4 | Verification Test File Directories 3–6                |

| TABLE 4-1 | Synthesis Script Details 4-2                          |

| TABLE 4-2 | Synthesis Output 4–3                                  |

| TABLE A-1 | Enviroment Variables A-19                             |

### **Preface**

The *OpenSPARC™ T2 Processor Design and Verification User's Guide* gives an overview of the design hierarchy on the OpenSPARC T2 processor. It also describes the files, procedures, and tools needed for running simulations and synthesis on the OpenSPARC T2 processor.

This book covers the following topics:

- Design and Verification implementation overview

- Design and Verification directory and files structure

- System and Electronic Design Automation (EDA) tools required to run simulations and synthesis

- Tools and scripts required to run simulation or complete regressions, including simulation flow

- Synthesis flow and scripts

## How This Document Is Organized

Chapter 1 describes quick steps to run simulations after you download the design and verification files from the web site. It also includes system requirements and EDA tools requirements to run simulations and synthesis.

Chapter 2 gives an overview of the OpenSPARC T2 design hierarchy and directory structure.

Chapter 3 gives an overview of the OpenSPARC T2 verification environment implementation and directory structure. The verification environment includes test benches, tests, scripts, and Verilog Programming Language Interface (PLI).

Chapter 4 describes the synthesis flow and synthesis scripts.

### Using UNIX Commands

This document might not contain information about basic UNIX® commands and procedures such as shutting down the system, booting the system, and configuring devices. Refer to the following for this information:

- Software documentation that you received with your system

- Solaris<sup>TM</sup> Operating System documentation, which is at:

http://docs.sun.com

### Shell Prompts

| Shell                                 | Prompt        |

|---------------------------------------|---------------|

| C shell                               | machine-name% |

| C shell superuser                     | machine-name# |

| Bourne shell and Korn shell           | \$            |

| Bourne shell and Korn shell superuser | #             |

# Typographic Conventions

| Typeface* | Meaning                                                                                                            | Examples                                                                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AaBbCc123 | The names of commands, files, and directories; on-screen computer output                                           | Edit your.login file.<br>Use 1s -a to list all files.<br>% You have mail.                                                                                                  |

| AaBbCc123 | What you type, when contrasted with on-screen computer output                                                      | % <b>su</b><br>Password:                                                                                                                                                   |

| AaBbCc123 | Book titles, new words or terms, words to be emphasized. Replace command-line variables with real names or values. | Read Chapter 6 in the <i>User's Guide</i> .  These are called <i>class</i> options.  You <i>must</i> be superuser to do this.  To delete a file, type rm <i>filename</i> . |

<sup>\*</sup> The settings on your browser might differ from these settings.

### Related Documentation

The documents listed as online or download are available at:

http://www.opensparc.net/

| Application                                                                | Title                                                                | Part Number | Format | Location |

|----------------------------------------------------------------------------|----------------------------------------------------------------------|-------------|--------|----------|

| Documentation                                                              | OpenSPARC T2 Core Microarchitecture Specification                    | 820-2545    | PDF    | Online   |

| Documentation                                                              | OpenSPARC T2 System-On-Chip (SoC)<br>Microarchitecture Specification | 820-2620    | PDF    | Online   |

| Documentation                                                              | OpenSPARC T2 Processor Megacell Specification                        | 820-2728    | PDF    | Online   |

| Documentation OpenSPARC T2 Processor Design a<br>Verification User's Guide |                                                                      | 820-2729    | PDF    | Online   |

### Documentation, Support, and Training

| Sun Function  | URL                               |

|---------------|-----------------------------------|

| Documentation | http://www.sun.com/documentation/ |

| Support       | http://www.sun.com/support/       |

| Training      | http://www.sun.com/training/      |

### Third-Party Web Sites

Sun is not responsible for the availability of third-party web sites mentioned in this document. Sun does not endorse and is not responsible or liable for any content, advertising, products, or other materials that are available on or through such sites or resources. Sun will not be responsible or liable for any actual or alleged damage or loss caused by or in connection with the use of or reliance on any such content, goods, or services that are available on or through such sites or resources.

### Sun Welcomes Your Comments

Sun is interested in improving its documentation and welcomes your comments and suggestions. You can submit your comments by going to:

http://www.sun.com/hwdocs/feedback

Please include the title and part number of your document with your feedback:

OpenSPARC T2 Processor Design and Verification User's Guide, part number 820-2729-10

### **Quick Start**

This chapter covers the following topics:

- System Requirements

- EDA Tool Requirements

- Running Simulations and Synthesis

Before you start running simulations or synthesis, make sure you meet system requirements and that you have the required Electronic Design Automation (EDA) tools. Once you download the OpenSPARC T2 tar file from the <a href="http://www.opensparc.net">http://www.opensparc.net</a> web site, follow the steps in this chapter to get started and run your first regression on the OpenSPARC T2 design.

# 1.1 System Requirements

OpenSPARC T2 regressions are currently supported to run on SPARC systems running the Solaris 9 or Solaris 10 Operating System and x86\_64 systems running Linux operating system.

Disk space requirements are listed in TABLE 1-1.

**TABLE 1-1** Disk Space Requirements

| Disk Space required | Required for:                                                |

|---------------------|--------------------------------------------------------------|

| 3.1 Gbyte           | Download, unzip or uncompress, and extract from the tar file |

| 0.3 Gbyte           | Run a mini-regression                                        |

**TABLE 1-1** Disk Space Requirements

| Disk Space required | Required for:         |  |  |

|---------------------|-----------------------|--|--|

| 11.5 Gbyte          | Run a full regression |  |  |

| 1.1 Gbyte           | Run synthesis         |  |  |

| 17 Gbyte            | Total                 |  |  |

#### **EDA Tool Requirements**

This section describes the commercial EDA tools required for running simulations for the OpenSPARC T2 processor and synthesizing OpenSPARC T2 Verilog Register Transfer Level (RTL) code.

#### **EDA Simulation Tools**

The following EDA tools are required to run Verilog simulations: Verilog Simulator, either VCS or NCVerilog.

- VCS from Synopsys, version vcsY-2006.06-7 or later OR

- NCVerilog from Cadence, version neverilog,v6.11 or later

- Vera from Synopsys, version vera,vX-2005.12-1 or later

The following EDA tools are optional for running Verilog simulations:

■ Debussy from Novas, version 5.3v19 or later

#### **EDA Synthesis Tools**

The following EDA tool is required to perform Verilog RTL synthesis:

■ Design Compiler from Synopsys, version X-2005.09 or later

# 1.2 Running Simulations and Synthesis

This section outlines the steps needed to obtain the simulation tools, set up the simulation environment, run the simulation, and read its log file.

### **▼** Get the Simulation Files

1. Download the file.

Download the OpenSPARCT2.tar.bz2 file from the http://www.opensparc.net web site. For this procedure's examples, the destination directory is:

/home/johndoe/OpenSPARCT2

2. Change directories to the directory where you downloaded the file. For example:

```

% cd /home/johndoe/OpenSPARCT2

```

3. Use the bunzip2 command to unzip the file.

```

% bunzip2 OpenSPARCT2.tar.bz2

```

4. Extract the tar file using the tar command.

```

% tar -xvf OpenSPARCT2.tar

```

This step creates the files and subdirectories listed in TABLE 1-2 in your current directory.

**TABLE 1-2** Contents of the OpenSPARCT2 Directory

| Name                        | Туре      | Description                                                                   |

|-----------------------------|-----------|-------------------------------------------------------------------------------|

| OpenSPARCT2.cshrc           | File      | File to set up environment variables and paths for the SPARC/Solaris platform |

| OpenSPARCT2.cshrc.<br>linux | File      | File to set up environment variables and paths for the x64/Linux platform     |

| README                      | File      | Instructions to set up and run simulations                                    |

| lib                         | Directory | Verilog libraries                                                             |

| verif                       | Directory | Verification directories and files                                            |

TABLE 1-2

Contents of the OpenSPARCT2 Directory (Continued)

| Name   | Туре      | Description                                               |

|--------|-----------|-----------------------------------------------------------|

| design | Directory | Verilog RTL for OpenSPARC T2 design                       |

| tools  | Directory | Tools and scripts needed to run simulations and synthesis |

| doc    | Directory | Documentation in PDF form for the OpenSPARC T2 processor  |

### ▼ Set Up Environment Variables

Edit the OpenSPARCT2.cshrc file to set the required environment variables as shown in TABLE 1-3:

TABLE 1-3

Environment Variables in .cshrc File

| <b>Environment Variable</b> | Usage                             | Example value                                                                                                       |

|-----------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|

| DV_ROOT                     | Running simulations and synthesis | /home/johndoe/OpenSPARCT2 (Directory where you ran the tar command above)                                           |

| MODEL_DIR                   | Running simulations               | /home/johndoe/OpenSPARCT2_model (Directory where you want to run your simulations)                                  |

| VERA_HOME                   | Running simulations               | /import/EDAtools/vera/vera,v6.2.10/5.x (Directory where Vera is installed)                                          |

| NOVAS_HOME                  | Running simulations               | /import/EDAtools/debussy/debussy,v5.3v19/5.x<br>(Directory where Debussy is installed)                              |

| VCS_HOME                    | Running VCS simulations           | /import/EDAtools/vcs7.1.1R21<br>(Directory where VCS is installed)                                                  |

| NCV_HOME                    | Running NCV simulation            | /import/EDAtools/ncverilog/ncverilog,v6.11.s3/5.x (Directory where NCV is installed)                                |

| SYN_HOME                    | Running synthesis                 | /import/EDAtools/synopsys/synopsys.vX-2005.09<br>(Directory where Synopsys is installed)                            |

| CC_BIN                      | Compiling PLI code                | /import/freetools/local/gcc/3.3.2/bin (Directory where C++ Compiler binaries are installed)                         |

| LM_LICENSE_FILE             | Running simulations and synthesis | <pre>/import/EDAtools/licenses/synopsys_key:/import/ EDAtools/licenses/ncverilog_key (EDA tool license files)</pre> |

**Note** – For x64/Linux platform, edit OpenSPARCT2.cshrc.linux file to set required environment variables

Once you set the environment variables from TABLE 1-3, the OpenSPARCT2.cshrc file sets the following environment variables:

- TRE\_ENTRY

- TRE\_SEARCH

- PERL MODULE BASE

- PERL\_PATH

The OpenSPARCT2.cshrc script also adds the following directories to your PATH and path variables:

- \$DV\_ROOT/tools/bin

- \$VCS\_HOME/bin

- \$VERA HOME/bin

- \$SYN\_HOME/sparcOS5/syn/bin

- \$CC\_BIN

After completing your OpenSPARCT2.cshrc file edits, source it by using the source command:

#### % source /home/johndoe/OpenSPARCT2/OpenSPARCT2.cshrc

You might want to include the above command in your ~/.cshrc file so that the above environment variables are set every time you log in.

### ▼ Run Your First Regression

The OpenSPARC T2 Design/Verification package comes with four test bench environments: cmp1, cmp8, fc1, and fc8.

The cmp1 environment consists of:

- One SPARC CPU core

- Cache

- Memory

- Crossbar

The cmp1 environment does not have an I/O subsystem.

The cmp8 environment consists of:

- Eight SPARC CPU cores

- Cache

- Memory

#### Crossbar

The cmp8 environment does not have an I/O subsystem.

The fc1 environment consists of:

- A full OpenSPARC T2 chip with one SPARC Core

- Cache

- Memory

- Crossbar

- I/O subsystem

The fc8 environment consists of:

- A full OpenSPARC T2 chip, including all eight cores

- Cache

- Memory

- Crossbar

- I/O subsystem

Each environment can perform either a mini-regression or a full regression.

To run a regression, use the sims command as described in To Run a Regression. The important parameters for the sims command are:

■ -sys: system type

Set this to cmp1 or cmp8 or fc1 or fc8. For example: -sys=cmp1

■ -group: Regression group name

The choices for -group are: cmp1\_mini\_T2, cmp1\_all\_T2, cmp8\_mini\_T2, cmp8\_all\_T2, fc1\_mini\_T2, and fc1\_all\_T2, fc8\_mini\_T2, and fc8\_all\_T2. For example: -group=cmp1\_mini\_T2

■ For help, type "sims -h"

### **▼** To Run a Regression

1. Create the \$MODEL\_DIR directory.

% mkdir \$MODEL\_DIR

2. Change directory to \$MODEL\_DIR.

#### % cd \$MODEL DIR

This is where the simulations are run.

3. Run a mini-regression for the cmp1 environment using the VCS simulator.

```

% sims -sys=cmp1 -group=cmp1_mini_T2

```

This command creates two directories:

- A directory called cmp1 under \$MODEL\_DIR. The regression compiles Vera and Verilog code under the cmp1 directory. This is the Vera and Verilog "build" directory.

- A directory named with today's date and a serial number, such as 2007\_01\_07\_0 (the format is YYYY\_MM\_DD\_ID) under the current directory where simulations will run. This is the Verilog simulation's "run" directory. There is one subdirectory under this directory for each diagnostics test.

By default, the simulations are run with Vera.

4. Once simulations are completed, run the regreport command to generate a regression report.

```

% cd run-directory

% regreport $PWD > report.log

```

Where *run-directory* is the "run" directory created in the above step, such as 2007\_08\_07\_0.

The cmp1\_mini\_T2 regression has 51 tests. An example of its report.log output is shown below:

| Group             | Total | PASS | FAIL | Cycles     | Time     | C/S   |

|-------------------|-------|------|------|------------|----------|-------|

| cmp1_st:          | 2     | 2    | 0    | 127399.00  | 2405.28  | 52.97 |

| cmp1_nospec:      | 5     | 5    | 0    | 349747.50  | 8391.28  | 41.68 |

| cmp1_mt:          | 15    | 15   | 0    | 684702.50  | 20884.47 | 32.79 |

| cmp1_mmu:         | 9     | 9    | 0    | 245845.50  | 7335.27  | 33.52 |

| cmp1_lsu:         | 5     | 5    | 0    | 190447.50  | 5876.04  | 32.41 |

| cmp1_fast_idtl b: | 4     | 4    | 0    | 102978.00  | 2579.26  | 39.93 |

| cmp1_fast_fgu:    | 5     | 5    | 0    | 109217.50  | 2205.12  | 49.53 |

| cmp1_fast_exu:    | 6     | 6    | 0    | 140307.00  | 3639.62  | 38.55 |

| ALL:              | 51    | 51   | 0    | 1950644.50 | 53316.34 | 36.59 |

If your report.log file displays a similar status, you have successfully completed running a mini-regression for the OpenSPARC T2 processor.

### **▼** Run Your First Synthesis

The command to run a synthesis is rsyn. For example, to run a synthesis for one of the modules called efu, type:

% rsyn efu

This command runs a synthesis for the efc block and creates gate level netlists under the \$DV\_ROOT/design/sys/iop/efu/synopsys/gate directory.

The synthesis flow and scripts are described in more detail in Chapter 4.

# OpenSPARC T2 Design Implementation

This chapter gives details on the following topics:

- OpenSPARC T2 Design

- OpenSPARC T2 Components

- Module Directory Structure

- Megacells

## 2.1 OpenSPARC T2 Design

OpenSPARC T2 is a single chip multi-threaded (CMT) processor. OpenSPARC T2 contains eight SPARC physical processor cores. Each SPARC physical processor core has full hardware support for eight strands, two integer execution pipelines, one floating-point execution pipeline, and one memory pipeline. The floating-point and memory pipelines are shared by all eight strands. The eight strands are hardpartitioned into two groups of four, and the four strands within a group share a single integer pipeline. While all eight strands run simultaneously, at any given time at most two strands will be active in the physical core, and those two strands will be issuing either a pair of integer pipeline operations, an integer operation and a floating-point operation, an integer operation and a memory operation, or a floatingpoint operation and a memory operation. Strands are switched on a cycle-by-cycle basis between the available strands within the hard-partitioned group of four using a least recently issued priority scheme. When a strand encounters a long-latency event, such as a cache miss, it is marked unavailable and instructions will not be issued from that strand until the long-latency event is resolved. Execution of the remaining available strands will continue while the long-latency event of the first strand is resolved.

Each SPARC physical core has a 16 KB, 8-way associative instruction cache (32-byte lines), 8 Kbytes, 4-way associative data cache (16-byte lines), 64-entry fully-associative instruction TLB, and 128-entry fully associative data TLB that are shared by the eight strands. The eight SPARC physical cores are connected through a crossbar to an on-chip unified 4 Mbyte, 16-way associative L2 cache (64-byte lines). The L2 cache is banked eight ways to provide sufficient bandwidth for the eight SPARC physical cores. The L2 cache connects to four on-chip DRAM controllers, which directly interface to a pair of fully buffered DIMM (FBD) channels. In addition, an on-chip PCI-EX controller, two 1-Gbit/10-Gbit Ethernet MACs, and several on-chip I/O-mapped control registers are accessible to the SPARC physical cores. Traffic from the PCI-EX port coherently interacts with the L2 cache.

**Note** – OpenSPARC T2 currently does not include PCI-Express design implementation due to current legal restrictions. Equivalent model may be available in the subsequent releases of OpenSPARC T2.

A block diagram of the OpenSPARC T2 chip is shown in FIGURE 2-1

# 2.2 OpenSPARC T2 Components

This section describes each component in OpenSPARC T2.

### 2.2.1 SPARC Physical Core

Each SPARC physical core has hardware support for eight strands. This support consists of a full register file (with eight register windows) per strand, with most of the ASI, ASR, and privileged registers replicated per strand. The eight strands share the instruction and data caches and TLBs. An auto-demap feature is included with the TLBs to allow the multiple strands to update the TLB without locking.

There is a single floating-point unit within each SPARC physical core for a total of 8 on a T2 chip. Each floating-point unit is shared by all eight strands and fully pipelined. The theoretical floating-point bandwidth is 11 Giga Floating Point Ops (GFlops) per second making the T2 an excellent floating-point processor.

Detailed information on the core processor is provided in *OpenSPARC T2 Core Microarchitecture Specification*.

### 2.2.2 SPARC System-On Chip (SoC)

Each SPARC physical core is supported by system on chip hardware components.

Information on each of the functioning units of the system on chip of OpenSPARC T2 are provided in the following chapters of *OpenSPARC T2 System-On Chip (SoC) Microarchitecture Specification*.

# 2.3 Module Directory Structure

The Verilog RTL for the OpenSPARC T2 processor is in the \$DV\_ROOT/design/sys/iop/cpu directory. The top level verilog module for the OpenSPARC T2 processor is called "cpu". All the top-level modules that make up that RTL, and their locations, are listed in TABLE 2-1..

TABLE 2-1

OpenSPARC T2 Top-Level Clusters

| Module Name | Туре    | Number of<br>Instances | Instance Names | Directory<br>Location<br>under<br>\$DV_ROOT/d<br>esign/sys/<br>iop | Description             |

|-------------|---------|------------------------|----------------|--------------------------------------------------------------------|-------------------------|

| ccu         | cluster | 1                      | ccu            | ccu                                                                | Clock Control Unit      |

| CCX         | Cluster | 1                      | ccx            | CCX                                                                | CPU-Cache Cross<br>bar  |

| db0         | Cluster | 1                      | db0            | db0                                                                | Debug Unit              |

| db1         | Cluster | 1                      | db1            | db1                                                                | Debug Unit              |

| dmu         | cluster | 1                      | dmu            | dmu                                                                | Data Management<br>Unit |

| efu         | Cluster | 1                      | efu            | efu                                                                | e-Fuse Cluster          |

| fsr         | cluster | 1                      | fsr            | fsr                                                                | FBDIMM Serdes macro     |

| fsr_bottom  | cluster | 1                      | fsr_bottom     | fsr_bott<br>om                                                     | FBDIMM Serdes<br>Macro  |

| fsr_left    | cluster | 1                      | fsr_left       | fsr_left                                                           | FBDIMM Serdes<br>Macro  |

| fsr_right   | cluster | 1                      | fsr_right      | fsr_righ<br>t                                                      | FBDIMM Serdes<br>Macro  |

| 12b         | Cluster | 8                      | l2b[0-7]       | 12b                                                                | L2\$ bank               |

| 12t         | Cluster | 8                      | 12t[0-7]       | 12t                                                                | L2 \$ tag               |

| 12d         | Cluster | 8                      | 12d[0-7]       | 12d                                                                | L2 \$ data              |

| mcu         | cluster | 4                      | mcu[0-3]       | mcu                                                                | Memory<br>Controller    |

| mio         | cluster | 1                      | mio            | mio                                                                | Miscellaneous I/O       |

| ncu         | cluster | 1                      | ncu            | ncu                                                                | Non-cacheable<br>Unit   |

TABLE 2-1

OpenSPARC T2 Top-Level Clusters (Continued)

| Module Name | Туре    | Number of<br>Instances | Instance Names | Directory<br>Location<br>under<br>\$DV_ROOT/d<br>esign/sys/<br>iop | Description                         |

|-------------|---------|------------------------|----------------|--------------------------------------------------------------------|-------------------------------------|

| rst         | cluster | 1                      | rst            | rst                                                                | Reset Unit                          |

| sii         | cluster | 1                      | sii            | sii                                                                | System Interface<br>Unit - Inbound  |

| sio         | cluster | 1                      | sio            | sio                                                                | System Interface<br>Unit - Outbound |

| spc         | Cluster | 8                      | spc[0-7]       | spc                                                                | SPARC CPU core                      |

| tcu         | cluster | 1                      | tcu            | tcu                                                                | Trap Control Unit                   |

| esr         | cluster | 1                      | esr            | esr                                                                | Ethernet SerDes model               |

| mac         | cluster | 1                      | mac            | mac                                                                | Ethernet MAC                        |

| tds         | cluster | 1                      | tds            | tds                                                                | Ethernet Transmit<br>Data Path      |

| rdp         | cluster | 1                      | rdp            | rdp                                                                | Ethernet Receive<br>Data Path       |

| rtx         | cluster | 1                      | rtx            | rtx                                                                | Ethernet Receive and Transmit       |

# 2.4 Megacells

The OpenSPARC T2 design contains many megacells, which are custom blocks for static random access memory (SRAMs), translation lookaside buffer (TLB), TAGs, Level 2 Cache, and so on. These megacells are instantiated in the top-level clusters. The detailed descriptions of all megacells, including their function descriptions, I/O lists, block diagrams, and timing diagrams, are in the *OpenSPARC T2 Megacell Specification*.

### OpenSPARC T2 Verification Environment

This chapter describes the following topics:

- OpenSPARC T2 Verification Environment

- Running a Regression

- PLI Code Used For the Test Bench

- Verification Test File Locations

# 3.1 OpenSPARC T2 Verification Environment

The OpenSPARC T2 verification environment is a highly automated environment. With a simple command, you can run the entire regression suite for the OpenSPARC T2 processor, containing hundreds of tests. With a second command, you can check the results of the regression.

The OpenSPARC T2 Design and Verification package comes with four test bench environments: cmp1, cmp8, fc1 and fc8.

The cmp1 environment consists of:

- One SPARC CPU core

- Cache

- Memory

- Crossbar

The cmp1 environment does not have an I/O subsystem.

The cmp8 environment consists of:

- Eight SPARC CPU cores

- Cache

- Memory

- Crossbar

The cmp8 environment does not have an I/O subsystem.

The fc1 environment consists of:

- A full OpenSPARC T2 chip, with one SPARC Core

- Cache

- Memory

- Crossbar

- I/O subsystem

The fc8 environment consists of:

- A full OpenSPARC T2 chip, including all eight cores

- Cache

- Memory

- Crossbar

- I/O subsystem

The verification environment uses source code in various languages. TABLE 3-1 shows a summary of the types of source code and their uses.

TABLE 3-1

Source Code Types in the Verification Environment

| Source Code Language | Used for:                                                                    |  |

|----------------------|------------------------------------------------------------------------------|--|

| Verilog              | Chip design, test bench drivers, and monitors.                               |  |

| Vera                 | Test bench drivers, monitors, and coverage objects. Use of Vera is optional. |  |

| PERL                 | Scripts for running simulations and regressions.                             |  |

| C and C++            | PLI (Programming Language Interface) for Verilog.                            |  |

| SPARC Assembly       | Verification tests.                                                          |  |

# 3.2 Running a Regression

For each environment, there is a mini-regression and a full regression. TABLE 3-2 describes the regression groups.

**TABLE 3-2** Details of Regression Groups

| Regression Group name | Environment | No. of Tests |

|-----------------------|-------------|--------------|

| cmp1_mini_T2          | cmp1        | 6            |

| cmp1_all_T2           | cmp1        | 768          |

| cmp8_mini_T2          | cmp8        | 7            |

| cmp8_all_T2           | cmp8        | 648          |

| fc1_mini_T2           | fc1         | 6            |

| fc1_full_T2           | fc1         | 353          |

| fc8_mini_T2           | fc8         | 17           |

| fc8_full_T2           | fc8         | 535          |

### ▼ To Run a Regression

1. Run the sims command with your chosen parameters.

For instance, to run a mini-regression for the cmp1 environment using the VCS simulator, set up the sims command as follows:

% sims -sys=cmp1 -group=cmp1\_mini\_T2

To run regressions on multiple groups at the same time, specify multiple – group= parameters at the same time. For a complete list of command-line options for the sims command, see Appendix A.

2. Run the regreport command to get a summary of the regression.

% regreport \$PWD/2007\_08\_07\_0 > report.log

### 3.2.1 What the sims Command Does

When running a simulation, the sims command performs the following steps:

- 1. Compiles the design into the \$MODEL\_DIR/cmp1 or \$MODEL\_DIR/fc8 directory, depending on which environment is being used.

- 2. Creates a directory for regression called \$PWD/DATE\_ID, where \$PWD is your current directory, DATE is in YYYY\_MM\_DD format, and ID is a serial number starting with 0. For example, for the first regression on August07, 2007, a directory called \$PWD/2007\_08\_07\_0 is created. For the second regression run on the same day, the last ID is incremented to become \$PWD/2007\_08\_07\_1.

- 3. Creates a master\_diaglist.regression\_group file under the above directory. such as master\_diaglist.cmp1\_mini\_T2 for the cmp1\_mini\_T2 regression group. This file is created based on diaglists under the \$DV\_ROOT/verif/diag directory.

- 4. Creates a subdirectory with the test name under the regression directory created in step 2 above.

- 5. Creates a sim\_command file for the test based on the parameters in the diaglist file for the group.

- 6. Executes sim\_command to run a Verilog simulation for the test. If the -sas option is specified for the test, it also runs the SPARC Architecture Simulator (SAS) in parallel with the Verilog simulator. The results of the Verilog simulation are compared with the SAS results after each instruction.

The sim\_command command creates many files in the test directory. Following are the sample files in the test directory:

```

diag.ev diag.s raw_coverage seeds.log

status.log vcs.log.gz diag.exe.gz midas.log

sas.log.gz sims.log symbol.tbl vcs.perf.log

```

The status.log file has a summary of the status, where the first line contains the name of the test and its status (PASS/FAIL).

```

Rundir: tlu_rand05_ind_03:cmp1_st:cmp1_mini_T2:0 PASS

```

7. Repeats steps 4 to 6 for each test in the regression group.

### 3.3 PLI Code Used For the Test Bench

Verilog's PLI (Programming Language Interface) is used to drive and monitor the simulations of the OpenSPARC T2 design. There are eight different directories for PLI source code. Some PLI code is in C language, and some is in C++ language. TABLE 3-3 gives the details of PLI code directories and VCS libraries.

**TABLE 3-3** PLI Source Code and Object Libraries

| PLI name        | Source code location under \$DV_ROOT    | VCS object library name | Description            |

|-----------------|-----------------------------------------|-------------------------|------------------------|

| iob             | verif/env/common/pli/cac<br>he          | libiob.a                | Cache warming routines |

| mem             | model/infineon                          | libbwmem_pli.a          | Memory<br>read/write   |

| socket          | <pre>verif/env/common/pli/soc ket</pre> | libsocket_pli.a         | Sockets to SAS         |

| utility         | verif/env/common/pli/uti<br>lity        | libbwutility_pli.a      | Utility functions      |

| monitor         | verif/env/common/pli/<br>monitor/c      | libmonitor_pli.a        | Various                |

| global_chk<br>r | verif/env/common/pli/glo<br>bal_chkr/   | libglobal_chkr.a        | Various checkers       |

VCS object libraries are statically linked libraries (.a files) which are linked when VCS compiles the Verilog code to generate a simv executable.

Makefile is provided to compile PLI code. There is a makefile file under \$DV\_ROOT/tools/pli directory which will compile static executable (.a file) of the PLI code.

### 3.4 Verification Test File Locations

The verification or diagnostics tests (diags) for the OpenSPARC T2 processor are written in SPARC assembly language (the file names have a .s extension). Some diagnostics test cases in SPARC assembly are automatically generated by Perl scripts.

The main diaglist for cmp1 is cmp1.diaglist. The main diaglist for fc8 is fc8.diaglist. These main diaglists for each environment also include many other diaglists. The locations of various verification test files are listed in TABLE 3-4.

**TABLE 3-4** Verification Test File Directories

| Directory                                 | Contents                                                                        |

|-------------------------------------------|---------------------------------------------------------------------------------|

| \$DV_ROOT/verif/diag                      | All diagnostics, various diagnostic list files with the extension.diaglist.     |

| <pre>\$DV_ROOT/verif/diag/a ssembly</pre> | Source code for SPARC assembly diagnostics. More than 1400 assembly test files. |

| <pre>\$DV_ROOT/verif/diag/e fuse</pre>    | EFuse cluster default memory load files.                                        |

# OpenSPARC T2 Synthesis

This chapter describes the following topics:

- Synthesis Flow for the OpenSPARC T2 Processor

- Synthesis Output

The scripts provided in the source code are for the Synopsys Design Compiler.

# 4.1 Synthesis Flow for the OpenSPARC T2 Processor

There are two types of synthesis scripts:

- One set to run the Synopsys Design Compiler (rsyn and syn\_command)

- One set used as input for the Design Compiler

The main script used to run Synopsys Design Compiler is called rsyn. This is a PERL script that calls a second script, syn\_command, once for each module you are synthesizing. The command-line options for the rsyn script are described in CODE EXAMPLE 4-1.

#### **CODE EXAMPLE 4-1** Command-Line Options for rsyn Script

```

rsyn : Run Synthesis for OpenSPARC T2

-all

to run synthesis for all blocks

-h / -help

to print help

-syn_q_command='Your job Queue command'

to specify Job queue command. e.g. specify submit command

for LSF or GRID

block_list :

specify list of blocks to synthesize

Examples:

rsyn -all

rsyn efu

```

Synthesis scripts for most of the modules are provided in the \$DV\_ROOT/design sub-directories. There are no synthesis scripts for the following types of modules:

- Megacell modules (SRAMS, TLB, TAG, Cache, etc.)

- Top-level hierarchical modules

Synopsys scripts, their locations, and their descriptions are listed in TABLE 4-1.

TABLE 4-1

Synthesis Script Details

| Script name                      | Location                                        | Description                                   |

|----------------------------------|-------------------------------------------------|-----------------------------------------------|

| run.scr                          | \$DV_ROOT/design/sys/synopsys/script            | Main synthesis script that calls user_cfg.scr |

| <pre>project_sparc_cfg.scr</pre> | <pre>\$DV_ROOT/design/sys/synopsys/script</pre> | SPARC module-specific synthesis script        |

| project_io_cfg.scr               | <pre>\$DV_ROOT/design/sys/synopsys/script</pre> | I/O module-specific synthesis script          |

| target_lib.scr                   | <pre>\$DV_ROOT/design/sys/synopsys/script</pre> | Target library-specific script                |

| user_cfg.scr                     | Module directory/synopsys/script                | Module-specific synthesis script              |

The top-level Synopsys script, run.scr, calls the module-specific script named user\_cfg.scr. The user\_cfg.scr script calls the project\_sparc\_cfg.scr script or the project\_io\_cfg.scr script, depending on whether the module belongs to sparc or io.

The list of all modules with synthesis scripts is in the \$DV\_ROOT/design/sys/synopsys/block.list file. Each module has:

- A synopsys directory under the module directory

- A script directory under each synopsys directory

- The user\_cfg.scr file under the script directory

For example, the efc module-specific synthesis script has the following directory path:

\$DV\_ROOT/design/sys/iop/efu/synopsys/script/user\_cfg.scr

The target library is set to a generic library called <code>lsi\_10k.db</code> in the <code>target\_lib.scr</code> script. Modify this file to set your own target library and its required variables.

### 4.2 Synthesis Output

Running synthesis for a module creates files and directories under the *Module name*/synopsys directory, described in TABLE 4-2.

**TABLE 4-2** Synthesis Output

| Name         | Туре      | Description                                |

|--------------|-----------|--------------------------------------------|

| dc_shell.log | File      | Log file from running Design Compiler      |

| command.log  | File      | Command log from running Design Compiler   |

| log          | Directory | Area report files from Design Compiler     |

| gate         | Directory | Gate netlist generated by Design Compiler  |

| .template    | Directory | Template directory used by Design Compiler |

# Design and Verification Manual Pages

This appendix provides the manual pages for commands used for OpenSPARC T2 design and verification.

# A.1 sims

NAME

sims - Verilog rtl simulation environment and regression script

#### SYNOPSIS

sims [args ...]

**Note** – Use "=" instead of "space" to separate args and their options.

where args are:

#### SIMULATION ENV

#### -sys=NAME

sys is a pointer to a specific testbench configuration to be built and run. a config file is used to associate the sys with a set of default options to build the testbench and run diagnostics on it. the arguments in the config file are the same as the arguments passed on the command line.

# -group=NAME

group name identifies a set of diags to run in a regression. The presence of this argument indicates that this is a regession run. the group must be found in the diaglist. multiple groups may be specified to be run within the same regression.

**Note** – If -sys=NAME option is specified then NAME.diaglist is used as root diaglist instead of the master diaglist.

# -group=NAME -alias=ALIAS

this combination of options gets the diag run time options from the diaglist based on the given group and alias. the group must be found in the diaglist. the alias is made up of diag\_alias:name\_tag. only one group should be specified when using this command format.

#### VERILOG COMPILATION RELATED

-sim\_q\_command="command"

defines which job queue manager command to use to launch jobs. Defaults to /bin/sh and runs simulation jobs on the local machine.

-vcs\_build/-novcs\_build

builds a vcs model and the vera testbench. defaults to off.

-vcs\_build\_args=OPTION

vcs compile options. multiple options can be specified using multiple such arguments.

-vcs\_clean/-novcs\_clean

wipes out the model directory and rebuilds it from scratch. defaults to off.

-vcs\_full64

sets the vcs -full64 compile flag so that the compiler is a 64 bit executable, and produces a 64 bit executable simv. will use the 64 bit version of vera, and link in the 64 bit versions of 0in, debussy, and denali tools.

-vcs\_use\_2state/-novcs\_use\_2state

builds a 2state model instead of the default 4state model. this defaults to off.

-vcs\_use\_initreg/-novcs\_use\_initreg

initialize all registers to a valid state (1/0).

this feature works with -tg\_seed to set the seed of the random initialization. this defaults to off.

# -vcs\_use\_fsdb/-novcs\_use\_fsdb

use the debussy fsdb pli and include the dump calls in the testbench. this defaults to on.

#### -vcs use vcsd/-novcs use vcsd

use the vcs direct kernel interface to dump out debussy files. this defaults to on.

# -vcs\_use\_vera/-novcs\_use\_vera

compile in the vera libraries. if -vcs\_use\_ntb and -vcs\_use\_vera are used, -vcs\_use\_ntb wins. this defaults to off.

# -vcs\_use\_ntb/-novcs\_use\_ntb

enable the use of NTB when building model (simv) and running simv. if -vcs\_use\_ntb and -vcs\_use\_vera are used, -vcs\_use\_ntb wins. this defaults to off.

# -vcs\_use\_rad/-novcs\_use\_rad

use the +rad option when building a vcs model (simv). defaults to off.

#### -vcs use sdf/-novcs use sdf

build vcs model (simv) with an sdf file. defaults to off.

# -vcs\_use\_radincr/-novcs\_use\_radincr

use incremental +rad when building a vcs model (simv). defaults to off.

this is now permanently disabled as synopsys advises against using it.

# -vcs\_use\_cli/-novcs\_use\_cli

use the +cli -line options when building a vcs model (simv). defaults to off.

use this switch, in conjunction with -nosimslog during runtime if you need to pass ctrl-c to the vcs/axis model and continue with CLI activity.

# Use this with VCS versions before 2006.

# -vcs\_use\_ucli/-novcs\_use\_ucli (Unified cli)

use the  $-\text{debug\_all}$  option when building a vcs model (simv). defaults to off.

use this switch, in conjunction with -nosimslog during runtime if you need to pass ctrl-c to the vcs/axis model and continue with UCLI activity.

At runtime, use -vcs\_run\_arg=-ucli to get the UCLI at time zero, or use -vcs\_run\_arg=-gui to get the UCLI GUI at time zero. At runtime, use -vcs\_run\_arg=-tbug to get NTB debug in the GUI.

# Use this with VCS versions 2006 and up.

#### -flist=FLIST

full path to flist to be appended together to generate the final verilog flist. multiple such arguments may be used and each flist will be concatenated into the final verilog flist used to build the model.

# -graft\_flist=GRAFTFILE

GRAFTFILE is the full path to a file that lists each verilog file that will be grafted into the design. the full path to the verilog files must also be given in the GRAFTFILE.

#### -vfile=FILE

verilog file to be included into the flist

# -config\_rtl=DEFINE

each such parameter is place as a `define in config.v to configure the model being built properly. this allows each testbench to select only the rtl code that it needs from the top level rtl file (ciop.v in blackwidow).

# -model=NAME

A-4

the name of a model to be built. the full path to a model is MODEL\_DIR/model/vcs\_rel\_name.

# -vcs\_rel\_name=NAME

specify the release of the model to be built. the full path to a model is MODEL\_DIR/model/vcs\_rel\_name.

# VERA/NTB COMPILATION RELATED

VERA and NTB share all of the vera options except a few. See NTB RELATED.

# -vera build/-novera build

builds the vera/ntb testbench. default on.

# -vera\_clean/-novera\_clean

performs a gmake clean on the vera/ntb testbench before building the model. defaults to off.

# -vera\_build\_args=OPTION

vera/NTB testbench compile time options.

Multiple options can be specified using multiple such options. these are passed as arguments to the gmake call when building the vera/NTB testbench.

(Eq: -vera build args=VERA SYS DEFS="-DSPC BENCH -DGATESIM")

For NTB, -vera\_build\_args=NTB\_BUILD\_ARGS="+error+10 -ntb\_define ABCD" can be used to add something directly to the "vcs -ntb\_cmp" command. For the -ntb\_lib option, NTB\_BUILD\_ARGS will affect both the vshell and bench+diag builds. See -vera\_diag\_args to not affect the vshell build.

# -vera\_diag\_args=OPTION

For NTB, these args are passed as arguments to the gmake call as NTB\_DIAG\_ARGS=" ... " to be part of the NTB bench+diag compile. These NTB\_DIAG\_ARGS are appended to the "vcs -ntb\_cmp" command when making the libtb.so so they better be legal in that context. For NTB, these args really affect the entire bench build, not just the diag, BUT they they do not affect the vshell build. (Eg. -vera\_diag\_args=+error+10 or

-vera\_diag\_args="-ntb\_define NCU\_ACK\_DLY1=100")

# -vera\_dummy\_diag=PATH

This option is used to give vera/NTB a path to a default diag or diag class (or a default program top if using RVM) that can be used for building purposes before an actual diag is chosen (NTB build of vshell file before regression for example).

Also, some benches may run both asm and vera diags but the vera diags are only run sometimes. In this case, you need a dummy vera testcase class/program top to fill in when an actual vera diag is not being used for that run (aka the sometimes diag problem). If your openVera code refers to a testcase class, you better have one even if it does nothing else you will not be able to build. The dummy lets you build. If your diag is implemented as the program top (RVM) then the dummy must have #includes for ALL of your vera interfaces or your vshell will be broken.

Whenever the actual vera/NTB diag is specified, the dummy is automatically \*not\* used (at regression time for example). The vera\_dummy\_diag should be specified in the bench config file. This option applies to Vera and NTB (but NTB only when using the -ntb\_lib option).

# -vera\_pal\_diag\_args=OPTION

vera/ntb pal diag expansion options

(i.e. "pal OPTIONS -o diag.vr diag.vrpal")

multiple options can be specified using multiple such arguments.

# -vera\_proj\_args=OPTION

vera proj file generation options. multiple options can be specified using multiple such arguments.

# -vera vcon file=ARG

name of the vera vcon file that is used when running the simulation.

# -vera\_cov\_obj=OBJ

this argument is passed to the vera Makefile as a OBJ=1 and to vera as -DOBJ to enable a given vera coverage object. multiple such arguments can be specified for multiple coverage objects.

# -vera\_gmake/-novera\_gmake

this argument optionally lets the flow skip running gmake for the vera/NTB build, while maintaining other operations within the -vera\_build flow. default ON (execute gmake)

# NTB RELATED

NTB and VERA share all of the vera options except these:

# -vcs\_use\_ntb/-novcs\_use\_ntb

enable the use of NTB (compiled vera) rather than the conventional Vera. if -vcs\_use\_ntb and -vcs\_use\_vera are used at once, then -vcs\_use\_ntb wins. defaults to off.

# -ntb\_lib/-nontb\_lib

enables the NTB 2 part compile where the openVera files get compiled separately into a libtb.so file which is dynamically loaded by vcs at runtime. The libtb.so file is built by the Vera/NTB Makefile, not sims. Use the Makefile to affect the build. If not using -ntb\_lib, sims will build VCS and the openVera files together in one pass (uses Makefile to affect that build as well). default is off.

The ntb\_lib method is know as the NTB LIB method. When not

using this ntb\_lib method, the ALL IN ONE method is used.

The NTB LIB method allows the bench to run unique openVera diags that are separate from the bench (via a diaglist if desired).

The NTB ALL IN ONE method does not allow the bench to run unique openVera diags that are separate from the bench. Use this for benches that do not run openVera diags (perhaps the bench only runs asm diags

# VERILOG RUNTIME RELATED

# -vera\_run/-novera\_run

runs the vcs simulation and loads in the vera proj file or the ntb libtb.so file. defaults to on.

# -vcd/-novcd

signals the bench to dump in VCD format

# -vcdfile=filename

the name of the vcd dump file. if the file name starts with a "/", that is the file dumped to, otherwise, the actual file is created under tmp\_dir/vcdfile and copied back to the current directory when the simulation ends. use "-vcdfile=`pwd`/filename" to force the file to be written in the current directory directly (not efficient since dumping is done over network instead of to a local disk).

#### -vcs run/-novcs run

runs the vcs simulation (simv). defaults to off.

# -vcs\_run\_args=OPTION

vcs (simv) runtime options. multiple options can be specified using multiple such arguments.

The order of vcs\_run\_args (plusargs) given to simv is:

args embedded in diag (using !SIMS+ARGS: ..), if any

args given in the command line, if any

args from diaglist : alias definition, if any

args from diaglist : <runargs>..</runargs>, if any

args from the config file, if any

# -vcs\_finish=TIMESTAMP

forces vcs to finish and exit at the specified timestamp.

#### -fast\_boot/-nofast\_boot

speeds up booting when using the ciop model. this passes the +fast\_boot switch to the simv run and the -sas\_run\_args=-DFAST\_BOOT and -midas\_args=-DFAST\_BOOT to sas and midas. Also sends

-DFAST\_BOOT to the diaglist and config file preprocessors.

# -debussy/-nodebussy

enable debussy dump. this must be implemented in the testbench to work properly. defaults to off.

# -start\_dump=START

start dumping out a waveform after START number of units

# -stop\_dump=STOP

stop dumping out a waveform after STOP number of units

#### -fsdb2vcd

runs fsdb2vcd after the simulation has completed to generate a vcd file.

#### -fsdbfile=filename

the name of the debussy dump file.

If the file name starts with a "/", that is the file dumped to, otherwise, the actual file is created under tmp\_dir/fsdbfile and copied back to the current directory when the simulation ends. Use "-fsdbfile='pwd'/filename" to force the file to be written in the current directory directly (not efficient since dumping is done over network instead of to a local disk).

# -fsdbDumplimit=SIZE\_IN\_MB

max size of Debussy dump file. minimum value is 32MB.

Latest values of signal values making up that size is saved.

#### -fsdb glitch

turn on glitch and sequence dumping in fsdb file. this will collect glitches and sequence of events within time in the fsdb waveform. beware that this will cause the fsdb file size to grow significantly. this is turned off by default. this option effectively does this: setenv FSDB\_ENV\_DUMP\_SEQ\_NUM 1 setenv FSDB\_ENV\_MAX\_GLITCH\_NUM 0

# -rerun

rerun the simulation from an existing regression run directory.

# -overwrite

overwrite current run dir when doing a -rerun. default is to create a rerun\_<n> subdir for reruns.

# -post\_process\_cmd=COMMAND

post processing command to be run after vcs (simv) run completes

# -pre\_process\_cmd=COMMAND

pre processing command to be run before vcs (simv) run starts

# -use\_denalirc=FILE

use FILE as the .denalirc in the run area. Default copies env base/.denalirc

#### SUNV OPTIONS

-sunv\_run/-nosunv\_run

runs the sunv program to convert structural files, e.g. <file>.sv to verilog. defaults to off.

-sunv\_args=ARGS

sunv options. Multiple options can be specified using multiple such arguments. In addition, a portion of these arguments can be provided in a file using the sunv option -optfile=<file>.

-sunv\_use\_nonprim/-nosunv\_use\_nonprim

use a list to hold primitives that we want to remove from the default primitive.list. defaults to off.

-sunv\_nonprim\_list=FILE

name of file holding the list of primitives that we want to remove. this is only used if -sunv\_use\_nonprim is specified.

#### VLINT OPTIONS

-vlint run/-novlint run

runs the vlint program. defaults to off.

-vlint\_args

vlint options. The <sysName>.config file can contain the desired vlint arguments, or they can also be given on the command line. Typically the -vlint\_compile is given on the command line.

vlint also requires identification of a rules deck.

-illust run

run illust after x2e

-illust\_args

illust options

-vlint\_top

top level module on which to run vlint

# VERIX OPTIONS

-verix\_run/-noverix\_run

runs the verix program. defaults to off.

# -verix libs

specify the library files to add to the vlist

# -verix\_args

verix template options. The <sysName>.config file can contain these desired verix arguments

verix also requires <top>.verix.tmplt in the config dir.

# -verix\_top

top level module on which to run verix

#### THARAS HAMMER RELATED

# -hcs build

build a model to be run on the Hammer Hardware Accelerator.

# -hcs\_build\_args

build arguments for Hammer Hardware Accelerator

# -hcs\_run

run a model on the Hammer Hardware Accelerator.

# -hcs\_run\_args

run arguments for the Hammer Hardware Accelerator.

# -hcs\_drm\_tokens

tokens for drmsubmit licenses

# AXIS RELATED

#### -axis build

build a model to be run on the Axis Hardware Accelerator.

# -axis\_build\_args

build arguments for Axis Hardware Accelerator

# -axis run

run a model on the Axis Hardware Accelerator.

# -axis\_run\_args

run arguments for the Axis Hardware Accelerator.

# PALLADIUM RELATED

-palladium\_build

build a model to be run on the palladium Hardware Accelerator.

# -palladium\_build\_args

build arguments for palladium Hardware Accelerator

# -palladium run

run a model on the palladium Hardware Accelerator.

# -palladium\_run\_args

run arguments for the palladium Hardware Accelerator.

# ZEROIN RELATED

# -zeroIn checklist

run 0in checklist

# -zeroIn\_build

build OIn pli for simulation into vcs model

# -zeroInSearch\_build

build Oin search pli for simulation into vcs model

# -zeroIn\_build\_args

additional arguments to be passed to the 0in command

# -zeroIn\_dbg\_args

additional debug arguments to be passed to the 0in shell

# SAS/SIMICS RELATED

#### -sas/-nosas

run architecture-simulator. If vcs\_run option is OFF, simulation is sas-only. If vcs\_run option is ON, sas runs in lock-step with rtl. default to off.

#### -sas\_run\_args=DARGS

Define arguments for sas.

# TCL/TAP RELATED

# -tcl\_tap/-notcl\_tap

run tcl/expect TAP program. If vcs\_run option is OFF, simulation is tcl-only. If vcs\_run option is ON, tcl runs in lock-step with rtl. default to off.

**Note** — You \_must\_ compile with -tcl\_tap as well, to enable to enable functions that are needed for running with tcl

#### MIDAS RELATED

midas is the diag assembler

-midas\_args=DARGS

arguments for midas. midas creates memory image and user-event files from the assembly diag.

-midas\_only

Compile the diag using midas and exit without running it.

-midas\_use\_tgseed

Add -DTG\_SEED=tg\_seed to midas command line. Use -tg\_seed to set the value passed to midas or use a random value from /dev/random.

#### PCI

pci is the tomatillo pci bus functional model

-pci\_args

arguments to be passed in to pci\_cmdgen.pl for generation of a pci random diagnostic.

-pci/-nopci

generates a random pci diagnostic using the -tg\_seed if provided. default is off.

-tomatillo

generates a random tomatillo diagnostic using the -tg\_seed if provided

-tg\_seed

random generator seed for pci/tomatillo random test generators also the value passed to +initreg+ to randomly initialize registers when -vcs\_use\_initreg is used.

#### SJM RELATED

sjm is the jalapeno jbus bus functional model

-sjm\_args

arguments to be passed in to sjm\_tstgen.pl for generation of an sjm

random diagnostic.

# -sim/-nosim

generates a random sjm diagnostic using the -tg\_seed if provided. default is off.

#### -tomatillo

generates a random tomatillo diagnostic using the -tg\_seed if provided

# -tg\_seed

random generator seed for sjm/tomatillo random test generators also the value passed to +initreg+ to randomly initialize registers when -vcs\_use\_initreg is used.

#### **EFCGEN**

efcgen.pl is a script to generate efuse.img files (default random), which is used by the efuse controller after reset. It is invoked by -efc.

# -efc/-noefc

generates an efuse image file using the -tg\_seed if provided. default is off. Random if no -efc\_args specified.

#### -efc args

$% \left( 1\right) =\left( 1\right) +\left( 1\right) +\left($

Default is random efuse replacement for each block.

# -tg\_seed

random generator seed for efcgen.pl script

also the value passed to +initreg+ to randomly initialize

registers when -vcs\_use\_initreg is used.

# VCS COVERMETER

# -vcs\_use\_cm/-novcs\_use\_cmd

passes in the -cm switch to vcs at build time and simv at runtime default to off.

# -vcs\_cm\_args=ARGS

argument to be given to the -cm switch

# -vcs\_cm\_cond=ARGS

argument to be given to the -cm\_cond switch.

# -vcs\_cm\_config=ARGS

argument to be given to the -cm\_hier switch

# -vcs\_cm\_fsmcfg=ARGS

argument to be given to the -cm\_fsmcfg switch specifies an FSM coverage configuration file

#### -vcs cm name=ARGS

argument to be given to the -cm name switch. defaults to cm data.

#### DFT

#### -dft.vert.

modifies the sims flow to accommodate dftvert. this skips compiling the vera testbench and modifies the simv command line at runtime.

#### CDMS

# -cdms\_rel\_name=CDMSREL

specify the  $\operatorname{cdms}++$  release that must be collected for this model.

# -diff\_cdms\_rel

performs a diff\_release of CDMSREL from -cdms\_rel\_name and records it in a file called diff\_rel.log lcoated in the model area. This file is copied into each run directory from the model area at runtime.

# -diff\_cdms\_curr

uses the current (in localdir) release of CDMSREL for the diff\_release command. Ignored if -cdms\_rel\_name and -diff\_cdms\_rel are not specified.

# MISC

# -regress

pretend this is a regression and run the job in DRMJOBSCRATCHSPACE instead of the launch directory. useful with -indrm and -interactive options and single jobs. automatically added for regressions.

#### -nobuild

this is a master switch to disable all building options. there is no such thing as -build to enable all build options.

# -copyall/-nocopyall

copy back all files to launch directory after passing regression run. Normally, only failing runs cause a copy back of files.

Default is off.

# -copyall/-nocopyall

copy back all files to launch directory after passing regression run. Normally, only failing runs cause a copy back of files.

Default is off.

# -copydump/-nocopydump

copy back dump file to launch directory after passing regression run. Normally, only failing runs cause a copy back of non-log files. The file copied back is vcs.fsdb, or vcs.vcd if -fsdb2vcd option is set.

Default is off.

# -tarcopy/-notarcopy

copy back files using 'tar'. This only works in copyall or in the case the simulations 'fails' (per sims' determination). Default is to use 'cp'.

# -diag\_pl\_args=ARGS

If the assembly diag has a Perl portion at the end, it is put into diag.pl and is run as a Perl script. This allows you to give arguments to that Perl script. The arguments accumulate, if the option is used multiple times.

# -pal\_use\_tgseed

Send '-seed=<tg\_seed\_value> to pal diags. Adds -pal\_diag\_args=-seed=tg\_seed to midas command line, and -seed=tg\_seed to pal options (vrpal diags). Use -tg\_seed to set the value passed to midas or use a random value from /dev/random.

# -parallel

when specifying multiple groups for regressions this switch will submit each group to DReAM to be executed as a separate regression. this has the effect of speeding up regression submissions.

NOTE: This switch must not be used with -indrm

#### -reg count=COUNT

runs the specified group multiple times in regression mode. this is useful when we want to run the same diag multiple times using a different random generator seed each time or some such.

# -regress\_id=ID

specify the name of the regression

#### -report

This flag is used to produce a report of a an old or running regression. With -group options, sims produces the report after the regression run. Report for the previous

regression run can be produced using -regress\_id=ID option along with this option,

# -finish\_mask=MASK

masks for vcs simulation termination. Simulation terminates when it hits 'good\_trap' or 'bad\_trap'. For multithread simulation, simulation terminates when any of the thread hits bad\_trap, or all the threads specified by the finish\_mask hits the good\_trap.

example: -finish\_mask=0xe

Simulation will be terminated by good\_trap, if thread 1, 2 and 3 hits the good trap.

# -stub\_mask=MASK

mask for vcs simulation termination. Simulation ends when the stub driving the relevant bit in the mask is asserted. This is a hexadecimal value similar to -finish mask

# -wait\_cycle\_to\_kill=VAL

passes a +wait\_cycle\_to\_kill to the simv run. a testbench may chose to implement this plusarg to delay killing a simulation by a number of clock cycles to allow collection of some more data before exiting (e.g. waveform).

# -rtl\_timeout

passes a +TIMEOUT to the simv run.

sets the number of clock cycles after all threads have become inactive for the diag to exit with an error. if all threads hit good trap on their own the diag exits right away. if any of the threads is inactive without hitting good trap/bad trap the rtl\_timeout will be reached and the diag fails. default is 1000. this is only implemented in the cmp based testbenches.

#### -max\_cycle

passes a +max\_cycle to the simv run.

sets the maximum number of clock cycle that the diag will take to complete. the default is 30000. if max\_cycle is hit the diag exits with a failure. not all testbenches implement this feature.

# -norun\_diag\_pl

Does not run diag.pl (if it exists) after simv (vcs) run. Use this option if, for some reason, you want to run anexisting assembly diag without the Perl part that is in the original diag.

#### -nosaslog

turns off redirection of sas stdout to the sas.log file. use this option when doing interactive runs with sas.

# -nosimslog

turns off redirection of stdout and stderr to the sims.log file. use this option in conjunction with -vcs\_use\_cli or -vcs\_use\_ucli to get to the cli prompt when using vcs or to see a truncated vcs.log file that exited with an error. this must be used if you want control-c to work while vcs is running.

# -nogzip

turns off compression of log files before they are copied over during regressions.

#### -version

print version number.

# -help

prints this

#### IT SYSTEM RELATED

# -use\_iver=FILE

full path to iver file for frozen tools

# -use\_sims\_iver/-nouse\_sims\_iver

For reruns of regression tests only, use sims.iver to choose TRE tool versions saved during original regression run. Defaults to true.

# -use\_cdms\_iver/-nouse\_cdms\_iver

Uses the frozen iver file located under DV\_ROOT if present. This defaults to true. This has no effect if an iver file is not found under the cdms tree.

# -dv\_root=PATH

absolute path to design root directory. this overrides DV\_ROOT.

# -model\_dir=PATH

absolute path to model root directory. this overrides MODEL\_DIR.

# -tmp\_dir=PATH

path where temporary files such as debussy dumps will be created

# -sims\_config=FILE

full path to sims config file

# -sims\_env=ENVAR=value

force sims to set ENVAR variable to specified value.

#### -env\_base=PATH

this specifies the root directory for the bench environment. it is typically defined in the bench config file. It has no default.

# -config\_cpp\_args=OPTION

this allows the user to provide CPP arguments (defines/undefines) that will be used when the testbench configuration file is processed through cpp. Multiple options are concatenated together.

# -result dir=PATH

this allows the regression run to be launched from a different directory than the one sims was launced from. defaults to PWD.

# -diaglist=FILE

full path to diaglist file

# -diaglist\_cpp\_args=OPTION

this allows the user to provide CPP arguments (defines/undefines) that will be used when the diaglist file is processed through cpp. Multiple options are concatenated together.

- -asm\_diag\_name=NAME

- -tpt\_diag\_name=NAME

- -tap diag name=NAME

- -vera diag name=NAME

- -vera\_config\_name=NAME

- -efuse image name=NAME

- -image\_diag\_name=NAME

- -sjm\_diag\_name=NAME

- -pci\_diag\_name=NAME

name of the diagnostic to be run.

- -asm\_diag\_root=PATH

- -tpt\_diag\_root=PATH

- -tap\_diag\_root=PATH

- -vera\_diag\_root=PATH

- -vera\_config\_root=PATH

- -efuse\_image\_root=PATH

- -image\_diag\_root=PATH

- -sjm\_diag\_root=PATH

- -pci\_diag\_root=PATH

absolute path to diag root directory. sims will perform a find from here to find the specified type of diag. if more than one instance of the diag name is found under root sims exits with an error. this option can be specified multiple times to allow multiple roots to be searched for the diag.

- -asm\_diag\_path=PATH

- -tpt\_diag\_path=PATH

- -tap\_diag\_path=PATH

- -vera\_diag\_path=PATH

- -vera\_config\_path=PATH

- -efuse\_image\_path=PATH

- -image\_diag\_path=PATH

- -sjm\_diag\_path=PATH

- -pci\_diag\_path=PATH

absolute path to diag directory. sims expects the specified diag to be in this directory. the last value of this option is the one used as the path.

# ClearCase

-clearcase

assume we are in ClearCase environment for setting DV\_ROOT and launching DReAM commands. default is off (CDMS++ version control)

-noclearcase

force clearcase option off

-cc\_dv\_root=PATH

ClearCase path to design root directory. this overrides CC\_DV\_ROOT.

# **ENV VARIABLES**

sims sets the following ENV variables that may be used with pre/post processing scripts, and other internal tools:

**TABLE A-1** Environment Variables

| Environment Variable | Description                                                                                            |

|----------------------|--------------------------------------------------------------------------------------------------------|

| ASM_DIAG_NAME        | Contains the assembly diag name.                                                                       |

| SIMS_LAUNCH_DIR      | Path to launch directory where sims is running the job. Useful when job is run in dream scratch space. |