XILINX°, XILINX, XACT, XC2064, XC3090, XC4005, XC-DS501, FPGA Archindry, NeoCAD, NeoCAD EPIC, NeoCAD PRISM, NeoROUTE, Plus Logic, Plustran, P+, Timing Wizard, and TRACE are registered trademarks of Xilinx, Inc.

\*\*, all XC-prefix product designations, XACT \*\*step\*\*, XACT \*\*step

All other trademarks are the property of their respective owners.

Xilinx does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or maskwork rights or any rights of others. Xilinx reserves the right to make changes, at any time, in order to improve reliability, function or design and to supply the best product possible. Xilinx will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. Xilinx devices and products are protected under one or more of the following U.S. Patents: 4.642.487; 4.695,740; 4,706,216; 4,713,557; 4,746,822; 4,750,155; 4,758,985; 4,820,937; 4,821,233; 4,835,418; 4,853,626; 4,855,619; 4,855,669; 4,902,910; 4,940,909; 4,967,107; 5,012,135; 5,023,606; 5,028,821; 5,047,710; 5,068,603; 5,140,193; 5,148,390; 5,155,432; 5,166,858; 5,224,056; 5,243,238; 5,245,277; 5,267,187; 5,291,079; 5,295,090; 5,302,866; 5,319,252; 5,319,254; 5,321,704; 5,329,174; 5,329,181; 5,331,220; 5,331,226; 5,332,929; 5,337,255; 5,343,406; 5,349,248; 5,349,249; 5,349,250; 5,349,691; 5,357,153; 5,360,747; 5,361,229; 5,362,999; 5,365,125; 5,367,207; 5,386,154; 5,394,104; 5,399,924; 5,399,925; 5,410,189; 5,410,194; 5,414,377; 5,422,833; 5,426,378; 5,426,379; 5,430,687; 5,432,719; 5,448,181; 5,448,493; 5,450,021; 5,450,022; 5,453,706; 5,466,117; 5,469,003; 5,475,253; 5,477,414; 5,481,206; 5,483,478; 5,486,707; 5,486,776; 5,488,316; 5,489,858; 5,489,866; 5,491,353; 5,495,196; 5,498,979; 5,498,989; 5,499,192; 5,500,608; 5,500,609; 5,502,000; 5,502,440; RE 34,363, RE 34,444, and RE 34,808. Other U.S. and foreign patents pending. Xilinx, Inc. does not represent that devices shown or products described herein are free from patent infringement or from any other third party right. Xilinx assumes no obligation to correct any errors contained herein or to advise any user of this text of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user.

Xilinx products are not intended for use in life support appliances, devices, or systems. Use of a Xilinx product in such applications without the written consent of the appropriate Xilinx officer is prohibited.

Copyright 1998 Xilinx, Inc. All Rights Reserved.

# Data Book

LogiCORE/AllianceCORE Fax: +1 408-377-3259

Tech Support E-mail: hotline@xilinx.com

Tech Support Phone Number: +1 800-255-7778

Information & Feedback E-mail: logicore@xilinx.com (all LogiCORE)

Xilinx Home Page URL: www.xilinx.com

PCI Solutions URL: www.xilinx.com/products/logicore/pci/pci\_sol.htm

2100 Logic Drive San Jose, CA 95124 United States of America Telephone: +1 408-559-7778

Fax: +1 408-559-7114

Dear PCI customer,

On behalf of the PCI Team at Xilinx, and our CORE partners, welcome to our May 1998 PCI Data Book, and thank you for your interest in Xilinx PCI Solutions.

As the inventor and leading provider of Field Programmable Gate Array Technology, we want to pledge our continuing commitment to support your great ideas when it comes to logic design and PCI applications.

Our mission is to provide you with a high-quality PCI solution that provides better flexibility, higher performance, and lower cost than any other available solution. Xilinx PCI allows you to integrate a PCI interface with your unique logic, into one flexible programmable device. Since the first PCI product introduction in February 1996, we have developed a complete solution for PCI including super-fast FPGAs, low-cost HardWire FpgASICs, easy-to-use predictable LogiCORE modules with guaranteed timing, as well as PCI boards, drivers and design examples. We think you will find Xilinx PCI Solution interesting and we hope that you consider us for future designs.

Together we can bring the great ideas to life!

Sincerely

Per Holmberg

LogiCORE Product Manager CORE Solutions Group

# **Section Titles**

| 1           | Introduction                                                     |

|-------------|------------------------------------------------------------------|

| 2           | PCI Products                                                     |

| 3           | FPGA Products                                                    |

| 4           | Design Methodology                                               |

| 5           | PCI Compliance Checklists                                        |

| 6           | Pinout and Configuration                                         |

| 7           | Resources                                                        |

| 8           | Waveforms                                                        |

| 9           | Ordering Information and License Agreement                       |

| 10          | Sales Offices, Sales Representatives, and Distributors           |

| 7<br>8<br>9 | Resources  Waveforms  Ordering Information and License Agreement |

iii

## Introduction **PCI Products** PCI32 4000 Master & Slave Interfaces Version 2.0 PCI32 Spartan Master & Slave Interface PCI I/O Interface Block 2 - 9 Verification Methods. 2 - 11

May, 1998

|             | thesizable PCI Bridge Design Examples                              |        |

|-------------|--------------------------------------------------------------------|--------|

| ı           | ntroduction                                                        | 2 - 13 |

| (           | General Description                                                | 2 - 13 |

| I           | Functional Description                                             |        |

|             | BAR0 Configuration                                                 |        |

|             | BAR1 Configuration (DE01 Only)                                     |        |

|             | Register File Interface                                            |        |

|             | Target FIFO Interface                                              |        |

|             | Initiator FIFO Interface                                           |        |

|             | Pinout                                                             |        |

|             | Core Modifications                                                 |        |

|             | Verification Methods                                               |        |

| l           | Recommended Design Experience                                      | 2 - 16 |

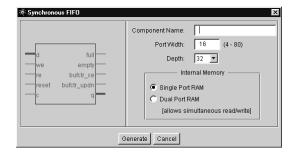

| Syn         | chronous FIFO                                                      |        |

|             | ntroduction                                                        | 2 - 17 |

| ı           | Features                                                           | 2 - 17 |

| ı           | Functional Description                                             | 2 - 17 |

| I           | Pinout                                                             | 2 - 19 |

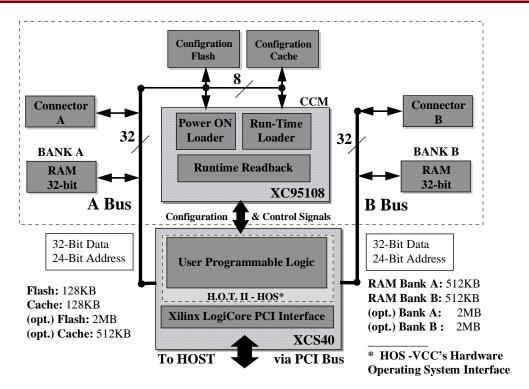

| HotE        | PCI Spartan Prototyping Board                                      |        |

|             | Virtual Computer Corporation                                       | 2 - 21 |

|             | ntroduction.                                                       |        |

|             | Features                                                           |        |

|             | Options                                                            |        |

|             | General Description                                                |        |

|             | Software                                                           | 2 - 22 |

| ı           | Functional Description                                             | 2 - 22 |

|             | Configuration with the CCM                                         | 2 - 22 |

|             | Configuration with an Xchecker cable                               | 2 - 23 |

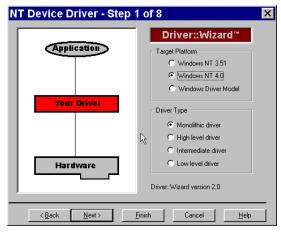

| Driv        | er::Works Windows Device Driver Development Kit Version 2.0        |        |

|             | Vireo Software, Inc                                                | 2 - 25 |

|             | ntroduction.                                                       |        |

|             | Support                                                            |        |

|             | eatures                                                            |        |

|             | Description                                                        |        |

|             | Licensing                                                          |        |

|             | olsD Windows Device Driver Development Kit Version 3.0             |        |

|             | Vireo Software, Inc.                                               | 2 20   |

|             | ntroduction                                                        |        |

|             | Support.                                                           |        |

|             | Features                                                           |        |

|             | Description                                                        |        |

|             | Licensing                                                          |        |

|             |                                                                    |        |

| <b>FPGA</b> | Products                                                           |        |

| VC4         | 000VLT Family Field Drawsmahle Octo America                        |        |

|             | 000XLT Family Field Programmable Gate Arrays                       | 2 4    |

|             | XC4000XLT FeaturesXC4000XLT Family FPGAs                           |        |

|             | XC4000XLT Electrical Features                                      |        |

|             | Additional XC4000XLT Family Features                               |        |

|             | PCI Compatible Features                                            |        |

|             | PCI Requirements for Clamp Diodes.                                 |        |

|             | 5.0 V PCI Requirement for Maximum AC Ratings and Device Protection |        |

| ı           | Difference between the XC4000XLT and XC4000XL FPGAs                |        |

|             | /O signaling compliance                                            |        |

|             | · - · · · · · · · · · · · · · · · · · ·                            |        |

*iv* May, 1998

| Pin Locations for XC4013XLT Devices                                 | 3 - 4  |

|---------------------------------------------------------------------|--------|

| Pin Locations for XC4028XLT Devices                                 | 3 - 6  |

| Pin Locations for XC4062XLT Devices                                 | 3 - 9  |

| Spartan and Spartan-XL Families Field Programmable Gate Arrays      |        |

| Introduction                                                        | 2 12   |

| Spartan Series Features                                             |        |

| ·                                                                   |        |

| General Overview.                                                   |        |

| Device-Specific Pinout Tables                                       |        |

| Pin Locations for XCS30 & XCS30XL Devices                           |        |

| Pin Locations for XCS40 & XCS40XL Devices                           | 3 - 17 |

| Design Mathedalem                                                   |        |

| Design Methodology                                                  |        |

| Design Methodology                                                  |        |

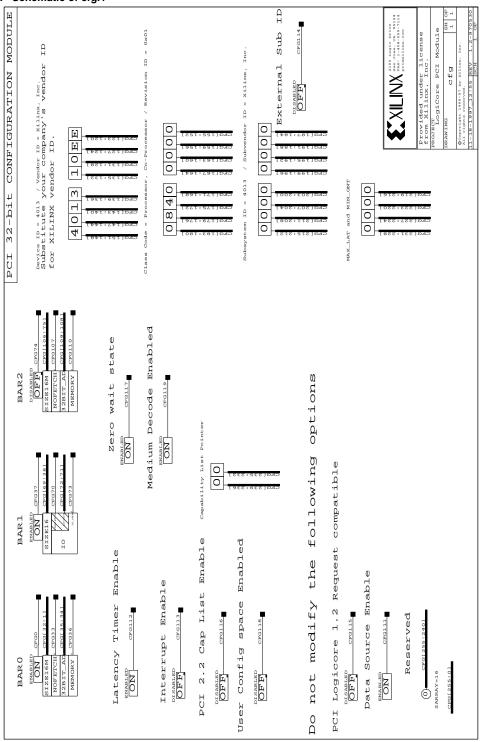

| LogiCORE PCI Configuration                                          |        |

| Configuration Module                                                |        |

| Schematic                                                           | 4 - 2  |

| VHDL and Verilog                                                    |        |

| Selectable Options                                                  | 4 - 2  |

| Wait States                                                         | 4 - 2  |

| Decode Speed                                                        | 4 - 2  |

| CapPtr and User Config Space                                        | 4 - 2  |

|                                                                     |        |

| PCI Compliance Checklists                                           |        |

| XC4000XLT PCI Compliance Checklist                                  |        |

| Component Product Information                                       | E 1    |

|                                                                     |        |

| Component Electrical Checklist                                      |        |

| 5 V Signaling                                                       |        |

| 3.3 V Signaling                                                     |        |

| Loading and Device Protection                                       |        |

| Timing Specification                                                |        |

| 64-bit Components                                                   | 5 - 8  |

| Spartan PCI Compliance Checklist                                    |        |

| Component Product Information                                       | 5 - 9  |

| Component Electrical Checklist                                      | 5 - 9  |

| 5 V Signaling                                                       | 5 - 10 |

| 3.3 V Signaling                                                     | 5 - 12 |

| Loading and Device Protection                                       |        |

| Timing Specification                                                |        |

| 64-bit Components                                                   |        |

| LogiCORE PCI32 Cores PCI Compliance Checklist                       |        |

| Component Product Information                                       | 5 17   |

|                                                                     |        |

| Component Configuration Checklist                                   |        |

| Device Control                                                      |        |

|                                                                     | -      |

| Device Status                                                       |        |

|                                                                     |        |

| VGA Devices                                                         |        |

| General Component Protocol Checklist (Master)                       |        |

| General Component Protocol Checklist (Target)                       |        |

| Component Protocol Checklist for a Master Device.                   |        |

| Test Scenario: 1.1. PCI Device Speed (as indicated by DEVSEL) Tests |        |

| Test Scenario: 1.2. PCI Bus Target Abort Cycles                     |        |

| Test Scenario: 1.3. PCI Bus Target Retry Cycles                     |        |

| Test Scenario: 1.4. PCI Bus Single Data Phase Disconnect Cycles     | 5 - 35 |

May, 1998 v

|           | Test Scenario: 1.5. PCI Bus Multi-Data Phase Target Abort Cycles                          | 5 - 37 |

|-----------|-------------------------------------------------------------------------------------------|--------|

|           | Test Scenario: 1.6. PCI Bus Multi-Data Phase Retry Cycles                                 |        |

|           | Test Scenario: 1.7. PCI Bus Multi-Data Phase Disconnect Cycles                            |        |

|           | Test Scenario: 1.8. Multi-Data Phase & TRDY# Cycles                                       |        |

|           | Test Scenario: 1.9. Bus Data Parity Error Single Cycles                                   |        |

|           | Test Scenario: 1.10. Bus Data Parity Error Multi-Data Phase Cycles                        | 5 - 49 |

|           | Test Scenario: 1.11. Bus Master Timeout.                                                  | 5 - 51 |

|           | Test Scenario: 1.12. Target Lock.                                                         |        |

|           | Test Scenario: 1.13. PCI Bus Master Parking                                               |        |

|           | Test Scenario: 1.14. PCI Bus Master Arbitration                                           |        |

| Co        | mponent Protocol Checklist for a Target Device                                            |        |

|           | Test Scenario: 2.1. Target Reception of an Interrupt Cycle                                |        |

|           | Test Scenario: 2.2. Target Reception of Special Cycle                                     |        |

|           | Test Scenario: 2.3. Target Detection of Address and Data parity Error for Special Cycle   |        |

|           | Test Scenario: 2.4. Target Reception of I/O Cycles With Legal and Illegal Byte Enables    |        |

|           | Test Scenario: 2.5. Target Ignores Reserved Commands                                      |        |

|           | Test Scenario: 2.6. Target Receives Configuration Cycles                                  |        |

|           | Test Scenario: 2.7. Target Receives I/O Cycles With Address and Data Parity Errors        |        |

|           | Test Scenario: 2.8. Target Gets Config. Cycles With Address and Data Parity Errors        |        |

|           | Test Scenario: 2.9. Target Receives Memory Cycles                                         |        |

|           | Test Scenario: 2.10. Target Gets Memory Cycles With Address and Data Parity Errors        |        |

|           | Test Scenario: 2.11. Target Gets Fast Back to Back Cycles                                 |        |

|           | Test Scenario: 2.12. Target Performs Exclusive Access Cycles                              |        |

|           | Test Scenario: 2.13. Target Gets Cycles With IRDY Used for Data Stepping                  |        |

|           | Test Scenario: 2.14. Target Signals and Responds to Various Target Termination Conditions |        |

|           | Test Scenario 2.x. Explanations.                                                          | 5 - 59 |

| Discout a | and Configuration                                                                         |        |

|           | nd Configuration                                                                          |        |

| Pin       | but and Configuration                                                                     |        |

|           | Layout Considerations                                                                     |        |

|           | Pinout Tables                                                                             |        |

|           | Configuration Mode                                                                        |        |

|           | Pinout for the XC4013XLT PQ208                                                            | -      |

|           | Pinout for the XC4013XLT PQ240                                                            | -      |

|           | Pinout for the XC4028XLT HQ240                                                            | -      |

|           | Pinout for the XC4062XLT HQ240                                                            |        |

|           | Pinout for the XC4062XLT BG432                                                            |        |

|           | Pinout for the XCS30 PQ208                                                                |        |

|           | Pinout for the XCS30 PQ240                                                                |        |

|           | Pinout for the XCS40 PQ208                                                                |        |

|           | Pinout for the XCS40 PQ240                                                                | 6 - 27 |

| Deceure   | ••                                                                                        |        |

| Resourc   |                                                                                           |        |

| Res       | sources                                                                                   |        |

|           | PCI Special Interest Group (PCI-SIG) Publications                                         |        |

|           | PCI and FPGA Design Consultants                                                           |        |

|           | Supporting PCI Tools.                                                                     |        |

|           | PCI Reference Books                                                                       |        |

|           | Xilinx Documents                                                                          |        |

|           | LogiCORE User's Lounge Web Site                                                           | 1 - 2  |

*vi* May, 1998

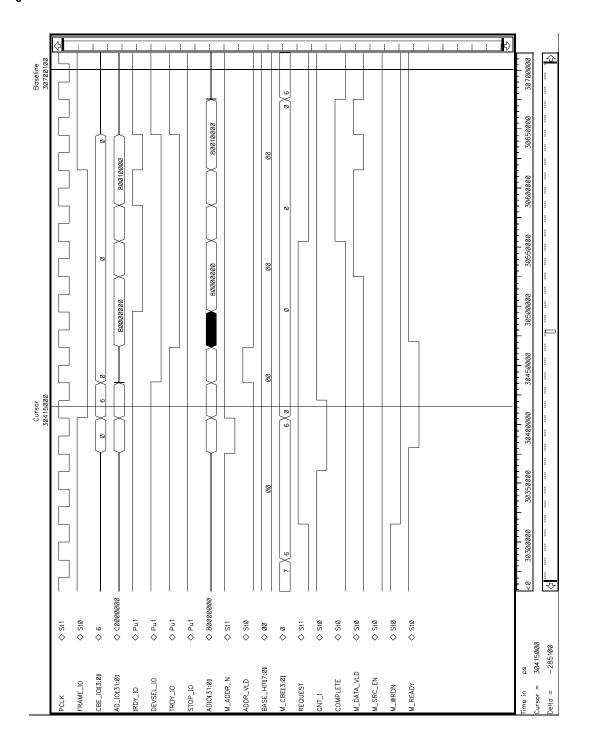

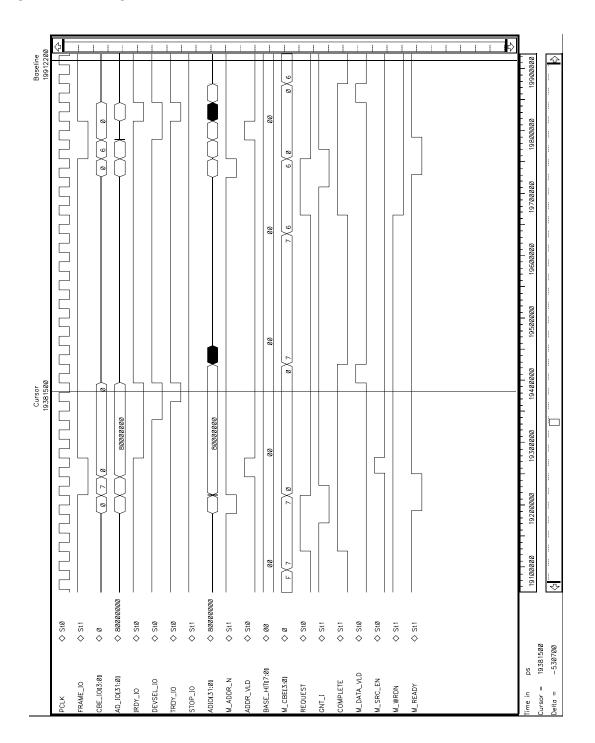

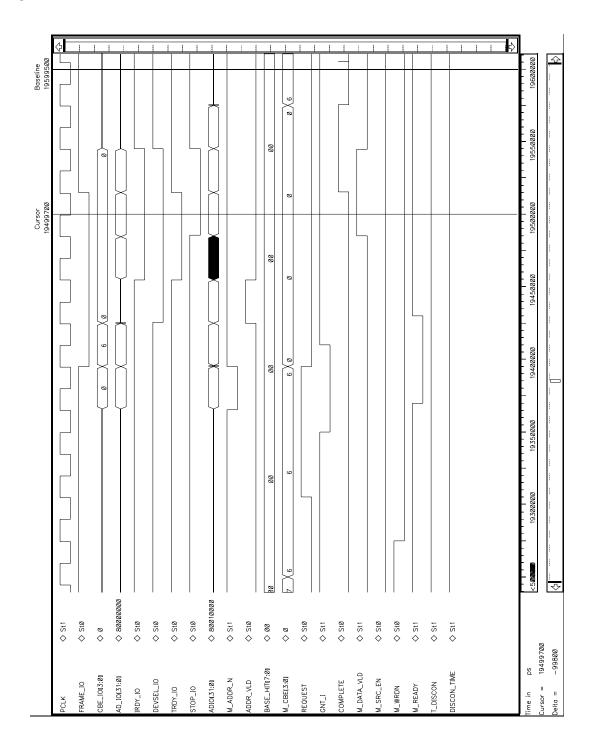

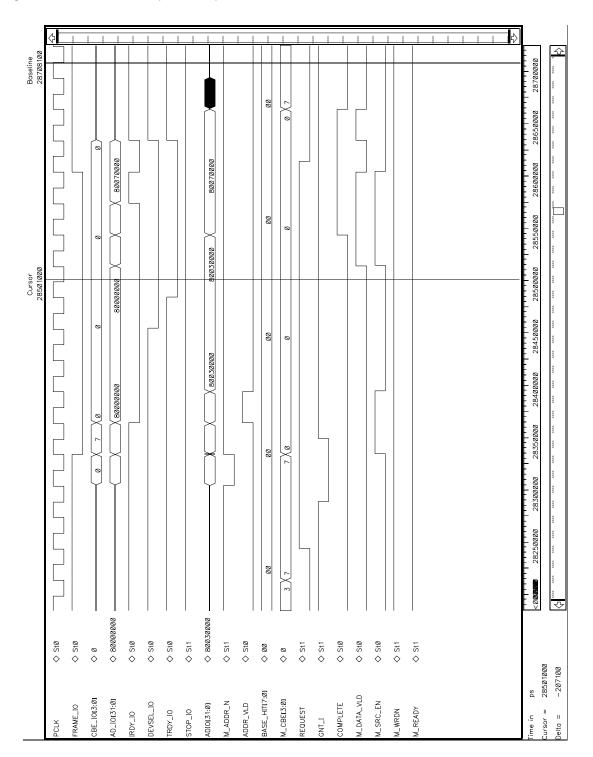

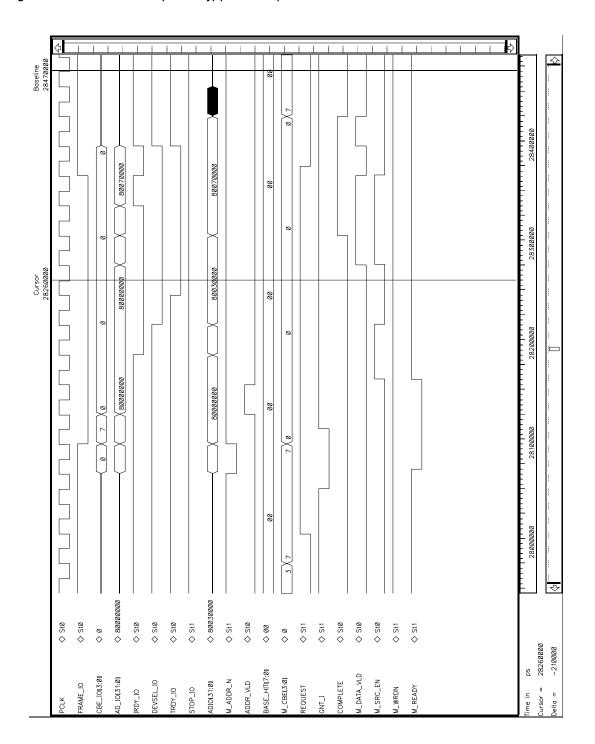

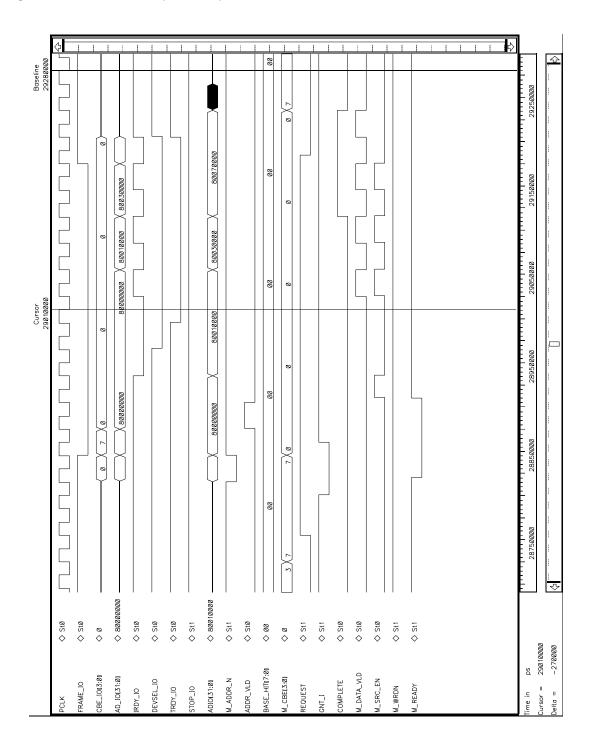

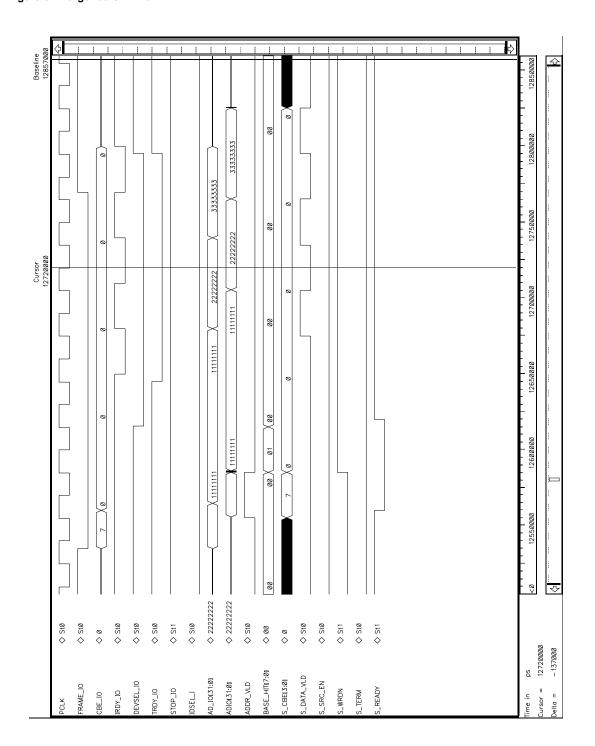

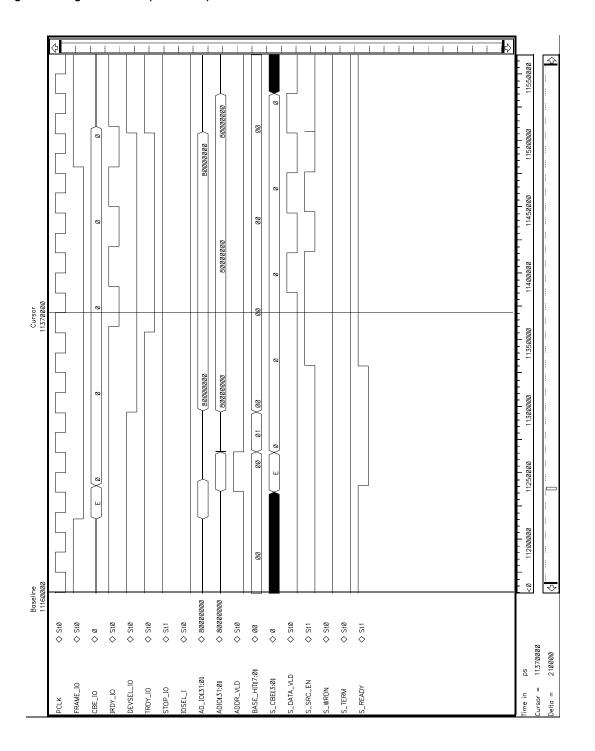

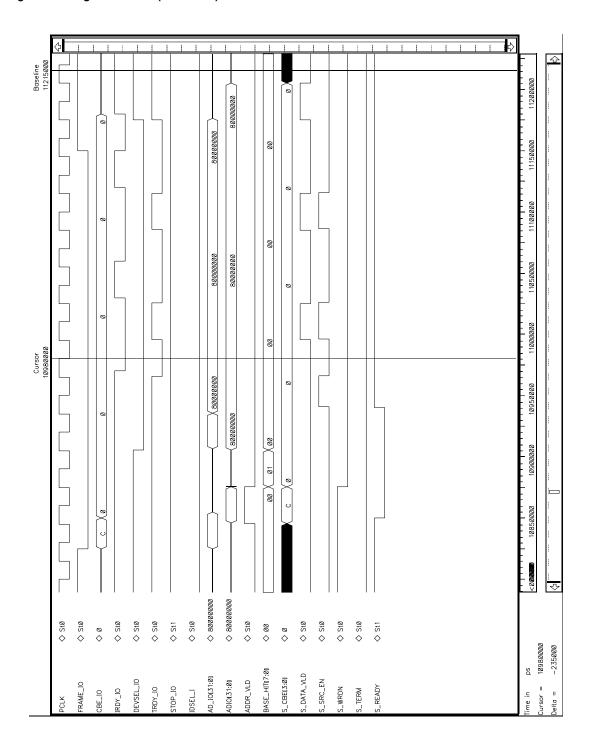

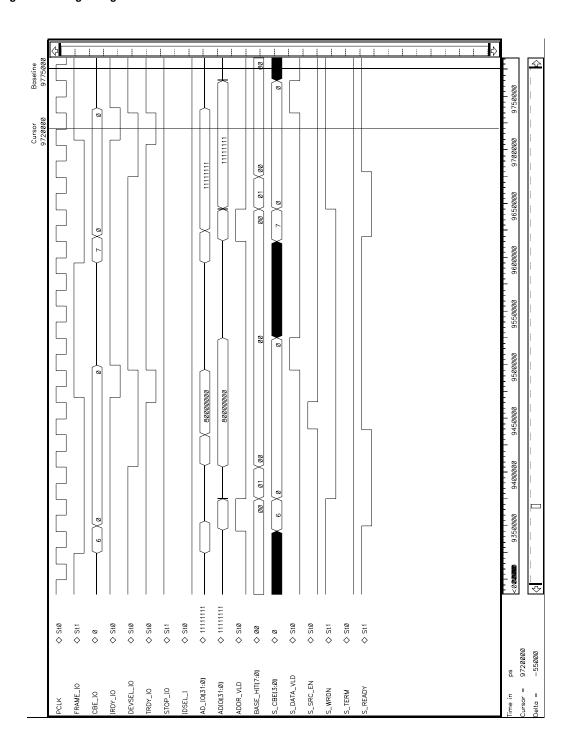

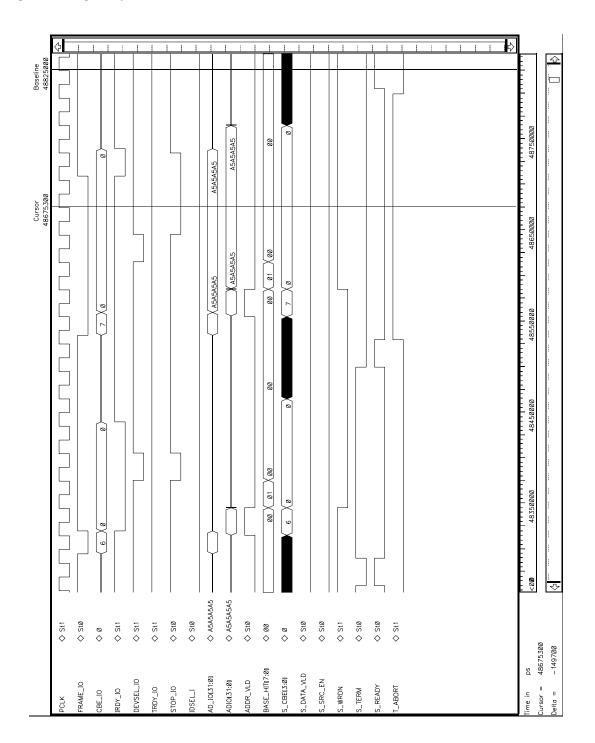

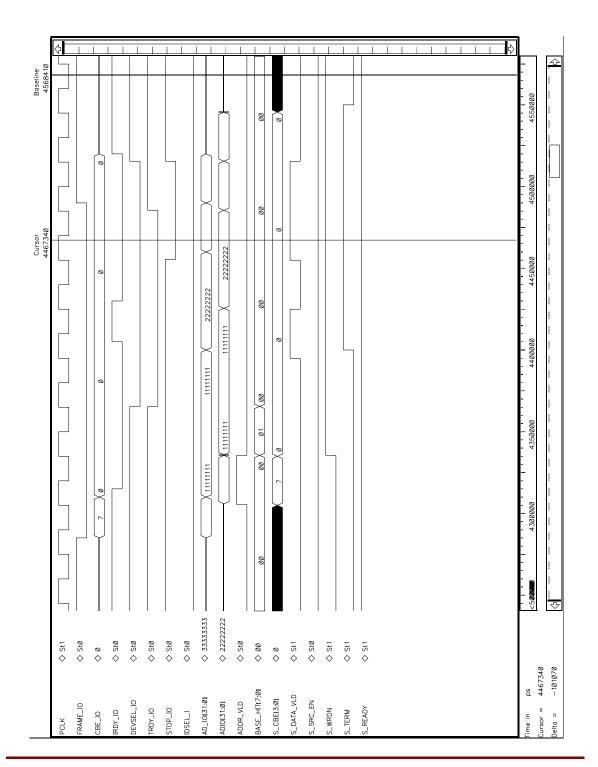

# Waveforms

| Waveforms                                                 | 8 - | - 1   |

|-----------------------------------------------------------|-----|-------|

| Configuration Read and Write                              | 8 - | - 2   |

| Initiator Burst Read                                      | 8 - | - 4   |

| Initiator Single Read and Write                           | 8 - | - 6   |

| Initiator Burst Write with Disconnect                     | 8 - | - 8   |

| Initiator Burst Write (0 waitstate)                       | 8 - | - 10  |

| Initiator Burst Write (not ready, 0 waitstate)            | 8 - | - 12  |

| Initiator Burst Write (1 waitstate)                       | 8 - | - 14  |

| Target Burst Write                                        | 8 - | - 16  |

| Target Burst Read (0 waitstate)                           | 8 - | - 18  |

| Target Burst Read (1 waitstate)                           | 8 - | - 20  |

| Target Single Read and Write                              | 8 - | - 22  |

| Target Retry and Abort                                    | 8 - | - 24  |

| Target Burst Write with Disconnect                        | 8 - | - 26  |

|                                                           |     |       |

| Ordering Information and License Agreement                |     |       |

| Ordering Information and License Agreement                |     |       |

| Summary                                                   |     |       |

| Xilinx PCl32 Design Kit                                   |     |       |

| Overview                                                  | _   |       |

| Package Includes                                          |     |       |

| Support and Updates                                       |     |       |

| Licensing                                                 |     |       |

| LogiCORE PCI32 Spartan                                    |     |       |

| Overview                                                  |     |       |

| Package Includes                                          |     |       |

| Support and Updates                                       |     |       |

| Licensing                                                 |     |       |

| Additional PCI Products from Virtual Computer Corporation |     |       |

| Products                                                  |     |       |

| Additional PCI Products from Vireo Software               |     |       |

| Obsolete products                                         |     |       |

| License Agreement                                         | 9 - | - 4   |

| Salas Offices Salas Penrasantativas and Distributors      |     |       |

| Sales Offices, Sales Representatives, and Distributors    | 4.0 |       |

| Headquarters                                              |     |       |

| Xilinx Sales Offices.                                     |     |       |

| North American Distributors                               |     |       |

| U.S. Sales Representatives                                |     |       |

| International Sales Representatives                       | 10  | J - 3 |

May, 1998

*viii* May, 1998

# Introduction

| 4 |   |     |   |   | - 41 |    |   |

|---|---|-----|---|---|------|----|---|

| 1 | m | tro | a | Ш | ct   | IO | n |

- 2 PCI Products

- 3 FPGA Products

- 4 Design Methodology

- 5 PCI Compliance Checklists

- 6 Pinout and Configuration

- 7 Resources

- 8 Waveforms

- 9 Ordering Information and License Agreement

- 10 Sales Offices, Sales Representatives, and Distributors

## Introduction

#### Xilinx PCI team - Mission

We provide the most cost-effective and highest-performance PCI solution in the market by leveraging the flexibility of Xilinx Field Programmable Gate Arrays (FPGAs). We make PCI easy to design by providing a complete solution of proven cores, intuitive development tools, and comprehensive support.

#### Why Xilinx PCI?

By integrating a fully-compliant PCI interface with an application-specific back-end design, into one FPGA, you can achieve higher integration and higher performance than other PCI solutions.

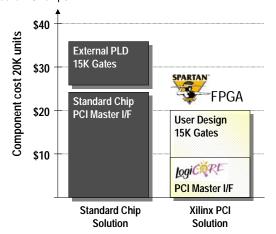

Because Xilinx FPGAs integrate the PCI interface plus 15,000 to 124,000 user gates, no external PLD is required for glue logic. The result is a highly integrated, one-chip PCI solution at a lower cost than most standard PCI chip sets. See Figure 1 for a comparison of the Xilinx PCI and standard PCI chips.

Figure 1: The cost of a Xilinx Spartan FPGA integrating a fully compliant PCI interface and 15,000 user gates, compared to a standard chip solution requiring an external PLD for glue logic.

The Xilinx PCI solution can be customized for a specific application and, as a result, the highest possible performance is achieved. Xilinx high-speed FPGAs support zero wait-state burst operations and by integrating scalable, dual-port FIFOs on the chip, a sustained bandwidth of up to 132 MBytes/sec can be achieve, system constraints being the only limitation.

The flexibility of Xilinx FPGAs makes it possible to update the PCI board, through software alone, in development or in the field. This significantly reduces your design risk and cuts development time. Xilinx and its partners can also provide reference design examples, prototyping boards, PCI drivers, driver development tools, and design services.

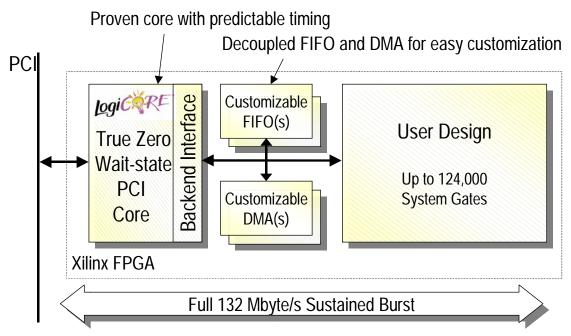

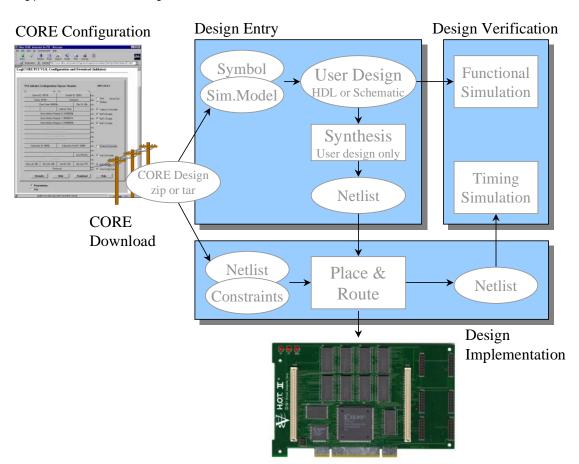

All LogiCORE PCI products incorporates Xilinx Smart-IP technology, which leverages the Xilinx architectural advantages, such as look-up tables (LUTs), distributed RAM, and segmented routing, and floorplanning information, such as logic mapping, placement and routing constraints. The result is a highly predictable core, which is fixed to meet the critical PCI timing. This combined with a modular architecture, illustrated in Figure 2, allows the designer to customize the back-end design including FIFOs and DMA functions without jeopardizing the critical timing on the PCI side.

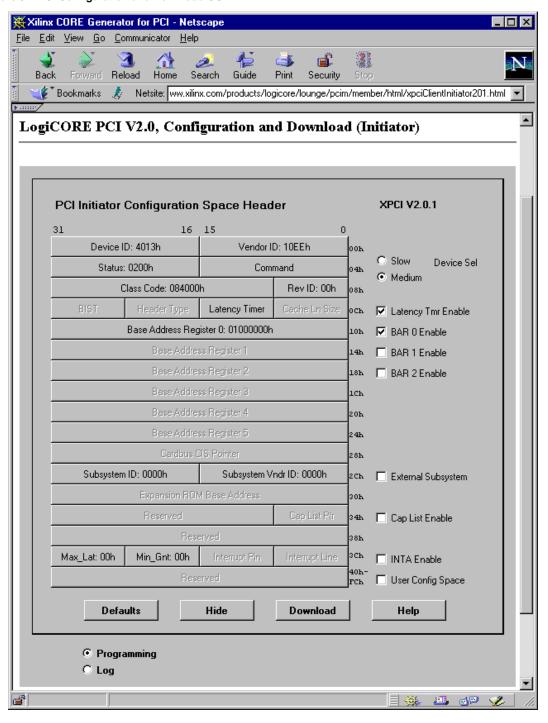

The predictable LogiCORE PCI interface is customized and downloaded using an intuitive graphical user interface available on Xilinx web-site, see the Design Methodologies chapter. The core is delivered with VHDL and Verilog simulation models, testbenches, and design examples.

# Xilinx PCI32 Design Kit

To minimize the learning curve for PCI and to enable rapid development and prototyping, Xilinx provides a complete PCI Design Kit including cores, a prototyping board and driver development tools. By forming a partnership with Virtual Computer Corporation, leading provider of rapid prototyping boards and reconfigurable computing systems, and Vireo Software, leading provider of device driver tools, our customers will always have access to the leading industry expertise.

Xilinx PCI32 Design Kit contains:

- LogiCORE PCI32 interfaces (Xilinx)

- PCI System Architecture book (MindShare, Inc.)

- Bridge Design Examples (Xilinx)

- HotPCI Prototyping Board (VCC)

- Demo software (VCC)

- Canned reference drivers (Vireo)

- Driver development tools (Vireo)

#### Xilinx PCI32 Interfaces

PCI32 4000 – the high-density PCI solution.

This solution integrates a PCI interface plus up to

1134,000 system gates. The core supports zero waitstate burst operations and a sustained bandwidth of up to 132 Mbytes per second. See the PCI32 4000 data sheet for more details.

PCI32 Spartan – the low-cost PCI solution.

This solution integrates a PCI interface plus up to 30,000 system gates at a price below standard chip solutions. The core supports zero wait-state burst operations and a sustained bandwidth of up to 132 Mbytes per second. See the PCI32 Spartan data sheet for more details.

See the Ordering Information chapter for more details.

May, 1998

Figure 2: Block Diagram of PCI32 4000 Interface and Backend Interface

## **About this Catalog**

The information in this catalog is also available on the Xilinx web-site, WebLINX at

www.xilinx.com/products/logicore/pci/pci\_sol.htm

Xilinx will use the web as primary means of delivering and updating this information since it is so dynamic by nature. We strongly recommend that customers consult the web for the latest information on new product availability and datasheet revisions.

1 - 2 May, 1998

# **PCI Products**

1 Introduction

#### 2 PCI Products

- 3 FPGA Products

- 4 Design Methodology

- 5 PCI Compliance Checklists

- 6 Pinout and Configuration

- 7 Resources

- 8 Waveforms

- 9 Ordering Information and License Agreement

- 10 Sales Offices, Sales Representatives, and Distributors

| DOI Des desets |  |  |

|----------------|--|--|

| PCI Products   |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

|                |  |  |

# PCI32 4000 Master & Slave Interfaces Version 2.0

May, 1998 Data Sheet

Xilinx Inc.

2100 Logic Drive San Jose, CA 95124

Phone: +1 408-559-7778 Fax: +1 408-377-3259

$\textbf{E-mail:} \quad \textbf{Techsupport:} \\ \texttt{hotline@xilinx.com} \\$

Feedback: logicore@xilinx.com

URL: http://www.xilinx.com

#### Introduction

With Xilinx LogiCORE PCl32 4000 Master and Slave interfaces Version 2.0, a designer can build a customized, 32 bit, 33 MHz fully PCl compliant system with the highest possible sustained performance, 132 Mbytes/s, and up to 124,000 system gates in a XC4000XLT FPGA.

#### **Features**

- Fully 2.1 PCI compliant 32 bit, 33 MHz PCI Interface

- Master (Initiator/Target)

- Slave (Target-only)

- Programmable single-chip solution with customizable back-end functionality

- Pre-defined implementation for predictable timing in Xilinx XC4000XLT FPGAs or HardWire<sup>™</sup> FpgASICs (see LogiCORE Facts for listing of supported devices)

- Incorporates Xilinx Smart-IP Technology

- 3.3 V Operation with XC4000XLT devices

- · Zero wait-state burst operation

- · Fully verified design

- Tested with the Xilinx internal testbench

- Tested in hardware (proven in FPGAs and HardWire devices)

- Configurable on-chip dual-port FIFOs can be added for maximum burst speed (see Xilinx Documents section)

- Design Once<sup>™</sup> automatic conversion to a HardWire FpgASIC for cost reduction

- Supported Initiator functions (PCI Master only)

- Initiate Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Read Line (MRL) commands

- Initiate I/O Read, I/O Write commands

- Initiate Configuration Read, Configuration Write commands

- Bus Parking

- Basic Host Bridging

| LogiCORE <sup>™</sup> Facts                            |                           |                                       |  |  |

|--------------------------------------------------------|---------------------------|---------------------------------------|--|--|

|                                                        | Core Specifics            |                                       |  |  |

| Device Family                                          |                           | XC4000XLT                             |  |  |

| CLBs Used                                              |                           | 178 - 308                             |  |  |

| IOBs Used <sup>1</sup>                                 |                           | 53/51                                 |  |  |

| System Clock f <sub>max</sub>                          |                           | 0 - 33MHz                             |  |  |

| Device Features                                        | Bi-dire                   | ctional data buses                    |  |  |

| Used                                                   |                           | ptional user FIFO)                    |  |  |

|                                                        | Bounda                    | ary scan (optional)                   |  |  |

| Supported De                                           | vices/Resources           | Remaining                             |  |  |

|                                                        | <b>I/O</b> <sup>1,2</sup> | CLB <sup>3</sup>                      |  |  |

| XC4013XLT PQ208                                        | 99/101                    | 268 - 398                             |  |  |

| XC4013XLT PQ240                                        | 133/135                   | 268 - 398                             |  |  |

| XC4028XLT HQ240                                        | 133/135                   | 716 - 846                             |  |  |

| XC4062XLT HQ240                                        | 133/135                   | 1996 - 2126                           |  |  |

| XC4062XLT BG432                                        | 293/295                   | 1996 - 2126                           |  |  |

| Pro                                                    | ovided with Core          |                                       |  |  |

| Documentation                                          | P                         | Cl32 User's Guide                     |  |  |

|                                                        |                           | PCI Data Book                         |  |  |

| Design File Formats                                    |                           | Nlogic schematics<br>Simulation Model |  |  |

|                                                        | vnbl, veillog             | NGO Netlist <sup>4</sup>              |  |  |

| Constraint Files                                       | M1 User Cou               | nstraint File (UCF)                   |  |  |

| Conducting 1 mod                                       | W1 0001 001               | M1 Guide files                        |  |  |

| Verification Tools                                     | VIEWIO                    | gic command files                     |  |  |

|                                                        |                           | VHDL Testbench                        |  |  |

|                                                        |                           | Verilog Testbench                     |  |  |

| Core Symbols                                           | VIEW <i>Io</i>            | <i>gic</i> , VHDL, Verilog            |  |  |

| Reference designs &                                    |                           | Example design:                       |  |  |

| application notes                                      |                           | Reference Design <sup>5</sup>         |  |  |

| A dalition of the sec                                  | Syntnes                   | sizable PCI Bridge                    |  |  |

| Additional Items Reference bool PCI System Architectur |                           |                                       |  |  |

| Design Tool Requirements                               |                           |                                       |  |  |

| Xilinx Core Tools                                      |                           | M1.4                                  |  |  |

| Entry/Verification                                     |                           |                                       |  |  |

| Tools <sup>6</sup>                                     |                           | /erilog, Schematic                    |  |  |

|                                                        | For cha                   | nging source files:                   |  |  |

|                                                        | Workview Off              | ice V7.1.2 or V7.2                    |  |  |

Notes: See next page.

# LogiCORE<sup>™</sup> Facts (cont.)

### Support

Xilinx provides technical support for this LogiCORE™ product when used as described in the User's Guide or supporting Application Notes. Xilinx cannot guarantee timing, functionality, or support of the product if implemented in devices not listed above, or customized beyond that referenced in the product documentation, or if any changes are done in sections of the design marked as "DO NOT MODIFY".

#### Notes:

- 1. Master/Slave.

- The XLT devices use 8 I/O locations for Vtt pins; see XC4000XLT Data Sheet.

- 3. The exact number of CLBs depends on user configuration of the core and level of resource sharing with adjacent logic. Factors that can affect the size of the design are number and size of the BARs, zero vs. one wait-state, and medium vs. slow decode. These numbers include a 16 x 32 FIFO.

- Available on Xilinx Home Page, in the LogiCORE PCI Lounge: www.xilinx.com/products/logicore/pci/pci\_sol.htm

- 5. Slave only.

- 6. See Xilinx Home Page for supported EDA tools.

# Features (cont.)

- Supported Target functions (PCI Master and Slave)

- Type 0 Configuration Space Header

- Up to 3 Base Address Registers (memory or I/O with adjustable block size from 16 bytes to 2 GBytes, slow or medium decode speed)

- Parity Generation (PAR), Parity Error Detection (PERR# and SERR#)

- Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Real Line (MRL), Memory Write, Invalidate (MWI) commands

- I/O Read, I/O Write commands

- Configuration Read, Configuration Write commands

- 32-bit data transfers, burst transfers with linear address ordering

- Target Abort, Target Retry, Target Disconnect

- Full Command/Status Register

- Available for configuration and download on the Web

- Web-based configuration with intuitive GUI

- Generation of proven design files

# **Applications**

- PCI add-in boards such as graphic cards, video adapters, LAN adapters and data acquisition boards

- Embedded applications within telecommunication and industrial systems

- CompactPCI boards

- · Other applications that need PCI

# **General Description**

The LogiCORE™ PCI32 4000 Master and Slave Interfaces V2.0 are pre-implemented and fully tested modules for Xilinx XC4000XLT FPGAs (see *LogiCORE Facts* for listing of supported devices). The pin-out and the relative placement of the internal Configurable Logic Blocks (CLBs) are predefined. Critical paths are controlled by TimeSpecs and guide files to ensure that timing is always met. This significantly reduces engineering time required to implement the PCI portion of your design. Resources can instead be

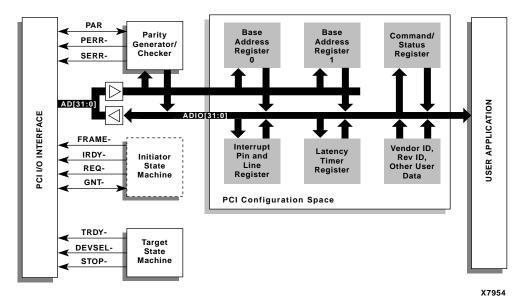

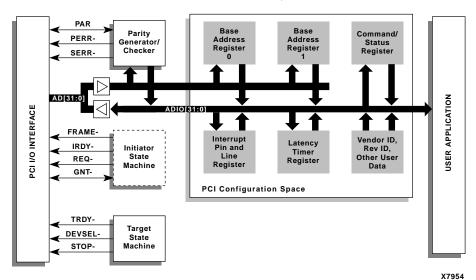

Figure 1: LogiCORE<sup>™</sup> PCI32 4000 Interface Block Diagram (BAR 2 not shown)

2 - 2 May, 1998

focused on the unique back-end logic in the FPGA and the system level design. As a result, the LogiCORE<sup>™</sup> PCI products can cut your development time by several months.

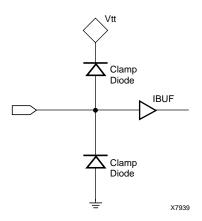

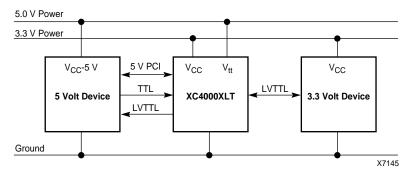

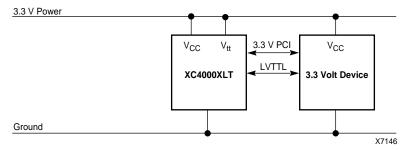

Xilinx XC4000XLT Series FPGAs enable designs of fully PCI-compliant systems. The devices meet all required electrical and timing parameters including AC output drive characteristics, input capacitance specifications (10pF), 7 ns setup and 0 ns hold to system clock, and 11 ns system clock to output. These devices meet all specifications for 3.3 V PCI. Although the XLT devices have a 3V driver they can be used in a 5V PCI system and meet timing for up to 8 loads.

The XC4000XLT devices differ from regular XL devices by the addition of clamp diodes, required by the PCI 3.3 V electrical specification. For more details about this see the XC4000XLT FPGA Data Sheet.

The PCI Compliance Checklist (later in this databook) has additional details about electrical compliance. Other features that enable efficient implementation of a complete PCI system in the XC4000XLT includes:

- Select-RAM™ memory: on-chip ultra-fast RAM with synchronous write option and dual-port RAM option.

Used in the PCI Interfaces to implement the FIFO.

- Individual output enable for each I/O

- Internal 3-state bus capability

- · 8 global low-skew clock or signal distribution networks

- IEEE 1149.1-compatible boundary scan logic support

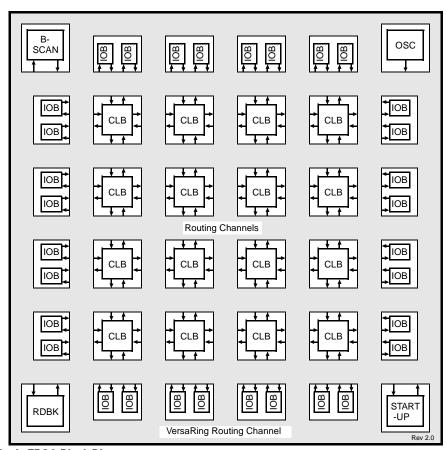

The module is carefully optimized for best possible performance and utilization in the XC4000XLT FPGA architecture. When implemented in the XC4013, more than 50% of the FPGA's resources remain for integrating a unique backend interface and other system functions into a fully programmable one-chip solution. When implemented in a XC4062, 90% of the FPGA's resources remain.

Xilinx DesignOnce<sup>™</sup> service allows an automatic conversion to a low cost HardWire<sup>™</sup> device for high-volume production.

# **Smart-IP Technology**

Drawing on the architectural advantages of Xilinx FPGAs, new Xilinx Smart-IP technology ensures highest performance, predictability, repeatability, and flexibility in PCI designs. The Smart-IP technology is incorporated in every LogiCORE PCI Core.

Xilinx Smart-IP technology leverages the Xilinx architectural advantages, such as look-up tables (LUTs), distributed RAM, and segmented routing, and floorplanning information, such as logic mapping and relative location constraints. This technology provides the best physical layout, predictability, and performance. Additionally, these predetermined features allow for significantly reduced compile times over competing architectures.

The PCI32 Spartan Interface can parameterized, allowing for design flexibility in which users can create the exact PCI interface needed. PCI Cores made with Smart-IP technology are unique by maintaining their performance and predictability regardless of the device size.

# **Functional Description**

The LogiCORE PCI32 4000 Interfaces are partitioned into five major blocks, plus the user application, shown in Figure 1. Each block is described below.

#### PCI I/O Interface Block

The I/O interface block handles the physical connection to the PCI bus including all signaling, input and output synchronization, output three-state controls, and all requestgrant handshaking for bus mastering.

### Parity Generator/Checker

Generates/checks even parity across the AD bus, the CBE lines, and the PAR signal. Reports data parity errors via PERR- and address parity errors via SERR-.

#### **Target State Machine**

This block manages control over the PCI interface for Target functions. The states implemented are a subset of equations defined in "Appendix B" of the PCI Local Bus Specification. The controller is a high-performance state machine using state-per-bit (one-hot) encoding for maximum performance. State-per-bit encoding has narrower and shallower next-state logic functions that closely match the Xilinx FPGA architecture.

## **Initiator State Machine (PCI Master only)**

This block manages control over the PCI interface for Initiator functions. The states implemented are a subset of equations defined in "Appendix B" of the PCI Local Bus Specification. The Initiator Control Logic also uses stateper-bit encoding for maximum performance.

## **PCI Configuration Space**

This block provides the first 64 bytes of Type 0, version 2.1, Configuration Space Header (CSH) (see Table 1) to support software-driven "Plug-and Play" initialization and configuration. This includes Command, Status, and three Base Address Registers (BARs). BAR 2 is not shown in figure 1. These BARs illustrate how to implement memory- or I/O-mapped address spaces. Each BAR sets the base address for the interface and allows the system software to determine the addressable range required by the interface. Using a combination of Configurable Logic Block (CLB) flipflops for the read/write registers and CLB look-up tables for the read-only registers results in optimized packing density and layout.

With this release, the hooks for extending configuration space has been built into the backend interface. These hooks, including the ability to implement a CapPtr in configuration space, allows the user to implement functions such as Advanced Configuration and Power Interface (ACPI) in the backend design.

Table 1: PCI Configuration Space Header

| 31      | 16 15 0             |                  |                    |         |  |

|---------|---------------------|------------------|--------------------|---------|--|

| Devi    | Device ID Vendor ID |                  |                    | 00h     |  |

| Sta     | itus                | Comi             | mand               | 04h     |  |

|         | Class Code          |                  | Rev ID             | 08h     |  |

| BIST    | Header<br>Type      | Latency<br>Timer | Cache<br>Line Size | 0Ch     |  |

| Bas     | e Address R         | egister 0 (BA    | \R0)               | 10h     |  |

| Bas     | e Address R         | egister 1 (BA    | \R1)               | 14h     |  |

| Bas     | e Address R         | egister 2 (BA    | AR2)               | 18h     |  |

| Bas     | e Address R         | egister 3 (BA    | A <i>R3)</i>       | 1Ch     |  |

| Bas     | e Address R         | egister 4 (BA    | A <i>R5)</i>       | 20h     |  |

| Bas     | e Address R         | egister 5 (BA    | A <i>R5)</i>       | 24h     |  |

|         | Cardbus C           | CIS Pointer      |                    | 28h     |  |

| Subsys  | stem ID             | Subsystem        | Vendor ID          | 2Ch     |  |

| Exp     | oansion RON         | Л Base Addr      | ess                | 30h     |  |

|         | Reserved CapPtr     |                  |                    |         |  |

|         | 38h                 |                  |                    |         |  |

| Max_Lat | Min_Gnt             | Interrupt<br>Pin | Interrupt<br>Line  | 3Ch     |  |

|         | Reserved            |                  |                    | 40h-FFh |  |

| Note:   | Note:               |                  |                    |         |  |

Note:

Italicized address areas are not implemented in the LogiCORE PCl32 4000 Interface default configuration. These locations return zero during configuration read accesses.

# **User Application with Optional Burst FIFOs**

The LogiCORE PCI32 4000 Interfaces provide a simple, general-purpose interface with a 32-bit data path and latched address for de-multiplexing the PCI address/data bus. The general-purpose user interface allows the rest of the device to be used in a wide range of applications.

Typically, the user application contains burst FIFOs to increase PCI system performance (An Application Note is available, please see the *Xilinx Documents* section). An onchip read/write FIFO, built from the on-chip synchronous

dual-port RAM (SelectRAM™) available in XC4000XLT devices, supports data transfers in excess of 33 MHz.

# **Interface Configuration**

The LogiCORE PCI32 4000 Interfaces can easily be configured to fit unique system requirements using Xilinx webbased graphical configuration tool or changing the VHDL, Verilog, or VIEW*logic* configuration file. The following customization is supported by the LogiCORE product and described in accompanying documentation.

- Initiator or target functionality (PCI Master only)

- Base Address Register configuration (1 3 Registers, size and mode)

- · Configuration Space Header ROM

- Initiator and target state machine (e.g., termination conditions, transaction types and request/transaction arbitration)

- Burst functionality

- User Application including FIFO (back-end design)

**Table 2: PCI Bus Commands**

| CBE [3:0] | Command                 | PCI<br>Master   | PCI<br>Slave |

|-----------|-------------------------|-----------------|--------------|

| 0000      | Interrupt Acknowledge   | No¹             | Ignore       |

| 0001      | Special Cycle           | No <sup>1</sup> | Ignore       |

| 0010      | I/O Read                | Yes             | Yes          |

| 0011      | I/O Write               | Yes             | Yes          |

| 0100      | Reserved                | Ignore          | Ignore       |

| 0101      | Reserved                | Ignore          | Ignore       |

| 0110      | Memory Read             | Yes             | Yes          |

| 0111      | Memory Write            | Yes             | Yes          |

| 1000      | Reserved                | Ignore          | Ignore       |

| 1001      | Reserved                | Ignore          | Ignore       |

| 1010      | Configuration Read      | Yes             | Yes          |

| 1011      | Configuration Write     | Yes             | Yes          |

| 1100      | Memory Read Multiple    | Yes             | Yes          |

| 1101      | Dual Address Cycle      | No¹             | Ignore       |

| 1110      | Memory Read Line        | Yes             | Yes          |

| 1111      | Memory Write Invalidate | No <sup>1</sup> | Yes          |

Note:

# Supported PCI Commands

Table 2 illustrates the PCI bus commands supported by the LogiCORE<sup>™</sup> PCI32 4000 Interfaces. The PCI Compliance Checklist, found later in this data book, has more details on supported and unsupported commands.

## **Burst Transfer**

The PCI bus derives its performance from its ability to support burst transfers. The performance of any PCI

2 - 4 May, 1998

<sup>1.</sup> The Initiator can present these commands, however, they either require additional user-application logic to support them or have not been thoroughly tested.

application depends largely on the size of the burst transfer. A FIFO to support PCI burst transfer can efficiently be implemented using the XC4000XLT on-chip RAM feature, SelectRAM™. Each XC4000XLT CLB supports two 16x1 RAM blocks. This corresponds to 32 bits of single-ported RAM or 16 bits of dual-ported RAM, with simultaneous read/write capability.

## **Bandwidth**

The Xilinx PCI32 4000 Interfaces support a sustained bandwidth of up to 132 MBytes/sec. The design can be configured to take advantage of the ability of the LogiCORE PCI32 Interface to do very long bursts. Since the FIFO isn't a fixed size, burst can go on as long as the chipset arbiter will allow. Furthermore, since the FIFOs and DMA are decoupled from the proven core, a designer can modify these functions without effecting the critical PCI timing.

The flexible Xilinx backend, combined with support for many different PCI features, gives users a solution that lends itself to being used in many high-performance applications. Xilinx is able to support different depths of FIFOs as well as dual port FIFOs, synchronous or asynchronous FIFOs and multiple FIFOs. The user is not locked into one DMA engine, hence, a DMA that fits a specific application can be designed.

The theoretical maximum bandwidth of a 32 bit, 33 MHz PCI bus is 132 MB/s. How close you get to this maximum will depend on several factors, including the PCI design used, PCI chipset, the processor's ability to keep up with your data stream, the maximum capability of your PCI design and other traffic on the PCI bus. Older chipsets and processors will tend to allow less bandwidth than newer ones.

This version of the Interface, supports a selectable wait-state for burst operation. The XC4013XLT-1, XC4028XLT-09 and XC4062XLT-09 support zero wait-state burst, equal to a sustained bandwidth of up to 132 MBytes/sec. The XC4028XLT-1 and the XC4062XLT-1 support zero wait-states while sinking data, but require one wait-state while sourcing data. See Table 3 for a list of required speed grades.

Table 3: Required Speed Grade for Desired Number of wait-states.

| Device          | Required Speed Grade |                 |  |

|-----------------|----------------------|-----------------|--|

| Device          | One Wait-State       | Zero Wait-State |  |

| XC4013XLT       | -1                   | -1              |  |

| XC4028XLT       | -1                   | -09             |  |

| XC4062XLT PQ240 | -1                   | TBD             |  |

| XC4062XLT BG432 | -1                   | -09             |  |

In the Zero wait-state mode, no wait-states are inserted either while sourcing data or receiving data. This allows a 100% burst transfer rate in both directions with full PCI compliance. No additional wait-states are inserted in

response to a wait-state from another agent on the bus. Either IRDY or TRDY is kept asserted until the current data phase ends, as required by the V2.1 PCI Specification.

In one wait-state mode, the LogiCORE PCI32 4000 Interface automatically inserts a wait-state when sourcing data (Initiator Write, Target Read) during a burst transfer. In this mode, the LogiCORE PCI32 4000 Interface can accept data at 100% burst transfer rate and supply data at 50%.

See Table 4 for a PCI bus transfer rates for various operations in either zero or one wait-state mode.

Table 4: LogiCORE PCI32 4000 Transfer Rates

| Zero Wait-State Mode             |               |  |  |  |

|----------------------------------|---------------|--|--|--|

| Operation                        | Transfer Rate |  |  |  |

| Initiator Write (PCI ← LogiCORE) | 3-1-1-2       |  |  |  |

| Initiator Read (PCI → LogiCORE)  | 4-1-1-2       |  |  |  |

| Target Write (PCI→ LogiCORE)     | 5-1-1-1       |  |  |  |

| Target Read (PCI ← LogiCORE)     | 6-1-1-1       |  |  |  |

| One Wait-State M                 | Mode          |  |  |  |

| Operation                        | Transfer Rate |  |  |  |

| Initiator Write (PCI ← LogiCORE) | 3-2-2-2       |  |  |  |

| Initiator Read (PCI → LogiCORE)  | 4-1-1-2       |  |  |  |

| Target Write (PCI→ LogiCORE)     | 5-1-1-1       |  |  |  |

| Target Read (PCI ← LogiCORE)     | 6-2-2-2       |  |  |  |

Note: Initiator Read and Target Write operations have effectively the same bandwidth for burst transfer.

# **Timing Specification**

The XC4000XLT family, together with the LogiCORE PCI32 products enables design of fully compliant PCI systems. Backend design can affect the maximum speed your design is capable of. Factors in your back-end designs that can affect timing include loading of hot signals coming directly from the PCI bus, and gate count. Table 5 shows the key timing parameters for the LogiCORE PCI32 Interfaces that must be met for full PCI compliance.

Table 5: Timing Parameters [ns]

| Parameter                                  | Ref.               | Ref. PCI Spec. |     | LogiCORE<br>PCI32 4000,<br>XC4000XLT-1 |                 |

|--------------------------------------------|--------------------|----------------|-----|----------------------------------------|-----------------|

|                                            |                    | Min            | Max | Min                                    | Max             |

| CLK Cycle Time                             |                    | 30             | ~   | 30 <sup>1</sup>                        | ~               |

| CLK High Time                              |                    | 11             |     | 11                                     |                 |

| CLK Low Time                               |                    | 11             |     | 11                                     |                 |

| CLK to Bus Sig-<br>nals Valid <sup>3</sup> | T <sub>ICKOF</sub> | 2              | 11  | 2 <sup>2</sup>                         | 8.5             |

| CLK to REQ# and GNT# Valid <sup>3</sup>    | T <sub>ICKOF</sub> | 2              | 12  | 2 <sup>2</sup>                         | 11              |

| Tri-state to Active                        |                    | 2              |     | 2 <sup>2</sup>                         |                 |

| CLK to Tri-state                           |                    |                | 28  |                                        | 28 <sup>1</sup> |

| Parameter                          | meter Ref. PCI Spec. |     | Spec. | LogiCORE<br>PCI32 4000,<br>XC4000XLT-1 |                 |

|------------------------------------|----------------------|-----|-------|----------------------------------------|-----------------|

|                                    |                      | Min | Max   | Min                                    | Max             |

| Bus Signal Setup to CLK (IOB)      | T <sub>PSD</sub>     |     | 7     |                                        | 7               |

| Bus Signal Setup<br>to CLK (CLB)   |                      |     | 7     |                                        | 7 <sup>1</sup>  |

| GNT# Setup to CLK                  | T <sub>PSD</sub>     |     | 10    |                                        | 7               |

| GNT# Setup to<br>CLK (CLB)         | T <sub>PSD</sub>     |     | 10    |                                        | 10              |

| Input Hold Time<br>After CLK (IOB) | T <sub>PHD</sub>     |     | 0     |                                        | 0               |

| Input Hold Time<br>After CLK (CLB) |                      |     | 0     |                                        | 0 <sup>2</sup>  |

| RST# to Tri-state                  |                      |     | 40    |                                        | 40 <sup>2</sup> |

#### Notes:

- 1. Controlled by TIMESPECS, included in product

- 2. Verified by analysis and bench-testing

- 3. IOB configured for Fast slew rate

## Verification Methods

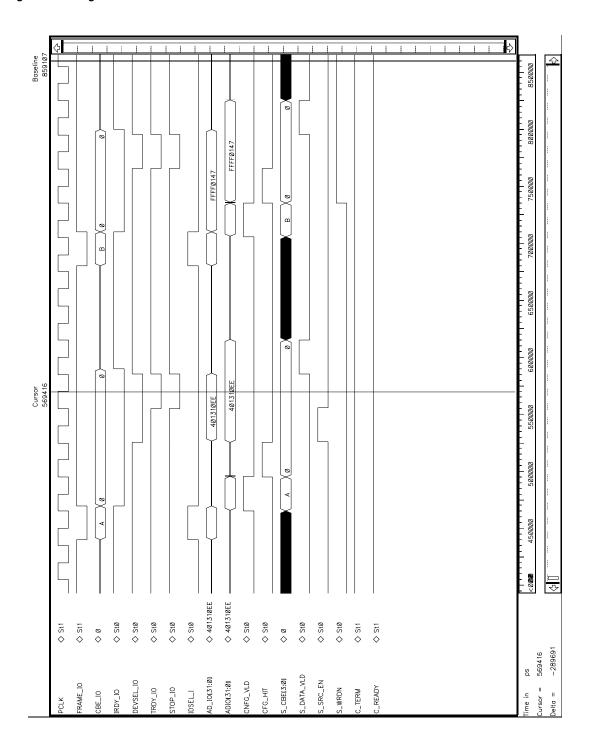

Xilinx has developed a testbench with numerous vectors to test the Xilinx PCI design; this is included with the Logi-CORE PCI32 4000 Master and Slave Interfaces A version of this testbench is also used internally by the Xilinx PCI team to verify the PCI32 Interfaces. Additionally, the PCI32 Interfaces have been tested in hardware for electrical, functional and timing compliance.

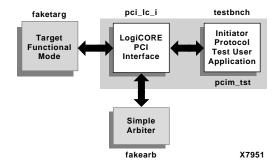

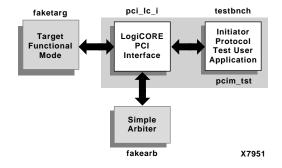

The testbench shipped with the interface verifies the PCI interface functions according to the test scenarios specified in the PCI Local Bus Specification, V2.1; see Figure 2. This testbench consists of 28 test scenarios, each designed to test a specific PCI bus operation. Refer to the checklists chapter in this databook for a complete list of scenarios.

Figure 2: PCI Protocol Testbench

# **Ping Reference Design**

The Xilinx LogiCORE PCI "PING" Application Example, delivered in VHDL and Verilog, has been developed to provide an easy-to-understand example which demonstrates many of the principles and techniques required to successfully use a LogiCORE PCI32 4000 Interface in a System On A Chip solution.

# Synthesizable PCI Bridge Design Example

Synthesizable PCI bridge design examples, delivered in Verilog and VHDL, are available to demonstrate how to interface to the LogiCORE PCI32 4000 V2.0 Interfaces and provides a modular foundation upon which to base other designs. See separate data sheet for details.

#### **Device Utilization**

The Target-Only and Target/Initiator options require a variable amount of CLB resources for the PCI32 4000 Interfaces. Choosing between one and zero wait-states device (e.g. XC4062-1 vs. -09) will change the amount of logic used. The core now includes a switch to force the entire deletion of unused Base Address Registers.

Utilization can vary widely, depending on the configuration choices made by the designer. Options that can affect the size of the core are:

- Initiator vs. Target-Only. The Initiator requires about 12 CLBs more than the target (not set in the cfg file; set at the time the core is generated).

- Number of Base Address Registers Used. Turning off any unused BARs will save on resources.

- Size of the BARs. Setting the BAR to a smaller size requires more flip-flops. A smaller address space requires more flip-flops to decode.

- Decode Speed. Medium decode requires slightly more logic than slow decode.

- Number of wait-states. Zero wait-states requires more logic than one wait-state.

- Latency timer. Disabling the latency timer will save a few resources. It must be enabled for bursting.

# Recommended Design Experience

The LogiCORE PCI32 4000 Interfaces are pre-implemented allowing engineering focus at the unique back-end functions of a PCI design. Regardless, PCI is a high-performance system that is challenging to implement in any technology, ASIC or FPGA. Therefore, we recommend previous experience with building high-performance, pipelined FPGA designs using Xilinx implementation software, TIMESPECs, and guide files. The challenge to implement a complete PCI design including back-end functions varies depending on configuration and functionality of your application. Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

2 - 6 May, 1998

# PCI32 Spartan Master & Slave Interface

May, 1998 Data Sheet

Xilinx Inc.

2100 Logic Drive San Jose, CA 95124

Phone: +1 408-559-7778 Fax: +1 408-377-3259

E-mail: Techsupport: hotline@xilinx.com

Feedback: logicore@xilinx.com

URL: http://www.xilinx.com

#### Introduction

With Xilinx LogiCORE PCI32 Spartan Master & Slave Interface, a designer can build a customizable, low-cost 32-bit, 33MHz fully PCI compliant system in a Spartan-family FPGA.

#### **Features**

- Fully 2.1 PCI compliant 32 bit, 33MHz PCI Interface

- Master (Initiator/Target)

- Slave (Target-only)

- Pre-defined implementation for predictable timing in Xilinx Spartan FPGAs (see LogiCORE Facts for listing of supported devices)

- Incorporates Xilinx Smart-IP Technology

- 5 V Operation with Spartan devices

- · Zero wait-state burst operation

- · Fully verified design

- Tested with the Xilinx internal testbench

- Tested in hardware (silicon proven)

- Configurable on-chip dual-port FIFOs can be added for maximum burst speed (see Xilinx Documents section)

- Programmable single-chip solution with customizable back-end functionality

- Supported Initiator functions

- Initiate Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Read Line (MRL) commands

- Initiate I/O Read, I/O Write commands

- Initiate Configuration Read, Configuration Write commands

- Bus Parking

- Basic Host Bridging

| LogiCORE <sup>™</sup> Facts   |                                 |                                               |

|-------------------------------|---------------------------------|-----------------------------------------------|

|                               | Core Specifics                  |                                               |

| Device Family                 |                                 | XCS Spartan                                   |

| CLBs Used <sup>1</sup>        |                                 | 152 - 268                                     |

| IOBs Used                     |                                 | 53                                            |

| System Clock f <sub>max</sub> |                                 | 0 – 33MHz                                     |

| Device Features               | Bi-dire                         | ctional data buses                            |

| Used                          |                                 | ptional user FIFO)                            |

|                               | Bounda                          | ary scan (optional)                           |

| Supported De                  | vices/Resources                 | Remaining                                     |

|                               | I/O                             | CLB <sup>1</sup>                              |

| XCS30 PQ208                   | 107                             | 308 - 424                                     |

| XCS30 PQ240                   | 141                             | 308 - 424                                     |

| XCS40 PQ208                   | 107                             | 516 - 632                                     |

| XCS40 PQ240                   | 141                             | 516 - 632                                     |

| Pro                           | ovided with Core                |                                               |

| Documentation                 | P                               | Cl32 User's Guide<br>PCl Data Book            |

| Design File Formats           | VHDL, Verilog                   | Simulation Models<br>NGO Netlist <sup>2</sup> |

| Constraint Files              | M1 User Cor                     | nstraint File (UCF)<br>M1 Guide files         |

| Verification Tools            | VHDL and                        | Verilog Testbench                             |

| Core Symbols                  |                                 | VHDL, Verilog                                 |

| Reference designs             | Synthesizable PCI Bridge Design |                                               |

| Desig                         | n Tool Requireme                | nts                                           |

| Xilinx Core Tools             |                                 | M1.4                                          |

| Entry/Verification            | VHDL, \                         | erilog, Schematic                             |

| Tools <sup>4</sup>            |                                 |                                               |

|                               | Support                         |                                               |

|                               |                                 |                                               |

Xilinx provides technical support for this LogiCORE product when used as described in the User's Guide or supporting Application Notes. Xilinx cannot guarantee timing, functionality, or support of the product if implemented in devices not listed above, or customized beyond that referenced in the product documentation.

#### Notes

- The exact number of CLBs depends on user configuration of the core and level of resource sharing with adjacent logic. Factors that can affect the size of the design are number and size of the BARs, and medium vs. slow decode. These numbers include a 16 x 32 FIFO.

- Available on Xilinx Home Page, in the LogiCORE PCI Lounge: www.xilinx.com/products/logicore/pci/pci\_sol.htm

- 3. See Xilinx Home Page for supported EDA tools

# Features (cont.)

- Supported Target functions

- Type 0 Configuration Space Header

- Up to 2 Base Address Registers (memory or I/O with adjustable block size from 16 bytes to 2 GBytes, slow decode speed)

- Parity Generation (PAR), Parity Error Detection (PERR# and SERR#

- ACPI Configuration Registers (backend module)

- Memory Read, Memory Write, Memory Read Multiple (MRM), Memory Real Line (MRL), Memory Write, Invalidate (MWI) commands

- I/O Read, I/O Write commands

- Configuration Read, Configuration Write commands

- 32-bit data transfers, burst transfers with linear address ordering

- Target Abort, Target Retry, Target Disconnect

- Full Command/Status Register

- Available for configuration and download on the web

- Web-based configuration

- Generation of proven design files

# **Applications**

- PCI add-in boards such as graphic cards, video adapters, LAN adapters and data acquisition boards.

- Embedded applications within telecommunication and industrial systems.

- · CompactPCI boards,

- · Other applications that need PCI

# **General Description**

The LogiCORE™ PCI32 Spartan Master and Slave Interfaces are pre-implemented and fully tested modules for Xilinx Spartan FPGAs (see *LogiCORE Facts* for listing of supported devices). The pin-out and the relative placement of the internal Configurable Logic Blocks (CLBs) are predefined. Critical paths are controlled by TimeSpecs and guide files to ensure that timing is always met. This significantly reduces engineering time required to implement the PCI portion of your design. Resources can instead be focused on the unique back-end logic in the FPGA and the system level design. As a result, the LogiCORE PCI products can cut your development time by several months.

Xilinx Spartan Series FPGAs enables designs of fully PCI compliant systems. The devices meet all required electrical and timing parameters including AC output drive characteristics, input capacitance specifications (10pF), 7 ns setup and 0 ns hold to system clock, and 11 ns system clock to output. These devices meet all specifications for 5 V PCI.

The PCI Compliance Checklists, found later in this data book, have additional details. Other features that enable efficient implementation of a complete PCI system in the Spartan family includes:

- Select-RAM<sup>TM</sup> memory: on-chip ultra-fast RAM with synchronous write option and dual-port RAM option.

Used in the PCl32 Spartan Interface to implement the FIFO.

- · Individual output enable for each I/O

- · Internal 3-state bus capability

- 8 global low-skew clock or signal distribution networks

- IEEE 1149.1-compatible boundary scan logic support

See Spartan FPGA Data Sheet for more details.

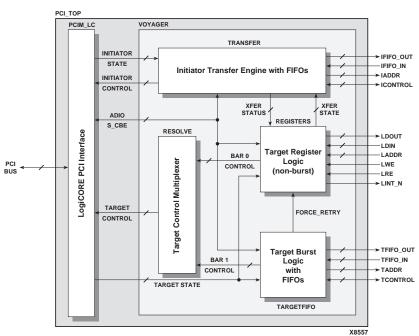

Figure 3: LogiCORE PCI32 Spartan Interface Block Diagram

2 - 8 May, 1998

The module is carefully optimized for best possible performance and utilization in the Spartan FPGA architecture. When implemented in the XCS30, more than 50% of the FPGA's resources remain for integrating a unique back-end interface and other system functions into a fully programmable one-chip solution. When implemented in the XCS40, more than 65% of the FPGA's resources remain for integrating a unique back-end interface and other system functions into a fully programmable one-chip solution.

# **Smart-IP Technology**

Drawing on the architectural advantages of Xilinx FPGAs, new Xilinx Smart-IP technology ensures highest performance, predictability, repeatability, and flexibility in PCI designs. The Smart-IP technology is incorporated in every LogiCORE PCI Core.

Xilinx Smart-IP technology leverages the Xilinx architectural advantages, such as look-up tables (LUTs), distributed RAM, and segmented routing, and floorplanning information, such as logic mapping and relative location constraints. This technology provides the best physical layout, predictability, and performance. Additionally, these predetermined features allow for significantly reduced compile times over competing architectures.

The PCI32 Spartan Interface can parameterized, allowing for design flexibility in which users can create the exact PCI interface needed. PCI Cores made with Smart-IP technology are unique by maintaining their performance and predictability regardless of the device size.

# **Functional Description**

The LogiCORE PCI32 Spartan Interface is partitioned into five major blocks, plus the user application, shown in Figure 1. Each block is described below.

#### PCI I/O Interface Block

The I/O interface block handles the physical connection to the PCI bus including all signaling, input and output synchronization, output three-state controls, and all requestgrant handshaking for bus mastering.

# Parity Generator/Checker

Generates/checks even parity across the AD bus, the CBE lines, and the PAR signal. Reports data parity errors via PERR- and address parity errors via SERR-.

## **Target State Machine**

This block manages control over the PCl32 Spartan Interface for Target functions. The states implemented are a subset of equations defined in "Appendix B" of the PCl

Local Bus Specification. The controller is a high-performance state machine using state-per-bit (one-hot) encoding for maximum performance. State-per-bit encoding has narrower and shallower next-state logic functions that closely match the Xilinx FPGA architecture.

#### Initiator State Machine

This block manages control over the PCl32 Spartan Interface for Initiator functions. The states implemented are a subset of equations defined in "Appendix B" of the PCl Local Bus Specification. The Initiator Control Logic also uses state-per-bit encoding for maximum performance.

## **PCI Configuration Space**

This block provides the first 64 bytes of Type 0, version 2.1, Configuration Space Header (CSH) (see Table 1) to support software-driven "Plug-and Play" initialization and configuration. This includes Command, Status, and two Base Address Registers (BARs). These BARs illustrate how to implement memory- or I/O-mapped address spaces. Each BAR sets the base address for the interface and allows the system software to determine the addressable range required by the interface. Using a combination of Configurable Logic Block (CLB) flip-flops for the read/write registers and CLB look-up tables for the read-only registers results in optimized packing density and layout.

With this release, the hooks for extending configuration space has been built into the backend interface. Setting the CapPtr and bit 15 of the Status Register allows the user to implement functions such as Advanced Configuration and Power Interface (ACPI) in the backend design.

# **User Application with Optional Burst FIFOs**

The LogiCORE PCI32 Spartan Interface provides a simple, general-purpose interface with a 32-bit data path and latched address for de-multiplexing the PCI address/data bus. The general-purpose user interface allows the rest of the device to be used in a wide range of applications.

Typically, the user application contains burst FIFOs to increase PCI system performance (An Application Note is available, please see the *Xilinx Documents* section). An onchip read/write FIFO, built from the on-chip synchronous dual-port RAM (SelectRAM™) available in Spartan devices, supports data transfers in excess of 33 MHz.

Table 1: PCI Configuration Space Header

| 31                             | 16 15                          |                  | 0                  |     |

|--------------------------------|--------------------------------|------------------|--------------------|-----|

| Devi                           | Device ID Vendo                |                  | or ID              | 00h |

| Sta                            | Status Com                     |                  | mand               | 04h |

|                                | Class Code                     |                  | Rev ID             | 08h |

| BIST                           | Header<br>Type                 | Latency<br>Timer | Cache<br>Line Size | 0Ch |

| Base                           | e Address R                    | egister 0 (BA    | AR0)               | 10h |

| Base                           | e Address R                    | egister 1 (BA    | \R1)               | 14h |

| Base                           | e Address R                    | egister 2 (BA    | A <i>R2)</i>       | 18h |

| Base                           | e Address R                    | egister 3 (BA    | A <i>R3)</i>       | 1Ch |

| Base Address Register 4 (BAR5) |                                |                  | 20h                |     |

| Base                           | Base Address Register 5 (BAR5) |                  |                    | 24h |