# **Speedbridge Megafunction**

#### **Solution Brief 13**

### **Target Application:**

Communications

Family: FLEX 10K and FLEX 8000

Vendor:

SIS Microelectronics, Inc.

P.O. Box 1432

1831 Lefthand Circle Suite E

Longmont, CO 80501

Tel.

(303) 776-1667 ext.223

Fax

(303) 776-5947

E-mail

info@sismicro.com

## Features

- Optimized for Altera<sup>®</sup> FLEX<sup>®</sup> 10K and FLEX 8000 device families

- Eliminates development of an asynchronous first-in first-out (FIFO) buffer

- Independently clocked write and read interfaces

- Configurable widths and depths

- Full and empty status flags

# **General Description**

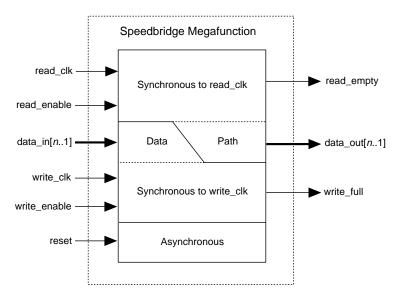

The SIS Microelectronics Speedbridge megafunction is a speed-matching FIFO buffer that can transfer data across an asynchronous interface. In the megafunction, the read and write ports have independent clocks and synchronous enables for accessing their respective functions. These features allow the clocks to run without triggering read or write operations. The Speedbridge megafunction addresses the need for an asynchronous FIFO, which helps to minimize system development and debugging time and to reduce development cost and design risks. Figure 1 shows a block diagram of the Speedbridge megafunction.

# **Functional Description**

The Speedbridge megafunction receives data synchronous with write\_clk and ensures that data\_out[n..1] is synchronous with read\_clk. At a maximum frequency of one write per clock cycle, the megafunction's specified depth will be fully used. However, if the write\_enable input is transferring data at a slower rate than one write per clock cycle, and data is being read at a slower rate, the megafunction will become "full" at one data word less than the specified depth.

January 1997, ver. 1

#### **Altera Corporation**

A-SB-013-01

The megafunction does not contain overflow or underflow flags. However, these flags can be identified outside the megafunction through the write\_full or read\_empty outputs. If write\_full and write\_enable are high, an overflow error will occur on the next write cycle, and the new data on data\_in[n..1] will be lost. If read\_empty and the read\_enable are high, an underflow error will occur on the next read cycle, and the data present on data\_in[n..1] at the time of the underflow will be undefined.

## Ports

Table 1 describes the Speedbridge megafunction's ports.

| Name                 | Туре   | Description                                                                                                                                                                                              |  |

|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| write_clk            | Input  | Clock input. This input can run at any frequency (depending<br>on the range set by the FLEX device architecture),<br>independent from the frequency of the read_clk input.                               |  |

| write_enable         | Input  | This input is synchronous with the write_clk input. When write_enable is high and write_full is low, data is written to the megafunction on the rising edge of write_clk input.                          |  |

| reset                | Input  | Asynchronous power on reset.                                                                                                                                                                             |  |

| data_in[ <i>n</i> 1] | Input  | This data input bus is synchronous with the write_clk input.                                                                                                                                             |  |

| read_enable          | Input  | This input is synchronous with the read_clk input. When read_enable is high and read_empty is low, valid data can be read from the megafunction.                                                         |  |

| read_clk             | Input  | Clock input. This input can run at any frequency (depending<br>on the range set by the FLEX device architecture),<br>independent from the frequency of the write_clk input.                              |  |

| write_full           | Output | This output is synchronous with the write_clk input.<br>When write_full is high, write_enable is ignored,<br>and no additional data is stored until write_full goes<br>low.                              |  |

| data_out[n1]         | Output | This data output bus is synchronous with the read_clk<br>input. Data words will be present for a minimum of one<br>read_clk cycle, plus a minimum output hold time, and<br>minus a maximum output delay. |  |

| read_empty           | Output | This output is synchronous with the read_clk input. When read_empty is high, read_enable is ignored and data should be considered invalid. Once read_empty goes low, data should be considered valid.    |  |

# Utilization

Table 2 lists the typical device utilization for several Speedbridge megafunction sizes. SIS Microelectronics will customize the megafunction's width and depth according to user specifications.

| Table 2. Typical Device Utilization for the Speedbridge Megafunction |                  |  |  |

|----------------------------------------------------------------------|------------------|--|--|

| Depth $	imes$ Width                                                  | Logic Cells Used |  |  |

| 4 bits × 8 words                                                     | 90               |  |  |

| 8 bits × 8 words                                                     | 195              |  |  |

| 16 bits $\times$ 8 words                                             | 389              |  |  |

| 32 bits $\times$ 9 words                                             | 800              |  |  |

# Application

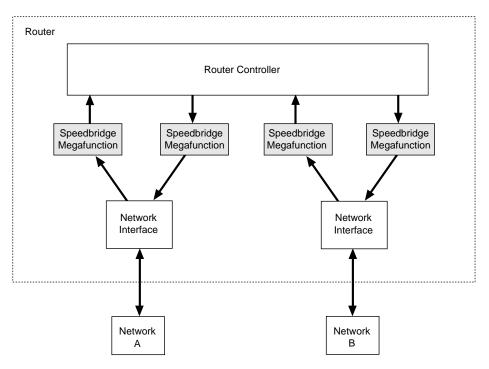

Speedbridge megafunctions can be used in a router controller application that provides a network interface between different networks, each running different protocols with different speed and bandwidth characteristics. Inserting a Speedbridge megafunction between the router controller and each network interface eliminates asynchronous timing problems. The router controller and network interface blocks can be designed as independent synchronous blocks, each with its own clock domain. Figure 2 shows several megafunctions used in a network router application.

#### Figure 2. Speedbridge Megafunctions in a Network Router Application

2610 Orchard Parkway San Jose, CA 95134-2020 (408) 894-7000 http://www.altera.com Copyright © 1997 Altera Corporation. Altera, AMPP, FLEX, FLEX 10K, and FLEX 8000 are trademarks and/or service marks of Altera Corporation in the United States and other countries. Other brands or products are trademarks of their respective holders. The specifications contained herein are subject to change without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. All rights reserved.