# **IDR Deframer Megafunction**

#### **Solution Brief 34**

## **Target Applications:**

Digital Signal Processing (DSP) Digital Video Broadcast (DVB) Satellite Communications

#### Family: FLEX® 10K

Integrated Silicon Systems Ltd. 50 Malone Road Belfast BT9 5BS Northern Ireland Tel. (44) 1232 664 664 Frax (44) 1232 669 664 E-mail support@iss-dsp.com http://www.iss-dsp.com

## Features

- Frame and multi-frame synchronization signals

- Four backward alarm signals

- Single voice channel of 8 Kbits/second

- Two voice channels of 32 Kbits/second

- Compatible with the INTELSAT Earth Station Standard (IESS)-308 specification

# **General Description**

The ISS IDR deframer megafunction is an IESS-308-compatible deframer, capable of extracting overhead data from a composite data stream. It supports the full range of overhead signals, including:

- Frame and multi-frame synchronization

- Four backward alarm signals

- Single data channel of 8 Kbits/second

- Two voice channels of 32 Kbits/second each

The IESS-308 specification details several IDR carrier frequencies; the IDR deframer megafunction supports the carrier frequencies shown below:

- 2.048 Mbits/second

- 8.448 Mbits/second

- 16.896 Mbits/second, *Note* (1)

- 34.368 Mbits/second

#### Note:

Although the 16.896 Mbits/second carrier frequency is not defined by the IESS-308 specification, it is similar to the 34.368 Mbits/second carrier frequency except each sub-frame carries only 176 data bits.

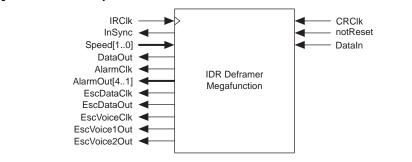

Figure 1 shows the symbol for the IDR deframer megafunction.

#### Figure 1. IDR Deframer Symbol

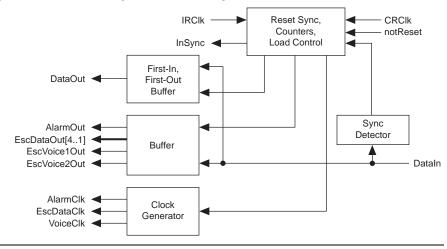

Figure 2 shows the block diagram for the IDR deframer megafunction.

May 1998, ver. 1

Figure 2. IDR Deframer Megafunction Block Diagram

#### **Functional Description**

The IDR deframer megafunction performs engineering service circuit (ESC) channel data, voice, and alarm extraction, together with frame synchronization signal detection. The recovered data streams are buffered and then clocked out at different rates. The megafunction generates clock signals for the slower data rate signals and supports four clock rate combinations. Designers must supply both the input data rate and composite data rate clocks at the exact frequency ratios defined by the IESS-308 specification.

#### Sync Detection

The incoming data stream is sampled a bit at a time over a succession of frames. If a synchronized pattern is not detected at that bit position within 16 frames, a bit is skipped and synchronization detection moves on to the next bit position. Once a valid synchronization is detected, frame data extraction begins on the next superframe. The InSync signal will be asserted when the initial data appears on the DataOut pin. In the absence of transmission bit errors, synchronization will be achieved within a time specified by the following formula.

Synchronization Time = CrClk period  $\times 16 \times (Total Bits Per Frame)^2$

#### First-In, First-Out (FIFO) Buffer

Input data is loaded into an asynchronous FIFO buffer for data rate conversion. Data is not loaded when frame overhead bits are being received. Data bits are extracted from the FIFO buffer at the intermediate rate, and output to the DataOut pin.

#### ESC Data Clocks & Buffers

The composite rate clock, CRClk, derives the clock signals for the ESC voice channels, ESC data channel, and ESC alarm signals. These signals have defined frequencies. Data for the relevant channel is loaded into small buffers on receipt from the composite stream. Data is removed from the buffers a maximum of two frames later, on the rising edge of the relevant clock signal, and driven onto the appropriate output pin.

#### Counters & Buffer Load Control

A number of counters keep track of the frame, subframe, and bit number, and control the input stream disassembly. IESS-308 does not specify a relationship between the content of the data streams and the framing signals. The equipment connected to the data streams must be synchronized to the data carried in those streams.

## Ports

Table 1 describes the ports for the IDR deframer megafunction.

| Name         | Туре   | Description                                                                                                                                                                                                                                                                                                       |  |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CRClk        | Input  | Composite rate clock. This signal drives the bulk of<br>the megafunction activity. The supplied signal must<br>have the exact frequency required by the IESS-308<br>specification in the frame clock section. Output clocks<br>are derived from this input. The required frequency is<br>8.554 MHz or 34.464 MHz. |  |

| notReset     | Input  | Core reset (active low). Initializes the megafunction t<br>a known state. This signal is clocked by IRC1k and<br>requires a 5-ns setup before the clock edge on<br>deassertion to ensure that all signals reset<br>simultaneously.                                                                                |  |

| Speed[10]    | Input  | IDR speed select. This signal is used to inform the megafunction of the IDR clock's speed. This signal should only be changed when the core reset signal is asserted; otherwise, unpredictable results may occur. Table 2 shows the Speed[10] values for each IDR clock speed.                                    |  |

| DataIn       | Input  | Composite data stream input. This signal is latched<br>on the rising edge of CRC1k and requires 15 ns of<br>setup time.                                                                                                                                                                                           |  |

| IRClk        | Input  | Intermediate rate clock. This signal is an input at the IDR frequency (i.e., 8.448 MHz or 34.368 MHz).                                                                                                                                                                                                            |  |

| InSync       | Output | Synchronization achieved. This signal is asserted<br>when the megafunction has detected and locked onto<br>a multiframe synchronization signal in the input<br>composite stream. This signal is clocked out by<br>IRClk and will be valid within 10 ns of the rising edge<br>of the IRClk input.                  |  |

| DataOut      | Output | Main data stream output. This signal is clocked out by<br>IRClk and will be valid within 10 ns of the rising edge<br>of the IRClk input. Main stream data is extracted<br>from the composite stream in accordance with the<br>IESS-308 specification and presented on this output                                 |  |

| AlarmClk     | Output | Main data stream output. This signal has only 50% duty cycle at the alarm clock frequency (1 kHz).                                                                                                                                                                                                                |  |

| AlarmOut[41] | Output | Backward alarm signals. These outputs are updated<br>on the falling edge of the AlarmClk output and are<br>stable around the rising edge of that clock. These<br>signals are extracted from the composite data<br>stream, A1 to A4 bits, as shown in the IESS-308<br>specification.                               |  |

| EscDataClk   | Output | ESC data clock. This signal has 50% duty cycle at the ESC data channel clock frequency (8 kHz).                                                                                                                                                                                                                   |  |

| EscDataOut   | Output | ESC data input. This signal is updated on the falling<br>edge of the EscDataClk output, and is stable<br>around the rising edge of that clock. The signal is<br>extracted from the composite data stream, d1 to d8<br>bits, as shown in the IESS-308 specification.                                               |  |

Table 1. IDR Deframer Megafunction Ports (Part 1 of 2)

| Name         | Туре   | Description                                                                                                                                                                                                                                                               |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EscVoiceClk  | Output | ESC voice clock. This signal has approximately 50% duty cycle at the ESC voice channel clock frequency (32 kHz). It is used for both voice channels.                                                                                                                      |

| EscVoicelOut | Output | ESC voice channel 1 input. This signal is updated on<br>the falling edge of the EscVoiceClk output, and is<br>stable around the rising edge of that clock. The signal<br>is extracted from the composite data stream, P1 bits,<br>as shown in the IESS-308 specification. |

| EscVoice20ut | Output | ESC voice channel 2 input. This signal is updated on<br>the falling edge of the EscVoiceClk signal, and is<br>stable around the rising edge of that clock. The signal<br>is extracted from the composite data stream, P2 bits,<br>as shown in the IESS-308 specification. |

T.L. 1 IND D. ( ....

Table 2 shows the Speed[1..0] values for each IDR clock speed.

| Table 2. Speed[10] Values      |          |          |  |  |  |  |

|--------------------------------|----------|----------|--|--|--|--|

| IDR Clock Speed (Mbits/Second) | Speed[1] | Speed[0] |  |  |  |  |

| 2.048                          | 0        | 0        |  |  |  |  |

| 8.448                          | 0        | 1        |  |  |  |  |

| 16.896                         | 1        | 0        |  |  |  |  |

| 34.368                         | 1        | 1        |  |  |  |  |

### Utilization

Table 3 describes the logic cell requirements for the IDR deframer megafunction.

| Table 3. IDR Deframer Megafunction Logic Cell Requirements |             |             |          |                        |              |  |  |  |

|------------------------------------------------------------|-------------|-------------|----------|------------------------|--------------|--|--|--|

| Device                                                     | Speed Grade | Utilization |          | f <sub>MAX</sub> (MHz) | Availability |  |  |  |

|                                                            |             | Logic Cells | EABs (1) |                        |              |  |  |  |

| EPF10K30A                                                  | -1          | 265         | 0        | 83                     | Now          |  |  |  |

Note:

(1) EABs = embedded array blocks.

## Deliverables

The ISS IDR deframer megafunction includes the following items:

- Encrypted Altera-specific netlist file, deframer.tdf

- Megafunction compilation constraints file, deframer.acf

- Symbol file, deframer.sym, for use in MAX+PLUS® II schematics

- Simulation model for the megafunction, deframer.snf

- Text-only readme file (readme.txt) explaining the function of all four files

Copyright © 1998 Altera Corporation. Altera, MAX, MAX+PLUS, MAX+PLUS II, FLEX, FLEX 10K, EPF10K30A, and AMPP are trademarks and/or service marks of Altera Corporation in the United States and other countries. Other brands or products are trademarks of their respective holders. The specifications contained herein are subject to change without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. All rights reserved.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com