### Newsletter for Altera Customers

# Altera Provides World-Class HDL Synthesis & Simulation Tools

Altera has entered into agreements with Synopsys, Inc., and Mentor Graphics Corporation that enable Altera's entire customer base to access premier programmable logic development tools. Under terms of the agreements, Altera® customers receive a fullfeatured version of either Synopsys' FPGA Express<sup>TM</sup> software or Mentor Graphics' LeonardoSpectrum<sup>TM</sup> software, and Mentor Graphic's ModelSim<sup>TM</sup> simulation software with their Altera software subscriptions. These thirdparty tools are included at no additional charge to the standard software subscription price. Now, Altera customers have access to a leading hardware description language (HDL) simulator and a choice of two performance-enhancing synthesis tools.

These agreements allow Altera to provide all active subscribers with world-class synthesis tools and enhanced behavioral simulation tools, continuing Altera's goal to deliver optimal performance and an enhanced design methodology through third-party software. With the release of the Quartus<sup>TM</sup> development system in 1999, Altera offered NativeLink<sup>TM</sup> functionality to link third-party synthesis and simulation with Quartus fitting and compilation algorithms; this integration provides efficient performance optimization and faster debugging.

Better synthesis directly equates to better performance. Altera designers now have a choice of either Synopsys' FPGA *Express* or Mentor Graphics' LeonardoSpectrum for synthesis. FPGA *Express* is a powerful VHDL and Verilog HDL synthesis tool with a simple, push-button user interface designed for highdensity programmable logic. LeonardoSpectrum combines a push-button interface with the powerful control and optimization features associated with workstation-based ASIC tools.

As designers use programmable logic devices (PLDs) with increasing density, behavioral simulation tools become more important. Altera now provides the ModelSim behavioral simulation tool to complement the existing timing simulation tools in the Quartus and MAX+PLUS® II development systems. Designers can easily adopt a system-on-aprogrammable-chip (SOPC) design methodology using ModelSim features such as behavioral simulation capability, test bench support, and Tcl scripting functionality.

The agreements with Synopsys and Mentor Graphics provide a cost-effective opportunity for Altera customers to use world-class synthesis and simulation tools. These third-party tools are included with each Altera software subscription; designers with current subscriptions will receive these third-party tools with a future Quartus and MAX+PLUS II upgrade. For more information on this offer, or to purchase an Altera software subscription, contact your Altera sales representative. North American customers can also purchase subscriptions from the Programmable eStore on the Altera web site (http://www.altera.com).

Premier Synthesis & Simulation Tools Now Available - FREE!

Quartus

### **Inside This Issue:**

- APEX PLLs Offer Advanced

Clock Synthesis, pg. 17

- Quartus Timing Analysis Verifies Design Performance, pg. 24

- Altera Devices on the Cutting Edge of Medical Technology, pg. 27

# Using Programmable Logic for DSP Solutions Saves Time,

The Altera<sup>®</sup> Finite Impulse Response (FIR) Compiler MegaCore<sup>™</sup> function reduces the design time of your high-performance FIR filters from **six weeks to less than one day**.

This benchmark is for a symmetric FIR filter (50 taps, 8-bit data, 12-bit coefficient resolution) targeting an Altera EP20K100 APEX™ device and a TI TMS320C54x (50 MHz) DSP processor.

### **Reduces Cost,**

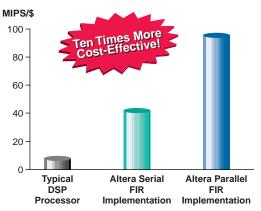

Using the FIR Compiler is ten times more cost-effective than using a standard DSP processor.

### and Makes the Job Easier!

This flexible, easy-to-use graphical compiler allows you to specify the data width, data type, number of taps, and the interpolation or decimation factor you need for your design. It supports third-party system-level DSP tools such as MATLAB or Simulink, and simulation tools such as VHDL and Verilog HDL.

### Test-Drive the Altera FIR Filter Compiler for Free

You can test-drive the Altera FIR Compiler for free by downloading it from the IP MegaStore<sup>™</sup> site at **http://www.altera.com/IPmegastore**. Discover for yourself how easily you can reduce your design time and cut your design costs.

The Programmable Solutions Company™

# Table of Contents

### **Features**

| Altera Provides World-Class HDL Synthesis & |   |

|---------------------------------------------|---|

| Simulation Tools                            | 1 |

| System-on-a-Programmable-Chip               |   |

| Development Board Speeds Verification       | 4 |

| Customer Application: Altera Devices on     |   |

| the Cutting Edge of Medical Technology      | 7 |

|                                             |   |

### Altera News

| Special Software Renewal Promotion            | 19 |

|-----------------------------------------------|----|

| Altera: The DSP Leader for Programmable Logic | 31 |

| Enhanced APEX PLLs Aid in Clock Management    | 33 |

### **Devices & Tools**

| More APEX 20KE Devices Now Available         | 1  |

|----------------------------------------------|----|

| New APEX Family Member                       | 7  |

| 5.0-V Tolerant APEX 20K Devices              | 7  |

| 1,020-Pin FineLine BGA Packages              | 7  |

| APEX 20K Product Transition                  | 8  |

| APEX PLL Offerings                           | 8  |

| Interest Grows for Low-Cost ACEX Family      | 8  |

| FLEX 10KE Devices Available in All Densities | 8  |

| FLEX 10KE Device Offerings                   | 8  |

| FLEX 10K Product Transitions                 | 9  |

| FLEX 10KE Industrial-Temperature Devices     | 9  |

| MAX 7000B Full-Featured Devices              | 10 |

| MAX 7000A Devices Available Now              | 10 |

| MAX 7000S Devices                            | 11 |

|                                              |    |

| Low-Cost MAX 3000A Devices 11                |

|----------------------------------------------|

| 4-Mbit Configuration Device Coming Soon      |

| Quartus Version 2000.02 Improves Design      |

| Performance (f <sub>Max</sub> )12            |

| MAX+PLUS II Version 9.5 Compiles $30 \times$ |

| Faster & Increases Performance 30%           |

| Quartus Operating System Update              |

| E+MAX Provides a Complete Design System for  |

| Product-Term Architecture PLDs               |

| Programmable eStore Provides Immediate       |

| Fulfillment for Existing Customers           |

| Discontinued Devices Update                  |

### **Technical Articles**

| Implementing CAM in an APEX Device          | 14 |

|---------------------------------------------|----|

| APEX PLLs Offer Advanced Clock Synthesis    | 17 |

| Using I/O Standards in the Quartus Software | 20 |

| Quartus Timing Analysis Verifies Design     |    |

| Performance                                 | 24 |

| Questions & Answers                         | 35 |

### In Every Issue

| New Altera Publications       |    |

|-------------------------------|----|

| Current Software Versions     |    |

| Altera Programming Support    |    |

| How to Contact Altera         |    |

| Altera Device Selection Guide | 40 |

Altera, ACCESS, ACEX, ACEX 1K, ACEX 2K, AMPP, APEX, APEX 20K, APEX 20KE, BitBlaster, ByteBlaster, ByteBlaster, V, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, F+MAX, EPC2, FastTrack, FineLine BGA, FLEX, FLEX 10K, FLEX 10KA, FLEX 10K0, FLEX 8000, FLEX 6000, Jam, MasterBlaster, MAX 9000, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000B, MAX 7000A, MAX 7000AE, MAX 7000AB, MAX 3000, MAX 3000A, MAX, MAX+PLUS, MAX+PLUS II, MegaCore, MegaLAB, MegaWizard, MultiCore, MultiVolt, NativeLink, NSTEP, OpenCore, OptiFLEX, Quartus, SignalTap, and specific device designations are trademarks and/or services mentioned in this document, specifically: Adobe and Acrobat are registered trademarks of Adobe Systems Incorporated. BP Microsystems is a registered trademark of BP Microsystems. CTI PET Systems, Inc. is a trademark for CTI, Inc. Data I/O and UniSite are registered trademarks of Data I/O Corporation. HP-VIX is a trademark of Hevlett-Packard Company. Mentor Graphics is a registered trademark and LeonardoSpectrum and ModelSim are trademarks of Mentor Graphics. Microsoft, Windows, Windows 98, and Windows NT are registered trademarks of Microsystems, Inc. Sun is a registered trademark of System General. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products or current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera's standard to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. The actual availability of Altera's products and features could differ from those projected in this publication

Copyright © 2000 Altera Corporation. All rights reserved.

101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 **n\_v@altera.com**

Ken Lau, Publisher

**Technical Editor**

Greg Steinke,

Printed on recycled paper.

# System-on-a-Programmable-Chip Development Board Speeds Verification

The System-on-a-Programmable-Chip Development Board supports many different applications by incorporating PMCs (allowing daughtercard expansion), programmable logic, memory, debug facilities, and several different interface resources. As system-on-a-programmable-chip designs gain broad acceptance, the need for costeffective, efficient design verification and implementation increases. The established methods of software-based simulation and hardware emulation are extremely timeconsuming and pose significant limitations such as high cost and low performance in systemlevel verification. Because of these limitations, designers must find alternative approaches to these verification dilemmas. The most common verification approach is to develop a customprototyping board, which could cost tens of thousands of dollars and take many months to create.

The ideal verification environment can run system software on a hardware platform in real time. Altera's new System-on-a-Programmable-Chip Development Board helps to move products through the design cycle quickly by providing a more effective alternative to the traditional system verification using expensive hardware-emulation systems.

### The Past

Before the System-on-a-Programmable-Chip Development Board, there were only two

approaches for verifying your design before manufacturing: software simulation and hardware emulation. In software simulation, an engineer implements a behavioral model to simulate the hardware. If the simulation reveals a bug, the engineer must correct the behavioral model and resimulate. However. simulation is timeconsuming and lacks the real-world accuracy necessary for comprehensive system verification. Verifying a design in a software

simulator is more time-consuming than running the design in the actual hardware. For example, a complex design may require several days of software simulation to get final results. Even if a design runs in a simulator without errors, it may, in fact, have functional or timing bugs when the real hardware is implemented and presented with unexpected conditions. This process results in another time-consuming design iteration cycle.

The second approach to design verification is hardware emulation. However, significant drawbacks hinder this approach as well. The emulation system is expensive; a box with a capacity of only 500,000 gates can cost as much as \$400,000. A typical emulation box can only run at hundreds-of-kHz speeds—much slower than actual device speeds. Additionally, emulation boxes only provide a hardware model to test your design. You can often encounter additional problems once you implement the design and operate the system software and hardware in a real-time environment.

### The Present

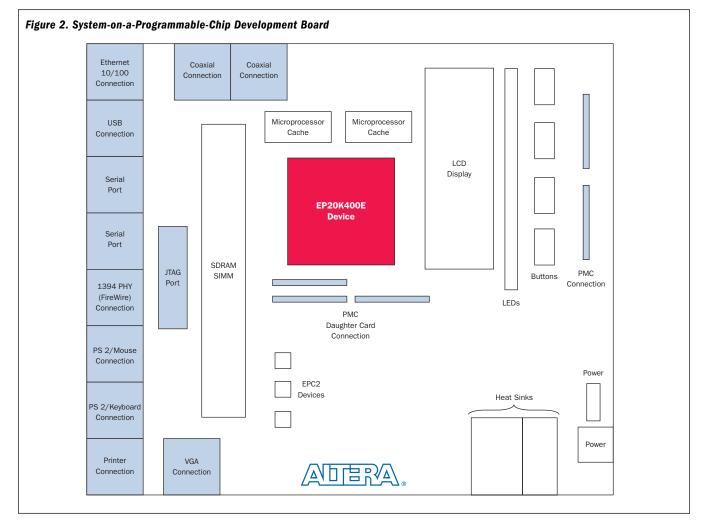

The Altera® System-on-a-Programmable-Chip Development Board offers a more accurate and economical solution to design development and verification. The System-on-a-Programmable-Chip Development Board supports many different applications by incorporating programmable logic, memory, debug facilities, numerous interface resources, and peripheral component interconnect (PCI) mezzanine cards (PMCs) allowing daughter-card expansion. The board is designed to operate at high speeds, providing accurate, real-time testing results that reduce design verification time and increase overall design productivity.

The System-on-a-Programmable-Chip Development Board is designed for the integration and debugging of intellectual property (IP) functions from multiple sources, including Altera MegaCore<sup>TM</sup> functions, Altera Megafunction Partners Program (AMPP<sup>SM</sup>) functions, and custom-designed IP, without the burden of having to develop a custom hardware platform.

The System-on-a-Programmable-Chip Development Board offers unmatched flexibility and user-customization opportunities. The board includes an EP20K400E programmable logic device (PLD) with 16,640 logic elements (LEs) and over 400,000 gates.

The memory subsystem on the board includes:

- Two banks of 1-Mbyte cache memory

- 64-Mbyte SDRAM in a DIMM socket

- 4-Mbyte FLASH memory

- 256-Kbyte EPROM

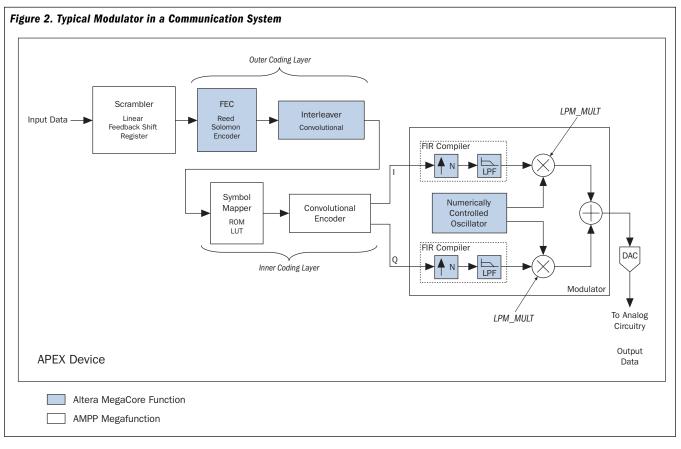

Figure 2 on page 6 shows a diagram of the System-on-a-Programmable-Chip Development Board.

To accommodate a wide variety of embedded applications, the board provides a robust set of I/O standards, such as IEEE Std. 1394a, IEEE Std. 1284, RS-232 DTE, 10/100 fast ethernet, and universal serial bus (USB) host. These standards allow design engineers to select the appropriate resources required to verify their application-specific IP. Additionally, the board features many debugging capabilities, including extended Joint Test Action Group (EJTAG), IEEE Std. 1149.1 JTAG, USB, and parallel port connections for accessing the on-board PLD. The APEX<sup>™</sup> EP20K400E device included with the board supports in-circuit reconfigurability (ICR) through the MasterBlaster<sup>TM</sup> communications cable (included with the board) or EPC2 configuration devices, allowing you to repeatedly modify and verify your design.

With all of the resources on the System-on-a-Programmable-Chip Development Board, you

continued on page 6

### *System-on-a-Programmable-Chip Development Board Speeds Verification, continued from page 5*

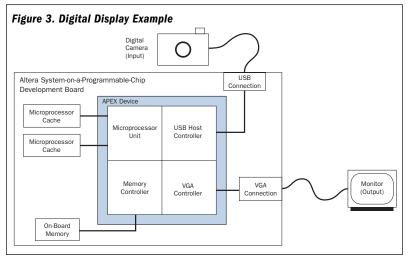

can implement a limitless number of designs. For example, by connecting a digital camera to the USB port and a VGA monitor to the VGA port, you have a digital display (see Figure 3). To utilize these I/O ports, you could implement a USB host controller, a processor, and a VGA controller within the EP20K400E device. A memory controller is also necessary to store the images in the SDRAM memory included on the board.

The speed of the APEX device is sufficient for the USB host controller (~48 MHz) and the processor function (~33 MHz). The approximate LE consumption for the necessary functions is shown in Table 1. The total LE consumption is approximately 9,300, which is far less than the 16,640 LEs available on the APEX device.

| Table 1. Approximate APEX LE Consumption |                               |                   |  |

|------------------------------------------|-------------------------------|-------------------|--|

| Core                                     | Approximate<br>LE Consumption | % of<br>Total LEs |  |

| Microprocessor                           | 4,000                         | 24                |  |

| USB Host Controller                      | 3,000                         | 18                |  |

| Memory Controller                        | 2,000                         | 12                |  |

| VGA Controller                           | 300                           | 2                 |  |

| Total                                    | 9,300                         | 56                |  |

With the complexity of larger designs, engineers need a way to view specific test points of their design within the device. Using the SignalTap<sup>TM</sup> embedded logic analyzer, a feature of the Quartus<sup>TM</sup> development system, an engineer can closely examine signals from internal nodes within the APEX device. The SignalTap logic analyzer is especially useful for today's ball-grid array (BGA) packages where pin access is limited by the package design. The SignalTap user decides how many internal signals to view and can filter out extraneous information to view only problematic circuitry.

The APEX device also supports many Altera MegaCore functions and AMPP megafunctions. You can use these off-the-shelf megafunctions together with the System-on-a-Programmable-Chip Development Board to bring your product to market quickly. OpenCore<sup>TM</sup> versions of MegaCore functions and AMPP megafunctions are available for testing.

### The Future

As costs decrease and PLD speeds and density increase, many new applications will abandon ASICs and adopt programmable logic. The System-on-a-Programmable-Chip Development Board is designed to accommodate these trends through its capability to be upgraded to higher density APEX devices in the same 652-pin BGA package, including EP20K1500E devices with over 50,000 LEs.

Altera and AMPP partners are designing daughter cards for the board's PMC slots. These daughter cards will supplement the board by increasing its functionality and memory capacity. For example, if your application needs analog capability for a digital signal processing (DSP)-based system, you could easily add this functionality to the System-on-a-Programmable-Chip Development Board via an analog PMC daughter card. For microprocessor designs, the CPU could be included in the system, implemented in the form of an IP function ported to the PLD, or implemented as a PMC processor card.

Altera created the System-on-a-Programmable-Chip Development Board with the flexibility to accommodate a multitude of designs for many application areas. With the board's high-density programmable logic, breadth of I/O standards, and available on-board memory, the System-ona-Programmable-Chip Development Board is a productive and cost-effective way to develop, integrate, and verify your complex system-on-aprogrammable-chip designs.

### APEX

### More APEX 20KE Devices Now Available

New APEX<sup>TM</sup> 20KE package and speed grade offerings for EP20K100E, EP20K200E, EP20K400E, and EP20K600E devices are now available. The EP20K400E and EP20K600E devices include embedded circuitry supporting multiple low-voltage differential signaling (LVDS) channels with bandwidth of up to 622 megabits per second (Mbps) each. The remaining APEX 20KE devices are scheduled to ship soon. Software support is currently available for EP20K60E, EP20K100E, EP20K200E, EP20K300E, EP20K400E, EP20K600E, and EP20K1000E devices in the Quartus<sup>TM</sup> software version 2000.02 (see Table 1).

### **New APEX Family Member**

Altera has added a new, low-cost, highperformance APEX 20KE device. The 30,000-gate EP20K30E device contains 1,200 logic elements (LEs) and 24,576 bits of on-chip RAM. Quartus software support will be available in the second quarter of 2000.

### 5.0-V Tolerant APEX 20K Devices

The APEX 20K device family has been enhanced to provide 5.0-V tolerant I/O buffers, allowing full compliance with the 5.0-V peripheral component interconnect (PCI) specification. These devices will begin shipping in March 2000.

### 1,020-Pin FineLine BGA Packages

EP20K600E, EP20K1000E, and EP20K1500E devices will be available in a 1,020-pin FineLine BGA<sup>TM</sup> package, providing up to 808 I/O pins. These devices will use an FC33 designation in the ordering code, which is based on the 33-mm body size rather than the 1,020 pin count. For example, the ordering code for an EP20K1000E device with phase-locked loop (PLL) circuitry in this package is EP20K1000EFC33-1X.

# Table 1. APEX 20KE Device & Quartus SoftwareSupport Availability

| Device      | Package                | Software<br>Support<br>Availability |  |

|-------------|------------------------|-------------------------------------|--|

| EP20K30E    | 144-pin TQFP           | Q2 2000                             |  |

|             | 144-pin FineLine BGA   | Q2 2000                             |  |

|             | 208-pin PQFP           | Q2 2000                             |  |

|             | 324-pin FineLine BGA   | Q2 2000                             |  |

| EP20K60E    | 144-pin TQFP (1)       | Now                                 |  |

|             | 144-pin FineLine BGA   | March 2000                          |  |

|             | 208-pin PQFP (1)       | Now                                 |  |

|             | 240-pin PQFP           | Now                                 |  |

|             | 324-pin FineLine BGA   | Now                                 |  |

|             | 356-pin BGA (1)        | Now                                 |  |

| EP20K100E   | 144-pin TQFP           | Now                                 |  |

|             | 144-pin FineLine BGA   | March 2000                          |  |

|             | 208-pin PQFP           | Now                                 |  |

|             | 240-pin PQFP           | Now                                 |  |

|             | 324-pin FineLine BGA   | Now                                 |  |

|             | 356-pin BGA            | Now                                 |  |

| EP20K160E   | 144-pin TQFP           | March 2000                          |  |

| 21 20112002 | 208-pin PQFP           | March 2000                          |  |

|             | 240-pin PQFP           | March 2000                          |  |

|             | 356-pin BGA            | March 2000                          |  |

|             | 484-pin FineLine BGA   | March 2000                          |  |

| EP20K200E   | 208-pin PQFP           | Now                                 |  |

| 2012002     | 240-pin PQFP           | Now                                 |  |

|             | 356-pin BGA            | Now                                 |  |

|             | 484-pin FineLine BGA   | Now                                 |  |

|             | 652-pin BGA            | Now                                 |  |

|             | 672-pin FineLine BGA   | Now                                 |  |

| EP20K300E   | 240-pin RQFP (1)       | Now                                 |  |

| LI ZUNJUUL  | 652-pin BGA            | Now                                 |  |

|             | 672-pin FineLine BGA   | Now                                 |  |

| EDOOK 400E  |                        |                                     |  |

| EP20K400E   | 652-pin BGA            | Now                                 |  |

|             | 672-pin FineLine BGA   | Now                                 |  |

| EP20K600E   | 652-pin BGA            | Now                                 |  |

|             | 672-pin FineLine BGA   | Now                                 |  |

|             | 1,020-pin FineLine BGA | Now                                 |  |

| EP20K1000E  | 652-pin BGA            | Now                                 |  |

|             | 672-pin FineLine BGA   | Now                                 |  |

|             | 984-pin PGA (1)        | Q2 2000                             |  |

|             | 1,020-pin FineLine BGA | Now                                 |  |

| EP20K1500E  | 652-pin BGA            | Q2 2000                             |  |

|             | 984-pin PGA            | Q2 2000                             |  |

|             | 1,020-pin FineLine BGA | Q2 2000                             |  |

Note:

(1) TQFP: thin quad flat pack, PQFP: plastic quad flat pack, BGA: ball-grid array, RQFP: power quad flat pack, PGA: pin-grid array.

Devices & Tools, continued from page 7

### **APEX 20K Product Transition**

Altera is migrating the 2.5-V EP20K400 device from a 0.25-µm process to a 0.22-µm process. Information regarding this device migration can be found in PCN 0005, available on the Altera<sup>®</sup> web site at http://www.altera.com.

### **APEX PLL Offerings**

APEX devices with PLL circuitry are now shipping. These devices are identified with an "X" suffix in the ordering code (i.e., EP20K400EBC652-1X). The PLL feature is offered in all APEX device densities in both -1 and -2 speed grades. APEX PLLs contain enhanced ClockLock<sup>™</sup> circuitry for skew reduction, ClockBoost<sup>™</sup> circuitry for flexible rate multiplication and division, and ClockShift<sup>™</sup> circuitry for phase-shift and delay capability. Additionally, you can use APEX 20KE PLLs for LVDS I/O interfaces to support high-speed data transfer rates and to convert LVDS and CMOS data.

### ACEX

**Interest Grows for Low-Cost ACEX Family**

The new low-cost ACEX<sup>TM</sup> family has been expanded to include both 1.8-V and 2.5-V devices. These devices are designed for highvolume, price-sensitive communications and computing market applications, including cable and xDSL modems, switches, and routers. ACEX devices are also used in remote-access concentrators, where high-volume production creates a strong sensitivity to cost-per-function, and complex communications processes require high performance capability and support for advanced features. ACEX devices meet these needs head-on with a low-cost, mid-rangedensity programmable solution.

The 2.5-V ACEX 1K offerings will be supported in the MAX+PLUS<sup>®</sup> II software version 9.51. These offerings will have devices ranging from 10,000 to 100,000 typical gates and have embedded memory for dual-port RAM, PLL support for clock management capabilities, and 64-bit, 66-MHz PCI compliance. ACEX 1K devices will be available in quad flat pack (QFP) and FineLine BGA packages.

Altera will also introduce 1.8-V ACEX 2K devices later this year. These devices combine the functionality of embedded memory with support for a large number of embedded RAM blocks. Support for a wide range of specialized I/O standards is also included in ACEX 2K devices. These advanced I/O standards provide high-speed board-level communication. Additionally, an embedded PLL includes ClockShift circuitry and can use a wide range of multiplication factors to drive two separate ClockLock- and ClockBoost-generated signals. Altera will offer ACEX 2K devices in QFP and FineLine BGA packages.

Quartus software support for ACEX 2K devices is scheduled to be available in the third quarter of 2000. For the latest information on ACEX devices, visit the Altera web site at http://www.altera.com.

### FLEX

### FLEX 10KE Devices Available in All Densities

FLEX® 10KE devices are now available in all densities. All EPF10K30E, EPF10K50S, EPF10K100E, EPF10K130E, and EPF10K200S devices are fabricated on 0.22-µm die sizes. These devices, in all packages, are shipping in the -1, -2, and -3 speed grades and have a programmable delay to provide full 64-bit, 66-MHz PCI compliance.

### **FLEX 10KE Device Offerings**

FLEX 10KE devices provide high-speed and high-density solutions for efficient designs. FLEX 10KE devices are offered with the PLL feature in -1 and -2 speed grades to reduce clock skew and allow clock multiplication. These devices have an "X" suffix in the ordering code (e.g., EPF10K100EQC208-1X). To assist designers in implementing their projects in FLEX 10KE devices, the MAX+PLUS II software offers design support for all device package options. Table 3 shows all of the 2.5-V FLEX 10KE device packages and speed grades.

The new low-cost ACEX family has been expanded to include both 1.8-V and 2.5-V devices. These devices are designed for highvolume, price-sensitive communications and computing market applications.

| Table 3. FLEX 10KE Devices |                      |                |  |

|----------------------------|----------------------|----------------|--|

| Device                     | Offerings            | Speed<br>Grade |  |

| EPF10K30E                  | 144-pin TQFP         | -1, -2, -3     |  |

|                            | 208-pin PQFP         | -1, -2, -3     |  |

|                            | 256-pin FineLine BGA | -1, -2, -3     |  |

|                            | 484-pin FineLine BGA | -1, -2, -3     |  |

|                            | PLL (all packages)   | -1X, -2X       |  |

| EPF10K50S                  | 144-pin TQFP         | -1, -2, -3     |  |

|                            | 208-pin PQFP         | -1, -2, -3     |  |

|                            | 240-pin PQFP         | -1, -2, -3     |  |

|                            | 256-pin FineLine BGA | -1, -2, -3     |  |

|                            | 356-pin BGA          | -1, -2, -3     |  |

|                            | 484-pin FineLine BGA | -1, -2, -3     |  |

|                            | PLL (all packages)   | -1X, -2X       |  |

| EPF10K100E                 | 208-pin PQFP         | -1, -2, -3     |  |

|                            | 240-pin PQFP         | -1, -2, -3     |  |

|                            | 256-pin FineLine BGA | -1, -2, -3     |  |

|                            | 356-pin BGA          | -1, -2, -3     |  |

|                            | 484-pin FineLine BGA | -1, -2, -3     |  |

|                            | PLL (all packages)   | -1X, -2X       |  |

| EPF10K130E                 | 240-pin PQFP         | -1, -2, -3     |  |

|                            | 356-pin BGA          | -1, -2, -3     |  |

|                            | 484-pin FineLine BGA | -1, -2, -3     |  |

|                            | 600-pin BGA          | -1, -2, -3     |  |

|                            | 672-pin FineLine BGA | -1, -2, -3     |  |

|                            | PLL (all packages)   | -1X, -2X       |  |

| EPF10K200S                 | 240-pin RQFP         | -1, -2, -3     |  |

|                            | 356-pin BGA          | -1, -2, -3     |  |

|                            | 484-pin FineLine BGA | -1, -2, -3     |  |

|                            | 600-pin BGA          | -1, -2, -3     |  |

|                            | 672-pin FineLine BGA | -1, -2, -3     |  |

|                            | PLL (all packages)   | -1X, -2X       |  |

### this migration. You can download these documents from the Customer Notifications page on the Altera web site at http://www.altera.com.

| Table 4. FLEX 10K Device Migration |                        |              |                      |                 |

|------------------------------------|------------------------|--------------|----------------------|-----------------|

| Device                             | Core<br>Voltage<br>(V) | Date         | Reference            | Process<br>(µm) |

| EPF10K10A                          | 3.3                    | Done         | PCN 9810             | 0.30            |

| EPF10K30A                          | 3.3                    | Done         | PCN 9810             | 0.30            |

| EPF10K50V                          | 3.3                    | Done         | PCN 9810             | 0.30 (1)        |

|                                    |                        | June<br>2000 | PCN 9915             | 0.30 (2)        |

| EPF10K100A                         | 3.3                    | Done         | PCN 9810             | 0.30            |

| EPF10K10                           | 5.0                    | Done         | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K20                           | 5.0                    | Done         | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K30                           | 5.0                    | Done         | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K50                           | 5.0                    | Done         | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K50E                          | 2.5                    | Feb.<br>2000 | PCN 9911             | 0.22            |

| EPF10K200E                         | 2.5                    | Mar.<br>2000 | PCN 9911             | 0.22            |

FLEX 10KE devices provide high-speed and high-density solutions for efficient designs.

٦

### Notes:

(1) 3-layer metal process.

(2) 4-layer metal process.

### **FLEX 10KE Industrial-Temperature Devices**

EPF10K30EQI208-2, EPF10K30EFI256-2, EPF10K50SQI208-2, and EPF10K200SFI672-2 devices are now available. Additional EPF10K50S and EPF10K200S industrialtemperature grade devices are scheduled to ship soon. Table 5 on page 10 lists the availability of industrial-temperature FLEX 10KE devices.

continued on page 10

### **FLEX 10K Product Transitions**

Altera is migrating 2.5-V EPF10K50E and EPF10K200E devices from a 0.25- $\mu$ m process to a 0.22- $\mu$ m process, and EPF10K50V devices from a 0.30- $\mu$ m, 3-layer-metal process to a 0.30- $\mu$ m, 4-layer-metal process. All other members of the FLEX 10KE family are already manufactured on a 0.22- $\mu$ m process. Table 4 outlines the process migration schedule and lists the reference documentation associated with

| Device            | Availability |

|-------------------|--------------|

| EPF10K30EQI208-2  | Now          |

| EPF10K30EFI256-2  | Now          |

| EPF10K50ETI144-2  | Now          |

| EPF10K50EQI240-2  | Now          |

| EPF10K50EFI256-2  | Now          |

| EPF10K50SQI208-2  | Now          |

| EPF10K50SBI356-2  | April 2000   |

| EPF10K50SFI484-2  | April 2000   |

| EPF10K100EQI208-2 | Now          |

| EPF10K100EFI256-2 | Now          |

| EPF10K100EFI484-2 | Now          |

| EPF10K130EQI240-2 | Now          |

| EPF10K130EBI356-2 | Now          |

| EPF10K130EFI484-2 | Now          |

| EPF10K200EBI600-2 | Now          |

| EPF10K200SRI240-2 | April 2000   |

| EPF10K200SBI356-2 | March 200    |

| EPF10K200SFI672-2 | Now          |

Devices & Tools, continued from page 9

#### Device Package **Speed Grade** EPM7032B 44-pin PLCC (1) -3, -5, -7 44-pin TQFP -3, -5, -7 48-pin TQFP -3, -5, -7 EPM7064B 44-pin PLCC -3, -5, -7 -3, -5, -7 44-pin TOFP 48-pin TQFP -3, -5, -7 49-pin Ultra -3, -5, -7 FineLine BGA (2) 100-pin TQFP -3, -5, -7 100-pin FineLine BGA -3, -5, -7 EPM7128B 49-pin Ultra -4, -7, -10 FineLine BGA 100-pin TQFP -4, -7, -10 -4, -7, -10 100-pin FineLine BGA 144-pin TQFP -4, -7, -10 169-pin Ultra -4, -7, -10 Finel ine BGA 256-pin FineLine BGA -4, -7, -10 EPM7256B -5, -7, -10 100-pin TQFP -5. -7. -10 144-pin TQFP -5, -7, -10 169-pin Ultra FineLine BGA 208-pin PQFP -5, -7, -10 256-pin FineLine BGA -5, -7, -10 EPM7512B 100-pin TQFP -6, -7, -10 144-pin TQFP -6, -7, -10 169-pin Ultra -6, -7, -10 FineLine BGA 208-pin PQFP -6, -7, -10 256-pin BGA -6, -7, -10 256-pin FineLine BGA -6, -7, -10

Table 6. MAX 7000B Commercial-Temperature

**Devices**

## MAX

### **MAX 7000B Full-Featured Devices**

2.5-V MAX<sup>®</sup> 7000B devices range from 32 to 512 macrocells with propagation delays as fast as 3.5 ns. MAX 7000B devices support advanced I/O standards such as Gunning transceiver logic plus (GTL+), stub-series terminated logic for 2.5 V (SSTL-2), and 3.3-V SSTL-3. These devices also feature enhanced in-system programmability (ISP), MultiVolt<sup>™</sup> I/O pins, hot-socketing capability, and pin compatibility with industry-standard MAX 7000 devices. Table 6 shows all MAX 7000B commercial package and speed grade options.

### MAX 7000A Devices Available Now

All MAX 7000A devices are now available. 3.3-V MAX 7000A devices range from 32 to 512 macrocells with propagation delays as fast as 4.5 ns. MAX 7000A devices support enhanced ISP, MultiVolt I/O pins, hot-socketing

### Notes:

(1) PLCC: plastic J-lead chip carrier.

Ultra FineLine BGA packages are Altera's newest 0.8-mm BGA packages.

capability, and pin compatibility with the industry-standard MAX 7000 devices. All MAX 7000A devices are available in industrialtemperature grades. Table 7 shows MAX 7000A device commercial package and speed grade options.

### MAX 7000S Devices

All MAX 7000S devices are now available. 5.0-V MAX 7000S devices offer features such as 5.0-ns speed grades, ISP, an open-drain output option, and IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry in devices with 128 or more macrocells. All MAX 7000S devices are available in industrial-

MAX 7000B devices support advanced I/O standards such as GTL+, SSTL-2, and SSTL-3.

МАХ

temperature grades. Table 8 shows the packages and speed grades available in the commercialtemperature grade.

Table 7. MAX 7000AE Commercial-Temperature

| Devices   |                      |              |

|-----------|----------------------|--------------|

| Device    | Package              | Speed Grade  |

| EPM7032AE | 44-pin PLCC          | -4, -7, -10  |

|           | 44-pin TQFP          | -4, -7, -10  |

| EPM7064AE | 44-pin PLCC          | -4, -7, -10  |

|           | 44-pin TQFP          | -4, -7, -10  |

|           | 49-pin Ultra         | -4, -7, -10  |

|           | FineLine BGA (1)     |              |

|           | 100-pin TQFP         | -4, -7, -10  |

|           | 100-pin FineLine BGA | -4, -7, -10  |

| EPM7128AE | 84-pin PLCC          | -5, -7, -10  |

|           | 100-pin TQFP         | -5, -7, -10  |

|           | 100-pin PQFP         | -5, -7, -10  |

|           | 144-pin TQFP         | -5, -7, -10  |

|           | 169-pin Ultra        | -5, -7, -10  |

|           | FineLine BGA         |              |

|           | 256-pin FineLine BGA | -5, -7, -10  |

| EPM7256AE | 100-pin TQFP         | -5, -7, -10  |

|           | 100-pin FineLine BGA | -5, -7, -10  |

|           | 144-pin TQFP         | -5, -7, -10  |

|           | 208-pin PQFP         | -5, -7, -10  |

|           | 256-pin FineLine BGA | -5, -7, -10  |

| EPM7512AE | 144-pin TQFP         | -7, -10, -12 |

|           | 208-pin PQFP         | -7, -10, -12 |

|           | 256-pin BGA          | -7, -10, -12 |

|           | 256-pin FineLine BGA | -7, -10, -12 |

Note:

Devices

Table 8. Commercial-Temperature MAX 7000S

| Devices  |              |                  |

|----------|--------------|------------------|

| Device   | Package      | Speed Grade      |

| EPM7032S | 44-pin PLCC  | -5, -6, -7, -10  |

|          | 44-pin TQFP  | -5, -6, -7, -10  |

| EPM7064S | 44-pin PLCC  | -5, -6, -7, -10  |

|          | 44-pin TQFP  | -5, -6, -7, -10  |

|          | 84-pin PLCC  | -5, -6, -7, -10  |

|          | 100-pin TQFP | -5, -6, -7, -10  |

| EPM7128S | 84-pin PLCC  | -6, -7, -10, -15 |

|          | 100-pin TQFP | -6, -7, -10, -15 |

|          | 100-pin PQFP | -6, -7, -10, -15 |

|          | 160-pin PQFP | -6, -7, -10, -15 |

| EPM7160S | 84-pin PLCC  | -6, -7, -10      |

|          | 100-pin TQFP | -6, -7, -10      |

|          | 160-pin PQFP | -6, -7, -10      |

| EPM7192S | 160-pin PQFP | -7, -10, -15     |

| EPM7256S | 208-pin PQFP | -7, -10, -15     |

### Low-Cost MAX 3000A Devices

3.3-V MAX 3000A devices are product-termbased programmable logic devices (PLDs) targeted for high-volume, low-cost designs. These devices have an enhanced ISP feature set and range in density from 32 to 256 macrocells (see Table 9). With propagation delays as fast as 4.5 ns, MAX 3000A devices provide exceptional performance at the lowest price per macrocell among Altera MAX devices.

| Table 9. MAX 3000A Devices |              |             |  |  |  |  |

|----------------------------|--------------|-------------|--|--|--|--|

| Device                     | Package      | Speed Grade |  |  |  |  |

| EPM3032A                   | 44-pin PLCC  | -4, -7, -10 |  |  |  |  |

|                            | 44-pin TQFP  | -4, -7, -10 |  |  |  |  |

| EPM3064A                   | 44-pin PLCC  | -4, -7, -10 |  |  |  |  |

|                            | 44-pin TQFP  | -4, -7, -10 |  |  |  |  |

|                            | 100-pin TQFP | -4, -7, -10 |  |  |  |  |

| EPM3128A                   | 100-pin TQFP | -5, -7, -10 |  |  |  |  |

|                            | 144-pin PQFP | -5, -7, -10 |  |  |  |  |

| EPM3256A                   | 144-pin TQFP | -5, -7, -10 |  |  |  |  |

|                            | 208-pin PQFP | -5, -7, -10 |  |  |  |  |

With propagation delays as fast as 4.5 ns, MAX 3000A devices provide exceptional performance at the lowest price per macrocell among Altera MAX devices.

## CONFIGURATION

### 4-Mbit Configuration Device Coming Soon

The new 4-Mbit EPC4E configuration device is scheduled for release in May 2000. This device will be offered in a 44-pin TQFP package as well as a 0.8-mm, 84-pin Ultra FineLine BGA package. A new 9-Mbit EPC9E configuration device is also being developed and is slated for release in the third quarter of 2000. A single EPC4E device will configure a 400,000-gate EP20K400E device, and a single EPC9E device will configure a 1-million-gate EP20K1000E device.

These new devices will include features such as faster configuration times and parallel configuration, and intellectual property (IP) security. Additionally, you can use a single device to configure several FLEX or APEX devices for higher board space efficiency.

continued on page 12

<sup>(1)</sup> Ultra FineLine BGA packages are Altera's newest 0.8-mm BGA packages.

Devices & Tools, continued from page 11

### TOOLS

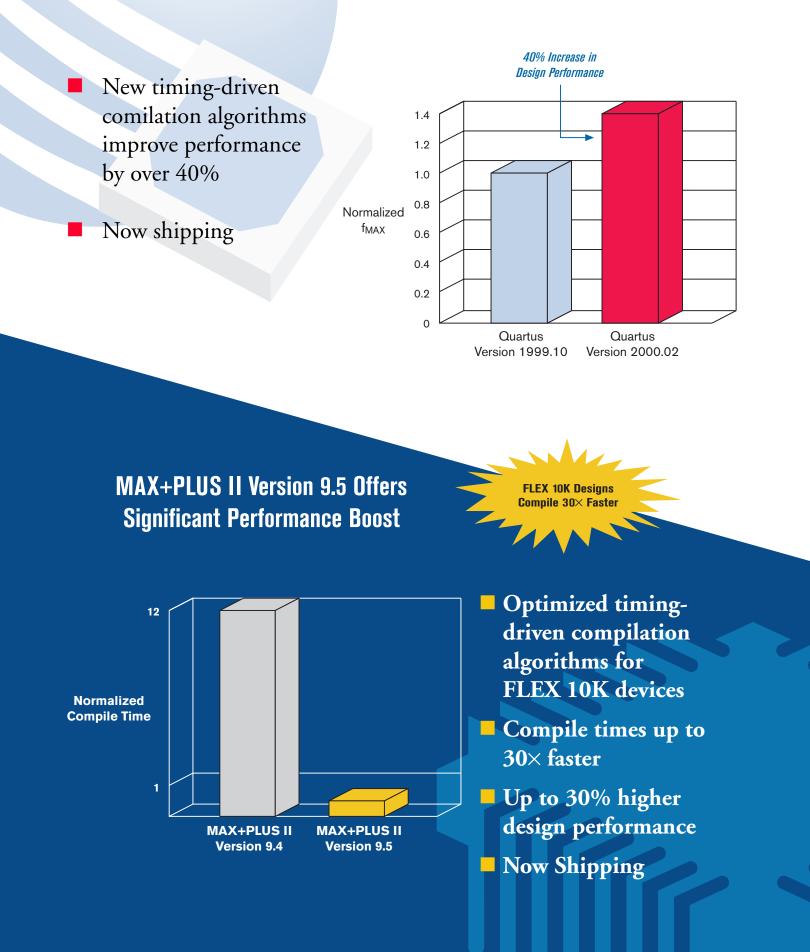

# Quartus Version 2000.02 Improves Design Performance ( $f_{MAX}$ )

The Quartus software version 2000.02 is available to all Altera customers with a current subscription. This latest version of the Quartus software features significant timing-driven compilation (TDC) enhancements as well as new device support.

The optimized compilation algorithms in the Quartus software version 2000.02 improve design performance ( $f_{MAX}$ ) by over 40% for designs targeting high-density APEX 20KE devices (i.e., EP20K400 devices and higher).

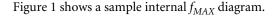

Version 2000.02 allows designers to separately specify timing constraints for both I/O pins and for internal (core) logic, as shown in Figure 1.

### Figure 1. Setting Timing in Quartus

### I/O Timing

Designers can now set  $t_{SU}$  and  $t_{CO}$  assignments, which forces the Quartus Compiler to implement input and output registers respectively in the I/O cells to meet the timing requirements. These settings optimize the overall system performance.

### Internal Timing

Internal (core) timing optimization takes into account the user settings, including inverted

clocks and relationships between different clocks. There are two settings for internal timing optimization: **Normal compilation** and **Extra effort**. The default setting is normal.

In addition to the devices supported by the Quartus software version 1999.10, the Quartus software version 2000.02 supports the APEX 20K devices listed in Table 10.

#### Table 10. New Devices Supported by Quartus 2000.02 Support Device Package EP20K200 Full 240-pin RQFP (1) Compilation, EP20K400 652-pin BGA (2) Simulation, EP20K400E 672-pin FineLine BGA (1) and Programming Support Compilation, EP20K100 144-pin TQFP (1), 208-pin Simulation. PQFP (1), 240-pin PQFP (1), and Pinout 324-pin FineLine BGA (1), Support Only 356-pin BGA (1) EP20K200 208-pin RQFP (1), 356-pin BGA (1), 484-pin FineLine BGA (1), 652-pin BGA (1), 672-pin FineLine BGA (1) EP20K300E 652-pin BGA (1), 672-pin FineLine BGA (1) Compilation EP20K60E 144-pin TQFP, 208-pin and Simulation (3) PQFP, 240-pin PQFP, 324-pin FineLine BGA, Support Only 356-pin BGA

Notes:

- (1) These devices contain PLLs.

- (2) -2 speed-grade devices in industrial-temperature grades only.

- (3) The Quartus software version 2000.02 supports EP20K60E devices with and without PLLs.

### MAX+PLUS II Version 9.5 Compiles 30× Faster & Increases Design Performance 30%

The MAX+PLUS II software version 9.5 features an enhanced compilation engine optimized for the FLEX 10K device family. The new compilation engine dramatically speeds up TDC times for FLEX 10K-based designs. The compile time improvement depends on both design density and device utilization. In general, highdensity designs with a high degree of device utilization show the most significant improvement in timing-driven compilation times.

The optimized compilation algorithms in the Quartus software version 2000.02 improve design performance  $(f_{MAX})$  by over 40% for designs targeting high-density APEX 20KE devices. High-density FLEX 10K designs compile up to 30× faster in the MAX+PLUS II software version 9.5 when compared to version 9.4. To put this in perspective, a high-density design with high device utilization which would have run overnight with the MAX+PLUS II software version 9.4 should now compile in under 30 minutes with version 9.5.

MAX+PLUS II version 9.5 also enhances the design performance for FLEX 10K designs. Customers should expect  $f_{MAX}$  to increase by up to 30%. Design performance improvement is also design-dependent and, in general, a higher degree of improvement can be expected for high-density designs. The same design targeting the same speed-grade device will achieve 30% faster f<sub>MAX</sub> by utilizing advanced compilation algorithms.

The EPF10K30E and EPF10K50S timing models in MAX+PLUS II version 9.5 have been updated to reflect a performance increase indicated by the latest characterization results. The new register-to-register delays  $(t_{DRR})$  are compared to the old t<sub>DRR</sub> numbers in Table 11.

|                | Table 11. Increased EPF10K30E & EPF10K50SPerformance in MAX+PLUS II Version 9.5 |                                      |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|--|

| Speed<br>Grade | Version 9.5<br>t <sub>DRR</sub> (ns)                                            | Version 9.4<br>t <sub>DRR</sub> (ns) |  |  |  |  |  |

| -1             | 8.0                                                                             | 8.5                                  |  |  |  |  |  |

| -2             | 9.5                                                                             | 10.0                                 |  |  |  |  |  |

| -3             | 12.5                                                                            | 13.5                                 |  |  |  |  |  |

### **Quartus Operating System Update**

The Quartus software now supports the operating systems listed in Table 12. Support for the Windows 2000 and the HP-UX 11.0 operating systems is scheduled to be added later this year.

| Table 12. Quartus Operating System Support |                          |  |  |  |

|--------------------------------------------|--------------------------|--|--|--|

| Platform                                   | <b>Operating System</b>  |  |  |  |

| PC                                         | Windows 98, Windows NT   |  |  |  |

| UNIX                                       | Solaris 2.6, HP-UX 10.20 |  |  |  |

### E+MAX Provides a Complete Design System for Product-Term Architecture PLDs

The E+MAX software is a full-featured development system optimized for Altera's popular product-term architectures, including all MAX 7000 and MAX 3000 devices. The E+MAX software includes hardware description language (HDL) synthesis. Designers targeting product-term architectures now have a powerful tool that they can download for free from the Altera web site (http://www.altera.com). Table 13 lists the E+MAX features:

| Table 13. E+MAX Software Features |                                                                                                      |  |  |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| Feature                           | Details                                                                                              |  |  |  |  |

| Design Entry                      | Schematic capture                                                                                    |  |  |  |  |

|                                   | VHDL, Verilog HDL, and AHDL synthesis                                                                |  |  |  |  |

| Device<br>Support                 | MAX 7000 family (including MAX 7000A,<br>MAX 7000AE, MAX 7000B,<br>MAX 7000E, and MAX 7000S devices) |  |  |  |  |

|                                   | MAX 3000A devices                                                                                    |  |  |  |  |

| Design                            | Functional and timing simulation                                                                     |  |  |  |  |

| Verification                      | Static timing analysis                                                                               |  |  |  |  |

| Other Features                    | Graphical floorplanner                                                                               |  |  |  |  |

|                                   | OpenCore evaluation for Altera MegaCore<br>functions                                                 |  |  |  |  |

|                                   | Integration with third-party EDA tools                                                               |  |  |  |  |

|                                   | Support for the library of parameterized modules (LPM)                                               |  |  |  |  |

### **Programmable eStore Provides Immediate Fulfillment for Existing Customers**

The Altera eStore offers immediate access to Altera tools and MegaCore<sup>TM</sup> functions. You can now purchase a new Altera tools subscription, renew your existing subscription, or purchase Altera MegaCore functions on-line any time of the day, seven days a week, at the Altera Programmable eStore.

The Programmable eStore uses the latest technology so that you receive your new license files immediately. Once your order is processed, your new license file is available on-line within seconds.

High-density FLEX 10K designs compile up to 30× faster in the MAX+PLUS II software version 9.5.

*The E+MAX software* features VHDL and Verilog HDL design entry.

# Technical Articles

# **Implementing CAM in an APEX Device**

Content-addressable memory (CAM) devices are used in applications that require fast searches. The data contained in CAM is organized as a set of patterns that can be thoroughly searched in a single clock cycle. If the input pattern presented to CAM matches one of the patterns stored in CAM, the address of the matching stored pattern is generated. APEX<sup>TM</sup> 20KE devices support ternary CAM, a type of CAM that allows stored patterns in memory words to contain "don't care" bits.

The Quartus<sup>™</sup> software version 1999.10 and higher supports designs using CAM. You can implement CAM through the Quartus software using the altcam megafunction.

### The altcam Megafunction

The altcam megafunction (see Figure 1) allows each stored pattern bit to be specified as a binary 1 bit, binary 0 bit, or a don't care bit.

### Writing Patterns into CAM

Writing a new pattern in the altcam megafunction or replacing its stored patterns with new patterns involves the pattern[],

| altca       | am         |              |             |

|-------------|------------|--------------|-------------|

| pattern[]   |            | Parameter    | Value       |

| wrx[]       |            | WIDTH        |             |

| wrxused     |            | WIDTHAD      |             |

| wrdelete    |            | NUMWORDS     | 2^WIDTHAD   |

| wraddress[] |            | LPM_FILE     | "UNUSED"    |

| wren        |            | LPM_FILEX    | "UNUSED"    |

|             | maddress[] | MATCH_MODE   | "MULTIPLE"  |

| inclock     | mbits[]    | OUTPUT_REG   | "UNREGISTER |

| inclocken   | mfound     | OUTPU_ACLR   | "ON"        |

| inaclr      | mcount[]   | PATTERN_REG  | "INCLOCK"   |

| mstart      |            | PATTERN_ACLR | "ON"        |

| mnext       | rdbusy     | WRADDRESS_AC | LR "ON"     |

|             | wrbusy     | WRX_REG      | "INCLOCK"   |

| outclock    |            | WRX_ACLR     | "ON"        |

| outclocken  |            | WRCONTROL_AC | _R "ON"     |

| outaclr     |            | USE_EAB      |             |

wrx[], wrxused, wrdelete, wren, and wraddress[] ports. Patterns without don't care bits can be written in two clock cycles, while those with don't care bits require three clock cycles. During all write cycles, wren must be asserted and wraddress[] and pattern[] must remain unchanged.

If the pattern does not contain don't care bits, then asserting pattern[], wren, and wraddress[] for two clock cycles is sufficient. Don't care bits can be added by using the wrx[] port. Bits with 0 in the wrx[] mark valid pattern bits, and bits with 1 in the wrx[] mark don't care pattern bits. When the wrx[] port is used, the wrx[], wrxused, pattern[], wren, and wraddress[] must be asserted for three clock cycles.

You can also delete altcam entries by asserting wrdelete and wren for two clock cycles. During this time, wraddress[] must indicate the address containing the data to be deleted. The pattern[], wrx[], and wrxused inputs are ignored during delete cycles.

You can use Intel Hexadecimal Format Files (.hex) or Memory Initialization Files (.mif) to initialize CAM during device configuration. MIFs support don't care and never match bits. To support these extra states in HEX files, you must use a second HEX file; one file initializes the data (0 and 1) and the second file sets the don't care and never match bits. If you use the optional second initialization file, it must be named *< first file name>\_udc.hex.*

### **Reading from CAM**

You can use three different modes to read data from the altcam megafunction:

- Single-match mode

- Multiple-match mode

- Fast multiple-match mode

In multiple-match and fast multiple-match modes, an external priority encoder generates the encoded match address output maddress[]. As a result, using this output in the modes listed above results in higher logic utilization.

In all three modes, you can use both encoded (maddress[]) and unencoded (mbits[]) outputs. External logic generates mfound and mcount[], which give the total number of matches.

### Single-Match Mode

In single-match mode

(match\_mode = "multiple"), only one inclock clock cycle is required to read from altcam.

When the input pattern matches one of the stored patterns in altcam, a match flag (mfound) is asserted and the address of the match is presented on maddress[]. Output port mbits[] gives the unencoded version of the match. The output that indicates the number of matches (mcount[]) is always either value 0 or value 1 in this mode.

In single-match mode, altcam will not operate properly if there are multiple patterns stored that match the same input pattern. altcam will give a warning during simulation if there are multiple input patterns.

In this single-match mode, the altcam megafunction uses multiple embedded system blocks (ESBs) to support CAM blocks deeper than 32 words. However, the longest data width supported is 32 bits. For input pattern widths greater than 32 bits, altcam automaticaly switches to the fast multiplematch mode of operation.

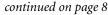

To write don't care bits into altcam, assert wrused high and hold waddress[], pattern[] and wren[]valid for three clock cycles. The bits in wrx[] with 1 indicate don't care bits. For example, in Figure 2, at address 010 the wrx[] is 100, which means the most significant bit is a don't care bit. As a result, reading 110 or 010 will find a match at address 010.

Figure 2. Single-Match CAM Simulation with "Don't Care" Bits

### Multiple-Match Mode

In multiple-match mode

(match\_mode = "multiple"), the megafunction takes two inclock cycles to read from altcam and generate valid outputs, because the ESB generates 16 outputs at each clock cycle. As a result, you need two cycles to generate all 32 outputs from an ESB.

To search the altcam megafunction for a new pattern, apply the pattern data to the pattern[] port and assert the mstart input. If the input pattern matches any of the stored patterns, mfound asserts high, and maddress[] provides the address of the first match (after a two-cycle delay). Other match addresses can be generated on subsequent clock cycles. Assert mnext and hold it high for no more than two clock cycles after mstart. Output port mbits[] gives the unecoded version of the matches. Output port mcount[] counts the total number of matches.

In this multiple-match mode, each ESB supports 31 bits of data because the MSB bit is used to select between the even or odd outputs of the ESB at each clock cycle. However, multiple-match mode supports both deeper and wider CAMs by cascading 32-word × 31-bit ESBs.

Figure 3 on page 16 shows the waveform for multiple-match mode. In multiple-match mode, mstart provides the lowest match address location, and mnext provides the consequent match locations on maddress[]. Do not assert the mnext signal for more than two clock cycles after mstart is asserted. In this example, data 1 is written in three locations: 1, 3, and 5.

continued on page 16

*Implementing CAM in an APEX Device, continued from page 15*

#### Figure 3. Multiple-Match Mode Simulation

| 4.00 | er Tiere Bar | 1.6-9        |      | -jn- | ÷.  | 411       | 104 mi         | -    | *        | 417.44 | -    | Stat      | tr               | et.    |          |

|------|--------------|--------------|------|------|-----|-----------|----------------|------|----------|--------|------|-----------|------------------|--------|----------|

|      | Name         | THE R<br>Box |      |      |     | Hill, Bri |                |      | 229,8 14 | 1      |      | 400,3 m   | 640              | lui -  | 000.1 e  |

| *    | 18.          | .9.8         | In.  | Π.   | n.  |           | 0.0            |      |          | 1.0    | 1.17 | -m.m.     | 7.7.7            |        |          |

| ir.  | B lates      | 8 800        | 100  | 1.   | 100 |           | 100            | 1.10 | 311      | 10     | 111  | 111113    | RECORD, BUILDING | 101100 | CHEX DEC |

| ie.  | E book       | 6 800        | 100  | 1    | 100 | X.        | 001            | 1    | OIT.     | 3C     | 101  | 17        | 00               |        | /        |

| 1    | area.        | 81           |      | 11   |     |           |                |      |          | -      |      |           |                  |        |          |

| 2    | III inter-   | 0 800        |      | 186  |     |           | 230            | 1.0  | 1987     | XT     | 100  | 111       | 1 1 1            | 0.     | 1        |

| 2    | brund        | 81           |      |      |     |           | V              | -    |          | -      | 1    | T X       |                  |        | X        |

| ÚÍ   | (related     | 8.0          | 1.17 |      | TIJ |           | $\neg \lambda$ | 111  |          | 177    | 11   |           |                  |        | 1        |

| CP.  | B holt       | 8 800        |      | 80   | ΞD  | 001       | DOM            | 1800 | \$1.CB   | i bén  | CO.  | n Datinin | "toint serior    | mante  | mbahin   |

| ωn.  | lettery.     | 00           |      | -    | ΠĽ  |           |                |      |          | K I    |      |           | TTTT             |        |          |

| ų,   | Incoar.      | 0.0          | L P  |      | тiг |           | 11             | thir | ħΖ       | 100    |      |           |                  |        |          |

| Ú,   | incase.      | 9.0          |      |      | 1.1 |           |                | V.   | Z        |        |      |           |                  |        |          |

| di l | Incour.      | 8.0          |      |      | 1.1 |           |                | AL.  |          |        |      |           |                  |        |          |

|      |              |              |      |      | П   |           | Dent           | Care | 815      | 11     |      |           |                  |        |          |

Asserting mstart provides address location 1 on the maddress[] port, and asserting mnext provides the consequent locations, 3 and 5. The mcount[] signal shows the total number of matches, which is three in this example.

#### Fast Multiple-Match Mode

Fast multiple-match mode

(match\_mode = "fast\_multiple") is similar to multiple-match mode. The difference is that fast multiple-match mode takes one inclock clock cycle to read from altcam and generate valid outputs. This acceleration comes at the cost of using only half of the memory available in each ESB. As a result, ESB utilization is higher, but data is read out of altcam in one cycle.

Most of the input and output ports used in fast multiple-match mode are identical to multiplematch mode with a few exceptions. Ports such

Figure 4. Fast Multiple-Match Mode Simulation

| -               | e finste - | 122514      | d Poster   | 871.15.00    | ( benefit   | 855.5 m  | Simt :   |            | EM.     |            |         |

|-----------------|------------|-------------|------------|--------------|-------------|----------|----------|------------|---------|------------|---------|

|                 | Norm       | 200         | 182,2 m    | 340,6 m . 13 | 1,6xx 48,6x | 401.2 -  | 80.2 m   | ALC: N     | 738,8 m | 30(1 sc    | 100.2 * |

| 11 <sup>2</sup> | Pch        | Inne        | 1.11.11    | 0.0.7        | 1.11.11.    |          |          |            |         | <b>FLF</b> |         |

| цяř             | M beter    | 0.0         | 1 1 1 1 1  | 00.131       | D0 4 D      | 3D.7     | 6200     | G-3.2      | 0.0     | 3 ( 10.    | OC R.   |

| iπ.             | B leads.   | 1 12 1 2    | 14.2 10 11 | C DC IN      | DG 19 D     | 1. 1.    |          | _          | 0       |            |         |

| 11 <sup>1</sup> | interv .   |             |            |              |             |          |          |            |         |            |         |

| MP:             | Includ     |             | 1 1 1 1 1  |              |             | 5        | _        |            | _       |            | _       |

| ω.              | inenti     |             |            |              |             |          |          | 12.5       |         |            |         |

| di.             | lieband    |             | 1 1 1 1    |              |             |          |          | 1.1.1.1.   |         |            |         |

| 2               | 图 heat     | A DEX TREMS | 11 34      | 378 3        | 1711 14     | OR 221 X | 1 11     | 10.00      | 11018   |            | 1.3     |

| 4               | initary.   |             | 1          |              |             |          |          | 17         |         |            |         |

|                 |            |             |            |              |             | 1        | we match | en fer inp | z.T     |            |         |

as maddress[], mcount[], mfound, pattern[], wrx[], and wren function the same as in multiple-match mode. The rbusy port is not used in fast multiple-match mode because the read does not exceed one clock cycle. The mstart and mnext ports are not required for this mode if the location of the matched address is not required (if maddress[] is not used), and only the mbits[] output gives the unencoded version of the matching address. If maddress[] output port is used, mstart and mnext must be used to give the first and next matching addresses.

In fast multiple-match mode, the altcam megafunction supports CAM blocks deeper and wider than 32 words and bits by cascading multiple ESBs. Figure 4 shows the simulation result of a fast multiple-match mode.

### **CAM Modes Comparison**

To compare the performance and utilization of CAM modes, a 32-word  $\times$  32-bit CAM was compiled for an EP20K200E-1 device. Table 1 shows the result for this comparison.

| Table 1. Peri<br>Parameter | formance & L             | Itilization of<br>Usage   | CAM Modes                          |

|----------------------------|--------------------------|---------------------------|------------------------------------|

|                            | Single-<br>Match<br>Mode | Mutiple-<br>Match<br>Mode | Fast<br>Multiple-<br>Match<br>Mode |

| RAM Blocks<br>(ESBs)       | 1                        | 1                         | 2                                  |

| LEs                        | 35                       | 98                        | 79                                 |

| fmax (MHz)                 | 198.89                   | 94.45                     | 190.91                             |

### Conclusion

The Quartus software version 1999.10 and higher supports CAM implementation in APEX 20KE devices. Depending on your design requirements, you can implement any CAM mode by using the altcam megafunction. Additionally, MIFs and HEX files support CAM initialization. By using CAM, you can speed up any design that requires searches.

### **APEX PLLs Offer Advanced Clock Synthesis**

APEX<sup>TM</sup> 20KE devices support the ClockLock<sup>TM</sup>, ClockBoost<sup>TM</sup>, ClockShift<sup>TM</sup>, and external clock output features, which are implemented with phase-locked loops (PLLs). The ClockLock feature minimizes clock delay and clock skew within the device, reducing clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry provides a clock multiplier to scale or multiply the input clock by integers or fractional ratios. The designer can use the programmable clock phase within the ClockShift circuitry for phase shift applications or for clock delay control to meet strict timing requirements. The external clock output drives a locked clock off-chip to external devices with optional zero delay or external feedback. The ClockLock, ClockBoost, and ClockShift features work in conjunction with the APEX 20KE device's high-speed clock to provide advanced clock synthesis capabilities. This article discusses the enhanced clock synthesis features within APEX 20KE devices.

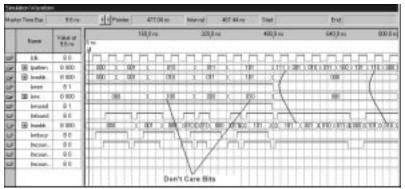

### **APEX 20KE PLLs Provide Clock Synthesis**

APEX 20KE devices incorporate up to four PLLs with advanced circuitry and feature low-voltage differential signaling (LVDS) support, ClockShift circuitry, and external clock outputs with optional external feedback inputs. Figure 1 shows the ClockLock and ClockBoost circuitry in one of the four APEX 20KE PLLs. You can instantiate APEX 20KE PLLs and adjust parameters to control advanced features in the Quartus<sup>™</sup> software with the altclklock megafunction.

Each APEX 20KE PLL includes circuitry that provides clock synthesis using  $m/(n \times k)$  or  $m/(n \times v)$  scaling, depending on the output clock used. When a PLL is locked, the locked output clock aligns to the rising edge of the input clock. Because the PLL output contains dual dividers, you can output two different frequencies from a single PLL. The closed loop equation for Figure 1 gives output frequencies of

### $f_{clock0} = f_{in}(m/(n \times k))$

$$f_{clock1} = f_{in}(m/(n \times v))$$

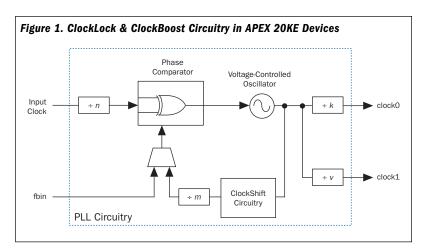

The Quartus software handles these equations for the user; the user only needs to enter the desired integer multiplication and division ratios. The MegaWizard<sup>TM</sup> Plug-In Manager provides a simple interface to enter parameters into the altclklock megafunction to achieve the desired PLL outputs. The MegaWizard Plug-In Manager notifies the designer if the multiplication and division rate is possible for the given frequency (see Figure 2).

continued on page 18

# APEX PLLs Offer Advanced Clock Synthesis, continued from page 17

The advanced ClockBoost feature allows the designer to reduce the effects of high-speed signals by using a low-speed clock on the printed circuit board (PCB). The ClockBoost feature can internally multiply those low-speed clocks. The ability to generate multiple scaled clocks within the device allows for easier board design.

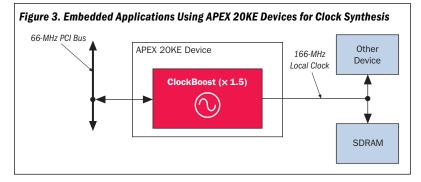

Designers can use the versatile multiplication capability to generate up to four scaled clocks within the same device from a single clock source. This process is useful in microprocessorbased systems, where a system clock may run at a lower rate than other system components. Figure 3 shows clock synthesis for an embedded application in an APEX 20KE device.

### Figure 5. Setting Phase Shift & Other PLL Features

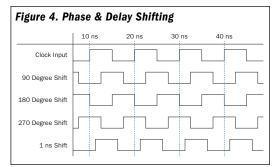

APEX 20KE PLLs have ClockShift circuitry that provides programmable clock delay and phase shift. The clock phase can be adjusted to lag the input by 90, 180, or 270 degrees, or to any desired phase or time shift with fine resolution (see Figure 4). The resolution steps range from 0.5 ns to 1.0 ns, depending on the input frequency and scaling rates. Users enter the desired phase shift in the MegaWizard Plug-In Manager (see Figure 5). The dialog box in Figure 2 displays the closest achievable shift with the frequency and scaling used.

Low-jitter external clocks are available in APEX 20KE devices for external clock sources. Other devices on the board can use these outputs as clock sources. The external clock output can also be configured as a zero delay buffer, i.e., the output-clock pin can be phasealigned with the input clock pin.

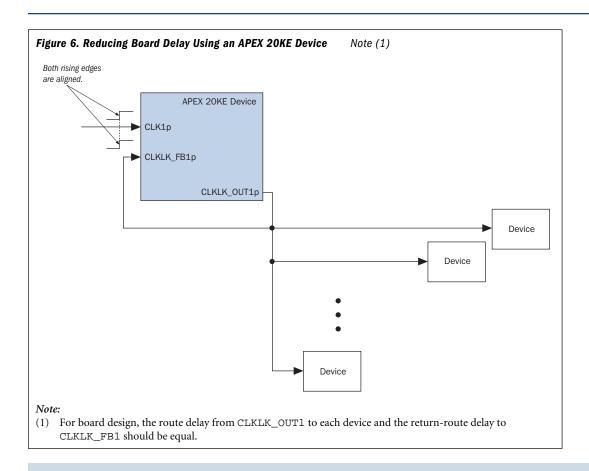

In addition to the clock output capability, you can use feedback inputs to align the external feedback clock pin with the input clock pin. By aligning these clocks, you can actively remove clock delay and skew between devices. Board delay is actively adjusted independent of process, temperature, or voltage.

Matching the return delay that contains the feedback input pin with the delay to each device ensures that delay is eliminated. See Figure 6.

### Summary

The advanced feature set of APEX PLLs, including ClockLock, ClockBoost, and ClockShift features, work in conjunction with the APEX device's high-speed clock to provide significant improvements in system performance, bandwidth, and clock synthesis. For more information on APEX 20KE PLLs, see *Application Note 115 (Using the ClockLock and ClockBoost Features in APEX Devices)* and the *Using APEX 20K & APEX 20KE PLLs in Quartus White Paper.*

# **Special Software Renewal Promotion**

For a limited time, you can receive a 10% discount on the renewal of your development tool subscription by submitting your renewal order before your current subscription expires.

All customers with a current subscription can take advantage of this offer. If you renew your subscription before expiration, Altera will take 10% off of the renewal list price of \$2,000.

Buying a renewal subscription will extend your subscription by 12 months from your current expiration date. There is no penalty for renewing early. You will continue to receive Quartus<sup>™</sup> and MAX+PLUS<sup>®</sup> II software updates for an additional 12 months without any interruption.

To renew your subscription, contact your local Altera<sup>®</sup> sales representative. For a complete listing, go to the Altera web site (http://www.altera.com). North American customers can also call Altera Tools Services at (888) 800-0631 or visit the Altera Programmable eStore at http://www.altera.com/html/ecommerce/ index.html to renew your license on-line.

## Using I/O Standards in the Quartus Software

APEX<sup>TM</sup> 20KE I/O banks support 14 I/O standards (see Table 1) and are the first programmable logic devices (PLDs) in the industry with dedicated circuitry supporting low-voltage differential signaling (LVDS). Altera's APEX 20KE devices offer the highest density, highest performance programmable logic solution with the necessary I/O standards for use in the communication and computer industries.

APEX 20KE I/O buffers are designed to meet the voltage, drive strength, and AC characteristics necessary to be compliant with the I/O standards listed in Table 1.

This article discusses the support for the selectable I/O standards for APEX 20KE devices in the Quartus<sup>™</sup> software.

Users can specify which pins support which I/O standard on a pin-by-pin basis, similar to pin assignments.

| Table 1. APEX 20KE Supported I/O Standards |                    |                                                          |                                            |                                             |  |  |

|--------------------------------------------|--------------------|----------------------------------------------------------|--------------------------------------------|---------------------------------------------|--|--|

| I/O Standard (1)                           | Туре               | Input<br>Reference<br>Voltage<br>(V <sub>REF</sub> ) (V) | Output<br>Supply<br>Voltage<br>(Vccio) (V) | Board<br>Termination<br>Voltage<br>(Vπ) (V) |  |  |

| LVTTL                                      | Single-ended       | N/A                                                      | 3.3                                        | N/A                                         |  |  |

| LVCMOS                                     | Single-ended       | N/A                                                      | 3.3                                        | N/A                                         |  |  |

| 2.5 V                                      | Single-ended       | N/A                                                      | 2.5                                        | N/A                                         |  |  |

| 1.8 V                                      | Single-ended       | N/A                                                      | 1.8                                        | N/A                                         |  |  |

| 3.3-V PCI                                  | Single-ended       | N/A                                                      | 3.3                                        | N/A                                         |  |  |

| LVDS                                       | Differential       | N/A                                                      | 3.3                                        | N/A                                         |  |  |

| GTL+                                       | Voltage referenced | 1.0                                                      | N/A                                        | 1.5                                         |  |  |

| SSTL-2 Class I and II                      | Voltage referenced | 1.125                                                    | 2.5                                        | 1.125                                       |  |  |

| SSTL-3 Class I and II                      | Voltage referenced | 1.5                                                      | 3.3                                        | 1.5                                         |  |  |

| HSTL Class I                               | Voltage referenced | 0.75                                                     | 1.5                                        | 0.75                                        |  |  |

| AGP                                        | Voltage referenced | 1.32                                                     | 3.3                                        | N/A                                         |  |  |

| CTT                                        | Voltage referenced | 1.5                                                      | 3.3                                        | 1.5                                         |  |  |

#### Notes:

AGP: advanced graphics port, CTT: center-tap-terminated, GTL+: Gunning transceiver logic plus, HSTL: high-speed transceiver logic, LVCMOS: low-voltage complementary metal-oxide semiconductor, LVTTL: low-voltage transistor-totransistor logic, PCI: peripheral component interconnect, SSTL: stub-series terminated logic.

- The pin-assignment windows in the Quartus software have been updated so that users can make I/O standard assignments, pin assignments, and reserved pin assignments in one dialog box.

- The enhanced Floorplan Editor displays the separate I/O banks and the LVDS transmitter and receiver blocks.

- The Quartus software verifies user placement and I/O standard assignments, and automatically places I/O pins based on V<sub>REF</sub> and I/O standard assignments.

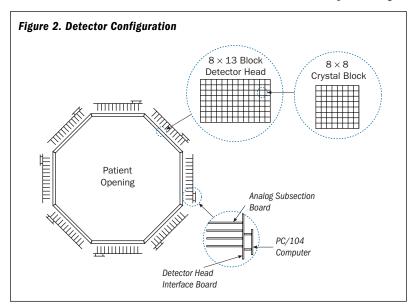

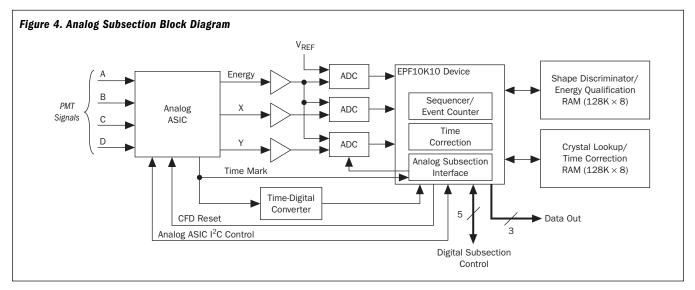

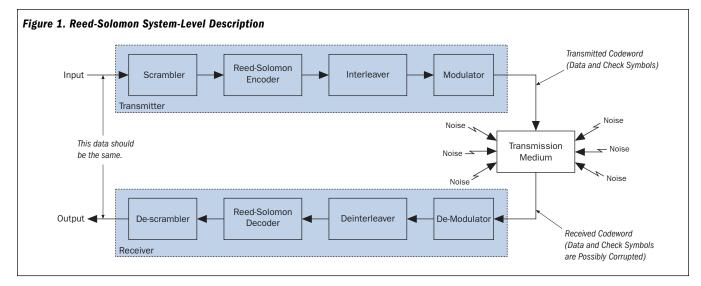

### Device & Pin Options Dialog Box (Compiler Settings Dialog Box)