## Newsletter for Altera Customers

## MAX 7000B Devices Maintain Leadership Through Innovation & Technology

Altera has successfully rolled out the industry's fastest product-term-based device family: MAX<sup>®</sup> 7000B devices. Fabricated using advanced 0.22-µm CMOS technology, MAX 7000B devices offer propagation delays as fast as 3.5 ns and counter frequencies of over 200 MHz. MAX 7000B devices are also the most feature-rich product-term-based devices in the programmable logic device (PLD) industry.

MAX 7000B devices provide a tremendous performance advantage, especially in the higher macrocell count (256 and 512 macrocell) designs. As Table 1 shows, the fast propagation delays offered by MAX 7000B devices extend Altera's performance leadership in the marketplace.

## Low-Power Leader in the High-Performance Spectrum

MAX 7000B devices also have the lowest power consumption for high-performance applications. Power consumed by a device is a

function of the operating current as well as the operating core voltage (Power = Voltage  $\times$  Current). Because the MAX 7000B core operates at 2.5 V, these devices consume 30% less power than 3.3-V Altera CPLDs.

MAX 7000B devices also feature a programmable power-saving mode, allowing you to configure one or more macrocells to operate at less than 50% of the normal power while adding only a nominal timing delay. This feature allows intelligent speed/power tradeoffs for different portions of the design. At high operating frequencies, MAX 7000B devices are a clear industry leader in low-power consumption.

## Advanced I/O Standards Support

Altera MAX 7000B devices are the leader in advanced I/O standard support. These devices are the only product-term architecture capable

continued on page 4

| Table 1. Typical Propagation Delay Times |                              |              |                |                  |  |  |  |

|------------------------------------------|------------------------------|--------------|----------------|------------------|--|--|--|

| Macrocell                                | Propagation Delay Times (ns) |              |                |                  |  |  |  |

| Range                                    | MAX 7000B (1)                | XC9500XL (1) | CoolRunner (1) | ispLSI2000VE (2) |  |  |  |

| 32 to 36                                 | 3.5                          | 5.0          | 5.0            | 4.5              |  |  |  |

| 64 to 72                                 | 3.5                          | 5.0          | 6.0            | 5.0              |  |  |  |

| 128 to 144                               | 4.0                          | 5.0          | 6.0            | 6.0              |  |  |  |

| 192 to 288                               | 5.0                          | 7.5          | 7.5            | 7.0              |  |  |  |

| 512 and higher                           | 5.5                          | -            | -              | -                |  |  |  |

#### Notes:

(1)  $t_{PD}$  values taken from device literature.

(2)  $t_{PD}$  value through a typical logic path consisting of five product-term elements and the output routing pool.

2.5-V ISP Now Shipping

Inside This Issue:

- APEX 20KE True-LVDS Solution Enables 840-Mbps Data Rate, pg. 5

- Synplicity's Physical Synthesis Boosts Performance by up to 40%, pg. 32

# Table of Contents

## Features

| MAX 7000B Devices Maintain Leadership through |   |

|-----------------------------------------------|---|

| Innovation & Technology                       | 1 |

| APEX 20KE True-LVDS Solution Enables          |   |

| 840-MBPS Data Rate                            | 5 |

| Design Tips: Using Ternary Content            |   |

| Addressable Memory1                           | 5 |

| Customer Application: LGIC Uses FLEX Devices  |   |

| to Pioneer Broadband CDMA WLL System 1        | 9 |

| Contributed Article: JTAG Technologies Adds   |   |

| Jam STAPL Support to On-Board Programming     |   |

| Software2                                     | 1 |

#### **Altera News**

| OEM Licensing Details for Mentor Graphics      |    |

|------------------------------------------------|----|

| Software                                       | 18 |

| Using Intellectual Property in Third-Party     |    |

| Synthesis                                      | 28 |

| Altera & HelloBrain.com: Using the Internet to |    |

| Facilitate Customer/Partner Interaction        | 31 |

| Synplicity's Physical Synthesis Boosts         |    |

| Performance by up to 40%                       | 32 |

| Improved Performance Specifications for        |    |

| APEX 20KE PLLs                                 | 34 |

| Implementing an ATM Switch with APEX           |    |

| Embedded CAM                                   | 36 |

|                                                |    |

## **Devices & Tools**

| APEX EP20K1500KE Devices Now Shipping       | 8 |

|---------------------------------------------|---|

| APEX 20KE Devices Support Advanced I/O      |   |

| Standards                                   | 8 |

| 5.0-V Tolerant APEX 20K & APEX 20KE Devices | 8 |

| APEX 20K Product Transition                 | 9 |

| ACEX 1K Devices Shipping Now                | 9 |

| All FLEX 10KE Devices Available             | 9 |

| FLEX 10K Product Transitions                | 9 |

| FLEX 10KE Industrial-Temperature Devices 1  | 0 |

| MAX 7000A Devices 11                                         |

|--------------------------------------------------------------|

| MAX 7000B Devices11                                          |

| MAX 7000S Devices11                                          |

| MAX 3000A Devices                                            |

| High Density Configuration Devices Coming Soon. 12           |

| Quartus Version 2000.09 Coming Soon                          |

|                                                              |

| PowerFit Fitter Provides Dramatic f <sub>MAX</sub> & Compile |

| Time Improvements 12                                         |

| More Powerful Timing Analysis                                |

| Support for Windows 2000 & HP-UX 11.0 13                     |

| Improved Support for Third Party Simulation                  |

| Timing Analysis Tools                                        |

| Block-Level Design Enhanced to Support Third                 |

| Party EDA Tools                                              |

| Expanded APEX Device Package Support                         |

| Quartus Windows 2000 Certified                               |

|                                                              |

| MAX+PLUS II Software Supports New ACEX                       |

| Devices                                                      |

| World-Class Synthesis & Simulation Tools                     |

| Now Shipping14                                               |

| Discontinued Devices Update                                  |

## **Technical Articles**

| Implementing LVDS Interfaces with       |    |

|-----------------------------------------|----|

| General-Purpose I/O Pins2               | 22 |

| Using ModelSim Altera: Frequently Asked |    |

| Questions                               | 25 |

| Questions & Answers                     | 38 |

## In Every Issue

| Current Software Versions     | 40 |

|-------------------------------|----|

| New Altera Publications       | 40 |

| Altera Programming Support    | 41 |

| How to Contact Altera         |    |

| Altera Device Selection Guide | 44 |

Altera, ACCESS Program, ACEX, ACEX, IK, ACEX, 2K, AMPP, APEX, APEX, 20K, APEX, 20KE, Atlas, BitBlaster, ByteBlaster, ByteBlaster, MV, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, E+MAX, EPC2, Excalibur, FastTrack, FineLine BGA, FLEX, FLEX 10K, FLEX 10KF, FLEX 10KA, FLEX 8000, FLEX 6000, A Jam, MasterBlaster, MAX, MAX 9000, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000AE, MAX 7000B, MAX 3000, MAX 3000A, 3000A, MAX 300A, MA  $MAX+PLUS, MAX+PLUS \ II, MegaCore, MegaLAB, MegaWizard, MultiCore, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NativeLink, Nios, nSTEP, OpenCore, NegaLAB, MegaWizard, MultiCore, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, Quartus, SignalTap, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, OpenCore, NegaVizard, NegaVizard, MultiVolt, NativeLink, Nios, nSTEP, NegaVizard, Nega$ SignalTap Plus, True-LVDS, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: Adobe and Acrobat are registered trademarks of Adobe Systems Incorporated. BP Microsystems is a registered trademark of BP Microsystems. Data I/O and UniSite are registered trademarks of Data I/O Corporation. HelloBrain.com is a trademark of HelloBrain.com. HP-UX is a trademark of Hewlett-Packard Company. JTAG Technologies is a registered trademark of JTAG Technologies B.V. LG Information & Communications (LGIC) is a registered trademark of LG Information & Communications, Ltd. Mentor Graphics is a registered trademark and LeonardoSpectrum and ModelSim are trademarks of Mentor Graphics. Microsoft, Windows, Windows 98, and Windows NT are registered trademarks of Microsoft Corporation. ObjectStore is is a registered trademark of ObjectDesign. Rochester Electronics is a registered trademark of Rochester Electronics, Inc. Sun is a registered trademark and Solaris is a trademark of Sun Microsystems, Inc. Synplicity is a registered trademark and Amplify and Physical Optimizer are trademarks of Synplicity, Inc. Synopsys is a registered trademark and FPGA *Express* is a trademark of Synopsys, Inc. System General is a registered trademark of System General. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. The actual availability of Altera's products and features could differ from those projected in this publication and are provided solely as an estimate to the reader.

Greg Steinke, Technical Editor 101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 n\_v@altera.com

Rhonda Scott,

Publisher

Copyright © 2000 Altera Corporation. All rights reserved.

3

MAX 7000B Devices Maintain Leadership through Innovation & Technology, continued from page 1

of supporting GTL+, SSTL-3, and, SSTL-2. Table 2 compares the I/O standards supported by MAX 7000B devices to other devices.

| l/0<br>Standard          | MAX 7000B    | XC9500XV<br>(2.5 V) | ispLSI2000VL<br>(2.5 V) | CoolRunner<br>(XPLA3-XL) |

|--------------------------|--------------|---------------------|-------------------------|--------------------------|

| GTL+                     | $\checkmark$ |                     |                         |                          |

| SSTL-2 class I<br>and II | $\checkmark$ |                     |                         |                          |

| SSTL-3 class I<br>and II | $\checkmark$ |                     |                         |                          |

| LVTTL                    | $\checkmark$ | $\checkmark$        | ~                       | $\checkmark$             |

| LVCMOS                   | $\checkmark$ | $\checkmark$        | ~                       | $\checkmark$             |

| 2.5 V                    | $\checkmark$ | $\checkmark$        | ~                       |                          |

| 1.8 V                    | $\checkmark$ | $\checkmark$        | $\checkmark$            |                          |

| 64-bit, 66-MHz<br>PCI    | $\checkmark$ |                     |                         |                          |

Support for advanced I/O standards (GTL+, SSTL-2, and SSTL-3) allows designers to use MAX 7000B devices in high-speed design applications such as processor interfaces, backplane drivers, and SDRAM memory interfaces.

## **Programming Times Leader**

Preliminary results show that MAX 7000B devices have programming times equivalent to MAX 7000AE devices. In a production environment, quick programming times represent substantial savings in overall cost. In a manufacturing flow, each extra second spent on programming adds about \$0.10 to \$0.25 to the system cost. MAX 7000B devices can be programmed in a fraction of the time required to program the Xilinx XC9500XL devices, as shown in Table 3.

| Device                                 | Programming Time<br>with 2-MHz TCK Rate |  |  |  |  |  |

|----------------------------------------|-----------------------------------------|--|--|--|--|--|

| EPM7128B (erase, program, and verify)  | 2.2 seconds                             |  |  |  |  |  |

| XC95144XL (erase, program, and verify) | 1.6 minutes                             |  |  |  |  |  |

| XC95144XL (program and verify only)    | 1.5 minutes                             |  |  |  |  |  |

Using a Xilinx CPLD instead of a MAX 7000B device can add between \$9.40 to \$23.50 in programming cost alone.

## MAX 7000B Versatility

MAX 7000B devices range in density from 32 to 512 macrocells and are offered in a wide range of packages, including 1.0-mm FineLine BGA<sup>TM</sup> and 0.8-mm Ultra FineLine BGA packages.

MAX 7000B devices offer vertical migration across devices (as shown in Table 4), and also support the SameFrame<sup>™</sup> pin-out feature for FineLine BGA and Ultra FineLine BGA packages, providing designers additional flexibility for package migration.

By offering a wide range of density, package, and speed grade options, MAX 7000B devices present an ideal solution for today's highperformance designs.

| Device   | ce Package     |                |                                    |                 |                            |                 |                                     |                 |                |                            |

|----------|----------------|----------------|------------------------------------|-----------------|----------------------------|-----------------|-------------------------------------|-----------------|----------------|----------------------------|

|          | 44-Pin<br>PLCC | 44-Pin<br>TQFP | 49-Pin<br>Ultra<br>FineLine<br>BGA | 100-Pin<br>TQFP | 100-Pin<br>FineLine<br>BGA | 144-Pin<br>TQFP | 169-Pin<br>Ultra<br>FineLine<br>BGA | 208-Pin<br>PQFP | 256-Pin<br>BGA | 256-Pin<br>FineLine<br>BGA |

| EPM7032B | $\checkmark$   | $\checkmark$   | $\checkmark$                       |                 |                            |                 |                                     |                 |                |                            |

| EPM7064B | $\checkmark$   | $\checkmark$   | $\checkmark$                       | $\checkmark$    | $\checkmark$               |                 |                                     |                 |                |                            |

| EPM7128B |                |                | $\checkmark$                       | $\checkmark$    | $\checkmark$               | $\checkmark$    | $\checkmark$                        |                 |                | $\checkmark$               |

| EPM7256B |                |                |                                    | $\checkmark$    |                            | $\checkmark$    | $\checkmark$                        | $\checkmark$    |                | $\checkmark$               |

| EPM7512B |                |                |                                    |                 |                            | $\checkmark$    | $\checkmark$                        | $\checkmark$    | $\checkmark$   | $\checkmark$               |

## **APEX 20KE True-LVDS Solution Enables 840-Mbps Data Rate**

With the latest advancements in next generation communication systems, the requirement for higher bandwidth and I/O performance has increased dramatically. This increase has been assisted by the creation of newer I/O standards such as the LVDS standard. LVDS has been identified as the best solution for communication applications because of its high performance, high noise immunity, and low power consumption.

To combine these benefits with the inherent advantages of the programmable logic devices (PLDs) such as flexibility and time-to-market, Altera has incorporated True-LVDS<sup>TM</sup> dedicated circuitry within the APEX<sup>TM</sup> 20KE family of devices. The True-LVDS solution in the APEX 20KE devices makes them industry's first system-on-a-programmable-chip (SOPC) solution to support data transfer rate up to 840 Megabits per second per channel.

This article outlines the robust performance of the True-LVDS circuitry in APEX 20KE devices through the following features:

- High speed data transfer rates of up to 840 Mbps per channel

- Dedicated LVDS circuitry such as LVDS Transmitter and LVDS Receiver

- High quality true differential I/O drivers

- Easy design flow in Quartus<sup>™</sup> software

- Integrated deskew circuitry

- Low power consumption

- Simple board-level design requirements

## **True-LVDS Solution**

The APEX 20KE True-LVDS solution not only provides a high data transfer rate of up to 840 Mbps per channel, but also offers high noise immunity, low power consumption, and low electromagnetic interference (EMI), benefits that are utilized by high-speed communication applications. The True-LVDS solution is made possible by the following innovative technology:

Dedicated receiver and transmitter circuitry performing serial-to-parallel and parallelto-serial conversions makes the high toggle rates (840 Mbps) possible.

continued on page 6

APEX True-LVDS Solution Enables 840 Mbps Data Rate, continued from page 5

- On-chip phase-locked loop (PLL) circuitry with 8× multiplication internally boosts the input clock to 840 MHz.

- Dedicated deskew circuitry ensures clock and data signals are internally aligned.

- True differential I/O drivers enable high noise immunity, low power consumption, and low EMI.

#### **True-LVDS Performance**

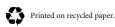

The APEX 20KE True-LVDS feature has been verified to run at 840 Mbps per channel under worst-case conditions. This confirms the robustness of the APEX 20KE True-LVDS feature. Figure 1 on page 5 shows the performance of True-LVDS circuitry at 840 Mbps.

When analyzing LVDS I/O performance, it is important to consider various specifications including channel skew on the output pins and maximum receiver input skew margin. These specifications are required to determine LVDS system performance. They also indicate whether the data captured by a particular channel will be correct or not. Table 1 defines the specifications and provides the APEX 20KE LVDS values at 840 Mbps.

| Specification | Definition                                                                                               | APEX 20KE<br>True-LVDS Values<br>840 Mbps |  |  |

|---------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|

| flvdsdr       | Maximum LVDS data<br>transfer rate                                                                       |                                           |  |  |

| TCCS          | Transmitter channel-<br>to-channel skew                                                                  | 400 ps                                    |  |  |

| SW            | Sampling window:<br>required time that<br>data must be stable<br>for LVDS receiver to<br>capture it.     | 440 ps                                    |  |  |

| RSKM          | Receiver input skew<br>margin: allowable<br>board skew,<br>specified with de-<br>skew feature<br>engaged | 473 ps                                    |  |  |

## **True-LVDS Quality**

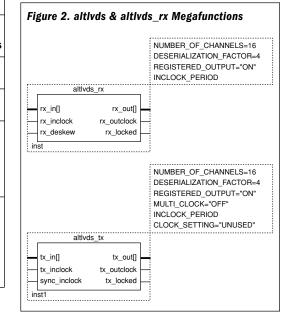

The overall quality of the LVDS I/O is typically measured using an "eye diagram" generated by a data sampling oscilloscope. An "eye diagram" is a visual representation of the jitter and output driver quality of an LVDS output signal. It is obtained by sending pseudo-random data over the LVDS channel and using a sampling oscilloscope to perform a persistence measurement. The transitions are captured and plotted over time. Horizontal eye closure is due to jitter, while vertical eye closure is due to signal attenuation or noise. Therefore, a larger "eye" indicates a better quality driver. Figure 3 shows the "eye diagram" for an APEX EP20K400E device operating at 840 Mbps data rate.

## **True-LVDS Software Support**

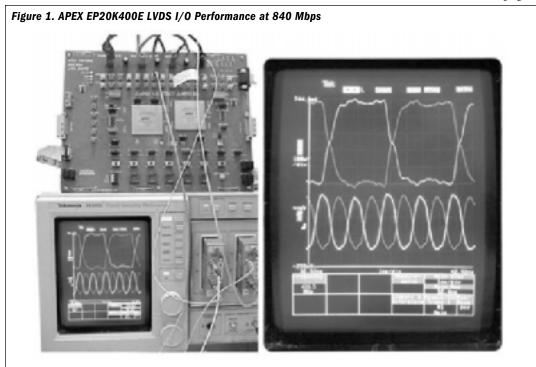

The APEX 20KE True-LVDS solution is very easy to implement via push button compilation support in the Quartus<sup>™</sup> software tool. The altlvds\_tx and altlvds\_rx megafunctions shown in Figure 2 are available in the Quartus software and allow for drop-in implementation of the LVDS Transmitter and LVDS Receiver, respectively. Designers can customize the number of channels, operating frequency, and data transfer modes for these megafunctions, thereby gaining greater design flexibility.

The APEX 20KE True-LVDS solution is very easy to implement via push button compilation support in the Quartus software tool.

#### Features

The APEX 20KE True-LVDS solution is ideal for telecommunication, data communication, and computing applications.

The APEX 20KE True-LVDS feature supports the 1×, 4×, 7×, and 8× data transfer modes that allow the designer to interface with other industry-standard LVDS devices such as the National Semiconductor LVDS chip that uses the 7× mode.

## **True-LVDS Applications**

APEX 20KE True-LVDS solution is ideal for telecommunication, data communication, and

computing applications. The 840 Mbps data transfer rate provides full support for Dense Wave Division Multiplexing (DWDM) systems transmitting and receiving OC-12 data with Reed-Solomon forward error correction encoding running at 666 Mbps per channel.

With LVDS, APEX 20KE devices offer the highest performance, highest bandwidth, and lowest power system-on-a-programmable-chip solution for high speed data transmission designs.

## APEX

## APEX EP20K1500E Devices Now Shipping

The largest APEX<sup>™</sup> 20KE device, the APEX EP20K1500E device, is now shipping. With a maximum of 2.4 million system gates, 51,840 logic elements (LEs), 416 KBytes of RAM, and 808 user I/O pins, this device addresses the needs of system-on-aprogrammable-chip (SOPC) applications.

Nine out of the ten APEX 20KE family members are now shipping, including the EP20K60E, EP20K100E, EP20K160E, EP20K200E, EP20K300E, EP20K400E, EP20K600E, EP20K1000E, and EP20K1500E devices. The smallest APEX 20KE device, the EP20K30E device, is scheduled to be available in the fourth quarter of 2000. These devices are available in multiple packages, including the FineLine BGA<sup>TM</sup> package.

## APEX 20KE Devices Support Advanced I/O Standards

APEX 20KE devices offer support for many advanced I/O standards, including LVDS. The APEX True-LVDS<sup>™</sup> dedicated circuitry has data transfer rates as high as 840 megabits per second (Mbps) per channel and is ideal for high-speed telecommunication, data communication, and computing applications. APEX 20KE devices also support the low-voltage positive emitter coupled logic (LVPECL) standard that can be used in high-performance clocking schemes, backplanes, optical transceivers, high-speed networking, and high-end video applications.

## 5.0-V Tolerant APEX 20K & APEX 20KE Devices

The APEX 20K device family has been enhanced to provide a 5.0-V tolerant I/O buffer, providing full compliance with the 5.0-V PCI specification. 5.0-V tolerant devices are now shipping and have a "V" suffix in the ordering code (e.g., EP20K400BC652-1V).

Table 1. APEX 20KE Device & Quartus Software

Support Availability

| Device      | Package                | Software<br>Support<br>Availability |

|-------------|------------------------|-------------------------------------|

| EP20K30E    | 144-pin TQFP (1)       | Q3 2000                             |

|             | 144-pin FineLine BGA   | Q3 2000                             |

|             | 208-pin PQFP (1)       | Q3 2000                             |

|             | 324-pin FineLine BGA   | Q3 2000                             |

| EP20K60E    | 144-pin TQFP           | Now                                 |

|             | 144-pin FineLine BGA   | Now                                 |

|             | 208-pin PQFP           | Now                                 |

|             | 240-pin PQFP           | Now                                 |

|             | 324-pin FineLine BGA   | Now                                 |

|             | 356-pin BGA (1)        | Now                                 |

| EP20K100E   | 144-pin TQFP           | Now                                 |

|             | 144-pin FineLine BGA   | Now                                 |

|             | 208-pin PQFP           | Now                                 |

|             | 240-pin PQFP           | Now                                 |

|             | 324-pin FineLine BGA   | Now                                 |

|             | 356-pin BGA            | Now                                 |

| EP20K160E   | 144-pin TQFP           | Now                                 |

|             | 208-pin PQFP           | Now                                 |

|             | 240-pin PQFP           | Now                                 |

|             | 356-pin BGA            | Now                                 |

|             | 484-pin FineLine BGA   | Now                                 |

| EP20K200E   | 208-pin PQFP           | Now                                 |

|             | 240-pin PQFP           | Now                                 |

|             | 356-pin BGA            | Now                                 |

|             | 484-pin FineLine BGA   | Now                                 |

|             | 652-pin BGA            | Now                                 |

|             | 672-pin FineLine BGA   | Now                                 |

| EP20K300E   | 240-pin PQFP           | Now                                 |

|             | 652-pin BGA            | Now                                 |

|             | 672-pin FineLine BGA   | Now                                 |

| EP20K400E   | 652-pin BGA            | Now                                 |

|             | 672-pin FineLine BGA   | Now                                 |

| EP20K600E   | 652-pin BGA            | Now                                 |

|             | 672-pin FineLine BGA   | Now                                 |

|             | 1,020-pin FineLine BGA | Now                                 |

| EP20K1000E  | 652-pin BGA            | Now                                 |

|             | 672-pin FineLine BGA   | Now                                 |

|             | 1,020-pin FineLine BGA | Now                                 |

| EP20K1500E  | 652-pin BGA            | Now                                 |

| LI 2011000L | 1,020-pin FineLine BGA | Now                                 |

Note:

(1) TQFP: thin quad flat pack, PQFP: plastic quad flat pack, BGA: ball-grid array.

You can use APEX 20KE devices with an additional external resistor to make these devices 5.0-V tolerant and provide flexibility for system design. The technical details for this improvement are described in the Altera 5.0-V *Tolerance in APEX 20KE Devices White Paper*.

## **APEX 20K Product Transition**

Altera is migrating the 2.5-V EP20K400 device from a 0.25-µm process to a 0.22-µm process. Information regarding this device migration can be found in process change notification (PCN) 0005, available on the Altera web site at http://www.altera.com.

## ACEX

## **ACEX 1K Devices Shipping Now**

ACEX<sup>TM</sup> 1K devices are now shipping in all packages for 30,000-, 50,000-, and 100,000-gate densities (see Table 2). These cost-optimized devices are especially well suited for low-cost, high-performance communications applications, and can be used to attain the lowest cost per programmable logic device (PLD) for high-volume designs.

| Table 2. ACEX 1K Device Offerings |                      |                |

|-----------------------------------|----------------------|----------------|

| Device                            | Package              | Availability   |

| EP1K10                            | 100-pin TQFP         | September 2000 |

|                                   | 144-pin TQFP         | September 2000 |

|                                   | 208-pin PQFP         | September 2000 |

|                                   | 256-pin FineLine BGA | September 2000 |

| EP1K30                            | 144-pin TQFP         | Now            |

|                                   | 208-pin PQFP         | Now            |

|                                   | 256-pin FineLine BGA | Now            |

| EP1K50                            | 144-pin TQFP         | Now            |

|                                   | 208-pin PQFP         | Now            |

|                                   | 256-pin FineLine BGA | Now            |

|                                   | 484-pin FineLine BGA | Now            |

| EP1K100                           | 208-pin PQFP         | Now            |

|                                   | 256-pin FineLine BGA | Now            |

|                                   | 484-pin FineLine BGA | Now            |

ACEX 1K devices provide full phase-locked loop (PLL) capability for ClockLock<sup>TM</sup> and ClockBoost<sup>TM</sup> features in every -1 and -2 speed grade device, embedded dual-port RAM, and

full 64-bit, 66-MHz PCI compliance. Developed on an innovative 0.22-µm/0.18-µm hybrid process, and featuring a 2.5-V core operating voltage, ACEX 1K devices offer an ideal combination of cost, performance, and features.

Full software support for ACEX 1K devices is available from the MAX+PLUS<sup>®</sup> II software version 10.0. In addition, a wide range of ACEX-optimized intellectual property (IP) functions can now be found at the Altera IP MegaStore<sup>™</sup> on-line store.

## FLEX

## All FLEX 10KE Devices Available

All EPF10K30E, EPF10K50S, EPF10K100E, EPF10K130E, and EPF10K200S devices are now shipping in -1, -2, and -3 speed grades. These devices are fabricated on a 0.22-µm process and have a programmable input buffer delay for full 64-bit, 66-MHz PCI compliance.

FLEX<sup>®</sup> 10KE devices are offered with the PLL feature in -1 and -2 speed grades to reduce clock skew and allow clock multiplication. These devices have an "X" suffix in the ordering code (e.g., EPF10K100EQC208-1X). The MAX+PLUS II software now offers design support for all device package options. Table 3 on page 10 shows all of the 2.5-V FLEX 10KE device packages and speed grades.

## **FLEX 10K Product Transitions**

2.5-V EPF10K50E and EPF10K200E devices have migrated from a 0.25-µm process to a 0.22-µm process. All other FLEX 10KE devices are already manufactured on a 0.22-µm process. EPF10K50V devices are migrating from a 0.30-µm 3-layer-metal process to a 0.30-µm 4-layer-metal process in September 2000. 5.0-V EPF10K40 and EPF10K70 devices are migrating from 0.5 µm to 0.42 µm in October and December, respectively. Table 4 on page 10 outlines the process migration schedule and lists the reference documentation associated with this migration. You can download these documents from the Customer Notifications page on the Altera web site at http://www.altera.com.

ACEX 1K devices are now shipping in all packages in the 30,000, 50,000, and 100,000 gate densities. Devices & Tools, continued from page 9

All FLEX 10KE devices are now available in

industrial-temperature

grades.

Table 3. FLEX 10KE Devices

| Device     | Offerings            | Speed<br>Grade |

|------------|----------------------|----------------|

| EPF10K30E  | 144-pin TQFP         | -1, -2, -3     |

|            | 208-pin PQFP         | -1, -2, -3     |

|            | 256-pin FineLine BGA | -1, -2, -3     |

|            | 484-pin FineLine BGA | -1, -2, -3     |

|            | PLL (all packages)   | -1X, -2X       |

| EPF10K50S  | 144-pin TQFP         | -1, -2, -3     |

|            | 208-pin PQFP         | -1, -2, -3     |

|            | 240-pin PQFP         | -1, -2, -3     |

|            | 256-pin FineLine BGA | -1, -2, -3     |

|            | 356-pin BGA          | -1, -2, -3     |

|            | 484-pin FineLine BGA | -1, -2, -3     |

|            | PLL (all packages)   | -1X, -2X       |

| EPF10K100E | 208-pin PQFP         | -1, -2, -3     |

|            | 240-pin PQFP         | -1, -2, -3     |

|            | 256-pin FineLine BGA | -1, -2, -3     |

|            | 356-pin BGA          | -1, -2, -3     |

|            | 484-pin FineLine BGA | -1, -2, -3     |

|            | PLL (all packages)   | -1X, -2X       |

| EPF10K130E | 240-pin PQFP         | -1, -2, -3     |

|            | 356-pin BGA          | -1, -2, -3     |

|            | 484-pin FineLine BGA | -1, -2, -3     |

|            | 600-pin BGA          | -1, -2, -3     |

|            | 672-pin FineLine BGA | -1, -2, -3     |

|            | PLL (all packages)   | -1X, -2X       |

| EPF10K200S | 240-pin RQFP (1)     | -1, -2, -3     |

|            | 356-pin BGA          | -1, -2, -3     |

|            | 484-pin FineLine BGA | -1, -2, -3     |

|            | 600-pin BGA          | -1, -2, -3     |

|            | 672-pin FineLine BGA | -1, -2, -3     |

|            | PLL (all packages)   | -1X, -2X       |

#### Table 4. FLEX 10K Device Migration

| Device     | Core<br>Voltage<br>(V) | Date            | Reference            | Process<br>(µm) |

|------------|------------------------|-----------------|----------------------|-----------------|

| EPF10K10A  | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K30A  | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K50V  | 3.3                    | Done            | PCN 9810             | 0.30 (1)        |

|            |                        | Sept.<br>2000   | PCN 9915             | 0.30 (2)        |

| EPF10K100A | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K10   | 5.0                    | Done            | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K20   | 5.0                    | Done            | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K30   | 5.0                    | Done            | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K40   | 5.0                    | October<br>2000 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K50   | 5.0                    | Done            | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K70   | 5.0                    | Dec.<br>2000    | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K50E  | 2.5                    | Done            | PCN 9911             | 0.22            |

| EPF10K200E | 2.5                    | Done            | PCN 9911             | 0.22            |

#### Notes:

(1) 3-layer metal process.

(2) 4-layer metal process.

#### Table 5. FLEX 10KE Industrial-Temperature **Device Availability**

| Device            | Availability |

|-------------------|--------------|

| EPF10K30EQI208-2  | Now          |

| EPF10K30EFI256-2  | Now          |

| EPF10K50ETI144-2  | Now          |

| EPF10K50EQI240-2  | Now          |

| EPF10K50EFI256-2  | Now          |

| EPF10K50SQI208-2  | Now          |

| EPF10K50SFI484-2  | Now          |

| EPF10K100EQI208-2 | Now          |

| EPF10K100EFI256-2 | Now          |

| EPF10K100EFI484-2 | Now          |

| EPF10K130EQI240-2 | Now          |

| EPF10K130EBI356-2 | Now          |

| EPF10K130EFI484-2 | Now          |

| EPF10K200EBI600-2 | Now          |

| EPF10K200SBI356-2 | Now          |

| EPF10K200SFI672-2 | Now          |

#### Note:

(1) RQFP: power quad flat pack,

## **FLEX 10KE Industrial-Temperature Devices**

All FLEX 10KE devices are now available in industrial-temperature grades. Table 5 lists the industrial-temperature FLEX 10KE devices.

## MAX

## MAX 7000A Devices

The feature-rich MAX<sup>®</sup> 7000A devices support enhanced in-system programmability (ISP), MultiVolt<sup>™</sup> I/O pins, hot-socketing, and pin compatibility with the industry-standard MAX 7000 devices. 3.3-V MAX 7000AE devices range from 32 to 512 macrocells with propagation delays as fast as 4.5 ns. All MAX 7000AE devices are available in industrialtemperature grades. Table 6 shows the commercial package and speed-grade options for MAX 7000AE devices.

## MAX 7000B Devices

2.5-V MAX 7000B devices range from 32 to 512 macrocells with propagation delays as fast as

| Table 6. MAX 7000AE Commercial-Temperature           Devices |                      |              |

|--------------------------------------------------------------|----------------------|--------------|

| Device                                                       | Package              | Speed Grade  |

| EPM7032AE                                                    | 44-pin PLCC (1)      | -4, -7, -10  |

|                                                              | 44-pin TQFP          | -4, -7, -10  |

| EPM7064AE                                                    | 44-pin PLCC          | -4, -7, -10  |

|                                                              | 44-pin TQFP          | -4, -7, -10  |

|                                                              | 49-pin Ultra         | -4, -7, -10  |

|                                                              | FineLine BGA (2)     |              |

|                                                              | 100-pin TQFP         | -4, -7, -10  |

|                                                              | 100-pin FineLine BGA | -4, -7, -10  |

| EPM7128AE                                                    | 84-pin PLCC          | -5, -7, -10  |

|                                                              | 100-pin TQFP         | -5, -7, -10  |

|                                                              | 100-pin PQFP         | -5, -7, -10  |

|                                                              | 144-pin TQFP         | -5, -7, -10  |

|                                                              | 169-pin Ultra        | -5, -7, -10  |

|                                                              | FineLine BGA         |              |

|                                                              | 256-pin FineLine BGA | -5, -7, -10  |

| EPM7256AE                                                    | 100-pin TQFP         | -5, -7, -10  |

|                                                              | 100-pin FineLine BGA | -5, -7, -10  |

|                                                              | 144-pin TQFP         | -5, -7, -10  |

|                                                              | 208-pin PQFP         | -5, -7, -10  |

|                                                              | 256-pin FineLine BGA | -5, -7, -10  |

| EPM7512AE                                                    | 144-pin TQFP         | -7, -10, -12 |

|                                                              | 208-pin PQFP         | -7, -10, -12 |

|                                                              | 256-pin BGA          | -7, -10, -12 |

|                                                              | 256-pin FineLine BGA | -7, -10, -12 |

## Notes:

(1) PLCC: plastic J-lead chip carrier.

(2) Ultra FineLine BGA<sup>™</sup> packages are Altera's 0.8mm pitch BGA packages. 3.5 ns. Additionally, MAX 7000B devices feature enhanced ISP, MultiVolt<sup>™</sup> I/O pins, and pin compatibility with the industry-standard MAX 7000 devices. Table 7 shows all commercial package and speed grade options. All devices are available now. Most MAX 7000B devices are expected to be available in industrial-grade temperature by October 2000. Contact your Altera sales representative for device availability. For more information, see "MAX 7000B Devices Maintain Product-Term Leadership through Innovation & Technology" on page 1.

## MAX 7000S Devices

5.0-V MAX 7000S devices offer features such as 5.0-ns speed grades, in-system programmability

| Device   | Package              | Speed Grade |

|----------|----------------------|-------------|

| EPM7032B | 44-pin PLCC          | -3, -5, -7  |

|          | 44-pin TQFP          | -3, -5, -7  |

|          | 49-pin Ultra         | -3, -5, -7  |

|          | FineLine BGA         |             |

| EPM7064B | 44-pin PLCC          | -3, -5, -7  |

|          | 44-pin TQFP          | -3, -5, -7  |

|          | 49-pin Ultra         | -3, -5, -7  |

|          | FineLine BGA         |             |

|          | 100-pin TQFP         | -3, -5, -7  |

|          | 100-pin FineLine BGA | -3, -5, -7  |

| EPM7128B | 49-pin Ultra         | -4, -7, -10 |

|          | FineLine BGA         |             |

|          | 100-pin TQFP         | -4, -7, -10 |

|          | 100-pin FineLine BGA | -4, -7, -10 |

|          | 144-pin TQFP         | -4, -7, -10 |

|          | 169-pin Ultra        | -4, -7, -10 |

|          | FineLine BGA         |             |

|          | 256-pin FineLine BGA | -4, -7, -10 |

| EPM7256B | 100-pin TQFP         | -5, -7, -10 |

|          | 144-pin TQFP         | -5, -7, -10 |

|          | 169-pin Ultra        | -5, -7, -10 |

|          | FineLine BGA         |             |

|          | 208-pin PQFP         | -5, -7, -10 |

|          | 256-pin FineLine BGA | -5, -7, -10 |

| EPM7512B | 144-pin TQFP         | -5, -7, -10 |

|          | 169-pin Ultra        | -5, -7, -10 |

|          | FineLine BGA         |             |

|          | 208-pin PQFP         | -5, -7, -10 |

|          | 256-pin BGA          | -5, -7, -10 |

|          | 256-pin FineLine BGA | -5, -7, -10 |

MAX 7000B devices feature enhanced ISP, MultiVolt I/O pins, and pin compatibility with the industry standard MAX 7000 devices. Devices & Tools, continued from page 11

(ISP), an open-drain output option, and IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan test circuitry in devices with 128 or more macrocells. All MAX 7000S devices are available in industrial-temperature grades. Table 8 shows the packages and speed grades available in the commercial-temperature grade.

| Table 8. Commercial-Temperature MAX 7000S<br>Devices |                                                             |                                                                              |

|------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|

| Device                                               | Package                                                     | Speed Grade                                                                  |

| EPM7032S                                             | 44-pin PLCC<br>44-pin TQFP                                  | -5, -6, -7, -10<br>-5, -6, -7, -10                                           |

| EPM7064S                                             | 44-pin PLCC<br>44-pin TQFP<br>84-pin PLCC<br>100-pin TQFP   | -5, -6, -7, -10<br>-5, -6, -7, -10<br>-5, -6, -7, -10<br>-5, -6, -7, -10     |

| EPM7128S                                             | 84-pin PLCC<br>100-pin TQFP<br>100-pin PQFP<br>160-pin PQFP | -6, -7, -10, -15<br>-6, -7, -10, -15<br>-6, -7, -10, -15<br>-6, -7, -10, -15 |

| EPM7160S                                             | 84-pin PLCC<br>100-pin TQFP<br>160-pin PQFP                 | -6, -7, -10<br>-6, -7, -10<br>-6, -7, -10                                    |

| EPM7192S                                             | 160-pin PQFP                                                | -7, -10, -15                                                                 |

| EPM7256S                                             | 208-pin PQFP                                                | -7, -10, -15                                                                 |

## MAX 3000A Devices

MAX 3000A devices are the ideal low-cost ISP solution for designers looking for high performance at a low price-per-macrocell. 3.3-V product-term-based MAX 3000A devices are targeted for high-volume, low-cost designs. These devices have an enhanced ISP feature set and range in density from 32 to 256 macrocells (see Table 9) with propagation delays as fast as 4.5 ns.

| Table 9. MAX 3000A Devices |              |             |  |

|----------------------------|--------------|-------------|--|

| Device                     | Package      | Speed Grade |  |

| EPM3032A                   | 44-pin PLCC  | -4, -7, -10 |  |

|                            | 44-pin TQFP  | -4, -7, -10 |  |

| EPM3064A                   | 44-pin PLCC  | -4, -7, -10 |  |

|                            | 44-pin TQFP  | -4, -7, -10 |  |

|                            | 100-pin TQFP | -4, -7, -10 |  |

| EPM3128A                   | 100-pin TQFP | -5, -7, -10 |  |

|                            | 144-pin PQFP | -5, -7, -10 |  |

| EPM3256A                   | 144-pin TQFP | -6, -7, -10 |  |

|                            | 208-pin PQFP | -6, -7, -10 |  |

## CONFIGURATION

## High Density Configuration Devices Coming Soon

The new 4-Mbit EPC4E and 16-Mbit EPC16F configuration devices are scheduled for release in December 2000. These new devices will include features such as faster configuration times, parallel configuration, reprogrammability, and much more. Additionally, you can use a single device to configure several APEX or FLEX devices in parallel to further speed configuration time and board space.

A single EPC16F device will configure two 1.5-million-gate EP20K1500E devices with new data compression options.

## TOOLS

## **Quartus Version 2000.09 Coming Soon**

The Quartus software version 2000.09, which includes the PowerFit fitter, is scheduled to ship to all customers on active subscription in October.

## PowerFit Fitter Provides Dramatic $\mathbf{f}_{\text{MAX}}$ & Compile Time Improvements

The Quartus<sup>TM</sup> software version 2000.09 includes the second generation PowerFit<sup>TM</sup> fitter, to provide optimal placement and fitting for high-density PLD designs. Benchmarks show significant  $f_{MAX}$  improvements coupled with reduced compile times for designs targeting APEX EP20K600E and larger devices. The PowerFit fitter is scheduled to ship to all customers on active subscription in October.

## **New Device Database**

A new Altera-developed database technology will replace the ObjectStore database. This new technology improves installation flows in UNIX environments and reduces UNIX-specific compile time bottlenecks.

## **More Powerful Timing Analysis**

Several new timing analysis assignment options are available in the Quartus software version 2000.09 including those listed in Table 10.

The Quartus software version 2000.09 timing analyzer provides designers the ability to more accurately analyze circuits that include complex clock structures where a clock is derived from another clock using combinatorial logic. Other timing analysis enhancements provide designers the ability to better specify multicycle path relationships. More information on these features will be published at the time of release.

## **Support for Windows 2000**

The Quartus software version 2000.09 and the MAX+PLUS II software version 10.0 are certified to operate on the Windows 2000 operating system. The Quartus and MAX+PLUS II development systems now support the operating systems listed in Table 11.

Table 10. Quartus Software Version 2000.09

| Timing Analysis Assignments |                                                                                          |  |

|-----------------------------|------------------------------------------------------------------------------------------|--|

| Assignments                 | Description                                                                              |  |

| NOT_CLOCK                   | Specifies signal should not be interpreted as a clock                                    |  |

| INVERTED_CLOCK              | Specifies inversion of a<br>derived clock generated with<br>complex logic                |  |

| MIN_TPD_REQUIREMENT         | Specifies the minimum delay<br>required for combinatorial<br>logic between two registers |  |

| HOLD_MULTICYCLE             | Used to enhance support for multicycle timing analysis                                   |  |

| SRC_HOLD_MULTICYCLE         |                                                                                          |  |

| Table 11. Quartus & MAX+PLUS II Operating<br>System Support |                                                                                                                                           |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Software                                                    | Operating System Support                                                                                                                  |  |

| Quartus<br>version 2000.09                                  | Windows 2000, Windows 98,<br>Windows NT version 4.0 and<br>higher, Sun Solaris 2.6 and<br>2.7, HP-UX 10.2x                                |  |

| MAX+PLUS II<br>version 10.0                                 | Windows 2000, Windows 98,<br>Windows NT version 4.0 and<br>higher, Sun Solaris 2.5 and<br>2.6, HP-UX 10.2x, AIX<br>version 4.1 and higher |  |

## Improved Support for Third-Party Simulation & Timing Analysis Tools

To account for the differences in how various EDA tools process verification netlists, the Quartus software now generates verification output netlists that vary depending on the targeted EDA tool. For example, if you select the Model*Sim*-Altera software for the simulation tool and the PrimeTime software for the timing analysis tool, distinct VHDL or Verilog HDL netlists and Standard Delay Format Output Files (.sdo) are placed in unique Model*Sim* and PrimeTime folders. This methodology guarantees accurate results using all third-party simulation and timing analysis tools.

## Block-Level Design Enhanced to Support Third-Party EDA Tools

You can use the **Create HDL Design File for Current File** option (Tools menu) to convert a top-level Block Design File (.bdf) from the Quartus software into a VHDL or Verilog HDL output file. Use any third-party HDL synthesis tool to synthesize the output file.

## **Expanded APEX Device-Package Support**

The Quartus software version 2000.09 supports new devices and packages, which are listed in Table 12.

| Table 12. New Devices Supported by<br>Quartus Version 2000.09 |            |                        |

|---------------------------------------------------------------|------------|------------------------|

| Support                                                       | Device     | Package                |

| Full                                                          | EP20K60E   | 144-pin FineLine BGA,  |

| Compilation,                                                  |            | 324-pin FlneLine BGA,  |

| Simulation,                                                   |            | 356-pin BGA            |

| and                                                           | EP20K100E  | 144-pin FineLine BGA   |

| Programming                                                   |            |                        |

| Support                                                       | EP20K160E  | 144-pin TQFP, 208-pin  |

|                                                               |            | RQFP, 240-pin PQFP,    |

|                                                               |            | 356-pin BGA, 484-pin   |

|                                                               |            | FineLine BGA           |

|                                                               | EP20K600E  | 1,020-pin FineLine BGA |

|                                                               | EP20K1500E | 652-pin BGA, 1,020-pin |

|                                                               |            | FineLine BGA           |

| Compilation                                                   | EP20K30E   | 144-pin TQFP, 144-pin  |

| and                                                           |            | FineLine BGA, 208-pin  |

| Simulation                                                    |            | RQFP, 324-pin FineLine |

| Support                                                       |            | BGA, 356-pin BGA       |

continued on page 14

The MAX+PLUS II software version 10.0 is shipping to all customers with current subscriptions, and features support for the new ACEX 1K device family. Devices & Tools, continued from page 13

## Quartus Software 2000.05 Service Pack 1 Released

The Quartus software version 2000.05 Service Pack 1 was released in July 2000. This service pack is to be used with version 2000.05 of the Quartus software. Service Pack 1 is the first Quartus version to have Windows 2000 certification and includes full support for 23 new APEX 20K and APEX 20KE devices, including the EP20K1500E in a 652-pin BGA package and EP20K1000E-X in 652-pin BGA and 1,020-pin FineLine BGA packages (see Table 13). Customers with an active subscription can download this update from https://websupport.altera.com.

#### MAX+PLUS II Software Supports New ACEX Devices

The MAX+PLUS II software version 10.0 is scheduled to ship with the Quartus software version 2000.09 as a single upgrade package in

|            | ew Devices with Full Support from the<br>tware Version 2000.05 Service Pack 1 |

|------------|-------------------------------------------------------------------------------|

| Device     | Package                                                                       |

| EP20K60E   | 144-pin TQFP (1)                                                              |

|            | 208-pin RQFP (1)                                                              |

|            | 240-pin RQFP (1)                                                              |

| EP20K100   | 144-pin TQFP (2)                                                              |

|            | 208-pin PQFP (2)                                                              |

|            | 240-pin PQFP (2)                                                              |

|            | 324-pin FineLine BGA (2)                                                      |

|            | 356-pin BGA (2)                                                               |

| EP20K200E  | 356-pin BGA (1)                                                               |

| EP20K300E  | 672-pin FineLine BGA (1)                                                      |

| EP20K400   | 652-pin BGA (2)                                                               |

|            | 672-pin FineLine BGA (2)                                                      |

| EP20K1000E | 652-pin BGA (2)                                                               |

|            | 672-pin FineLine BGA (1)                                                      |

|            | 1,020-pin FineLine BGA (1)                                                    |

| EP20K1500E | 652-pin BGA (3)                                                               |

Notes:

- (1) These packages refer to devices either with or without PLLs.

- (2) These packages only refer to devices with PLLs.

- (3) These packages only refer to devices without PLLs.

## Table 14. New Devices with Full Support from theMAX+PLUS II Software Version 10.0

| Device    | Package                    |

|-----------|----------------------------|

| EPM7032B  | 44-pin TQFP                |

|           | 49-pin Ultra FineLine BGA  |

| EPM7064B  | 49-pin Ultra FineLine BGA  |

|           | 100-pin FineLine BGA       |

| EPM7064AE | 49-pin Ultra FineLine BGA  |

| EPM7128B  | 49-pin Ultra FineLine BGA  |

| EPM7256B  | 169-pin Ultra FineLine BGA |

| EPM7512B  | 144-pin TQFP               |

|           | 256-pin BGA                |

|           | 256-pin FineLine BGA       |

|           | 169-pin Ultra FineLine BGA |

| EP1K10    | 100-pin TQFP               |

|           | 144-pin TQFP               |

|           | 208-pin PQFP               |

|           | 256-pin BGA                |

October 2000. This release features new device support for many MAX 7000B devices and packages as well as ACEX EP1K10 devices (see Table 14).

## World Class Synthesis & Simulation Tools Now Shipping

Synopsys FPGA *Express*-Altera version 3.4, Exemplar Logic LeonardoSpectrum-Altera version 1999j, and Model Technology Model*Sim*-Altera version 5.3 are shipping to all customers on active subscription. These products provide access to world class HDL synthesis and simulation tools to all of Altera's customers on active subscription. For more information on these tools, or to obtain a license file, visit the Altera web site at http://www.altera.com.

Design Tips

## **Using Ternary Content Addressable Memory**

Altera's APEX<sup>TM</sup> 20KE devices contain embedded content addressable memory (CAM) that supports a number of different design configurations. APEX 20KE CAM supports ternary operation, where user-programmable memory bits can store 0, 1, or "don't care" values. "Don't care" values force the CAM blocks to produce a match when either a 0 or a 1 is presented as an input signal and can be used for many applications, such as masking fields in Internet protocol addresses. The "don't care" feature is a very flexible feature that is not supported by any other programmable logic vendor. "Don't care" values can be written to APEX 20KE devices with the following three methods:

- Memory Initialization File (.mif)

- initialization method

- wrx port method

- pattern port method

## **MIF Initialization Method**

The easiest way to store "don't care" values in CAM is to initialize the CAM with a MIF. The MIF allows you to enter both "don't care" values and normal pattern values into CAM. Figure 1 shows a MIF and illustrates how "don't care" values are initialized in a CAM block.

In Figure 1, the MIF contains "don't care" values, denoted by an X. A "don't care" value of

continued on page 16

| Addr | +0       | +1       | +2        | +3       | +4        | +5       | +6       | +7       |

|------|----------|----------|-----------|----------|-----------|----------|----------|----------|

| 0    | 00000001 | 00000002 | 00000003  | 00000004 | 00000005  | 00000006 | 00000007 | 00000008 |

| 8    | 00000008 | 0000000A | 0000000B  | 0000000C | 0000000D  | 000000E  | 0000000F | 00000010 |

| 16   | 00000011 | 00000012 | 00000013  | 00000014 | 00000015  | 00000016 | 00000017 | 00000018 |

| 24   | 00000019 | 0000001A | 0000001 B | 0000001C | 0000001 D | 0000001F | 00000100 | XXXXFFFF |

Design Tips: Ternary Content Addressable Memory, continued from page 15

XXXXFFFF is written to address 24. Therefore, any patterns between 0000FFFF and FFFFFFFF will produce matches at address 24.

#### wrx Port Method

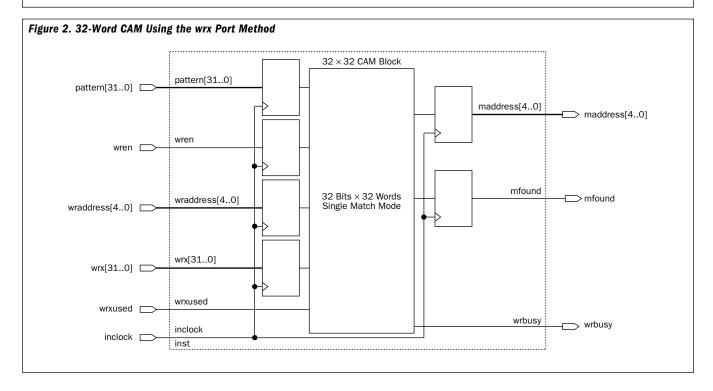

In most designs, the system must update the CAM's contents after the device has been configured. The CAM MegaWizard® Plug-In can create a wrx port and a wrxused port to write "don't care" values to a CAM block after configuring the device. Figure 2 shows a 32-word CAM block generated by the MegaWizard Plug-In that uses the wrx port and the wrxused port to write "don't care" values.

A CAM block configured with the wrx port method requires three clock cycles to write a "don't care" value. Bits configured as normal bits are written with the pattern bus, and bits configured as "don't care" bits are set high on the wrx bus. For example, you can write a value of BX to CAM by placing a value of B0 on the pattern bus and 0F on the wrx bus. Figure 3 shows how to write a "don't care" value of 000000BX to CAM at address location 7.

The wrx port method provides a simple method for writing "don't care" values to a CAM. Bits

that will be "don't care" bits are set to 1 on the wrx bus. The 32-word CAM block shown in Figure 2 is capable of running at speeds in the range of 100 MHz. This speed is sufficient for many designs. If your design requires CAM to operate at frequencies faster than 100 MHz, use the pattern port method.

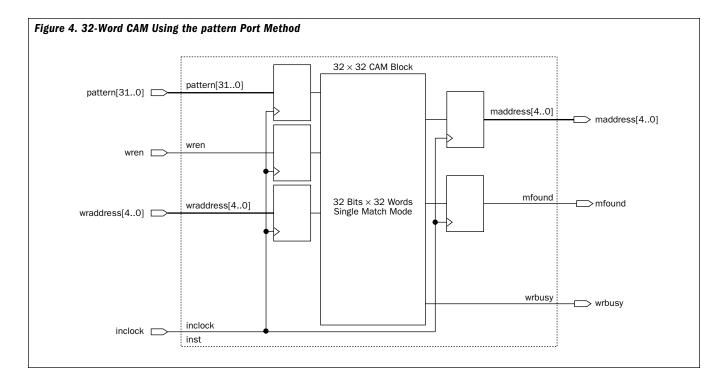

## pattern Port Method

"Don't care" values can also be written with the pattern port. The pattern port method requires less logic than the wrx port method and can run at faster clock frequencies. However, writing the "don't care" bits is slightly more complicated. Figure 4 shows a MegaWizard instantiation of a 32-word CAM block that does not use the wrx port or the wrxused port.

In Figure 4, "don't care" values can be written in three clock cycles. A normal bit is written to the CAM by writing a 0 or a 1 to the normal bit on the first clock cycle and by writing a 0 or a 1 to the normal bit on the third clock cycle. You can write a "don't care" bit to the CAM by writing a 0 to the "don't care" bit on the first clock cycle and a 1 to the "don't care" bit on the third clock cycle. Table 1 shows how to write a value of 000000BX to the CAM at address location 7.

In Table 1 on page 17, since bits [3..0] need to be "don't care" values, a 0 is written to each

|            | Name        | 0 ps | 10.0 ms  | 20.0 ms | 30.0 ms | 40   |

|------------|-------------|------|----------|---------|---------|------|

|            |             | _    |          |         |         |      |

| 1          | linclock    |      |          |         |         |      |

| <b>D</b> 2 | wren        |      |          |         |         |      |

| 2          | + wraddress |      | 7        |         | X       |      |

| <b>1</b>   | + pattern   |      | 00000080 |         | X 00000 | 00 ) |

|            | woused      |      |          |         |         |      |

| <b>P</b>   | 🛨  wix      |      | 0000000F |         | X       |      |

| 9          | + maddress  |      |          |         | 0       |      |

| 02         | Infound     | _    |          |         | 1       | 1    |

| Table 1. Writing into CAM |                  |                  |                  |  |  |

|---------------------------|------------------|------------------|------------------|--|--|

| Port                      | Clock<br>Cycle 1 | Clock<br>Cycle 2 | Clock<br>Cycle 3 |  |  |

| wren                      | 1                | 0                | 1                |  |  |

| pattern                   | 000000B0         | ບບບບບບບບ (1)     | 000000BF         |  |  |

| wraddress                 | 7                | 7                | 7                |  |  |

#### Note:

(1) The pattern value on the second clock cycle is not written to CAM; therefore, you can apply any data value to the pattern bus during this clock cycle.

of these bits' locations on the first clock cycle and a 1 is written to each of these bits' locations on the third clock cycle. Also, since bits [7..4] need to be set to B, a B is written to each of these bits on the first clock cycle and on the third clock cycle. Finally, since bits [31..8] need to be all 0s, a 0 is written to the CAM on both the first and third clock cycles.

Writing "don't care" values to CAM using the pattern port method is slightly more complicated than the wrx port method. However, the pattern port method significantly increases the CAM's overall performance. The pattern port method eliminates the critical path caused by the wrx port, thereby increasing performance. The 32 × 32 CAM block shown in Figure 4 will run at 160 MHz compared to the CAM block shown in Figure 2 that runs at 100 MHz.

You should choose which method will adapt best to your design. Designs that require a simple method of writing "don't care" values should use the wrx port method. Since very little decoding is required to write an X value to the CAM, the wrx port method is simple. You should consider using the pattern port method for designs that are speed-critical. The pattern port method requires somewhat more complex user logic, but the pattern port method significantly increases the CAM's overall speed.

## Conclusion

APEX 20KE devices contain high-speed CAM that can be used for a wide variety of applications. Altera's CAM can store "don't care" values with three separate methods, each of which has different benefits. The MIF initialization method is the easiest method to use. However, if your design requires you to write "don't care" values to the CAM after device configuration, you can write these values with the wrx port method or, for highfrequency designs, the pattern port method.

Altera has entered into

**OEM Licensing Details for Mentor Graphics Software**

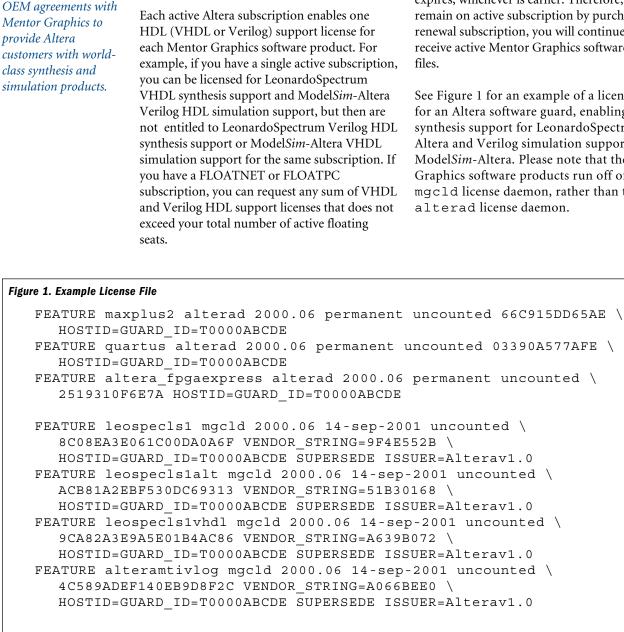

All Altera customers on active subscription have received the LeonardoSpectrum for Altera and ModelSim-Altera software with their Altera software products. You can request license files to enable these tools on the Altera web site (http://www.altera.com).

The license file FEATURE lines for the Mentor Graphics software products differ from the Altera and Synopsys OEM FEATURE lines. The Mentor Graphics software licenses expire 15 months from the date you request a license or from the date your Altera subscription expires, whichever is earlier. Therefore, if you remain on active subscription by purchasing a renewal subscription, you will continue to receive active Mentor Graphics software license

See Figure 1 for an example of a license file for an Altera software guard, enabling VHDL synthesis support for LeonardoSpectrum for Altera and Verilog simulation support for ModelSim-Altera. Please note that the Mentor Graphics software products run off of the mgcld license daemon, rather than the alterad license daemon.

# **Customer** Application

## LGIC Uses FLEX Devices to Pioneer Broadband CDMA WLL System

In the wireless world, the demand for advanced information services is growing. Voice and low-rate data services are insufficient in a world where high-speed Internet access is taken for granted. The trend is toward global information networks that offer flexible multimedia information services to users on demand, anywhere, anytime. The need to support bandwidth-intensive multimedia services places new and challenging demands on cellular systems and networks.

## **Evolving Standards Need Flexible Solutions**

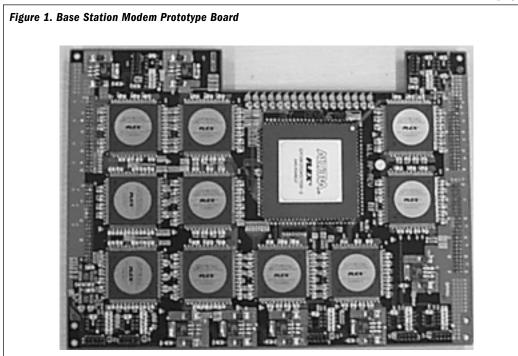

LG Information & Communications, Ltd. (LGIC) is the biggest supplier of code division multiple access (CDMA) infrastructure equipment to the largest cellular operator in Korea, and is one of the biggest handset suppliers to major operators such as Bell Atlantic Mobile, Airtouch, Sprint, and Telesp. In 1997, five companies—including LGIC began developing a wideband CDMA (W-CDMA) modem for wireless local loop (WLL) service for Hanaro Telecom. Because the service standard was still under development, LGIC decided to use Altera FLEX® 10K devices to build their prototype system. The other four companies decided to use ASICs.

LGIC's initial prototype used four EPF10K100GC503-3 devices in each modem. Because of the modem complexity and because the standard was evolving, the engineers had to carefully fine-tune the design. Unfortunately, fine-tuning could not be tested with computer simulation; it had to be checked in-system. Because the Altera devices were reconfigurable, the LGIC designers could make changes quickly and see the results. In contrast, when the ASICs used by the competing companies began to have various problems, the ASICs had to be refabricated several times, wasting considerable time and money.

LGIC's second prototype had additional features and used EP10K100A and EPF10K250A devices for both the base station and the terminals. The operating clock frequency was more than 60 MHz, and the devices implemented key

continued on page 20

LGIC is upgrading their system design and will use Altera APEX<sup>TM</sup> devices in upcoming revisions. LGIC Uses FLEX Devices to Pioneer Broadband CDMA WLL System, continued from page 19

functions of the modem such as the searcher, finger, Viterbi decoder, combiner, and FIR filters.

"The device usage was mostly more than 90%, but we still managed to do a very good job," stated Kim Youn Hwan, a senior research design for LGIC. "It was really exciting that we did such a hard thing. Furthermore, because the MAX+PLUS II software had such good performance and was so easy to use, we didn't use any other third-party tools for VHDL synthesis."

In the Hanaro Telecom field tests, LGIC engineers used thousands of FLEX 10K devices. After successful field testing, LGIC built an ASIC to be used in the production system. Because of the performance and stability of the system, Hanaro Telecom chose LGIC as the provider of Korea's WLL systems and subscriber units.

#### Looking Forward: IMT-2000

The International Telecommunications Union (ITU), under an initiative named IMT-2000, devised a number of standards that support emerging third-generation wireless requirements. However, these standards will continue to evolve as new services and technologies are identified. Systems that implement these standards must be flexible enough to accomodate changes easily. Because of LGIC's success in Korea with W-CDMA WLL, the company is well-positioned to expand their products to support third-generation wireless communications such as IMT-2000.

LGIC is upgrading their system design and will use Altera APEX<sup>TM</sup> devices in the next revision. "We expect the high-performance APEX devices will help us improve the system, and we are also impressed by the powerful Quartus<sup>TM</sup> software," Kim Youn Hwan said. "I definitely think that the APEX/Quartus combination will be a good choice."

## **Discontinued Devices Update**

Altera distributes advisories (ADVs) and product discontinuance notices (PDNs) that provide information on discontinued devices. To obtain a copy of a specific ADV or PDN, contact your local Altera® sales representative. Selected ADVs, PDNs, and a complete listing of discontinued devices are also available on Altera's web site at http://www.altera.com. Rochester Electronics, an after-market supplier, offers many discontinued Altera products. Contact Rochester Electronics at (978) 462-9332 or go to their web site at http://www.rocelec.com.

# ContributedArticle

## JTAG Technologies Adds Jam STAPL Support to On-Board Programming Software

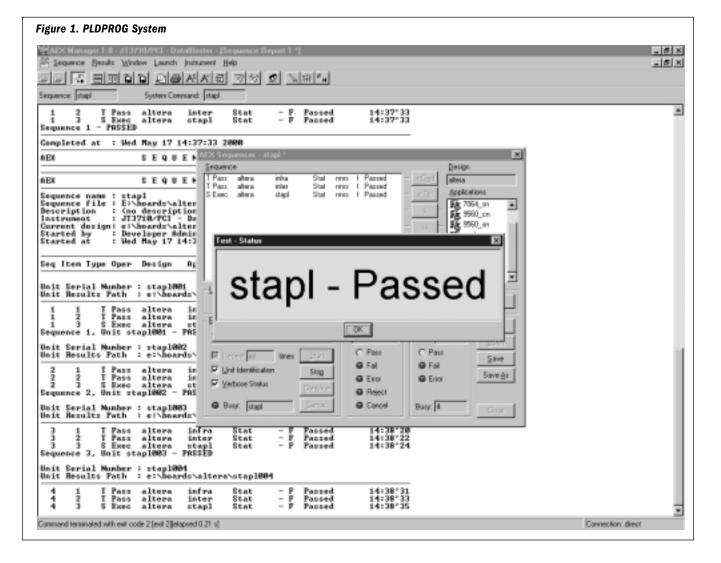

JTAG Technologies has added Jam<sup>™</sup> Standard Test and Programming Language (STAPL) support to PLDPROG, its on-board programming solution for Altera® programmable logic devices (PLDs). With this product line extension, JTAG Technologies allows users to choose any of the popular PLD programming formats within boundary-scan designs of virtually any level of complexity.

## **PLD Programming Development**

PLD programming support from JTAG Technologies now includes the Jam STAPL standardized format as well as the prior JEDEC and Serial Vector File (.svf) formats. As a result, JTAG Technologies provides in-system programmability (ISP) for all Altera MAX® 7000A, MAX 7000B, MAX 7000S, MAX 9000, MAX 3000A, and EPC2 devices. Regardless of the device type or format used, the system presents a common interface to the user, avoiding a proliferation of tools throughout the organization. The system allows the rapid creation of files that perform all on-board device operations, such as erase, blank-check, programming, verification, security fuse programming, and user-code readback. JTAG Technologies tools also provide JTAG-based in-circuit reconfigurability (ICR) support for ACEX<sup>TM</sup> 1K, APEX<sup>TM</sup> 20K, APEX 20KE, FLEX® 10K, and FLEX 10KE devices.

The PLDPROG system handles a wide variety of scan chain configurations, ranging from a simple single chain structure up to multi-chain, multi-level hierarchical scan architectures. Scan chains of any length are possible, with automatic, safe board configuration during PLD programming. The software's graphical user interface (GUI) guides the developer in verifying boundary-scan description language (BSDL) files, testing the board's boundary-scan chain, and performing the programming functions.

#### **Production Support**

PLD programming applications run on a wide variety of fully-compatible hardware controllers in a broad range of operating environments. Interfaces are available for peripheral component interconnect (PCI), ISA, universal serial bus (USB), VXI, and PC parallel port. The production environments include:

- Stand-alone PC or work stations with a convenient GUI for sequencing desired operations

- Full integration within an existing production step, such as functional test, through delay-locked loop (DLL)-based applications

- Support for incorporating PLD programming within a National Instruments LabWindows/CVI or LabView platform

- Client/server operation, in which the boundary-scan software and hardware are controlled within a single computer or across a network

The JTAG Technologies tools allow designers to properly sequence PLD programming with other powerful boundary-scan applications, board testing, and in-system flash programming. Multiple authorization levels are provided for operators, technicians, and engineers. Production personnel benefit from having quick and easy controls, typically via single-button operation, along with execution reports that summarize the results.

## **About JTAG Technologies**

JTAG Technologies was founded in 1993 and focuses its R&D effort at providing powerful, cost-effective boundary-scan solutions for electronics producers. Corporate headquarters are in Eindhoven, the Netherlands, with a US

JTAG Technologies Adds Jam STAPL Support to On-Board Programming Software, continued from page 21

Customer Support Center in Stevensville, MD, and a regional office in the United Kingdom. The company maintains an experienced staff of Development Engineers and Application Engineers to support customer needs, and is represented by authorized distributors around the world. There are now over 1,200 JTAG Technologies systems in operation around the world.

JTAG Technologies Headquarters: ++31 40 295 0870 Toll-free in the US and Canada: (877) FORJTAG (367-5824) United Kingdom: 01234 27 22 26 Email: info@jtag.nl Web site: http://www.jtag.com

# Technical Articles

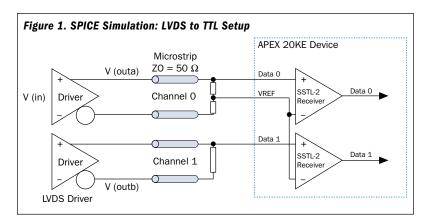

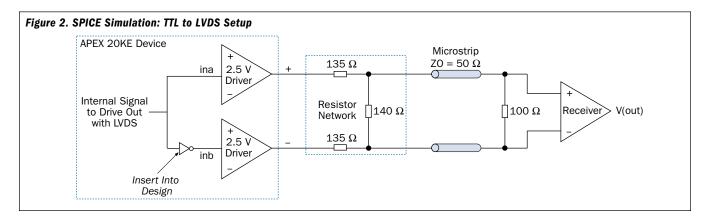

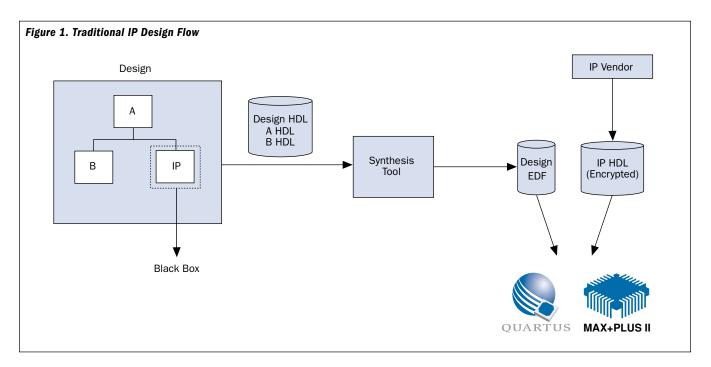

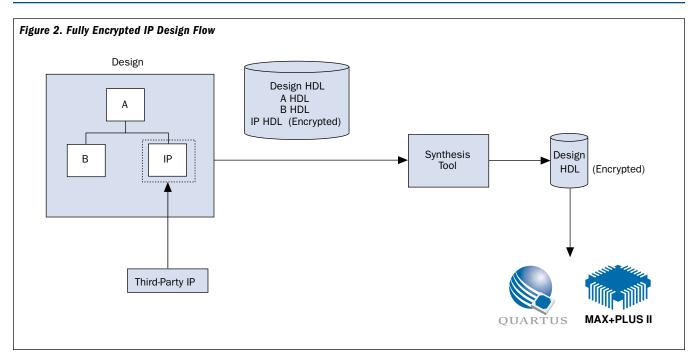

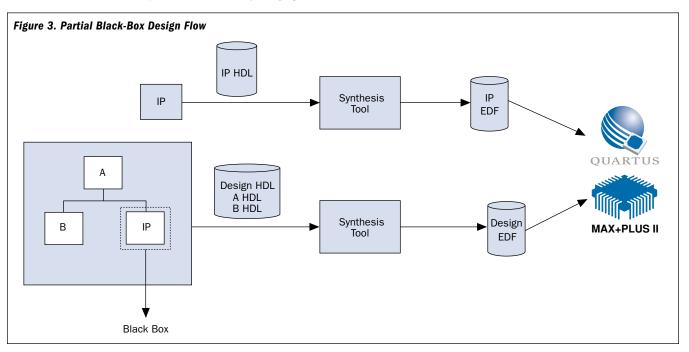

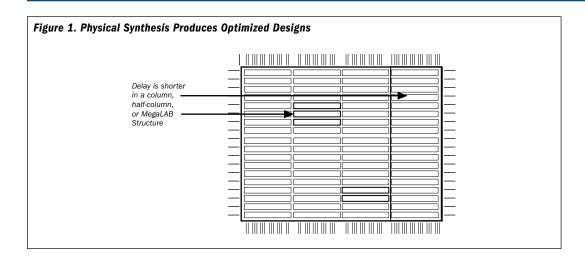

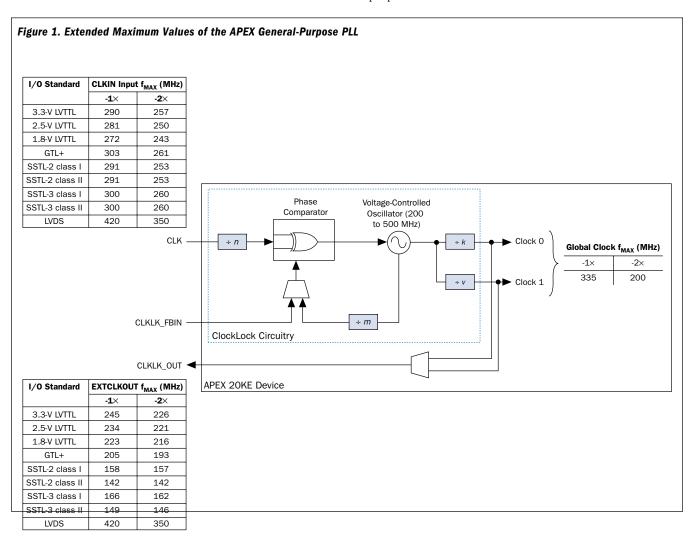

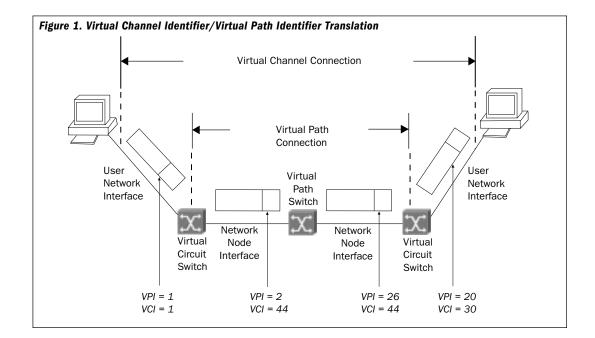

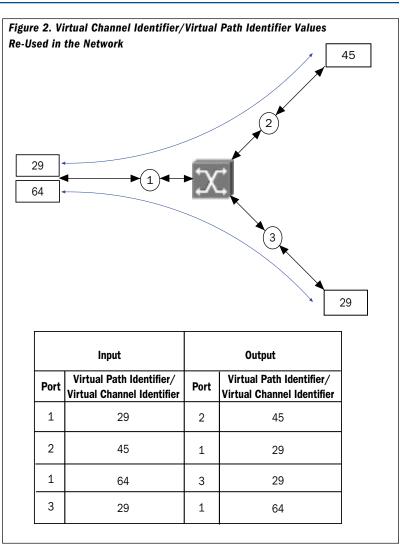

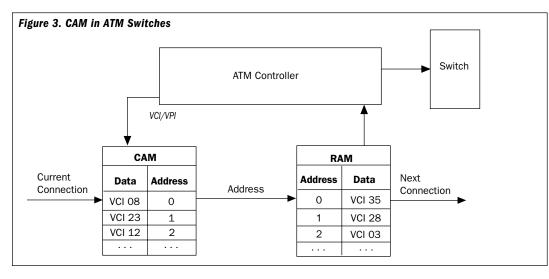

## Implementing LVDS Interfaces with General-Purpose I/O Pins