# Quartus Version 2000.09 Dramatically Improves f<sub>MAX</sub> & Compile Times

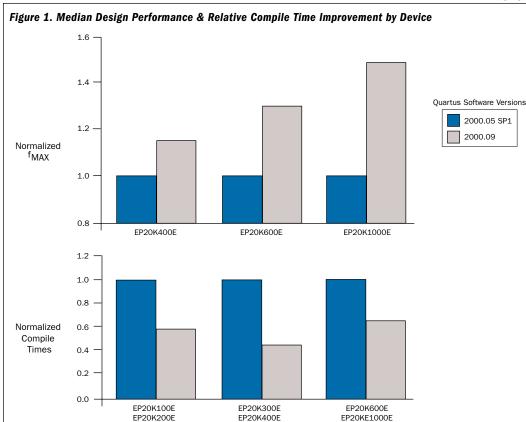

The Quartus<sup>TM</sup> software version 2000.09 includes the new PowerFit<sup>TM</sup> fitter that delivers an average of 15% to 45% faster  $f_{MAX}$  and 1.5× to 3.0× faster compile times for designs targeting APEX<sup>TM</sup> EP20K400E and larger devices. This new PowerFit fitter technology optimizes designs based on the user's timing specifications and meets design requirements with only minimal user effort.

Figure 1 shows the design performance enhancements and compile time reductions

achieved with the PowerFit technology. The charts in Figure 1 demonstrate these improvements over a design set compiled using random pin assignments in the Quartus software versions 2000.05 Service Pack 1 and 2000.09.

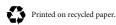

With each new release, the Quartus software has consistently improved compile times. Figure 2 on page 4 highlights compile time improvements for designs targeting high-density devices.

continued on page 4

#### **Inside This Issue:**

- APEX 20KC Devices with All-Layer Copper Interconnect Enhance Internal Performance by 25% to 35%, pg. 5

- ARM- & MIPS-Based Excalibur Products Provide Industy-Leading Performance & Flexibility, pg. 8

M-NV-Q400-01

# Table of Contents

#### Features

| Quartus Version 2000.09 Dramatically Improves |

|-----------------------------------------------|

| f <sub>Max</sub> & Compile Times 1            |

| APEX 20KC Devices with All-Layer Copper       |

| Interconnect Enhance Internal Performance     |

| by 25% to 35%5                                |

| ARM- & MIPS-Based Excalibur Products Provide  |

| Industry-Leading Performance & Flexibility 8  |

| Design Tips:                                  |

| Designing Memory-Mapped Peripherals           |

| for the Nios Embedded Processor15             |

| Customer Application:                         |

| OMEGA-TECHNOLOGIES S.A.: APEX Device          |

| Doubles Processing Power in Signal            |

| Processing Application19                      |

| Contributed Article:                          |

| Multi-Channel, Full-Duplex ADPCM Solutions    |

| from ISS for APEX, ACEX & FLEX Devices        |

|                                               |

#### Altera News

| MAX 7000B: I/O Standards for High-Speed |    |

|-----------------------------------------|----|

| Applications                            | 27 |

| MAX 7000B Devices Outperform the        |    |

| Competition                             | 28 |

| MAX EPM7128 Celebrates 50 Million Units | 29 |

|                                         |    |

#### **Devices & Tools**

| Discontinued Devices Update                     | 7    |

|-------------------------------------------------|------|

| Introducing New APEX 20KC Devices               | . 10 |

| All 10 APEX 20KE Devices Now Shipping           |      |

| LVDS & PLL Support Now Available in Industrial- |      |

| Speed-Grade Devices                             | . 10 |

| APEX 20KE Production Devices                | 10  |

|---------------------------------------------|-----|

| 5.0-V Tolerant APEX 20K & APEX 20KE Devices | 10  |

| APEX 20K Product Transition                 | 11  |

| ACEX 1K Devices Shipping Now                |     |

| Broad Range of FineLine BGA Packages        |     |

| <b>v</b>                                    | 10  |

| Available for MAX Devices                   |     |

| MAX 7000B Industrial-Grade Availability     | 12  |

| MAX 7000AE Devices Migrate to               |     |

| Advanced Process                            | 12  |

| High-Density Configuration Devices          |     |

| Coming Soon                                 | 13  |

| Quartus Version 2000.09 & MAX+PLUS II       |     |

| Version 10.0 Now Available                  | 13  |

| Operating System Update                     | 14  |

| Quartus Roadmap                             |     |

| MAX+PLUS II BASELINE, E+MAX & ASAP2         | ± . |

|                                             |     |

| Version 10.0 Now Available                  | 14  |

| Download the Latest OEM Synthesis &         |     |

| Simulation Tools                            | 14  |

|                                             |     |

#### **Technical Articles**

| Designing Switches & Routers with APEX CAM 22 | 2 |

|-----------------------------------------------|---|

| LVDS Timing Analysis                          | 5 |

| Questions & Answers                           | 9 |

#### In Every Issue

| New Altera Publications       | . 32 |

|-------------------------------|------|

| Current Software Versions     | . 32 |

| Altera Programming Support    | . 33 |

| How to Contact Altera         | . 35 |

| Altera Device Selection Guide | . 36 |

Altera, ACCESS, ACEX, ACEX 1K, AMPP, APEX, APEX 20K, APEX 20KC, APEX 20KE, Atlas, BitBlaster, ByteBlaster, ByteBlaster, MV, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, E+MAX, Excalibur, FastTrack, FineLine BGA, FLEX, FLEX 10KE, FLEX 10KA, FLEX 8000, FLEX 6000, FLEX 6000A, IP MegaStore, Jam, MasterBlaster, MAX, MAX 9000, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000B, MAX 7000B, MAX 9000A, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000B, MAX 9000A, MAX 9000A, MAX 4000A, MAX 7000E, MAX 7000B, MAX 7000B, MAX 7000B, MAX 9000A, MAX 9000A, MAX 9000A, MAX 9000A, MAX 7000E, MAX 7000B, MAX 7000B, MAX 7000B, MAX 9000A, M

Rhonda Scott, Publisher Greg Steinke, Technical Editor 101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 **n\_v@altera.com**

Copyright © 2000 Altera Corporation. All rights reserved.

provided solely as an estimate to the reader.

*Quartus Version 2000.09 Dramatically Improves*  $f_{MAX} & Compile Times, continued from page 1$

#### **PowerFit Technology Improves Device Fitting**

The PowerFit technology dramatically enhances the stability of the fitter as well as device fitting, particularly for the highest density APEX 20KE devices. This enhancement allows designers to fit larger designs into a given APEX device.

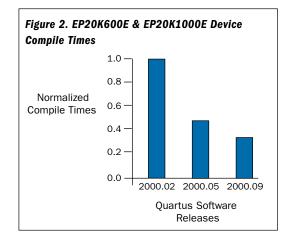

#### UNIX Installation & Compile Time Improvements

In addition to the PowerFit technology improvements, the Quartus software version 2000.09 includes new database technology developed by Altera. This database technology simplifies installation in UNIX environments and reduces UNIX-specific compile time bottlenecks.

Figure 3 shows the PC and UNIX compile time improvements.

With previous versions of the Quartus software, high-density designs took longer to compile on Solaris platforms. The Quartus software version 2000.09 eliminates this problem through Solaris compiler optimization. The Quartus software version 2000.09 for Solaris offers compile times over 8× faster than version 2000.02.

Compile times for the Quartus software version 2000.09 for Solaris are now only 1.15× longer than PC compile times (SPECint normalized to account for performance differences in PC- and UNIX-based processor architectures).

#### **Reduced Memory Requirements**

The minimum physical RAM required to compile high-density APEX devices drops significantly with the Quartus software version 2000.09.

The Quartus software version 2000.05 required 1,331 Mbytes of RAM to compile large EP20K1000E and EP20K1500E devices. The Quartus software version 2000.09 enables mainstream PCs using Windows NT to compile designs for the largest APEX 20KE devices without this high memory requirement. Table 1 lists the memory requirements for the Quartus software version 2000.09.

| Table 1. Quartus 2000.09 Memory Requirements |                      |  |  |

|----------------------------------------------|----------------------|--|--|

| Device                                       | Minimum Physical RAM |  |  |

| EP20K30E                                     | 256 Mbytes           |  |  |

| EP20K60E                                     |                      |  |  |

| EP20K100E                                    |                      |  |  |

| EP20K160E                                    |                      |  |  |

| EP20K200E                                    |                      |  |  |

| EP20K300E                                    | 512 Mbytes           |  |  |

| EP20K400E                                    |                      |  |  |

| EP20K600E                                    |                      |  |  |

| EP20K1000E                                   | 1,024 Mbytes         |  |  |

| EP20K1500E                                   |                      |  |  |

#### **HP-UX 11.0 Support Now Available**

The Quartus development tool is now available for both the HP-UX 11.0 and 10.2 operating systems. HP-UX versions of the software are not included in Altera's standard software shipments. If you have an active FLOATNET subscription and would like to receive the Quartus development tool for HP-UX, fill out the on-line request form on the Altera web site at http://www.altera.com/hpux, and the software will be sent to you.

#### **Timing Analysis Enhancements**

The Quartus software version 2000.09 includes timing analysis enhancements that make it easier to analyze circuits with complex clocking structures as well as specify multicycle path relationships. The Quartus software version 2000.09 optimizes support for thirdparty simulation and timing analysis tools by creating distinct VHDL or Verilog HDL verification netlists and Standard Delay Format Files (.sdo) targeted to specific third-party tools.

#### **Third-Party Integration Enhancements**

Top-level block design schematic files can now be converted to VHDL or Verilog HDL design files using the Quartus software version 2000.09. The VHDL or Verilog output files can be processed by third-party synthesis and simulation tools. The Quartus software version 2000.09 also facilitates the use of encrypted Altera intellectual property (IP) MegaCore® functions through third-party synthesis tools to produce optimal results. For more information on these features, visit the Altera web site at http://www.altera.com.

# APEX 20KC Devices with All-Layer Copper Interconnect Enhance Internal Performance by 25% to 35%

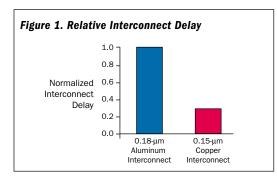

The new APEX<sup>TM</sup> 20KC devices are the first programmable logic devices (PLDs) with an alllayer copper metal interconnect, providing a 25% to 35% performance advantage over 0.18-µm-based devices using aluminum interconnect (see Figure 1).

Because of the relatively small routing delays with copper, APEX 20KC devices can support the high-bandwidth needs of advanced networking standards that exist in the communication marketplace. APEX 20KC devices provide a feature set comparable to APEX 20KE devices, including content-addressable memory (CAM), True-LVDS<sup>™</sup> circuitry, and advanced clock management. These features make APEX 20KC devices the industry-leading, high-density device for high-end system-on-a-programmable-chip (SOPC) solutions.

#### **All-Layer Copper Interconnect**

Breakthroughs in semiconductor performance have been primarily in transistor fabrication. However, in advanced processes, a large portion of chip delays are due to routing structure delays, not transistors. Therefore, significant performance enhancements can be achieved by replacing aluminum—which is traditionally used in routing structures—with a superior conductor of electricity that significantly decreases routing delays and increases overall system performance. 0.15-µm all-layer copper interconnectbased APEX 20KC devices offer a 25% to 35% performance improvement over 0.18-µm-based devices. APEX 20KC Devices with All-Layer Copper Interconnect Enhance Internal Performance by 25% to 35%, continued from page 5

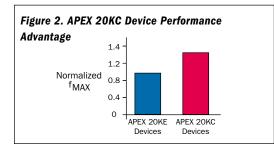

The primary benefit of using copper for the interconnect layers is improved internal performance. For example, APEX 20KC devices with all-layer copper interconnect technology provide a 25% to 35% performance advantage over the aluminum interconnects found in APEX 20KE devices (see Figure 2). A faster interconnect increases the operating frequencies of designs.

#### All-Layer Copper Interconnect vs. Partial Copper Interconnect

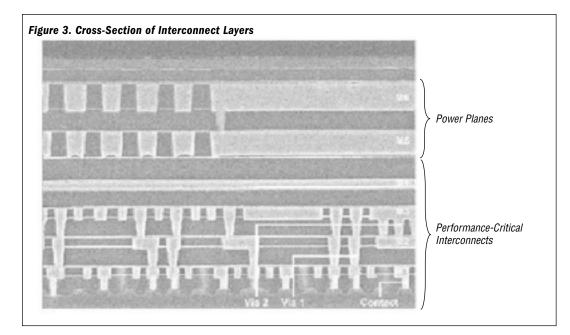

All-layer copper interconnect technology uses copper for all metal layers. Partial copper interconnect has copper on the top layers only.

The top layers are power planes, while the bottom layers are performance-critical interconnect layers. Figure 3 shows a crosssection of these interconnect layers.

Copper on the top layer only does not offer a significant performance increase because these power layers do not have a major impact on performance. In fact, using copper on the top two layers will create silicon/copper design challenges without providing significant performance benefits. Only the all-layer copper interconnect, including the performance-critical bottom layers, will lead to a significant performance advantage.

#### **APEX 20KC Process Technology**

APEX 20KC devices will be fabricated on a state-of-the-art 0.15-µm, 8-layer metal process with a copper interconnect. This more advanced process technology and all-layer copper interconnect will provide significant performance advantages over APEX 20KE devices.

#### **APEX 20KC Device Offering & Features**

APEX 20KC devices will continue Altera's leadership in density and user I/O pins. The

The largest APEX 20KC device will have 1.5 million system gates and more than 800 user I/O pins.

APEX 20KC devices

True-LVDS circuitry,

CAM, PLLs, and

advanced I/O

standards.

will support

largest APEX 20KC device will have 1.5 million system gates and more than 800 user I/O pins. Table 1 outlines the APEX 20KC device features.

APEX 20KC devices will have many of the same features as APEX 20KE devices, including True-LVDS circuitry, CAM, phase-locked loops (PLLs), and advanced I/O standards.

#### True-LVDS Support

APEX 20KC devices will support True-LVDS circuitry up to 840 megabits per second (Mbps), which make them ideal for advanced network protocols that require high data transfer rates.

#### Content Addressable Memory

APEX 20KC devices will support CAM applications in embedded system blocks (ESBs). The copper interconnect of APEX 20KC devices will further reduce access times and make highspeed CAM applications possible in Altera devices without the use of external CAM chips.

#### Phase-Locked Loops

APEX 20KC PLLs will offer higher operating frequency ranges than the APEX 20KE PLLs.

#### Advanced I/O Standards

APEX 20KC devices will support all APEX 20KE advanced I/O standards, including HSTL, GTL+, and SSTL.

Advanced feature support, high density, and fast performance make APEX 20KC devices ideal for SOPC applications.

#### **Software Support & Device Availability**

APEX 20KC devices will be supported in Altera's industry-leading Quartus<sup>™</sup> software by the end of 2000. Devices will be available in the first half of 2001.

| Table 1. APEX 20KC Device Overview |                         |                         |                     |      |                  |

|------------------------------------|-------------------------|-------------------------|---------------------|------|------------------|

| Device                             | Maximum<br>System Gates | Logic Elements<br>(LEs) | Maximum<br>RAM Bits | PLLs | Speed Grades (1) |

| EP20K100C                          | 263,000                 | 4,160                   | 53,248              | 2    | -7, -8, -9       |

| EP20K200C                          | 526,000                 | 8,320                   | 106,496             | 2    | -7, -8, -9       |

| EP20K400C                          | 1,052,000               | 16,640                  | 212,992             | 4    | -7, -8, -9       |

| EP20K600C                          | 1,537,000               | 24,320                  | 311,296             | 4    | -7, -8, -9       |

| EP20K1000C                         | 1,772,000               | 38,400                  | 327,680             | 4    | -7, -8, -9       |

| EP20K1500C                         | 2,392,000               | 51,840                  | 442,368             | 4    | -7, -8, -9       |

Note:

(1) The -7 speed grade is the fastest speed grade.

## **Discontinued Devices Update**

Altera distributes advisories (ADVs) and product discontinuance notices (PDNs) that provide information on discontinued devices. To obtain a copy of a specific ADV or PDN, contact your local Altera® sales representative. Selected ADVs, PDNs, and a complete listing of discontinued devices are also available on Altera's web site at http://www.altera.com. Rochester Electronics, an after-market supplier, offers many discontinued Altera products. Contact Rochester Electronics at (978) 462-9332 or go to their web site at http://www.rocelec.com.

# ARM- & MIPS-Based Excalibur Products Provide Industry-Leading Performance & Flexibility

Altera's Excalibur<sup>TM</sup> embedded microprocessorbased products are the first in the industry to combine the design flexibility of programmable logic with high-performance embedded processors, large on-chip SRAM memory arrays, and peripherals that are essential for systemlevel design. Altera has licensed both a MIPS32<sup>TM</sup> 4Kc<sup>TM</sup> processor core from MIPS® Technologies and an ARM922 core from ARM® Ltd., two of the most widely used instruction set architectures in the embedded systems market. These cores eliminate customer processor licensing and per-unit royalties; Altera takes care of these business issues and offers standard products that customers can immediately design for faster time-to-market.

Altera's ARM-based Excalibur products will be available in Q1 of 2001, followed by the MIPSbased products in Q2 of 2001. Both Excalibur products have hardmacro processor implementations for maximum performance and will operate at 200-MHz processor clock frequencies. Both ARM- and MIPS-based Excalibur products include on-chip single port memory (up to 256 Kbytes), dual-port memory (up to 128 Kbytes), external flash memory support (up to 32 Mbytes), and an SDRAM controller capable of supporting up to 512 Mbytes of 133-MHz (PC133) external memory or up to 256 Mbytes of 266-MHz (PC266) double data rate (DDR) external memory.

On-chip peripherals include interrupt controllers, universal asynchronous receiver / transmitters (UARTs), general purpose timers, watchdog timers, an ETM9 embedded trace module, and JTAG support for the ARM922based products as well as EJTAG support for the MIPS 4Kc-based products. Altera's highperformance APEX<sup>TM</sup> 20KE architecture is implemented in the Excalibur products. Table 1 shows the three different Excalibur ARM- and MIPS-based product features.

One of the key advantages of both Excalibur hard core products is that the on-chip processor system buses operate at full processor clock frequencies (up to 200 MHz) for maximum system bandwidth and performance. This enables superior system-level performance. Other conventional, discrete processor-based solutions may be limited by processor system buses that operate at half the CPU clock frequency or by system controller chip sets that only offer 133 MHz SDRAM controller support. The advanced Excalibur hard core embedded processor products that feature key on-chip peripherals support, large on-chip memory arrays, APEX embedded system blocks (ESBs) memory bits, and the design flexibility and time-to-market advantages of integrated programmable logic structures makes the Excalibur products ideal for system-level design.

| Feature               | EPXA1/EPXM1 | EPXA4/EPXM4 | EPXA10/EPXM10 |

|-----------------------|-------------|-------------|---------------|

| Maximum system gates  | 263,000     | 1,052,000   | 1,772,000     |

| Typical gates         | 100,000     | 400,000     | 1,000,000     |

| Logic elements (LEs)  | 4,160       | 16,640      | 38,400        |

| ESBs                  | 26          | 104         | 160           |

| Maximum RAM bits      | 53,248      | 212,992     | 327,680       |

| Maximum macrocells    | 416         | 1,664       | 2,560         |

| Maximum user I/O pins | 178         | 360         | 521           |

| Single-port SRAM      | 32 Kbytes   | 128 Kbytes  | 256 Kbytes    |

| Dual-port SRAM        | 16 Kbytes   | 64 Kbytes   | 128 Kbytes    |

#### Features

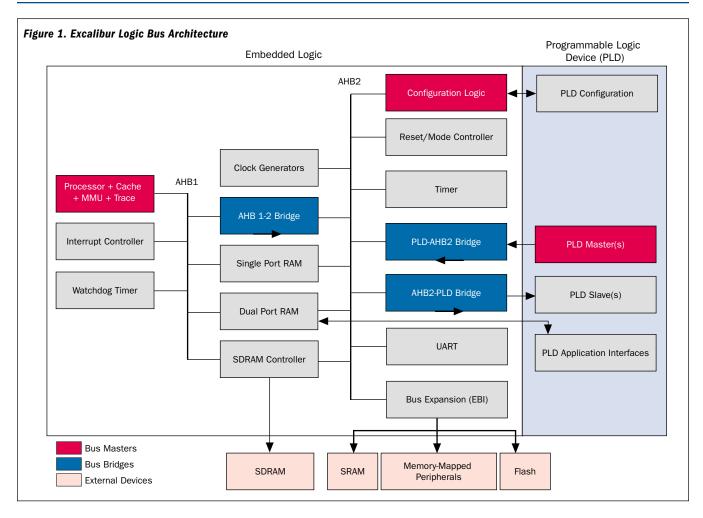

Both Excalibur ARM- and MIPS-based products implement the advanced microcontroller bus architecture (AMBA<sup>TM</sup>) high-performance bus (AHB). This is an industry-standard bus architecture capable of multiple bus masters, slave modules, locked transfers, split transactions, and bus frequencies of up to 200 MHz. The AMBA AHB is used as an interface between the processor stripe, bus masters, and slave modules implemented in the programmable logic architecture (see Figure 1).

The processor and the PLD bus master can simultaneously access different blocks of the onchip single-port memory and on-chip dual-port memory. In addition, different system functions (e.g., processor and on-chip memory, SDRAM controller and peripherals, and PLD structure) are decoupled from each other through localized bus structures and are driven by phaselocked loops (PLLs) in different clock domains. The AMBA bus interface can be used to interface with the Altera® MegaCore® intellectual property (IP) functions or thirdparty Altera Megafunction Partners Program (AMPP<sup>SM</sup>) partner IP blocks.

Both Excalibur ARM- and MIPS-based products are fully supported by industry-standard realtime operating systems (RTOSs) and embedded software tool chains (e.g., compilers, debuggers, assemblers, linkers, and loaders). The Quartus<sup>TM</sup> development tool is used for design entry, simulation, and synthesis through thirdparty tools, and optimized place and route of designs implemented in the programmable logic structure.

### APEX

#### Introducing New APEX 20KC Devices

The new high-performance APEX<sup>TM</sup> 20KC devices address the high-bandwidth needs of system-on-a-programmable-chip (SOPC) applications. These devices combine the stateof-the-art features found in APEX 20KE devices with industry-leading, 0.15- $\mu$ m all-layer copper interconnect technology to provide performance improvements of 25% to 35% over 0.18- $\mu$ m-based devices. For more information on these new APEX devices, see "APEX 20KC Devices with All-Layer Copper Interconnect Enhance Performance by 25% to 35%" on page 5.

#### All 10 APEX 20KE Devices Now Shipping

The APEX EP20K30E device, the smallest APEX 20KE device, is now shipping. With 30,000 typical gates (113,000 maximum system gates), 1,200 logic elements (LEs), 24 Kbits of RAM and 128 maximum user I/O pins, this device addresses low-density application needs. All 10 APEX 20KE devices are now shipping: EP20K30E, EP20K60E, EP20K100E, EP20K160E, EP20K200E, EP20K300E, EP20K400E, EP20K600E, EP20K1000E, and EP20K1500E. These devices are available in multiple packages, including the advanced Fineline BGA<sup>TM</sup> package.

#### LVDS & PLL Support Now Available in Industrial-Speed-Grade Devices

In addition to offering data transfer rates up to 840 megabits per second (Mbps) on commercial temperature grade devices, APEX 20KE devices now support LVDS in industrial-speed-grade devices. APEX 20KE industrial-grade devices also feature phase-locked loops (PLLs). Table 1 summarizes the LVDS support in APEX 20KE devices. Table 2 summarizes PLL support in APEX 20KE devices.

The True-LVDS<sup>™</sup> solution, with data transfer rates as high as 840 Mbps per channel, is ideal for high-speed telecommunication, data communication, and computing applications. Table 1. LVDS Support in APEX 20KE Devices

| Device     | Maximum Data Transfer Rate<br>Per True-LVDS Channel (Mbps) |                   |                   |  |

|------------|------------------------------------------------------------|-------------------|-------------------|--|

|            | Commercial<br>-1X                                          | Commercial<br>-2X | Industrial<br>-2X |  |

| EP20K300E  | 156                                                        | 156               | 156               |  |

| EP20K400E  | 840                                                        | 700               | 625               |  |

| EP20K600E  | 840                                                        | 700               | 625               |  |

| EP20K1000E | 750                                                        | 625               | 625               |  |

| EP20K1500E | 750                                                        | 625               | 625               |  |

#### Table 2. PLL Support in APEX 20KE Devices

| Speed Grade    | Maximum Internal Output<br>Frequency from PLL (MHz) |  |

|----------------|-----------------------------------------------------|--|

| Commercial -1X | 335                                                 |  |

| Commercial -2X | 250                                                 |  |

| Industrial -2X | 250                                                 |  |

The PLLs offer flexible frequency synthesis and zero clock skew capability for high-performance design needs. APEX 20KE devices also support the LVPECL standard that can be used in highperformance clocking schemes, backplanes, optical transceivers, high-speed networking, and high-end video applications.

#### **APEX 20KE Production Devices**

All APEX 20KE -ES and -XES engineering sample devices have changed to production -1 and -1X speed grade devices. These productionready devices are available today in all packages and replace the engineering sample devices.

# 5.0-V Tolerant APEX 20K & APEX 20KE Devices

The APEX 20K device family has been enhanced to provide a 5.0-V tolerant I/O buffer, providing full compliance with the 5.0-V PCI specification. 5.0-V tolerant devices are now shipping and have a "V" suffix in the ordering code (e.g., EP20K400BC652-1V).

APEX 20KE devices can be used with an additional external resistor to make them 5.0-V

tolerant and provide flexibility for system design. For details on this improvement, see the 5.0-V Tolerance in APEX 20KE Devices White Paper on the Altera® web site (http://www.altera.com).

| Table 3. APEX 20KE Device & Quartus Software<br>Support Availability |                        |                                     |  |

|----------------------------------------------------------------------|------------------------|-------------------------------------|--|

| Device                                                               | Package                | Software<br>Support<br>Availability |  |

| EP20K30E                                                             | 144-pin TQFP (1)       | Now                                 |  |

|                                                                      | 144-pin FineLine BGA   | Now                                 |  |

|                                                                      | 208-pin PQFP (1)       | Now                                 |  |

|                                                                      | 324-pin FineLine BGA   | Now                                 |  |

| EP20K60E                                                             | 144-pin TQFP           | Now                                 |  |

|                                                                      | 144-pin FineLine BGA   | Now                                 |  |

|                                                                      | 208-pin PQFP           | Now                                 |  |

|                                                                      | 240-pin PQFP           | Now                                 |  |

|                                                                      | 324-pin FineLine BGA   | Now                                 |  |

|                                                                      | 356-pin BGA (1)        | Now                                 |  |

| EP20K100E                                                            | 144-pin TQFP           | Now                                 |  |

|                                                                      | 144-pin FineLine BGA   | Now                                 |  |

|                                                                      | 208-pin PQFP           | Now                                 |  |

|                                                                      | 240-pin PQFP           | Now                                 |  |

|                                                                      | 324-pin FineLine BGA   | Now                                 |  |

|                                                                      | 356-pin BGA            | Now                                 |  |

| EP20K160E                                                            | 144-pin TQFP           | Now                                 |  |

|                                                                      | 208-pin PQFP           | Now                                 |  |

|                                                                      | 240-pin PQFP           | Now                                 |  |

|                                                                      | 356-pin BGA            | Now                                 |  |

|                                                                      | 484-pin FineLine BGA   | Now                                 |  |

| EP20K200E                                                            | 208-pin PQFP           | Now                                 |  |

|                                                                      | 240-pin PQFP           | Now                                 |  |

|                                                                      | 356-pin BGA            | Now                                 |  |

|                                                                      | 484-pin FineLine BGA   | Now                                 |  |

|                                                                      | 652-pin BGA            | Now                                 |  |

|                                                                      | 672-pin FineLine BGA   | Now                                 |  |

| EP20K300E                                                            | 240-pin PQFP           | Now                                 |  |

|                                                                      | 652-pin BGA            | Now                                 |  |

|                                                                      | 672-pin FineLine BGA   | Now                                 |  |

| EP20K400E                                                            | 652-pin BGA            | Now                                 |  |

|                                                                      | 672-pin FineLine BGA   | Now                                 |  |

| EP20K600E                                                            | 652-pin BGA            | Now                                 |  |

|                                                                      | 672-pin FineLine BGA   | Now                                 |  |

|                                                                      | 1,020-pin FineLine BGA | Now                                 |  |

| EP20K1000E                                                           | 652-pin BGA            | Now                                 |  |

|                                                                      | 672-pin FineLine BGA   | Now                                 |  |

|                                                                      | 1,020-pin FineLine BGA | Now                                 |  |

| EP20K1500E                                                           | 652-pin BGA            | Now                                 |  |

|                                                                      | 1,020-pin FineLine BGA | Now                                 |  |

#### **APEX 20K Product Transition**

Altera is migrating the 2.5-V EP20K400 device from a 0.25-µm process to a 0.22-µm process. Information regarding this device migration can be found in process change notification (PCN) 0005, available on the Altera web site at http://www.altera.com.

### ACEX

#### **ACEX 1K Devices Shipping Now**

ACEX<sup>TM</sup> 1K devices are now shipping in all packages for 10,000-, 30,000-, 50,000-, and 100,000-gate densities (see Table 4). These costoptimized devices are especially suited for lowcost, high-volume applications and can be used to attain the lowest cost per PLD for highvolume designs.

| Device  | Package              | Availability |  |

|---------|----------------------|--------------|--|

| EP1K10  | 100-pin TQFP         | Now          |  |

|         | 144-pin TQFP         | Now          |  |

|         | 208-pin PQFP         | Now          |  |

|         | 256-pin FineLine BGA | Now          |  |

| EP1K30  | 144-pin TQFP         | Now          |  |

|         | 208-pin PQFP         | Now          |  |

|         | 256-pin FineLine BGA | Now          |  |

| EP1K50  | 144-pin TQFP         | Now          |  |

|         | 208-pin PQFP         | Now          |  |

|         | 256-pin FineLine BGA | Now          |  |

|         | 484-pin FineLine BGA | Now          |  |

| EP1K100 | 208-pin PQFP         | Now          |  |

|         | 256-pin FineLine BGA | Now          |  |

|         | 484-pin FineLine BGA | Now          |  |

ACEX 1K devices provide full PLL capability for ClockLock<sup>™</sup> and ClockBoost<sup>™</sup> features, such as embedded dual-port RAM and full 64-bit, 66-MHz PCI compliance in every -1X and -2X speed grade device. Developed on a costoptimized 0.22-µm/0.18-µm hybrid process, and featuring a 2.5-V core operating voltage, ACEX 1K devices offer an ideal combination of cost, performance, and features. ACEX 1K devices are now shipping in all packages in the 10,000, 30,000, 50,000, and 100.000 gate densities.

#### Note:

<sup>(1)</sup> TQFP: thin quad flat pack, PQFP: plastic quad flat pack, BGA: ball-grid array.

Devices & Tools, continued from page 11

Full software support for ACEX 1K devices is available from the MAX+PLUS® II software version 10.0. In addition, a wide range of ACEX-optimized intellectual property (IP) functions can now be found at the Altera IP MegaStore<sup>TM</sup> on-line store.

## MAX

#### Broad Range of FineLine BGA Packages Available for MAX Devices

MAX<sup>®</sup> devices are available in a wide range of FineLine BGA<sup>TM</sup> packaging, including both the 1.0-mm pitch (FineLine BGA) and the 0.8-mm pitch (Ultra FineLine BGA) packages. Table 5 shows the FineLine BGA and Ultra FineLine BGA packaging options for MAX 7000B devices.

Table 5. FineLine BGA Packages Available for

| MAX Devices |                            |                            |                                    |                                     |  |  |

|-------------|----------------------------|----------------------------|------------------------------------|-------------------------------------|--|--|

| Device      | 100-Pin<br>FineLine<br>BGA | 256-Pin<br>FineLine<br>BGA | 49-Pin<br>Ultra<br>FineLine<br>BGA | 169-Pin<br>Ultra<br>FineLine<br>BGA |  |  |

| EPM7032B    |                            |                            | $\checkmark$                       |                                     |  |  |

| EPM7064B    | $\checkmark$               |                            | $\checkmark$                       |                                     |  |  |

| EPM7128B    | $\checkmark$               | ~                          | ~                                  | ~                                   |  |  |

| EPM7256B    |                            | ~                          |                                    | ~                                   |  |  |

| EPM7512B    |                            | ~                          |                                    | $\checkmark$                        |  |  |

| EPM7064AE   | $\checkmark$               |                            | $\checkmark$                       |                                     |  |  |

| EPM7128AE   | $\checkmark$               | $\checkmark$               |                                    | $\checkmark$                        |  |  |

| EPM7256AE   | ~                          | ~                          |                                    |                                     |  |  |

| EPM7512AE   |                            | ~                          |                                    |                                     |  |  |

FineLine BGA packages occupy a smaller footprint than traditional TQFP packages and can offer more I/O pins to the designer. For example, Figure 1 shows a 169-pin Ultra FineLine BGA package that occupies less than half the board space occupied by the 144-pin TQFP package.

An EPM7512B device in a 169-pin FineLine BGA package offers 141 I/O pins compared to the 120 I/O pins offered in a 144-pin TQFP package.

#### Figure 1. Ultra FineLine BGA Package

This variety of BGA packages and pin counts offers flexibility in choosing the device that is right for your specific application.

#### MAX 7000B Industrial-Grade Availability

Altera now offers the popular 2.5-V MAX 7000B devices in industrial-grades. Table 6 shows which packages are now available in the industrial grade. Contact your local Altera sales representative for availability and lead times on specific packages.

Table 6. MAX 7000B Industrial-Temperature

Dovicos

| Devices  |                      |             |  |  |

|----------|----------------------|-------------|--|--|

| Device   | Package              | Speed Grade |  |  |

| EPM7032B | 44-pin TQFP          | -5          |  |  |

| EPM7064B | 44-pin PLCC          | -5          |  |  |

|          | 44-pin TQFP          | -5          |  |  |

|          | 100-pin TQFP         | -5          |  |  |

| EPM7128B | 100-pin TQFP         | -7          |  |  |

|          | 100-pin FineLine BGA | -7          |  |  |

|          | 144-pin TQFP         | -7          |  |  |

|          | 256-pin FineLine BGA | -7          |  |  |

| EPM7256B | 100-pin TQFP         | -7          |  |  |

|          | 144-pin TQFP         | -7          |  |  |

|          | 208-pin PQFP         | -7          |  |  |

|          | 256-pin FineLine BGA | -7          |  |  |

| EPM7512B | 256-pin BGA          | -7          |  |  |

|          | 256-pin FineLine BGA | -7          |  |  |

#### MAX 7000AE Devices Migrate to Advanced Process

MAX 7000AE devices will migrate to a 0.30-µm quad-layer-metal process. This process is a linear shrink of the existing 0.35-µm quadlayer-metal process that uses the same equipment and process flow. These devices will be pin-, function-, timing-, and programming file-compatible with existing 0.35-µm versions of the MAX 7000AE devices.

FineLine BGA packages occupy a smaller footprint than traditional TQFP packages and can offer more I/O pins to the designer.

This transition will begin on March 20, 2001. After this date, you may receive devices from either the 0.35- $\mu$ m or 0.30- $\mu$ m quad-layer-metal processes.

For additional information regarding this transition, contact your local Altera sales representative. Initial qualification and characterization data will be available on December 20, 2000. Contact Altera's Customer Quality Engineering Manager at (408) 544-7563 for more details.

### **CONFIGURATION**

#### High-Density Configuration Devices Coming Soon

The new 4-Mbit EPC4 and 16-Mbit EPC16 configuration devices are scheduled for release in January 2001. These new devices will include features such as faster configuration times and reprogrammability. Additionally, you can use a single device to configure several APEX<sup>TM</sup> or FLEX<sup>®</sup> devices in parallel to further speed configuration and save board space.

A single EPC16 device will configure two 1.5-million-gate EP20K1500E devices using the new data compression features.

### TOOLS

#### Quartus Version 2000.09 & MAX+PLUS II Version 10.0 Now Available

Version 2000.09 of the Quartus<sup>TM</sup> development tool brings dramatic performance improvements to Altera customers. The new PowerFit<sup>TM</sup> fitting technology improves customer design performance by up to 45% and decreases compile times by 1.5× to 3.0×, depending on the device density for the design. For more details on the Quartus software version 2000.09 see the "Quartus Version 2000.09 Dramatically Improves  $f_{MAX}$  & Compile Times" feature article on page 1, or visit the Altera web site at http://www.altera.com. Table 7 lists the new devices supported by the Quartus software version 2000.09.

#### Table 7. New Devices Supported by the Quartus Software Version 2000.09

| Support      | Device     | Package                |

|--------------|------------|------------------------|

| Full         | EP20K60E   | 144-pin FineLine BGA,  |

| Compilation, |            | 324-pin FlneLine BGA,  |

| Simulation,  |            | 356-pin BGA            |

| and          | EP20K100E  | 144-pin FineLine BGA   |

| Programming  | EP20K160E  | 144-pin TQFP, 208-pin  |

| Support      |            | RQFP, 240-pin PQFP,    |

|              |            | 356-pin BGA, 484-pin   |

|              |            | FineLine BGA           |

|              | EP20K600E  | 1,020-pin FineLine BGA |

|              | EP20K1500E | 652-pin BGA, 1,020-pin |

|              |            | FineLine BGA           |

| Compilation  | EP20K30E   | 144-pin TQFP, 144-pin  |

| and          |            | FineLine BGA, 208-pin  |

| Simulation   |            | RQFP, 324-pin FineLine |

| Support      |            | BGA, 356-pin BGA       |

The MAX+PLUS II software version 10.0 adds support for the latest MAX 7000B device package combinations and adds programming support for the new ACEX EP1K10 devices. Table 8 lists the new devices supported by the MAX+PLUS II software version 10.0.

| Table 8. New Devices with Full Support from the |  |

|-------------------------------------------------|--|

| MAX+PLUS II Software Version 10.0               |  |

| Package                    |  |  |

|----------------------------|--|--|

| 44-pin TQFP                |  |  |

| 49-pin Ultra FineLine BGA  |  |  |

| 49-pin Ultra FineLine BGA  |  |  |

| 100-pin FineLine BGA       |  |  |

| 49-pin Ultra FineLine BGA  |  |  |

| 49-pin Ultra FineLine BGA  |  |  |

| 169-pin Ultra FineLine BGA |  |  |

| 144-pin TQFP               |  |  |

| 256-pin BGA                |  |  |

| 256-pin FineLine BGA       |  |  |

| 169-pin Ultra FineLine BGA |  |  |

| 100-pin TQFP               |  |  |

| 144-pin TQFP               |  |  |

| 208-pin PQFP               |  |  |

| 256-pin BGA                |  |  |

|                            |  |  |

continued on page 14

Devices & Tools, continued from page 13

#### **Operating System Update**

The Quartus software version 2000.09 and the MAX+PLUS II software version 10.0 both support the Windows 2000 operating system. The Quartus software version 2000.09 also adds support for the HP-UX 11.0 operating system. Table 9 shows the Quartus and MAX+PLUS II operating system support.

| Table 9. Quartus & MAX+PLUS II Operating<br>System Support |                                                                                                                                                                  |  |  |  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Software                                                   | Operating System Support                                                                                                                                         |  |  |  |

| Quartus<br>version 2000.09                                 | Windows 2000, Windows 98,<br>Windows NT version 4.0 and<br>higher, Sun Solaris 2.6 and<br>2.7, and HP-UX 10.2x and<br>11.0 (1)                                   |  |  |  |

| MAX+PLUS II<br>version 10.0                                | Windows 2000, Windows 98,<br>Windows 95, Windows NT<br>version 4.0 and higher,<br>Sun Solaris 2.5 and 2.6,<br>HP-UX 10.2x, and AIX<br>version 4.1 and higher (1) |  |  |  |

software and hardware within the Quartus environment.

The next release of the

Quartus software will

designers to co-design

include a software

mode to allow

Note:

(1) Support for Solaris 2.8 will be added in the initial releases in 2001.

#### **Quartus Roadmap**

The next major release of the Quartus software is scheduled for Q1 2001. This release will support the Altera Excalibur<sup>TM</sup> hard core embedded processor solutions and include major enhancements that help designers with PLD and system-level design issues.

In addition to the compilation and simulation modes, the next release of the Quartus software will include a software mode to allow designers to co-design software and hardware within the Quartus environment. This new mode will provide the capability to configure the ARM, MIPS, and Nios embedded processors and their integration with C/C++ compiler tools.

#### MAX+PLUS II BASELINE, E+MAX & ASAP2 Version 10.0 Now Available

MAX+PLUS II BASELINE development software, E+MAX<sup>TM</sup> development software, and

ASAP2 programmer software version 10.0 are now available for download from the Altera web site at http://www.altera.com. These software programs provide support for the latest MAX 7000B devices. The MAX+PLUS II BASELINE software version 10.0 also adds support for the latest ACEX EP1K10 devices.

MAX+PLUS II BASELINE and E+MAX software customers can download and license the world-class Synopsys FPGA *Express* software and/or Exemplar Logic LeonardoSpectrum-Altera software from the Altera web site (http://www.altera.com) to support HDL synthesis.

#### MAX+PLUS II BASELINE

The MAX+PLUS II BASELINE software features a seamless development flow that allows designers to enter, compile, and perform timing analysis on designs and program a wide range of Altera PLDs—including the new ACEX 1K family and FLEX 6000, MAX 7000, and MAX 3000 devices. The MAX+PLUS II BASELINE software download file is 45,822,459 bytes.

#### E+MAX

The E+MAX software is a subset of the MAX+PLUS II BASELINE software targeted at the industry's most popular product-term architectures—the MAX 7000 and MAX 3000 devices. The E+MAX software no longer includes Altera's native VHDL and Verilog HDL synthesis, as it provides access to world-class synthesis tools from Exemplar Logic and Synopsys on the Altera web site (http://www.altera.com). The E+MAX software download file is 20,025,630 bytes.

#### ASAP2

The ASAP2 software is a subset of the MAX+PLUS II software that only supports device programming. The ASAP2 software download file is 13,907,408 bytes.

Download files are now available from the Altera web site at http://www.altera.com.

# Download the Latest OEM Synthesis & Simulation Tools

All customers with an active subscription can download the latest versions of the OEM synthesis and simulation tools Altera includes with software subscriptions. These tools can be downloaded from the Altera web site at http://www.altera.com. The new versions include support for the latest APEX 20KE, ACEX 1K, and MAX 7000B devices and include enhancements to improve design flows. The new LeonardoSpectrum-Altera and ModelSim-Altera also include support for the Microsoft

# Design Tips

Windows 2000 operating system. Table 10 shows the versions available.

| Tool                                          | Version | Availability |

|-----------------------------------------------|---------|--------------|

| Synopsys<br>FPGA <i>Expr</i> ess              | 3.5     | Now          |

| Exemplar Logic<br>LeonardoSpectrum-<br>Altera | 2000.1b | Now          |

| Model Technology<br>ModelSim-Altera           | 3.4c    | Now          |

## Designing Memory-Mapped Peripherals for the Nios Embedded Processor

The Nios<sup>TM</sup> embedded processor provides high levels of integration by allowing a microprocessor, memory, peripherals, and programmable logic to reside on the same device. The Excalibur<sup>TM</sup> Development Kit, featuring the Nios embedded processor, contains a number of peripherals, including a timer, a universal asynchronous receiver/ transmitter (UART), and a parallel input/ output (PIO). Other peripherals can be designed to interface with the Nios embedded processor using memory-mapped techniques. Memory-mapped peripherals provide a straightforward interface to the Nios embedded processor.

#### **Memory-Mapped Peripherals**

All peripherals that connect to the Nios embedded processor should be designed as memory-mapped I/O peripherals. Memorymapped peripherals occupy a specific range in the address space of the Nios embedded processor. A memory-mapped peripheral is accessed by either reading or writing to addresses within the peripherals' address range. The Nios embedded processor interfaces to memory-mapped peripherals by using the following signals:

#### clk

irq\_from\_the\_peripheral data\_to\_cpu\_from\_the\_peripheral address\_to\_the\_peripheral cpu\_be\_n\_to\_the\_peripheral cpu\_read\_n\_to\_the\_peripheral cpu\_write\_n\_to\_the\_peripheral data\_from\_cpu\_to\_the\_peripheral select\_to\_the\_peripheral

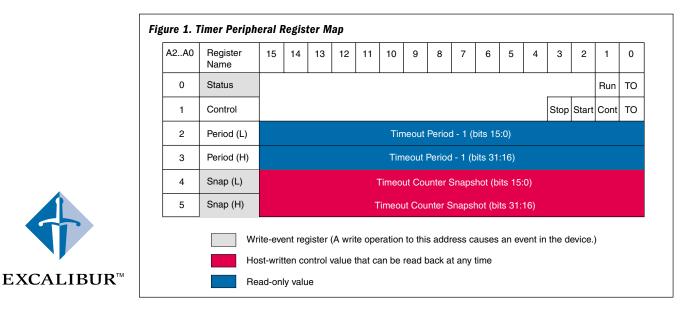

The Nios embedded processor supplies write enable, read enable, byte enable, chip select, data, and address lines to the peripheral. These signals are used to read or write from a register bank within the peripheral. The register map shown in Figure 1 on page 16 describes an example of the operation of each register within the register bank.

Figure 1 on page 16 illustrates the register map for the timer peripheral included in the Excalibur Development Kit.

continued on page 16

Designing Memory-Mapped Peripherals for the Nios Embedded Processor, continued from page 15

The timer contains six registers in its register map. Registers in a memory-mapped peripheral can be read-only or read- and write-capable. The timer is controlled by writing to register 1. Writing a 1 to bit 2 of register 1 starts the timer, and writing a 1 to bit 3 of register 1 stops the timer. Values can be pre-loaded into the timer by writing the upper half of the 32-bit word to register 3 and the lower half of the 32bit word to register 2.

Additional information on timer operation is available with the Excalibur Development Kit.

#### Creating a Custom Memory-Mapped Peripheral

Custom memory-mapped peripherals can be designed for the Nios embedded processor by following these three steps:

- 1. Determine the design requirements of the peripheral.

- 2. Create a peripheral register.

- 3. Code the peripheral using a hardware description language (HDL).

The following example demonstrates these three steps by creating a custom memorymapped first-in first-out (FIFO) peripheral.

#### Determine the FIFO Peripheral Design Requirements

The FIFO in this example is designed to allow the Nios embedded processor to interface with a fast I/O source. The FIFO requires that the fast I/O source writes to the FIFO, and the Nios processor reads from the FIFO. The FIFO needs to assert an interrupt request signal whenever the FIFO is full. Therefore, the FIFO buffer would have the characteristics shown in Table 1.

| Table 1. Example FIFO Buffer Characteristics |                                                               |  |  |  |

|----------------------------------------------|---------------------------------------------------------------|--|--|--|

| Description                                  | Criteria                                                      |  |  |  |

| Width                                        | 32 bits                                                       |  |  |  |

| Depth                                        | 128 words                                                     |  |  |  |

| FIFO input signals                           | clock, reset, write, read, data                               |  |  |  |

| FIFO output signals                          | data, empty_flag, full_flag,<br>word_count, interrupt_request |  |  |  |

The I/O source will directly drive the data input port of the FIFO. The Nios embedded processor outputs

cpu\_write\_n\_to\_the\_peripheral and cpu\_be\_n\_to\_the\_peripheral signals for each peripheral to which it interfaces. However, for the example in Table 1, the FIFO cannot be written by the Nios embedded processor (it can only be written by the I/O source), so the

cpu\_be\_n\_to\_the\_peripheral and

cpu\_write\_n\_to\_the\_peripheral

signals will not be used.

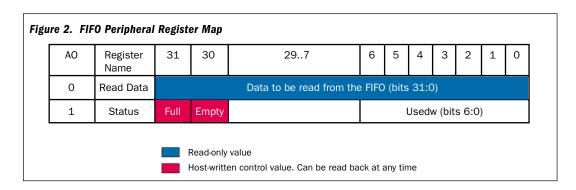

#### FIFO Peripheral Register Map

The layout of the FIFO's register map is determined by how many input and output signals are connected to it (see Figure 2). The FIFO has two control signal inputs (write and read) and one data input (data). The I/O source directly writes to the FIFO, so write registers are not required in the FIFO memory map. The register map consists of two readable registers: Read Data and Status. The Read Data register contains the 32-bit output of the FIFO, and the Status register indicates the current state of the FIFO. The full, empty, and word count (usedw) signals are placed in the same 32-bit register to conserve address space. However, if address space is not a consideration, each output signal can be placed in a separate register in the register map.

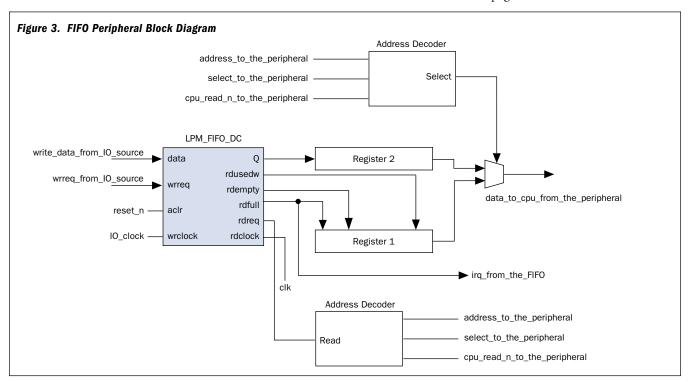

This FIFO peripheral can be implemented using the block diagram shown in Figure 3. The I/O source writes to the FIFO directly using the FIFO's data, wrreq, and wrclock signals. The FIFO will update the Read Data register by writing to Register 0 whenever the Nios embedded processor sets the address\_to\_the\_peripheral signal to 0 and when it asserts the select\_to\_the\_peripheral and the cpu\_read\_n\_to\_the\_peripheral

Designing Memory-Mapped Peripherals for the Nios Embedded Processor, continued from page 17

signals. The Status register (Register 1) is updated by the FIFO whenever reads or writes are performed. The contents of the Status register can be read by setting the address\_to\_the\_peripheral signal to 1 and by asserting the select\_to\_the\_peripheral and the cpu\_read\_n\_to\_the\_peripheral signals.

#### **Simulation Example**

Figure 4 depicts a simulation example for the custom FIFO. The values 1 through 24 are written to the FIFO by asserting the IO\_wrreq signal and applying the values 1 through 24 to the FIFO's data\_in\_from\_IO bus. After 24 IO\_clock cycles, the IO\_wrreq line is deasserted. The Nios embedded processor begins reading from the FIFO by asserting the select\_to\_the\_peripheral and cpu\_read\_n\_to\_the\_peripheral lines at 300 ns. The address bus holds a value of 0 from 300 ns to 480 ns, which causes the FIFO to update the

data\_to\_cpu\_from\_peripheral bus with the current output of the FIFO. These results are verified in the waveform because the data\_to\_cpu\_from\_peripheral bus outputs the values 1 through 6. The Status register is read at time 502 ns by setting the address\_to\_the\_peripheral signal to 1 and by asserting the

select\_to\_the\_peripheral and cpu\_read\_n\_to\_the\_peripheral signals. The Status register value is output to the data\_to\_cpu\_from\_peripheral bus at time 510 ns. The

data\_to\_cpu\_from\_peripheral bus reads a value of 18 at time 510 ns, indicating that 18 words remain in the FIFO.

Memory-mapped peripherals create a simple interface between a peripheral and the Nios embedded processor. When using memory-mapping, the Nios embedded processor communicates to its peripherals by reading and writing to the system memory space. You can optimize the register map of a memory-mapped peripheral by designing it with a knowledge of which input and output signals of the Nios embedded processor are important for your application. The register map is central to creating an efficient interface between the Nios embedded processor and your peripheral. A design aim should be to create a small register map, as this will conserve address space and in some instances increase the maximum speed of the peripheral.

|     |                                                     | 231.0 ns        | 295,0 ns | 359,0 ns | 423,0 ns | 487,0 ns    |

|-----|-----------------------------------------------------|-----------------|----------|----------|----------|-------------|

|     | Name                                                |                 |          |          |          |             |

| цÞ  | reset_n                                             |                 |          |          |          |             |

| цÞ. | clk.                                                |                 |          |          |          |             |

| цÞ. | select_to_the_peripheral                            |                 |          |          |          |             |

| цÞ. | cpu_read_n_to_the_peripheral                        |                 |          |          |          |             |

| цÞ. | address_to_the_peripheral                           |                 |          |          |          |             |

| 9   | <ul> <li>data_to_cpu_from_the_peripheral</li> </ul> |                 | 0 X      | 1 X 2 X  | 3 X 4 X  | \$ X 6 X 18 |

| цÞ. | I0_clock                                            | лллг            | uunnuu   | ากกกกก   | nnnnn    |             |

|     | ▲ data_in_from_I0                                   | 2)(22)(23)(24)( |          |          | 0        |             |

| цÞ. | IO_wreq                                             |                 |          |          |          |             |

| Ċ   | isq_from_the_peripheral                             |                 |          |          |          |             |

Figure 4. FIFO Peripheral Simulation Example

# **Customer** Application

# OMEGA-TECHNOLOGIES S.A.: APEX Device Doubles Processing Power in Signal Processing Application

Hybrid radio frequency (RF) simulation is now widely used for radar, electronic warfare (EW), or laboratory communication equipment tests. This laboratory-based simulation reproduces "real life" electromagnetic environments seen by receivers such as handsets or complex radar systems.

Because RF simulation involves the generation of millions of RF pulses and signals, it consumes much real-time computing power to control the synthesizers in charge of microwave generation. This real-time data processing was traditionally dedicated to digital signal processing (DSP) equipment, while high-level software ran on workstations or multiprocessor-networked PCs.

OMEGA-TECHNOLOGIES S.A., a subsidiary of Thomson-CSF in Massy Cedex, France, is now introducing its new CARIBOU real-time simulation engine, which replaces the 200-MHz TMS320C6201 device with a single Altera® APEX<sup>TM</sup> device. This APEX device offers a 100% increase in computing power.

#### A Typical DSP Job

In DSP-based simulations, the system architecture is based on a real-time unit (RTU) with a PCI interface plugged into a multiprocessor PC (Windows NT).

The first DSP-based RTU had a multiprocessor 320C40 board (see Figure 1), which evolved into a single 320C6 board.

Nevertheless, drawbacks of DSP sets the following system-wide limitations:

- High price of DSPs and associated circuits

- Need for a very detailed code optimization (assembly level) to get full performance of parallel computing (Software was written in C for portability, but optimization was difficult.)

- Speed limitation due to memory architecture

These drawbacks led to the natural conclusion that the next generation of systems would need a different approach.

#### Using an APEX Device: The CARIBOU Project

The first phase of replacing a DSP-based system is to transfer the *C* core algorithms for pulse processing into VHDL. Simulation in the Quartus<sup>TM</sup> software helps to define the new system architecture.

During each 100-ms time slice, the CARIBOU architecture performs the following tasks:

- Downloads up to 800 Kbytes of raw data from the PCI interface to memory bank A or B

- Extracts from the other bank (A or B) up to 32 emitter parameters from the same amount of data

- Computes up to 50,000 pulse descriptors

- Generates up to 8 RF channel control words (amplitude or phase) for each descriptor

- Emits output data to a proprietary bus (32 bits wide)

The CARIBOU system is simple: one PCI main board with one APEX device, one PCI interface chip, and two SRAM banks on two daughter boards.

continued on page 20

#### Figure 1. Former C40 Multiprocessor Board

Implementing an APEX device increased the CARIBOU simulation engine's computing power by 100%. OMEGA-TECHNOLOGIES S.A.: APEX Device Doubles Processing Power in Signal Processing Application, continued from page 19

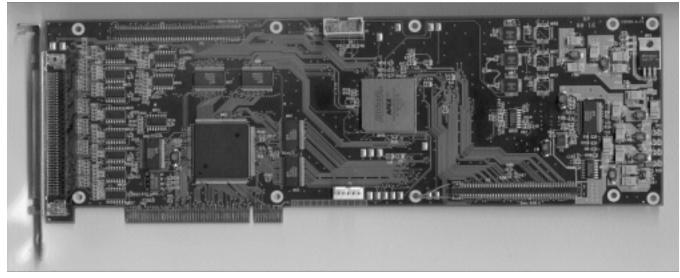

Table 1 shows the CARIBOU system features. Figure 2 shows the CARIBOU printed circuit board (PCB).

#### Conclusion

Using VHDL core simulation in the Quartus software provides programming flexibility and simplifies system implementation.

Implementing the Altera APEX device not only allows OMEGA-TECHNOLOGIES S.A. to double the processing power of their new CARIBOU system, but it also reduces production costs by 40%.

| Table 1. CARIBOU System |                       |  |  |  |

|-------------------------|-----------------------|--|--|--|

| Feature                 | Description           |  |  |  |

| APEX devices (1)        | EP20K400E             |  |  |  |

|                         | EP20K600E             |  |  |  |

|                         | EP20K1000E            |  |  |  |

| APEX device usage       | < 25%                 |  |  |  |

| Clocks                  | 32 & 64 MHz (PLL) (2) |  |  |  |

| SRAMs                   | 8 Mbytes per bank     |  |  |  |

| Memory                  | 256 Mbytes            |  |  |  |

| Power supplies          | 5 V @ 0.9 A           |  |  |  |

|                         | 3.3 V @1.2 A          |  |  |  |

#### Notes:

- The basic CARIBOU system includes the EP20K400EFC672-1X device in the 672-pin ballgrid array (BGA) package.

- (2) PLL: phase-locked loop.

Using VHDL core simulation provides programming flexibility, and system implementation is greatly simplified: no boot ROMs, no loader codes, and no power-greedy digital signal processors. The new CARIBOU system shows that using an APEX device for high-end signal processing is faster and much more flexible than classical DSP-based simulation.

#### About OMEGA-TECHNOLOGIES S.A.

OMEGA-TECHNOLOGIES S.A. is a whollyowned subsidiary of THOMSON-CSF and is located in the high-tech area of Massy (20 km from Paris).

The Company is developing innovative products in the frequency synthesis field and is a major player in the EW simulator business.

Products range from microwave modules and digital synthesizers to radar and communications simulators, mainly in the DC to 26 GHz range.

OMEGA-TECHNOLOGIES S.A. 29, Avenue Carnot 91349 Massey Cedex, FRANCE Tel: 33 1 69934134 Fax: 33 1 69934138 email : eric.duriez@omega-tech.com http://www.omega-tech.com

#### Figure 2. The CARIBOU System PCB

# Contributed Article

# Multi-Channel, Full-Duplex ADPCM Solutions from ISS for APEX, ACEX & FLEX Devices

Integrated Silicon Systems (ISS) recently extended its adaptive differential pulse code modulator (ADPCM) megafunction offering to include 32-, 64-, 128- and 256-channel fullduplex ADPCM codecs optimized for Altera's APEX<sup>TM</sup>, ACEX<sup>TM</sup>, and FLEX® programmable logic devices (PLDs). Typical implementation figures for these megafunctions are shown in Table 1. The megafunctions are fully supported by ISS and are also available for OpenCore<sup>TM</sup> evaluation. A bit-accurate C model, test bench, and documentation are included.

The extension of ISS's range of ADPCM megafunctions is a direct result of the exponential growth of voice traffic over voice and data networks and the need for the simultaneous compression/decompression of voice data at the network interface. The consequence of this growth from the system manufacturer's side is an explosion in the development of systems that can economically handle the increased capacity. PLDs are a costeffective solution for these implementations in systems that used to be dominated by digital signal processing (DSP) processors.

ISS has used a number of selectable variables to implement the ADPCM megafunctions and provide customers with a range of solutions that can be matched to their specific needs. The megafunctions are used in applications such as voice-over-DSL, voice-over-ATM systems, and cordless telephony.

The megafunctions fully support the ADPCM standards G.726, G.726a, G.727, and G.727a and facilitate individual channel reset and control – a major requirement in most voice systems. In addition, the functions support burst mode operation. The megafunctions require 16 clock cycles per sample per direction (CSC4110AA, CSC4120AA, and CSC4125AA) or six clock cycles per sample per direction (CSC4130AA and CSC4190AA).

For more information on these megafunctions, contact ISS by visiting their web site at http://www.issdsp.com.

Altera PLDs are a cost-effective solution for implementations in systems that used to be dominated by DSP processors.

| Product Code | Duplex<br>Channels | Device           | Minimum<br>Required<br>Clock Rate | Maximum<br>Achieved<br>Clock Rate | Pins | Logic<br>Elements<br>(LEs) | Memory Bits/<br>Embedded System<br>Blocks (ESBs) |

|--------------|--------------------|------------------|-----------------------------------|-----------------------------------|------|----------------------------|--------------------------------------------------|

| CSC4110AA    | 8                  | EP20K300EBC652-1 | 2.048                             | 21.90                             | 63   | 4,294                      | 9,088/11                                         |

| CSC4120AA    | 32                 | EP20K300EBC652-1 | 8.192                             | 22.50                             | 65   | 4,302                      | 18,176/16                                        |

| CSC4125AA    | 64                 | EP20K300EBC652-1 | 16.384                            | 20.10                             | 66   | 4,307                      | 36,352/24                                        |

|              | 64                 | EP1K100FC256-1   | 16.384                            | 21.83                             | 66   | 3,888                      | 36,352/12                                        |

| CSC4130AA    | 128                | EP20K300EBC652-1 | 12.288                            | 26.70                             | 67   | 7,174                      | 72,192/47                                        |

|              | 128                | EP20K200QC240-1  | 12.288                            | 30.94                             | 67   | 7,174                      | 72,192/47                                        |

| CSC4130AA    | 256                | EP20K400EBC652-1 | 24.576                            | 27.90                             | 68   | 7,178                      | 144,384/72                                       |

|              | 256                | EP20K300EBC652-1 | 24.576                            | 30.20                             | 68   | 7,178                      | 144,384/72                                       |

# Technical Articles

## **Designing Switches & Routers with APEX CAM**

Content-addressable memory (CAM) allows a design to search a table for a particular item. The data is supplied by the user or the system, and CAM uses the information provided to determine the location of the requested data.

CAM is especially useful in speeding up search operations in switches and routers. This article describes how APEX<sup>TM</sup> CAM can be used in specific applications such as:

Multi-protocol label switching (MPLS)

Internet protocol address resolution

#### **Multi-Protocol Label Switching**

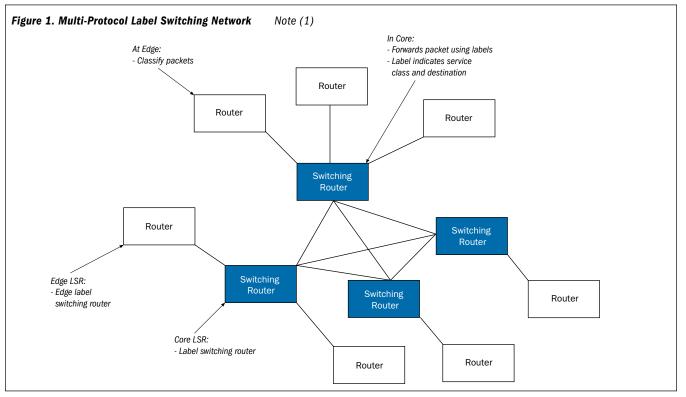

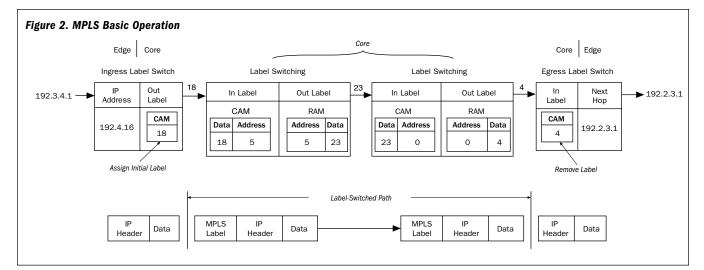

MPLS provides solutions that combine the control of Internet protocol routing with the simplicity of layer 1 switching. MPLS is a new technique in the evolution of routing/ forwarding technology for the core of the Internet and supports the use of advanced routing services. This technique solves problematic issues such as quality of services and delivery of new routing capabilities. Figure 1 shows MPLS by indicating that routers on the edge or in the core of the network have separate functions.

A multi-protocol label switching system is composed of two functional components: control and forwarding. The control component uses standard routing protocol to exchange information and maintain a forwarding table with other routers along the network. When a router receives a packet, the forwarding component searches the forwarding table, which is maintained by the control component, to make a routing decision for each packet. The forwarding component is based on a labelswapping forwarding algorithm. Each control component is responsible for assigning and maintaining other relevant control information.

#### Note:

(1) Routers using MPLS are highlighted in blue.

Because MPLS allows different modules to assign labels to packets, it decouples the forwarding of a packet from the contents of the packet's Internet protocol header.

At the ingress edges (entry) of the network, each incoming packet is classified and an initial label is assigned. The label switch performs a "longest-match routing" table look-up, assigns a label to the packet, then forwards it to the next hop on the label-switched path. In the core of the network, when a labeled packet arrives at a switch, the forwarding component uses the input port number and label to perform an exact match search of its forwarding table. If a match is found, the forwarding component retrieves the outgoing label, the outgoing interface and the next hop address from forwarding table. The forwarding component then replaces the incoming label with the outgoing label and directs the packet to the outbound interface for transmission to the next hop in the label-switched path. When the packet reaches the egress edge, the forwarding component searches its forwarding table. If the next hop is not a label switch, the egress switch discards the label and forwards the packet using conventional longest-match Internet protocol forwarding. Figure 2 shows the MPLS basic operation.

A CAM block can implement the required table and perform the fast search operation in the multi-protocol label switching operation. A CAM block finds the appropriate label for the incoming packet by searching the look-up table (LUT) in the ingress label switch. The label is used as an index into a table that specifies the next hop and the new label. The packet is forwarded to its next hop with the label attached. At the last edge of the network or egress label switch section, a CAM block can efficiently implement the table to remove the label from the incoming packet and forward the packet using Internet protocol forwarding.

A combination of CAM and RAM can be used to implement the table, which routes the incoming labeled packet to its next hop and finds the new label. Typical MPLS switches store up to 1,024 labels at a time, therefore requiring a 1,024  $\times$  32 CAM block. This CAM only takes 32 ESBs, so it can be implemented within APEX devices. Because the out-label is another label, a 1,024  $\times$  32 bit RAM block that consumes 16 ESBs can assign the appropriate label to the incoming label. A total of 48 ESBs can perform the multi-protocol label switching operation (see Figure 2).

#### **Internet Protocol Address Resolution**

Internet protocol address resolution is used in layer 3 switches to convert Internet protocol addresses to Ethernet or media access control (MAC) addresses and vice versa. An Internet protocol address is a 32-bit value that identifies each sender or receiver of information that is sent in packets across the Internet. When a source attempts to send data over the Internet, the Internet protocol portion of the transmission control protocol/Internet protocol (TCP/IP) includes the source Internet protocol

continued on page 24

A combination of CAM and RAM can be used to maintain a correlation between each MAC address and its corresponding Internet protocol address. Designing Switches & Routers with APEX CAM, continued from page 23

address and the destination Internet protocol address in the packet. Once all the required information for delivery is included in the packet, the TCP/IP stack sends the entire packet across the Internet to the destination. The destination receives the data, and a response can be sent to the source by using the existing Internet protocol address.

A MAC address, or Ethernet address, is the unique physical address designated to a hardware device (such as PC) when it is manufactured. When a computer is connected to a local area network (LAN), a correspondence table relates the Internet protocol address to the device's MAC address. A combination of CAM and RAM can be used to implement a table to maintain a correlation between each MAC address and its corresponding Internet protocol address and perform address conversion in both directions. CAM contains the Internet protocol addresses that point to corresponding locations in RAM, which contain the MAC or Ethernet address.

Address resolution protocol (ARP) is used to map an Internet protocol address to a recognized MAC address in the local network. When a host machine receives a packet, ARP runs a search to verify that the packet's destination address is on its particular network. The CAM and RAM combination, implemented in the ARP, compares the Internet protocol address against the content of the CAM table to find the appropriate MAC address in RAM. If CAM contains the Internet protocol address, the packet can be converted to the appropriate length and format, then sent to the destination device. If no match is found, ARP broadcasts a request packet to all the devices on the LAN in search of the corresponding address. If a device recognizes the Internet protocol addresses, it sends a message to the ARP claiming the Internet protocol address. ARP updates the contents of CAM and RAM for future reference and sends the packet to the destination machine. Figure 3 shows this Internet protocol address resolution process. This process can be implemented in software; however, implementing the search in hardware improves system performance.

#### Conclusion

Many networking applications require a fast search operation. APEX CAM can provide a solution for search operations in critical applications such as multi-protocol label switching, or Internet protocol address resolution. Using CAM simplifies and accelerates these functions and applications by increasing the performance of table look-up and translation implementation.

| Internet           |             |         | Address |         |                   |         |

|--------------------|-------------|---------|---------|---------|-------------------|---------|

| Protocol — Address | CAM         |         |         | RAM     |                   | Address |

|                    | Data        | Address |         | Address | Data              |         |

|                    | 192.2.41.53 | 0       |         | 0       | 92:ad:26:7e:81:ae |         |

|                    | 192.63.12.3 | 1       |         | 1       | 12:84:ea:72:9e:bd |         |

|                    | 192.21.42.3 | 2       |         | 2       | ae:b3:f4:87:2e:81 |         |

## **LVDS Timing Analysis**

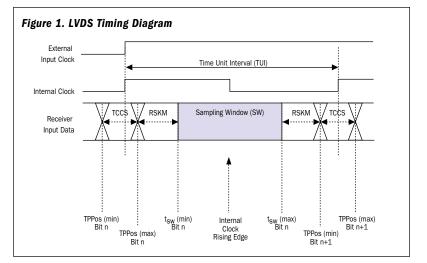

The LVDS I/O standard allows data to be transmitted at very high speeds. This high data transmission rate results in better overall system performance. To take advantage of this high system performance, designers need to understand how to analyze timing for LVDS. LVDS timing analysis is different from traditional synchronous timing analysis techniques; rather than focusing on clock-tooutput and setup times, LVDS timing analysis is based on the skew between the data and the clock signals.