## Altera Provides New Levels of System Integration with the Introduction of the Stratix Device Family

Next-generation systems demand a dramatic level of programmable logic device (PLD) bandwidth, including core processing, embedded memory, routing, and I/O bandwidth. Altera's new Stratix<sup>TM</sup> device family breaks the performance and density barriers for high-density programmable logic. Stratix devices are the first PLD family designed with a highperformance architecture, built from the ground up to enable true block-based design methodology. For the first time, designers can optimize and lock the performance of individual design blocks even when blocks are moved or integrated with other optimized functions. The Stratix family's unique combination of unmatched core performance, high memory bandwidth, digital signal processing (DSP) functionality, high-speed I/O performance, and blockbased design methodology results in new levels of system integration for high-bandwidth system-on-aprogrammable-chip (SOPC) designs.

### **New Levels of System Integration**

Stratix devices are manufactured on a state-of-the-art 1.5-V, 0.13-µm, all-layercopper SRAM process, with densities ranging from 10,570 to 114,140 logic elements (LEs). The Stratix family offers up to 10 Mbits of RAM with its TriMatrix<sup>TM</sup> memory structure. Comprised of three sizes of embedded memory blocks, the TriMatrix memory structure is optimized for high memory bandwidth and large memory storage requirements.

continued on page 4

### **Inside This Issue:**

- Stratix Devices Combined with Quartus II Version 2.0 Provides Top Performance Page 8

- Optimizing Nios System Performance Using Custom Instructions Page 18

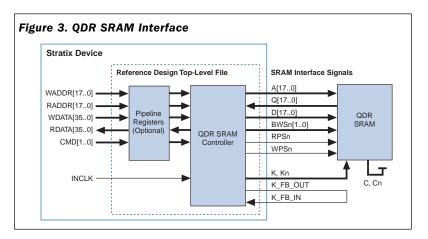

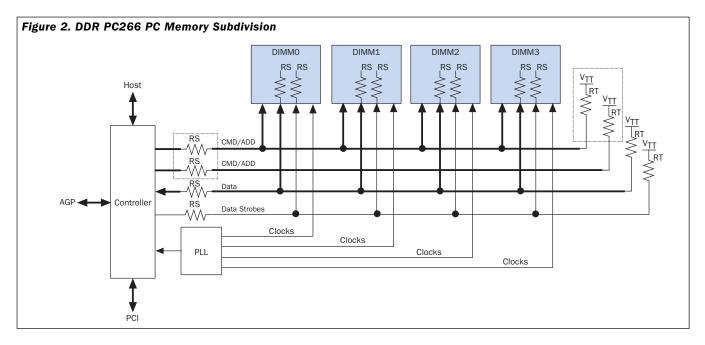

- Interfacing to External Memories Using Stratix Devices Page 28

- Stratix Frequently Asked Questions

Page 46

# Message from the <u>CEO</u>

## **Stratix Devices Provide New Levels of Integration**

Last year was a banner year for Altera. With first-to-market products like the Mercury<sup>TM</sup> devices, the Excalibur<sup>TM</sup> embedded processor solutions, the HardCopy<sup>TM</sup> devices—and process technology milestones such as industry-first all-copper 0.13-µm programmable logic devices (PLDs)—we are in a position to further gain on our leadership position in the PLD industry. Today, Altera ushers in a new era for programmable logic with the introduction of the Stratix<sup>TM</sup> device family, the industry's fastest, most powerful PLD. Stratix devices have three times more memory and 22% more logic elements (LEs) than our competitor's devices and Stratix devices yield an astounding 40% increase in performance from our previous architecture. With the inclusion of dedicated digital signal processing (DSP) functionality, Stratix devices address DSP and computationally complex applications up to twice as fast as any other PLD in the industry. All that power

is loaded onto a die that is 35% smaller than previous architectures. Building on our long history of innovation, Altera is once again breaking PLD boundaries and delivering the fastest devices in the industry while achieving the highest levels of integration with the most memory, logic elements, and DSP functionality in a PLD.

The Stratix architecture was built from the ground up and is a result of extensive customer feedback. Architectural innovations allow us to address our customers' needs for more processing power, speed, functionality, and cost efficiencies. Most significant, however, is how PLD design is changing as these devices grow in density and complexity to include more system functionality. In the past, an individual designer used multiple PLDs to create a single system. Today, we see teambased system-on-a-programmable-chip (SOPC) designs intended for a single device. Sections of a single large system design are divided among multiple engineers, resulting in a "block-based" design methodology. To address these increasing complexities, Altera simplified the design process by enabling a true timing-locked block-based design methodology. For the first time, a designer or teams of designers can work on specific areas of a design, lock in the timing integrity during the integration process, and break the endless loop of re-optimization. The powerful combination of our Stratix devices and the LogicLock<sup>™</sup> capabilities of our Quartus<sup>®</sup> II design software allows team-based SOPC designs to not only shorten design cycles from months to weeks, but to dramatically increase overall system performance by as much as 100%.

Initial feedback on the Stratix devices has been overwhelmingly positive. Many beta customers were given access to the Quartus II software for Stratix design last November and found its increased performance to be unparalleled. PLD customers now have the performance boost they were waiting for and the option to migrate these high-density designs to a lower-cost HardCopy device—a very compelling solution.

Altera's new, powerful, Stratix device family is further proof of our steadfast commitment to deliver to our customers the best, most innovative solutions so that they can focus on their core competencies and get their products to market in a timely, risk-free, and cost efficient manner.

John Daane

# Table of *Contents*

### **Features**

| Altera Provides New Levels of System             |   |

|--------------------------------------------------|---|

| Integration with the Introduction of the Stratix |   |

| Device Family                                    | 1 |

| Stratix Devices Combined with Quartus II         |   |

| Version 2.0 Provides Top Performance             | 8 |

### **Devices & Tools**

| Quartus II Now Supports Stratix Devices     | 10 |

|---------------------------------------------|----|

| Nios 2.0 Now Shipping                       | 10 |

| APEX II Board Offerings                     | 12 |

| Mercury Silicon Available in Production     |    |

| Mode                                        | 13 |

| APEX 20KC Available in Production Mode      | 13 |

| ACEX 1K Availability                        | 14 |

| Altera Provides Complete Silicon & Software |    |

| Support for the IEEE 1532 Standard          | 15 |

| Enhanced Configuration Devices              | 15 |

| SignalProbe Compilation Enables Fast        |    |

| System Debugging with the Quartus II        |    |

| Software                                    | 17 |

|                                             |    |

### **Design Tips**

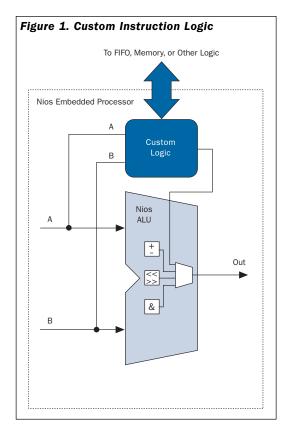

| Optimizing Nios | System Perfo | rmance |    |

|-----------------|--------------|--------|----|

| Using Custom    | Instructions |        | 18 |

### **Contributed Articles**

| Creating an ASIC-Like Flow Using Synopsys |    |

|-------------------------------------------|----|

| Tools & Stratix Devices                   | 21 |

| LeonardoSpectrum Supports Advanced        |    |

| Features in Stratix Devices               | 22 |

| Synplicity's Advanced Support for Stratix |    |

| Devices                                   | 24 |

### **Customer Application**

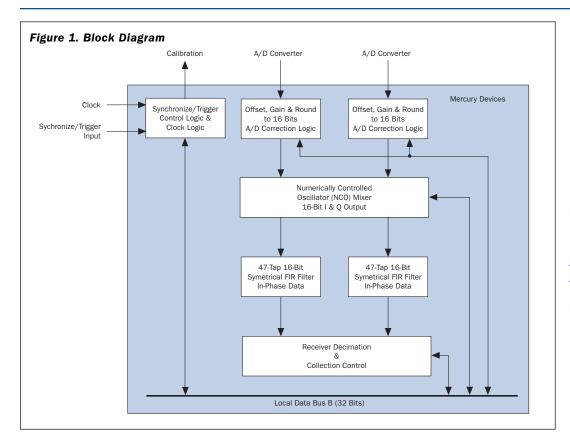

| Mercury Devices Ena | able Echotek's |    |

|---------------------|----------------|----|

| Software-Defined    | Radio 2        | 26 |

### **Technical Articles**

| Interfacing to External Memories Using<br>Stratix Devices |

|-----------------------------------------------------------|

| Stratix Devices Provide the Solution for                  |

| High-Bandwidth Memory Architecture                        |

| in PLDs 30                                                |

| Resolving Clock Management Issues Using                   |

| Stratix Devices                                           |

| Remote System Upgrades with                               |

| New Stratix Devices                                       |

| DSP Blocks in Stratix Devices Boost                       |

| DSP Performance                                           |

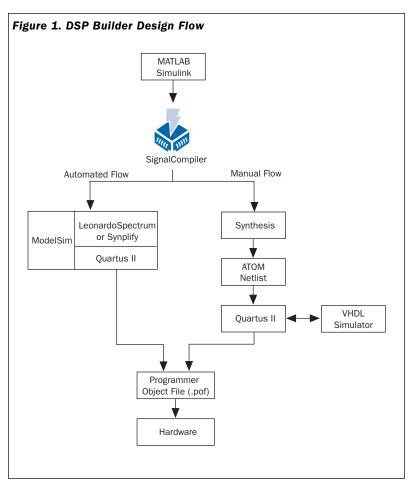

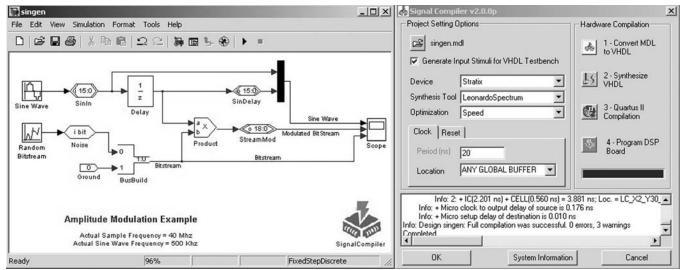

| Altera Simplifies DSP Design with                         |

| DSP Builder & Stratix Devices                             |

| Using Terminator Technology in Stratix Devices            |

| to Address System Design Challenges 40                    |

| Stratix Devices Deliver the Features &                    |

| Flexibility for High-Speed Interface Design 42            |

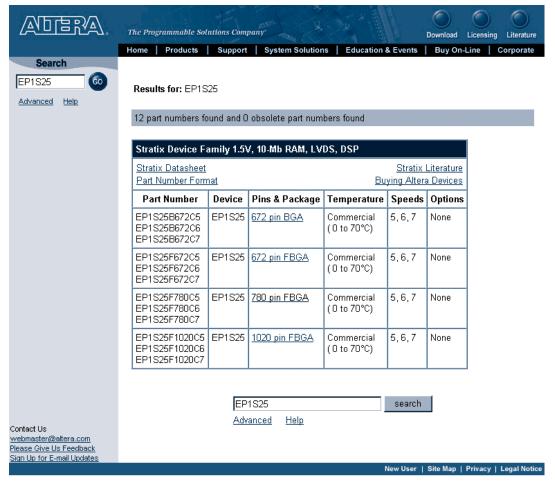

### Altera News

| Altera | Improves | Web Site | by I | Integratir | ng Ne | ew |    |

|--------|----------|----------|------|------------|-------|----|----|

| Part   | Number   | Search   |      |            |       |    | 45 |

### In Every Issue

| Stratix Frequently Asked Questions | 46 |

|------------------------------------|----|

| Discontinued Devices Update        | 49 |

| How to Contact Altera              | 50 |

Altera, ACAP, ACCESS, ACEX, ACEX 1K, AMPP, APEX, APEX 20K, APEX 20KC, APEX 20KE, APEX II, Atlantic, Avalon, BitBlaster, ByteBlaster, ByteBlaster, MV, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, DirectDrive, E+MAX, Excalibur, FastTrack, FineLine BGA, FLEX, FLEX 10K, FLEX 10KE, MAX 7000B, MAX 7000B, MAX 7000B, MAX 3000, MAX+PLUS, MAX+PLUS II, MegaCore, MegaLAB, MegaRAM, MegaWizard, Mercury, MultiCore, MultiVolt, MultiTrack, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, PowerGauge, Quartus, Quartus II, RapidLAB, SignalCore, SignalProbe, SignalTap, SignalTap Plus, SoftMode, Stratix, Terminator, The Programmable Solutions Company, TriMatrix, True-LVDS, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: Adobe and Acroabt are registered trademarks of Adobe Systems Incorporated. ARM and the ARM Powered logo are registered trademarks of ARM Limited. HP-UX is a trademark of Hewlett-Packard Company. HyperTransport is a trademark of HyperTransport Consortium. Mentor Graphics is a registered trademark and Exemplar, LeonardoSpectrum, and ModelSim are trademarks of Mentor Graphics Corporation. Nchester Electronics is a registered trademark of Rochester Electronics, Inc. Sun is a registered trademark and Solaris is a trademark of Sun Microsystems, Inc. Synplicity, Synplify Propused trademarks of Synplicity, Inc. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor

Altera's products and features could differ from those projected in this publication and are provided solely as an estimate to the reader.

Δ

John Panattoni, Publisher Greg Steinke, Technical Editor Pete Santana, Cover Layout 101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 **n\_v@altera.com**

Copyright © 2002 Altera Corporation. All rights reserved.

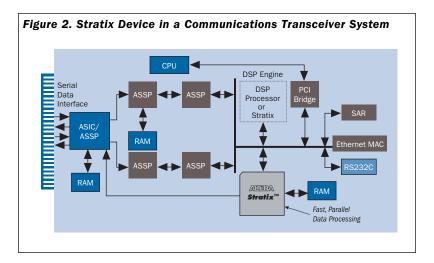

The Stratix device family was specifically designed to address the increasing bandwidth requirements of highspeed systems. Altera Provides New Levels of System Integration with the Introduction of the Stratix Device Family, continued from page 1

Stratix devices include up to 28 embedded DSP blocks that eliminate the performance bottlenecks in DSP applications. Comprised of multiply and accumulate circuitry, the DSP blocks provide predictable performance and significant resource savings for complex applications that require high-data throughput. With up to 12 phase-locked loops (PLLs) and up to 40 system clocks for system-level clock management, support for many single-ended and differential I/O electrical standards, on-chip termination, and remote system upgrade circuitry, Stratix devices bring new levels of system integration for SOPC designs. Table 1 describes some of the highlights of the Stratix devices. Table 2 shows a family overview with the wide range of features and packages available.

### High-Performance Architecture for Block-Based Design

The Stratix device family is based on a new architecture, built from the ground up to power complex designs to new levels of system integration. In combination with the Altera<sup>®</sup> Quartus<sup>®</sup> II LogicLock<sup>™</sup> design methodology, Stratix devices simplify the difficult process of design integration, providing the basis upon which block-based designs can be developed and optimized for maximum performance.

### **Stratix Architectural Advances**

The innovative, high-performance Stratix architecture is based on the MultiTrack<sup>TM</sup> interconnect with DirectDrive<sup>TM</sup> technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths used for inter- and intra-block connectivity. DirectDrive technology is a proprietary, deterministic routing technology that enables identical routing resource usage for any function regardless of placement within the device. DirectDrive technology simplifies the system integration stage of block-based design by eliminating the countless, time-consuming system re-optimization cycles that typically follow design changes and additions.

#### Table 1. Stratix Highlights

| Feature                                    | Benefit                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance<br>Architecture           | New routing structure that<br>facilitates block-based design for<br>maximum system performance<br>with minimum development time                                                                                                                                                                                                                                          |

| TriMatrix Memory                           | Three sizes of embedded<br>memory blocks with up to<br>10 Mbits of RAM, up to<br>12 terabits per second of<br>memory bandwidth, and data<br>transfer rates over 300 MHz per<br>RAM block                                                                                                                                                                                 |

| DSP Blocks                                 | Dedicated blocks run at up to<br>250 MHz for data throughput<br>performance of up to 2.0 giga<br>multiply-accumulate operations<br>per second (GMACS) per DSP<br>block                                                                                                                                                                                                   |

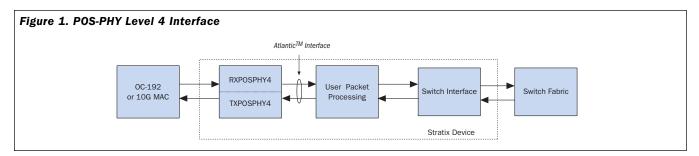

| High-Speed I/O Standards<br>and Interfaces | Support for high-speed I/O<br>standards and high-speed<br>interfaces such as 10-Gigabit<br>Ethernet (XSBI), SFI-4, POS-PHY<br>Level 4, HyperTransport <sup>™</sup><br>technology, RapidIO <sup>™</sup> standard,<br>and UTOPIA Level 4 interfaces at<br>up to 840 megabits per second<br>(Mbps), as well as support for<br>advanced external memory<br>device interfaces |

| Clock Management<br>Circuitry              | Up to 12 PLLs and up to 40<br>system clocks plus features<br>such as programmable<br>bandwidth, clock switchover, PLL<br>reconfiguration, spread-spectrum<br>clocking, frequency synthesis,<br>and programmable phase and<br>delay shift                                                                                                                                 |

| Terminator <sup>™</sup> Technology         | On-chip serial, parallel, and differential termination                                                                                                                                                                                                                                                                                                                   |

| Remote System Upgrades                     | Enables updates to PLDs in remote locations                                                                                                                                                                                                                                                                                                                              |

### **High-Bandwidth Solutions**

The Stratix device family was specifically designed to address the increasing bandwidth requirements of high-speed systems. All aspects of bandwidth are increased: overall memory bandwidth, arithmetic bandwidth for DSP applications, I/O bandwidth, and core performance.

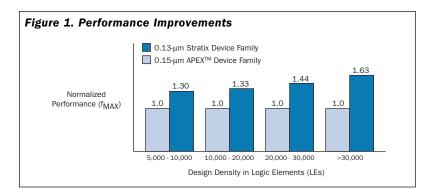

Built on the performance-optimized and highly flexible MultiTrack interconnect routing structure, Stratix devices offer a dramatically

| Table 2. Stratix Family Overview                                   |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EP1\$10                                                            | EP1\$20                                                                                                                                                   | EP1\$25                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EP1530                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EP1\$40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EP1S60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EP1580                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EP1\$120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10,570                                                             | 18,460                                                                                                                                                    | 25,660                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32,470                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41,250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57,120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 79,040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 114,140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 94                                                                 | 194                                                                                                                                                       | 224                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 384                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 574                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 767                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1,118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 60                                                                 | 82                                                                                                                                                        | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 292                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 364                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 520                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1                                                                  | 2                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 920,448                                                            | 1,669,248                                                                                                                                                 | 1,944,576                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3,317,184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3,423,744                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5,215,104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7,427,520                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10,118,016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6                                                                  | 10                                                                                                                                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

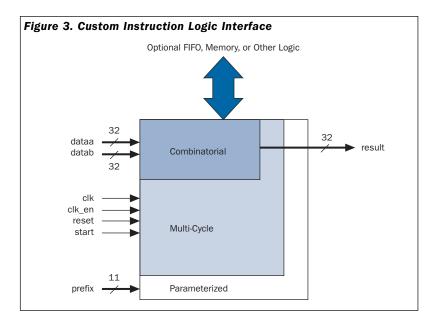

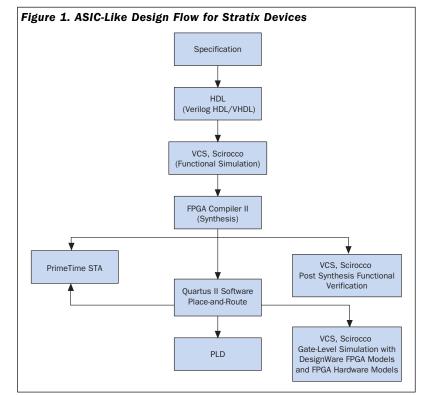

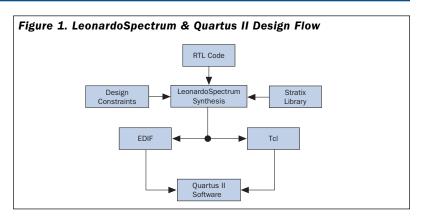

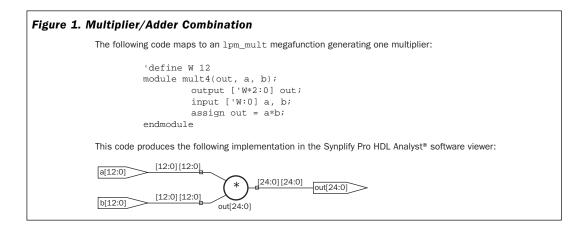

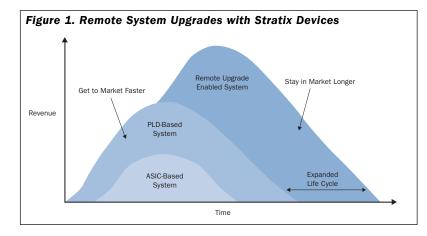

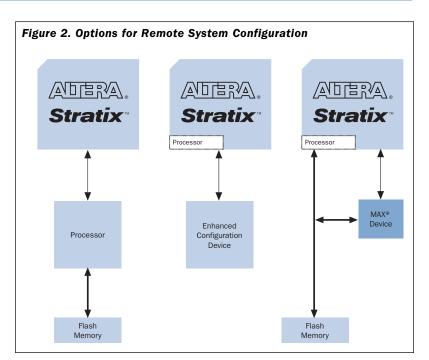

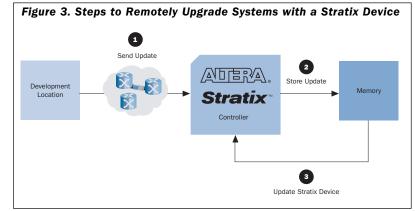

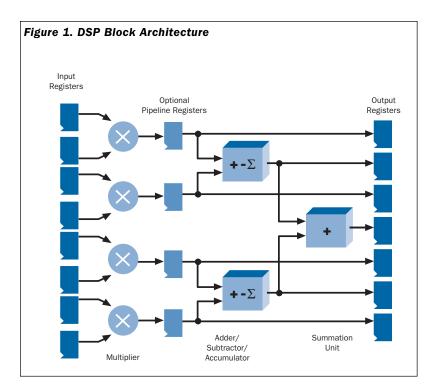

| 48                                                                 | 80                                                                                                                                                        | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |