Newsletter for Altera Customers

# **Power Up with New Quartus II Verification Features**

As increasingly complex, team-based system-on-a-programmable-chip (SOPC) design becomes the norm, hardware, software, and systems designers grapple with new verification challenges in addition to the urgency of the usual time to market, cost, and performance goals. Verification is historically the longest and most critical portion of system-level design. To ease those verification blues, engineers can now power up with a comprehensive, multi-faceted suite of verification features in Altera's Quartus<sup>®</sup> II software.

The latest Quartus II software release (version 2.1) includes the SignalTap<sup>®</sup> II logic analyzer and the SignalProbe<sup>™</sup> verification tool to provide deeper levels of analysis and greater visibility into the design's operation. These features leverage the generous memory and innovative MultiTrack<sup>™</sup> routing resources of Altera's new Stratix<sup>™</sup> device family, which is shipping today.

continued on page 4

### **Inside This Issue:**

Introducing the SignalTap II Logic Analyzer Page 8 SOPC Builder—From **Concept to System in** Minutes Page 11 Implementing a Barrel **Shifter Using Stratix DSP** Blocks Page 29 **Stratix Devices Provide Unprecedented Performance** & Area Utilization for DSP Applications Page 31

# Message from *Software*

### Quartus II—Altera's True Customer Experience

The Altera<sup>®</sup> Quartus<sup>®</sup> II design software is the foundation of Altera's system-on-aprogrammable-chip (SOPC) design environment and is Altera's true customer experience. As the only product that most of you, our customers, get intimately involved with, the Quartus II software is designed and developed to deliver complete satisfaction, meeting your demands for ease-of-use, the fastest compile times, innovative design and verification features, and continual performance improvements.

Altera has reclaimed its title as the champion of design software solutions for programmable logic. By acting on the recommendations of hardware and software design engineers around the world, Altera has assembled an arsenal of software and development tools to

accomplish a single goal: to give you a powerful yet easy-to-use environment in which to develop the next generation of SOPC solutions. The positive response to the Quartus II software version 2.0 proves that we are achieving that goal.

This issue of *News & Views* introduces the Quartus II software version 2.1, a fully integrated design platform that also embraces today's growing trend of embedded microprocessors and peripherals. Altera's SOPC Builder (now included as a standard part of the Quartus II software) and DSP Builder tools offer both hardware and software designers the ability to communicate the status of their specific portions of the system-under-development. In effect, the system definition and integration phases of the development are automated, saving time and money. The Quartus II software version 2.1 includes enhanced support for Altera Stratix<sup>TM</sup> devices, the industry's most advanced FPGAs—which are available today. The software includes enhancements to many industry-first developments such the LogicLock<sup>TM</sup> block-based design flow, native support for the Linux operating system, and the PowerGauge<sup>TM</sup> power analysis tool.

This issue focuses on sophisticated verification techniques—new to the Quartus II software version 2.1—that distinguish Altera's superior SOPC methodology as a powerful tool, helping you to meet the new challenges you face in design validation. As you confront the increasing obstacles of designing with high-performance devices, we place laser focus on quick and accurate verification of the design at every level. From formal verification and testbench generation to board-level verification, Altera's SignalTap<sup>®</sup> II logic analyzer and other features in the Quartus II software version 2.1 discussed in this issue deliver increased insight into the powerful tools now available to help you go from concept to system in less time than ever.

Tim Southgate, Vice President of Software & Tools Marketing

# Table of *Contents*

### **Features**

| Power Up with New Quartus II        |

|-------------------------------------|

| Verification Features1              |

| Introducing the SignalTap II        |

| Logic Analyzer                      |

| SOPC Builder—From Concept to System |

| in Minutes11                        |

### **Devices & Tools**

| Stratix Devices Now Available                                                                                                                                                                                                                                                                                          | 14                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| More Stratix Devices Supported by Quartus II                                                                                                                                                                                                                                                                           |                                        |

| Version 2.0 Service Pack 1                                                                                                                                                                                                                                                                                             | 14                                     |

| Stratix Support in the Nios Embedded                                                                                                                                                                                                                                                                                   |                                        |

| Processor Version 2.1                                                                                                                                                                                                                                                                                                  | 14                                     |

| Nios Processor Version 2.1 Now Shipping                                                                                                                                                                                                                                                                                | 15                                     |

| Nios Subscription Renewal                                                                                                                                                                                                                                                                                              | 15                                     |

| SOPC Builder Now Supports Both Nios                                                                                                                                                                                                                                                                                    |                                        |

| & Excalibur Embedded Processors                                                                                                                                                                                                                                                                                        | 15                                     |

| Excalibur Solutions Pack                                                                                                                                                                                                                                                                                               | 15                                     |

| APEX II Availability                                                                                                                                                                                                                                                                                                   |                                        |

| APEX II HardCopy Solution                                                                                                                                                                                                                                                                                              | 16                                     |

| APEX II Industrial Offerings                                                                                                                                                                                                                                                                                           |                                        |

| ACEX 1K Availability                                                                                                                                                                                                                                                                                                   | 16                                     |

| Mercury Silicon Available in                                                                                                                                                                                                                                                                                           |                                        |

|                                                                                                                                                                                                                                                                                                                        |                                        |

| Production Mode                                                                                                                                                                                                                                                                                                        | 17                                     |

| Production Mode<br>APEX 20KC Available in Production Mode                                                                                                                                                                                                                                                              |                                        |

|                                                                                                                                                                                                                                                                                                                        | 17                                     |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page                                                                                                                                                                                                                 | 17<br>17<br>18                         |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition                                                                                                                                                                                       | 17<br>17<br>18<br>18                   |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition<br>Enhanced Configuration Devices                                                                                                                                                     | 17<br>17<br>18<br>18                   |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition<br>Enhanced Configuration Devices<br>Quartus II Version 2.0 for Linux                                                                                                                 | 17<br>17<br>18<br>18<br>18             |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition<br>Enhanced Configuration Devices                                                                                                                                                     | 17<br>17<br>18<br>18<br>18             |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition<br>Enhanced Configuration Devices<br>Quartus II Version 2.0 for Linux<br>Now Available<br>Introducing the SignalTap II                                                                | 17<br>17<br>18<br>18<br>18<br>19       |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition<br>Enhanced Configuration Devices<br>Quartus II Version 2.0 for Linux<br>Now Available<br>Introducing the SignalTap II<br>Embedded Logic Analyzer                                     | 17<br>17<br>18<br>18<br>18<br>19       |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition<br>Enhanced Configuration Devices<br>Quartus II Version 2.0 for Linux<br>Now Available<br>Introducing the SignalTap II<br>Embedded Logic Analyzer<br>Quartus II Version 2.0 SP1 & SP2 | 17<br>17<br>18<br>18<br>18<br>19<br>19 |

| APEX 20KC Available in Production Mode<br>Industrial-Grade APEX Offerings<br>MAX Applications Web Page<br>MAX Process Transition<br>Enhanced Configuration Devices<br>Quartus II Version 2.0 for Linux<br>Now Available<br>Introducing the SignalTap II<br>Embedded Logic Analyzer                                     | 17<br>17<br>18<br>18<br>18<br>19<br>19 |

### **Contributed Articles**

| El Camino Develops Application to Embed |

|-----------------------------------------|

| Digital Data into Analog Video Signals  |

| Princeton Technology Group Partners     |

| With Altera to Provide High-Speed       |

| I/O Evaluation Board                    |

| ,                                       |

### **Customer Applications**

| ROWE Engineering Announces Stratix           |

|----------------------------------------------|

| FPGA Development Board24                     |

| Altera's EP20K30E Device                     |

| Cornerstone for PCMCIA-Based Camera          |

| ETAS Improves Automotive Control System with |

| Excalibur Devices                            |

### **Technical Articles**

| Implementing a Barrel Shifter            |   |

|------------------------------------------|---|

| Using Stratix DSP Blocks2                | 9 |

| Stratix Devices Provide Unprecedented    |   |

| Performance & Area Utilization           |   |

| for DSP Applications 3                   | 1 |

| Configuring Altera's FPGAs Using the     |   |

| MicroBlaster Source Code & the Motorola  |   |

| MCF5206e (ColdFire) Embedded Processor 3 | 3 |

### Altera News

| Altera Features On-Line Solution Centers | 5 |

|------------------------------------------|---|

| Cost of Using PLDs vs. ASICs             | 6 |

### In Every Issue

| Discontinued Devices Update | 37 |

|-----------------------------|----|

| How to Contact Altera       | 38 |

| News & Views On-Line Survey | 38 |

Altera, ACAP, ACCESS, ACEX, ACEX 1K, AMPP, APEX, APEX 20K, APEX 20KC, APEX 20KE, APEX II, Atlantic, Avalon, BitBlaster, ByteBlaster, ByteBlaster, MV, Classic, ClockBoost, ClockShift, CoreSyn, DirectDrive, E+MAX, Excalibur, FastLUT, FastTrack, FineLine BGA, FLEX, FLEX 10K, FLEX 10KE, FLEX 10KA, FLEX 8000, FLEX 6000, FLEX 6000A, Flexible-LVDS, HardCopy, IP MegaStore, Jam, LogicLock, MasterBlaster, MAX, MAX 9000, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000AE, MAX 7000B, MAX 3000, MAX 3000A, MAX +PLUS, MAX+PLUS II, MegaCore, MegaLAB, MegaWizard, Mercury, MultiCore, MultiVolt, MultiTrack, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, PowerGauge, Quartus, Quartus II, RapidLAB, SignalCore, SignalProbe, SignalTap, SignalTap Plus, SignalTap II, SoftMode, Stratix, Terminator, The Programmable Solutions Company, TriMatrix, True-LVDS, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: Adobe and Acrobat are registered trademarks of Adobe Systems Incorporated. HP-UX is a trademark of Hewlett-Packard Company. HyperTransport is a trademark of HyperTransport Consortium. Mentor Graphics is a registered trademark and Exemplar, LeonardoSpectrum, and ModelSim are trademarks of Mentor Graphics Corporation. Microsoft, Windows, Windows 98, and Windows NT are registered trademarks of Microsoft Corporation. RapidIO is a trademark of RapidIO Trade Association. Rochester Electronics is a registered trademark of Rochester Electronics, Inc. Sun is a registered trademark and Solaris is a trademark of Sun Microsystems, Inc. Synplicity, Synplify, Synplify Pro are registered trademarks of Synplicity, Inc. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. The actual availability of Altera's products and features could differ from those projected in this publication and are provided solely as an estimate to the reader.

Copyright © 2002 Altera Corporation. All rights reserved.

John Panattoni, Publisher Greg Steinke, Technical Editor Pete Santana, Cover Layout 101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7809 n\_v@altera.com

*Power Up with New Quartus II Verification Features, continued from page 1*

### **Comprehensive SOPC Verification Solution**

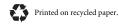

The Quartus II software now provides the most comprehensive verification solutions available for traditional programmable logic device (PLD) hardware design and complete SOPC solutions. Table 1 provides an overview of the verification solutions available to Quartus II designers, and which stage of the design process relies on each solution. The table order is arranged in approximate order of use in the design flow.

As shown in Table 1, Quartus II users have several verification options available. Some solutions are supported by both the Quartus II software and third-party tools. You can select the flow to get a design completed in the shortest possible time. In team environments, designers can easily pass Quartus II-generated simulation netlists to other engineers or directly to third-party software tools for further analysis. For example, board-level designers can perform other signal integrity analysis on high-speed I/O signals or board-level simulations using Quartus II software-generated simulation files, and PLD designers can pass Quartus II PowerGauge power consumption estimates to board-level designers before board design and layout.

### **Hardware-Software Co-Simulation**

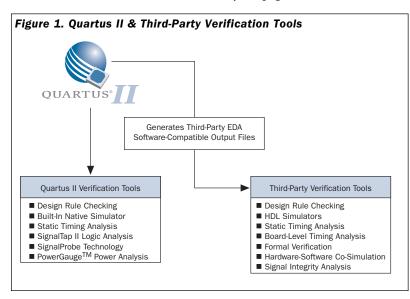

The Quartus II software and the SOPC Builder system development tool can output complete system simulation models and testbenches that let you simulate hardware and software at the same time. This feature includes simulating your embedded processor code, operating system code, PLD hardware, and internal and external memory. Wizards initialize the memory models and create sample universal asynchronous receiver/ transmitter (UART) character streams for simulation. PLD designers can use traditional thirdparty HDL simulators while software engineers can simultaneously run HDL simulators and software debugging tools to interactively control the simulation. See Figure 2.

To optimize this flow, Altera has developed an Excalibur<sup>TM</sup> stripe simulator (ESS), which is a fast, functional stripe simulator and an instruction set simulator for the ARM922T<sup>TM</sup> processor. The ESS enables you to simulate systems in minutes instead of days. For example, an Excalibur EPXA10 device booting the WindRiver VxWorks operating system can be simulated in just three minutes.

| Verification<br>Method                                                  | Description                                                                                                                                                   | Quartus II Software or<br>Subscription<br>Support                                                                   | Third-Party<br>Support                                                                   | Stage Used                                    |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------|

| Design rule checking                                                    | Checks designs for coding<br>styles that will cause<br>synthesis, simulation, or<br>design migration problems<br>later                                        | Quartus II software design<br>assistant                                                                             | Atrenta (SpyGlass)<br>Synopsys (Leda)                                                    | PLD design                                    |

| Functional verification                                                 | Checks if a design meets<br>functional requirements before<br>you perform place-and-route                                                                     | Quartus II software simulator<br>ModelSim®-Altera                                                                   | Cadence (NC-Verilog, NC-VHDL)<br>Mentor Graphics® (ModelSim)<br>Synopsys (VCS, Scirocco) | PLD design                                    |

| Testbench generation                                                    | Reduces the number of hand-<br>generated test vectors                                                                                                         | Waveform-to-testbench converter<br>Testbench template generator                                                     |                                                                                          | PLD design                                    |

| Static timing analysis                                                  | Analyzes, debugs, and<br>validates a design's<br>performance after place-and-<br>route                                                                        | Quartus II software static timing<br>analyzer                                                                       | Synopsys (PrimeTime)                                                                     | PLD design                                    |

| Timing simulation                                                       | Performs a detailed gate-level<br>timing simulation after place-<br>and-route                                                                                 | Quartus II Simulator<br>ModelSim-Altera                                                                             | Cadence (NC-Verilog, NC-VHDL)<br>Mentor Graphics (ModelSim)<br>Synopsys (VCS, Scirocco)  | PLD design                                    |

| Hardware-software co-<br>simulation                                     | Quickly simulates interaction<br>between PLD hardware,<br>embedded processors,<br>memory, and peripherals                                                     | ModelSim-Altera                                                                                                     | Mentor Graphics (ModelSim)                                                               | PLD design<br>Board design<br>Software design |

| In-system debug                                                         | Enables you to see the<br>behavior of internal nodes in-<br>system and at system speeds                                                                       | Quartus II SignalTap II logic<br>analyzer<br>Quartus II SignalProbe technology                                      | Bridges 2 silicon                                                                        | PLD design<br>Software design                 |

| Board-level timing analysis                                             | Verifies that the PLD and the<br>entire board meets system<br>timing requirements                                                                             |                                                                                                                     | Innoveda (Blast)<br>Mentor Graphics (Tau)                                                | Board design                                  |

| Signal integrity analysis<br>and electromagnetic<br>compatibility (EMC) | Verifies that the high-speed<br>I/O signals will be transmitted<br>reliably and within EMC<br>guidelines                                                      | Quartus II software design-<br>specific input/output buffer<br>information specification (IBIS)<br>model generation | Cadence (SPECCTRAQuest)<br>Innoveda (XTK, Hyperlynx)<br>Mentor Graphics (Interconnectix) | Board design                                  |

| Formal verification                                                     | Identifies differences between<br>source register transfer level<br>(RTL) netlists and post place-<br>and-route netlists without<br>creating any test vectors |                                                                                                                     | Synopsys (Formality)<br>Verplex (Conformal LEC)                                          | PLD design                                    |

| Power estimation                                                        | Estimates the power<br>consumption of your device<br>using your design's operating<br>characteristics                                                         | Quartus II Simulator<br>ModelSim-Altera                                                                             | Mentor Graphics (ModelSim)                                                               | PLD design<br>Board design                    |

*Power Up with New Quartus II Verification Features, continued from page 5*

The following sections describe the verification tools available in the Quartus II software.

Design Rule Checking

Design rule checking tools contain a set of customized rules that designers can apply to a design to initially check if the design can be synthesized, simulated, and migrated to a particular device technology. The upcoming Quartus II software version 2.1 contains design rule checking for designs targeted for an Altera HardCopy<sup>™</sup> device. Altera is working closely with Atrenta and Synopsys to develop customized rule sets for their design rule checking tools. Customized rule sets help you optimize designs targeting Altera devices early in the design process.

#### Testbench Generation

In addition to outputting verification netlists for use in third-party HDL simulators, the Quartus II software version 2.0 and later can create HDL testbench templates that can jumpstart verification efforts. The Quartus II software can also create complete HDL testbenches from Quartus II software simulator waveform files. The Altera SOPC Builder and DSP Builder software tools can also generate complete system simulation models and testbenches.

#### Static Timing Analysis

You can use static timing analysis to analyze, debug, and validate a design's performance. Static timing analysis measures the delay of every path in the design and reports the design's performance. The Quartus II software provides advanced timing analysis features such as multi-cycle and multi-clock analysis. The Quartus II software also outputs industry-standard Standard Delay Format Output files (.sdo) and STAMP format files for further analysis by third-party chip-level or board-level timing analysis tools.

### Excalibur Simulation

Excalibur embedded processor solutions include HDL designs as well as embedded software that is executed by the embedded processor. The only way to verify that the hardware and software portions of the design are working together correctly before building a prototype is to co-simulate the hardware and software at the same time.

The Quartus II software outputs Excalibur simulation models that designers can use with ModelSim-Altera and other third-party simulation products to simulate complete systems, including embedded processors, embedded processor software, memory, and custom programmable logic systems. Excalibur simulation models included with Altera design software subscriptions include bus-functional models for peripheral development, fast-functional simulation and instruction set simulation models for quick hardware-software co-simulation (simulates up to 500K instructions per second), and cycle-accurate models to verify the processor and PLD system's exact operation.

#### Formal Verification

Formal verification is a relatively new verification technology that uses mathematical algorithms to verify that a post-place-and-route netlist provides the same functionality as a pre-place-and-route netlist. Formal verification tools do not require the user to create any test vectors and can significantly accelerate verification efforts for large designs. The upcoming Quartus II software version 2.1 will support the Verplex Conformal LEC formal verification tool flow. Support for the Synopsys Formality software is under development for a future release of the Quartus II software.

#### In-System Verification

Altera developed two in-system verification methods that utilize the programmable nature of SOPC designs to help designers analyze their devices' internal nodes or I/O pins while operating insystem and at system speeds. These methods are the SignalTap II logic analyzer and SignalProbe debugging technology. The SignalTap II and SignalProbe technologies fit seamlessly into any third-party synthesis flow and do not require any modifications to the HDL design source files.

The upcoming Quartus II software version 2.1 contains design rule checking for designs targeted for an Altera HardCopy device.

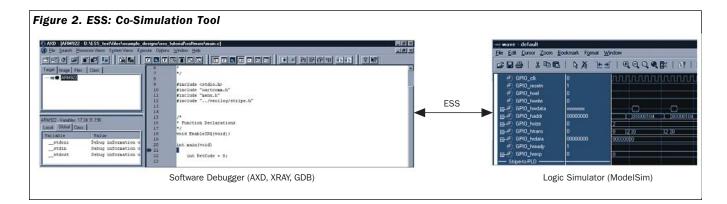

### SignalTap II Logic Analyzer for Hardware Verification

The SignalTap II logic analyzer is Altera's nextgeneration embedded logic analyzer verification tool included in the upcoming Quartus II software version 2.1. The SignalTap II logic analyzer facilitates the verification process by integrating the functionality of one or more logic analyzers within the Quartus II software. The SignalTap II logic analyzer allows the design team to capture the state of any internal node or I/O pin on a device in real time, operating at system speeds. The SignalTap II logic analyzer does not require any external probes or changes to user design files. Data is filtered, captured, and stored in the device's embedded RAM block. Captured data is sent to the Quartus II software waveform viewer via a download cable. For more information on The SignalTap II logic analyzer, refer to "Introducing the SignalTap II Logic Analyzer" on page 8.

### SignalProbe Debugging Technology

The SignalProbe hardware debugging technology, is available in the Quartus II software version 2.0 and later, lets designers incrementally route an internal node to an unused or reserved pin for analysis with an external scope or logic analyzer. Because SignalProbe technology can incrementally route paths from the node(s) of interest to device pin(s), compile times are typically less than 5% of a full compilation. Furthermore, the design's original routing and timing are fully preserved. As the SignalProbe technology reports any delays added in the routing from internal nodes to the device pin (where the external signal capture occurs), designers have an accurate picture of the captured signal's timing relationships. For more information, refer to TB 82: Signal-Probe Compilation Enables Fast System Debugging with the Quartus II Software.

### Signal Integrity & EMC Analysis

The keys to developing systems with high-speed I/O are signal integrity and meeting stringent EMC requirements. The Quartus II software can generate design-specific IBIS models that designers can export to third-party signal integrity and EMC analysis tools such as Cadence SPECCTRAQuest, Innoveda XTK and Hyperlynx, and Mentor Graphics Interconnectix software.

#### PowerGauge Power Analysis

The Quartus II software includes PowerGauge technology, the industry's first integrated power analysis tool. The PowerGauge analysis tool uses the designer's simulation files to link the power consumption estimate with customer-specific design files and operating parameters. Integrated power analysis using the Quartus II Simulator or third-party simulators enables Altera designers to identify and optimize system-level power consumption early in the design cycle.

### ModelSim-Altera

Altera software subscriptions include the Mentor Graphics ModelSim-Altera HDL simulator. For large designs requiring multiple design iterations, the ModelSim-Altera software supports behavioral RTL simulation for pre-place-androute functional verification of HDL code. The ModelSim-Altera software also gives Quartus II users full support for VHDL and Verilog HDL testbenches so they can perform automated and fully repeatable testing of large and complicated designs.

#### Conclusion

Altera's Quartus II software now provides access to the most comprehensive verification solution available for SOPC designs. The Quartus II software provides verification methodologies for each design team member and for each stage of a project including PLD hardware design, board-level design, and embedded software design. The SignalTap II logic analyzer facilitates the verification process by integrating the functionality of one or more logic analyzers within the Quartus II software.

# Introducing the SignalTap II Logic Analyzer

Available exclusively in the Altera<sup>®</sup> Quartus<sup>®</sup> II software, the SignalTap<sup>®</sup> II logic analyzer supports the highest number of channels and sample depths and the fastest acquisition clocks of any embedded logic analyzer in the programmable logic market.

Similar to the original SignalTap logic analyzer, the SignalTap II logic analyzer does not require any external probes or changes to user design files to capture the state of internal nodes or I/O pins in your design. The SignalTap II analyzer also provides the following new features:

- Includes support for multiple devices in a single Joint Test Action Group (JTAG) chain

Allows multiple logic analyzer megafunctions

- in each device in a JTAG chain

- Supports up to 1,024 channels and up to 128K samples per channel

- Supports up to 200-MHz acquisition clocks

- Features new user interface with separate triggering and data-acquisition windows

- Includes up to 10 trigger levels to filter captured data

- Customized display options to make captured data more useful

- Supports Stratix<sup>TM</sup> devices

### SignalTap II Overview

Running at speed under "real-world" system conditions is the ultimate testbench if you want to monitor the active processes within your design as it operates. The SignalTap II logic analyzer allows you to capture the state of internal nodes or I/O pins while the device is running in-system and at system speed. The following components are required to use the SignalTap II logic analyzer to perform logic analysis:

- The Quartus II software

- The megafunctions that are inserted into the device:

- SignalTap II logic analyzer megafunction

- SignalTap II hub

- The download cable:

- ByteBlasterMV<sup>TM</sup> cable

- MasterBlaster<sup>TM</sup> cable

- The design under test

You can store captured data in the Altera device's memory blocks and stream out the data to the Quartus II software waveform display using a ByteBlasterMV or MasterBlaster communications cable (see Figure 1).

Table 1 summarizes the features and benefits of the SignalTap II embedded logic analyzer.

### Multiple Logic Analyzers in a Single Device

The SignalTap II logic analyzer includes support for multiple instances of the logic analyzer megafunction in each device. This support allows you to create a unique embedded logic analyzer (ELA) megafunction for each clock domain present on the device. Additionally, by "reserving" a free node in a particular ELA, you can add an internal register or node to the ELA for data capture without having to recompile later (this feature will be supported in a future release of the SignalTap II logic analyzer).

Logic analyzer megafunctions are defined in SignalTap files (.stp). Each .stp can contain multiple logic analyzer megafunctions. Each .stp file's scope is limited to a single device in the JTAG chain. The Instance Manager is available in the top portion of the new interface and shows all recognized logic analyzers in the design that you can use to capture and store data (see Figure 2).

### Figure 2. Instance Manager

| Instance Manager: ▷ 🕫 | 200          | × |

|-----------------------|--------------|---|

| Instance              | Status       |   |

| 🕏 auto_signaltap      | Ready to Run |   |

| 🛃 auto_signaltap_0    | Ready to Run |   |

# Multiple Logic Analyzers in Multiple Devices in a Single JTAG Chain

The SignalTap II logic analyzer allows multiple devices in a single JTAG chain in combination with multiple logic analyzer megafunctions in each device in that JTAG chain.

### Up to 10 Levels of Trigger Conditions for Each Analyzer

Trigger conditions instruct the SignalTap II analyzer when to start capturing data. Ten levels of trigger conditions offer a great deal of flexibility to set up complex triggering conditions that assist the engineer in isolating reasons for failures or problems.

To set up multiple levels of trigger conditions, use the setup tab in the SignalTap II user interface. You can trigger-out signals to trigger external logic analyzers or oscilloscopes.

### Four Different Trigger Positions

The SignalTap II logic analyzer supports four trigger positions, allowing you to have more control over what data is captured and displayed when a trigger condition is satisfied.

The "pre" trigger position tells the software to save and store 12% of the samples that occurred before the trigger condition was met, and 88% of the samples that occurred after the trigger condition was met.

The "center" trigger position tells the software to save and store 50% of the samples that occurred before the trigger condition was met, and 50% of the samples that occurred after the trigger condition was met.

### Table 1. SignalTap II Features & Benefits

| Feature                                             | Benefit                                                                                                             |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

|                                                     |                                                                                                                     |  |

| Multiple logic analyzers in a single device         | Supports multiple clock domains in a single device                                                                  |  |

| Multiple logic analyzers in multiple                | Allows multiple devices with multiple clock                                                                         |  |

| devices in a single JTAG chain                      | domains to be analyzed                                                                                              |  |

| Up to 10 levels of trigger for each analyzer        | Allows for more complex data capture commands, providing greater accuracy and problem isolation                     |  |

| Four different trigger positions                    | Sets up each trigger to sample at different ranges                                                                  |  |

|                                                     | relative to the triggering event, allowing more<br>accurate data collection                                         |  |

| Up to 1,024 channels in each device                 | Samples many signals and wide-bus structures,<br>allowing for a great deal of data collection to<br>locate problems |  |

| Up to 128K samples in each device                   | Provides more than enough samples than you                                                                          |  |

|                                                     | would normally use for practical applications                                                                       |  |

| Supports clocks up to 200 MHz                       | Samples design data at system frequency                                                                             |  |

| Vendor-independent application program              | Allows third-party software to utilize SignalTap II                                                                 |  |

| interface (API) for source level debug tools        | resources                                                                                                           |  |

| Add nodes, change signal selection, and             | During analysis, if you want to add an internal                                                                     |  |

| change trigger conditions without recompilation (1) | register to the analyzer, you can add it and capture data without recompiling your design                           |  |

| Mnemonic and radix tables                           | Labels signals with true signal names from<br>software source to assist in identification of<br>problem source      |  |

| Auto-detect devices in JTAG chain                   | Confirms connection to device before attempting to initiate data capture                                            |  |

| Auto-detect programming hardware                    | Confirms connection to device before attempting                                                                     |  |

|                                                     | to initiate data capture                                                                                            |  |

| Print waveforms                                     | Allows you to print the waveforms you have                                                                          |  |

|                                                     | captured for reporting                                                                                              |  |

| New, user-friendly interface                        | Easier to use and less cluttered display                                                                            |  |

|                                                     |                                                                                                                     |  |

#### Note to Table 1:

(1) This feature will be supported in a future release of the SignalTap II logic analyzer.

The "post" trigger position tells the software to save and store 88% of the samples that occurred before the trigger condition was met, and 12% of the samples that occurred after the trigger condition was met.

The "continuous" trigger position tells the software to save samples continuously in a circular buffer fashion, until terminated by the user.

continued on page 10

*Introducing the SignalTap II Logic Analyzer, continued from page 9*

Up to 1,024 Channels in Each Device

The number of channels that can be supported in a specific design is largely a function of the available device resources (logic elements (LEs) and RAM). The SignalTap II logic analyzer is capable of managing up to 1,024 channels from one or more logic analyzer megafunctions in each device.

### Up to 128K Samples Per Channel

The number of samples the embedded memory of an Altera device can store is a function of the surplus memory resources on the device that are not consumed by the design under test. The SignalTap II logic analyzer can support up to 128K samples per channel.

### Supports Clocks Up to 200 MHz

Many complex digital systems with FPGAs include clocks that are faster than 100 MHz. With support for clocks at frequencies as high as 200 MHz, the SignalTap II analyzer samples your data at system speeds.

### Add a Node, Change Signal Selection & Change Trigger Conditions Without Recompilation

The SignalTap II logic analyzer enables you to add nodes, change which signals are under sample, and change trigger conditions without recompiling your design.

To add a node, you must reserve a channel on the embedded logic analyzer megafunction before compilation. After capturing data, the reserved channel may then be incrementally connected to a node in the device by use of the SignalProbe<sup>TM</sup> feature. This feature will be supported in future release of the SignalTap II logic analyzer.

### Mnemonic & Radix Tables

The SignalTap II software includes both a mnemonic feature (to associate names with bit patterns) and selectable radices (binary, octal, hexadecimal, 8-bit ASCII, two's complement, unsigned, and signed). You can associate a mnemonic table with a group of signals in the data waveform view or define a mnemonic table based on the number of bits in the group. If you define multiple mnemonic tables with the same bitwidth, you can choose the table from a dropdown list.

### SignalTap II Device Support

You can use the SignalTap II embedded logic analyzers with the following Altera devices:

- Stratix<sup>TM</sup> devices

- Excalibur<sup>TM</sup> devices

- APEX<sup>TM</sup> II devices

- APEX 20K devices

- Mercury<sup>TM</sup> devices

### Conclusion

The SignalTap II logic analyzer supports the highest number of channels, highest sample depth, and fastest acquisition clocks of any embedded logic analyzer in the programmable logic market. By combining the ability to capture large amounts of high-speed data with powerful trigger-condition filters and data display features, you can focus on the most critical data to quickly solve your design problems.

The SignalTap II logic The analyzer is capable of of a managing up to 1,024 sur channels from one or not more logic analyzer Sig megafunctions in each 128 device.

### SOPC Builder—From Concept to System in Minutes

SOPC Builder is an automated system development tool that simplifies the task of creating highperformance system-on-a-programmable-chip (SOPC) designs. The tool accelerates time-tomarket by automating the system definition, integration, and verification phases of SOPC development.

SOPC Builder encompasses all aspects of embedded system design, including software design and verification, within one tool. You can generate embedded systems in a fraction of the time of traditional system-on-chip (SOC) designs. SOPC Builder is integrated within the Altera® Quartus® II software to give programmable logic device (PLD) designers immediate access to this revolutionary new development tool.

With the introduction of million-gate FPGAs, complex intellectual property (IP) cores, and Altera's Nios<sup>®</sup> and Excalibur<sup>TM</sup> embedded processors, the individual technologies are in place to enable true SOPC-level design. SOPC Builder ties all these technologies together in one flow. SOPC Builder, combined with Altera's core technologies, gives you a complete solution for implementing entire embedded systems in programmable logic.

### **SOPC Builder Feature Overview**

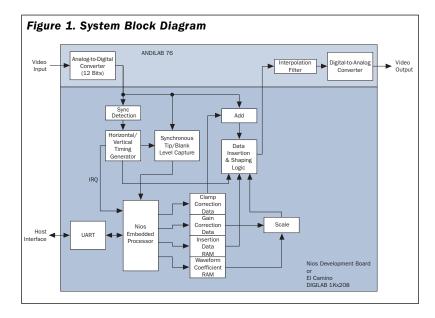

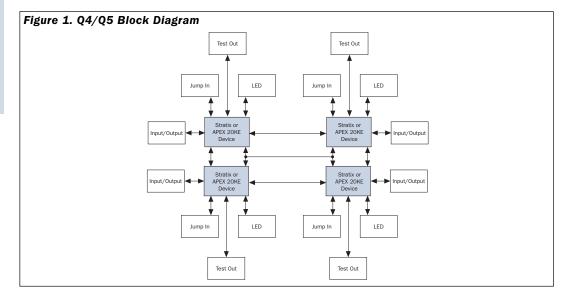

SOPC Builder allows you to create SOPC designs in a fraction of the time traditionally required for embedded SOC designs. SOPC Builder saves design time by significantly simplifying engineering effort in four key areas (see Figure 1).

### **System Definition & Customization**

SOPC Builder provides an intuitive graphical user interface (GUI) that simplifies the definition and customization of your system. Because you do not have to edit HDL code to customize the system, SOPC Builder can save weeks of design time. SOPC Builder presents a wizard tailored for each component, allowing you to easily customize functionality. For example, you can launch wizards to configure the ARM® CPU in Excalibur devices to add a Nios® processor, or to customize each peripheral and memory interface in your system.

### Figure 1. SOPC Builder System Overview

| <u> </u>                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System Customization                                                                                                                                                                                                                                                                                                                                 | System Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Using wizard-based interfaces,<br>you can configure:                                                                                                                                                                                                                                                                                                 | SOPC Builder accelerates system<br>integration by:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| <ul> <li>Excalibur and/or Nios processors</li> <li>Memory map, interrupt priority, boot<br/>address, vector table location</li> <li>Peripherals and on-chip memory</li> <li>Off-chip memory interfaces</li> <li>Component connection, bus<br/>architecture, and arbitration priority</li> </ul>                                                      | <ul> <li>Automatically connecting all<br/>components</li> <li>Creating multi-master bus<br/>architecture with arbitration logic</li> <li>Connecting user-defined blocks of<br/>logic to system</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Software Generation                                                                                                                                                                                                                                                                                                                                  | System Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| <ul> <li>SOPC Builder jump-starts software development by automatically creating:</li> <li>Header files that define the memory map, interrupts and hardware-specific data structures</li> <li>Libraries of routines to access each hardware peripheral</li> <li>Software components, such as an OS korman, driver and (ar protocol data);</li> </ul> | Simulation can start immediately,<br>because SOPC Builder creates a full<br>simulation environment, including:<br>Register transfer level (RTL)<br>simulation model<br>System testbench<br>ModelSim® project with pre-formatted<br>waveforms                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                      | Using wizard-based interfaces,<br>you can configure:<br>• Excalibur and/or Nios processors<br>• Memory map, interrupt priority, boot<br>address, vector table location<br>• Peripherals and on-chip memory<br>• Off-chip memory interfaces<br>• Component connection, bus<br>architecture, and arbitration priority<br><b>Software Generation</b><br>SOPC Builder jump-starts software<br>development by automatically creating:<br>• Header files that define the memory<br>map, interrupts and hardware-specific<br>data structures<br>• Libraries of routines to access each<br>hardware peripheral |  |  |

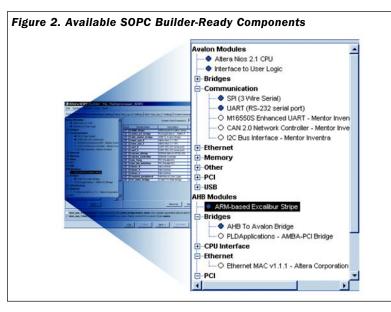

You can select and parameterize intellectual property (IP) blocks from SOPC Builder's extensive list of communication, digital signal processing (DSP), microprocessor, and bus interface IP cores. SOPC Builder-Ready IP cores are available both from Altera and third-party IP vendors (see Figure 2 on page 12). Altera certifies that these IP blocks are SOPC Builder Ready, ensuring seamless integration with the SOPC Builder design flow. If you are designing custom modules, SOPC Builder offers an application programming interface (API) so that you can include and configure any block of IP (either proprietary or purchased) similar to standard SOPC Builder components.

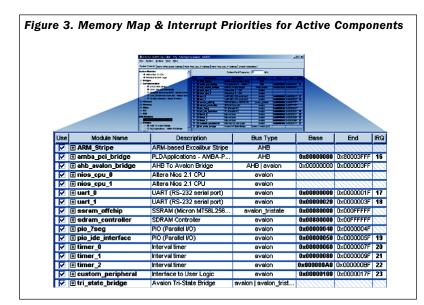

SOPC Builder's GUI allows you to specify the memory map, interrupt priorities (see Figure 3 on page 12), CPU boot address, interrupt vector table location, and program and data memory locations.

continued on page 12

SOPC Builder—From Concept to System in Minutes, continued from page 11

### **System Integration**

SOPC Builder saves weeks or months of design time by automating mundane, error-prone tasks of writing the system. After you customize the system architecture, SOPC Builder automatically generates all necessary logic to integrate processors, peripherals, memories, IP cores, on-chip buses, and bus arbitrators. To connect the system components together, SOPC Builder takes system specifications from the system customization step and creates the appropriate VHDL or Verilog HDL code. The result is an HDL description of the entire system.

If a system contains multiple masters (e.g., two processors, or a processor and a direct memory access (DMA) peripheral), SOPC Builder automatically generates the bus arbitration logic to connect these masters to shared slave peripherals and memories. SOPC Builder uses a technique called slave-side arbitration that allows multiple masters to transfer data simultaneously. The arbitration logic never stalls a master unless multiple masters are attempting to access the same slave at the same time. Using the SOPC Builder GUI, you can easily specify arbitration priorities.

### **Software Generation**

SOPC Builder automatically generates a software development environment that matches the target hardware. You save days or weeks of design time by using the software components generated by SOPC Builder:

- Header files that define the memory map, interrupt priorities, and data structures corresponding to each hardware peripheral

- Software routines to access system hardware peripherals

- Operating system or real-time operating system (RTOS) kernels with the appropriate drivers to control the system hardware

By guaranteeing that the software components always match the hardware, SOPC Builder can save weeks of debug time especially when the hardware design changes.

### **System Verification**

SOPC Builder provides an environment for the simulators of hardware and software. SOPC Builder automatically generates a simulation model of the system, a testbench for it, and a full environment for immediate system simulation. This includes ModelSim® project files, formatted bus-interface waveforms, and a testbench to simulate user software executing on the custom hardware.

Furthermore, Altera development boards provide a means for immediate prototyping of hardware and software. Using development boards, designers can verify their system in hardware, at full system speed, using real-world stimuli. Because the target hardware is programmable, the hardware design can be developed incrementally

Features

and downloaded to the board at each phase. Software can be verified and optimized to work on the exact target hardware, rather than just a simulation model.

### **Evolution of Embedded Design Methodology**

SOPC Builder enables very complex systems to be customized, integrated, and verified in much less time than a traditional embedded design. This increased productivity can be attributed to a few fundamental shifts in embedded design methodology.

### True Design Automation

Many of the tasks of embedded design are systematic, mundane, and error-prone. SOPC Builder can simplify the design process by automating such tasks as wiring together complex buses or creating software header files. SOPC Builder is more than just a tool that helps you design; it is a tool that creates designs, outputting HDL and software.

### Incremental Design

Programmable hardware allows subsystems to be created incrementally, and tested in hardware at each step. Incremental design allows software and hardware developers to work in parallel through much more of the design cycle than in an ASIC-based design flow. For example, the hardware team creates the processor subsystem and passes it to the software team. The software team begins prototyping software immediately. In parallel, the hardware team incrementally develops additional logic.

#### Performance Optimization & Resource Allocation

Customizable hardware allows you optimize performance by allocating the most appropriate hardware and/or software resources to a given task. Time-critical software tasks can be accelerated with custom hardware much more easily in FPGAs than in traditional processor systems. For example, you can integrate SOPC Builder-Ready IP cores with the CPU to optimize the system's processing and throughput performance. Alternately, you can add application-specific custom instructions to a configurable processor such as the Nios processor, drastically improving performance for software algorithms that use the custom instruction.

### Closed-Loop Design

Programmable logic allows the hardware design to evolve to meet the needs of software, thus closing the loop between desired software performance and the actual hardware implementation. You can observe software performance executing on real hardware. If the software needs greater performance for a specific task, you can augment the CPU with hardware acceleration logic.

### Software is Integral

In the SOPC Builder methodology, software is viewed as a system component, allowing protocol stacks, OS/RTOS, and other software components to be easily added to a system.

### **SOPC Builder-Ready IP Cores Now Shipping**

SOPC Builder-Ready IP functions are megafunctions that integrate seamlessly into the SOPC Builder development flow. Over 25 SOPC Builder-Ready IP cores are available today from Altera and the Altera Megafunction Partners Program (AMPP<sup>SM</sup>) partners, which include companies such as Alcatel, Eureka Technology Inc., Mentor Graphics Inventra, and PLD Applications. For a complete list of SOPC Builder-Ready IP and to request a free evaluation copy of the SOPC Builder, visit the Altera web site at http://www.altera.com/sopcbuilder.

### Availability

SOPC Builder is included in the Quartus II design software, in the Nios Development Kit, and in the Excalibur Solutions Pack.

### Stratix

### Stratix Devices Now Available

The first Stratix<sup>™</sup> device, the EP1S25 device, is available now and is shipping in the packages shown in Table 2. Pin-out tables are now available at http://www.altera.com. See Tables 1 and 2 for Stratix availability schedules and software support.

### More Stratix Devices Supported by Quartus II Version 2.0 Service Pack 1

Support for the Stratix EP1S10, EP1S20, and EP1S25 devices in the 672-pin ball-grid array (BGA) and FineLine BGA® packages is currently available in the Altera® Quartus® II software version 2.0 service pack 1.

The feature-rich Stratix devices range in density from 10,570 to 114,140 logic elements (LEs) and offer up to 10 Mbits of embedded RAM through its TriMatrix<sup>TM</sup> memory structure. Stratix devices include up to 28 digital signal processing (DSP) blocks for complex arithmetic functions that require high data throughput. Based on a leadingedge 0.13-µm all-layer-copper SRAM process, Stratix devices support high-speed data transfers through a wide range of high-speed differential and single-ended I/O standards and interfaces. Stratix devices offer up to 12 on-chip phase-locked loops (PLLs) for system-level clock management. In addition, the Terminator<sup>TM</sup> technology in Stratix devices supports on-chip serial, parallel, and differential termination and driver impedance matching. Stratix devices also offer remote system upgrade capabilities, allowing real-time updates to programmable logic devices (PLDs) from remote locations.

#### Table 1. Stratix Device Availability Device **Device Availability Pin-Out Availability** EP1S10 September 2002 Now FP1S20 Q4 2002 Now **FP1S25** Now Now EP1S30 Q4 2002 Now EP1S40 04 2002 Now EP1S60 First half of 2003 Now October 2002 FP1S80 Now EP1S120 First half of 2003 TBD

# Table 2. Stratix Devices & Quartus II Software Advanced Support Availability

| Device  | Package                | Quartus II Software<br>Advanced Support<br>Availability |  |

|---------|------------------------|---------------------------------------------------------|--|

| EP1S10  | 672-pin BGA            | Now                                                     |  |

|         | 672-pin FineLine BGA   | Now                                                     |  |

|         | 780-pin FineLine BGA   | Now                                                     |  |

| EP1S20  | 672-pin BGA            | Now                                                     |  |

|         | 672-pin FineLine BGA   | Now                                                     |  |

|         | 780-pin FineLine BGA   | Now                                                     |  |

| EP1S25  | 672-pin BGA            | Now                                                     |  |

|         | 672-pin FineLine BGA   | Now                                                     |  |

|         | 780-pin FineLine BGA   | Now                                                     |  |

|         | 1,020-pin FineLine BGA | Now                                                     |  |

| EP1S30  | 780-pin FineLine BGA   | Version 2.1                                             |  |

|         | 956-pin BGA            | Now                                                     |  |

|         | 1,020-pin FineLine BGA | Now                                                     |  |

| EP1S40  | 956-pin BGA            | Now                                                     |  |

|         | 1,020-pin FineLine BGA | Now                                                     |  |

|         | 1,508-pin FineLine BGA | Now                                                     |  |

| EP1S60  | 956-pin BGA            | Now                                                     |  |

|         | 1,020-pin FineLine BGA | Now                                                     |  |

|         | 1,508-pin FineLine BGA | Now                                                     |  |

| EP1S80  | 956-pin BGA            | Now                                                     |  |

|         | 1,508-pin FineLine BGA | Now                                                     |  |

|         | 1,923-pin FineLine BGA | Version 2.2                                             |  |

| EP1S120 | 1,923-pin FineLine BGA | Version 2.2                                             |  |

### Stratix Support in the Nios Embedded Processor Version 2.1

The Nios<sup>®</sup> embedded processor version 2.1 includes support for the Stratix device family. Designed to maximize the performance benefits of the Nios embedded processor, the advanced architectural features of Stratix devices combined with the enhanced Nios embedded processor improve the overall system performance of the embedded SOPC Builder to over 125 MHz, offering unparalleled processing power that meets the needs of high-bandwidth systems.

### **EXCALIBUR**

### **Nios Processor Version 2.1 Now Shipping**

Altera is now shipping version 2.1 of the Nios embedded processor. This upgrade to the highly successful Nios embedded processor version 2.0 provides optimized compilation support for Altera's new Stratix device family. Version 2.1 of the Nios processor takes advantage of the Stratix architecture, achieving even higher f<sub>MAX</sub> performance while consuming fewer LE resources. A fully functional Nios embedded processor system in Stratix devices consumes 500 fewer LEs than other Altera architectures and can reach up to 125 MHz. This performance boost, combined with custom instructions and the simultaneous multi-master bus architecture, gives the industry's most powerful configurable processor for programmable logic an even greater performance lead.

This upgrade ships only to customers with a Nios subscription. Customers who purchased the Excalibur<sup>™</sup> Development Kit, featuring the Nios embedded processor longer than one year ago must purchase a Nios subscription renewal to receive this upgrade.

### **Nios Subscription Renewal**

Annual subscription renewal is now available for the Nios embedded processor. With the Nios Subscription Renewal Program, you will receive automatic updates to the Nios embedded processor, SOPC Builder, GNUPro® Toolkit, and the Quartus II Limited Edition software for one year for only \$495. Contact your local Altera sales representative or visit the Altera web site at http://www.altera.com/niosrenewal for more details.

### SOPC Builder Now Supports Both Nios & Excalibur Embedded Processors

Altera is now shipping SOPC Builder including support for the Excalibur embedded stripe. Designers can use SOPC Builder to create custom system-on-a-programmable-chip (SOPC) designs based on the Nios embedded processor. Version 2.1 of the SOPC Builder now supports both the Nios and Excalibur processors in the same easy-to-use design flow. SOPC Builder enables designers to easily combine the Excalibur embedded stripe, multiple Nios embedded processors, any of the SOPC Builder-Ready IP functions, and user-defined logic into a single system. SOPC Builder automatically generates on-chip bus logic for both the advanced high-performance bus (AHB) and the Avalon<sup>™</sup> bus. Designers gain productivity by avoiding the task of creating bus bridges or multi-master arbitration logic.

You can download evaluation versions of SOPC Builder at http://www.altera.com/sopcbuilder. For more information on SOPC Builder, see "SOPC Builder—From Concept to System in Minutes" on page 11.

### **Excalibur Solutions Pack**

The Excalibur Solutions Pack provides software designers with access to Altera utilities and offers a suite of the industry's leading development tools, debugging solutions, and operating system support for building SOPC solutions.

The Excalibur Utilities and Resources CD version 1.4 features the Excalibur stripe simulator (ESS). The ESS facilitates the integration of hardware and software on the Excalibur architecture. Reference designs and updated documentation for the EPXA10 development board and Excalibur devices are also included in the CD.

The third-party tools include evaluation and demonstration versions of system integration tools, debug tools, and operating system support for Excalibur devices:

- Nucleus Plus real-time operating system (RTOS) from the Accelerated Technologies division of Mentor Graphics<sup>®</sup>

- OSE RTOS from OSE Systems

- Embedded Linux operating system from Red Hat.

- XRAY Debugger for Excalibur Devices from Mentor Graphics

- EASI\_Integrator—System Integration tools from Beach Solutions

The Excalibur Solutions Pack is shipped as an upgrade to owners of the Excalibur EPXA10 development kit.

continued on page 16

Devices & Tools, continued from page 15

### APEX II

### **APEX II Availability**

All members of the APEXTM II device family are shipping. This family includes the EP2A70 device, which is the industry's first PLD on a 0.13-µm process. APEX II devices range in density from 16,640 to 67,200 LEs and are memoryrich, offering 4 Kbits of memory per embedded system block (ESB), with total device memory ranging from 416 Kbits to 1.1 Mbits. The APEX II device family supports high-speed data transfers through a wide range of high-speed I/O standards such as the LVDS, PCML, LVPECL, HyperTransport<sup>TM</sup>, HSTL, and SSTL standards. With True-LVDS™ circuitry, APEX II devices can achieve data transfer rates of up to 1 gigabit per second (Gbps) per channel. With these I/O features, you can use APEX II devices in the following applications:

- PHY-link layer interface applications (POS-PHY, Flexbus, and UTOPIA)

- Host-processor interface applications (HyperTransport technology, peripheral component interconnect (PCI), and PCI-X)

- Switch fabric interfaces (CSIX and LCS)

- External memory interfaces (double data rate (DDR), zero bus turnaround (ZBT), and quad data rate (QDR) memory devices)

See Tables 3 and 4 for availability and software support for APEX II devices.

### **APEX II HardCopy Solution**

Altera offers a migration solution from APEX II to HardCopy<sup>™</sup> devices for system designers who need a low-risk, cost-reduction solution for highvolume production. You can prototype time-sensitive applications using APEX II devices and migrate the design to HardCopy devices for highvolume production. HardCopy devices preserve the functionality and timing of the design and allow you to improve time-to-market at the lowest cost.

### **APEX II Industrial Offerings**

Altera has proactively selected industrial-grade devices of the APEX II device family to further

compress design cycles for the fastest possible time-to-market. Industrial-grade production versions of the device offerings are available in a -8 speed grade. Table 5 shows the availability for industrial-grade offerings.

| Table 3. APEX II Device Availability |                         |  |

|--------------------------------------|-------------------------|--|

| Device                               | Production Availability |  |

| EP2A15                               | Now                     |  |

| EP2A25                               | Now                     |  |

| EP2A40                               | Now                     |  |

| EP2A70                               | Now                     |  |

# Table 4. APEX II Devices & Quartus II Software Support

| Device | Package                  | Software<br>Support |  |  |

|--------|--------------------------|---------------------|--|--|

| EP2A15 | 672-pin FineLine BGA     | Now                 |  |  |

|        | 724-pin BGA              |                     |  |  |

| EP2A25 | 672-pin FineLine BGA     | Now                 |  |  |

|        | 724-pin BGA              |                     |  |  |

| EP2A40 | 672-pin FineLine BGA Now |                     |  |  |

|        | 724-pin BGA              |                     |  |  |

|        | 1,020-pin FineLine BGA   |                     |  |  |

| EP2A70 | 724-pin BGA              | Now                 |  |  |

|        | 1,508-pin FineLine BGA   |                     |  |  |

| Table 5. APEX II Industrial Device Offering |                        |                            |  |

|---------------------------------------------|------------------------|----------------------------|--|

| Device Package                              |                        | Production<br>Availability |  |

| EP2A15                                      | 672-pin FineLine BGA   | Now                        |  |

| EP2A25                                      | 672-pin FineLine BGA   | Now                        |  |

|                                             | 724-pin BGA            | Now                        |  |

| EP2A40                                      | 1,020-pin FineLine BGA | Now                        |  |

### ACEX

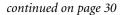

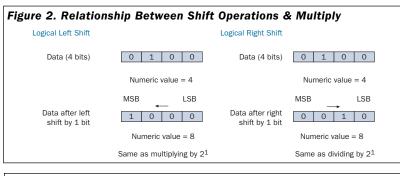

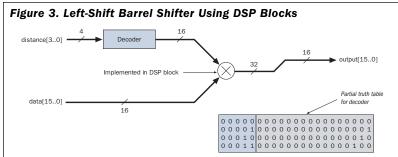

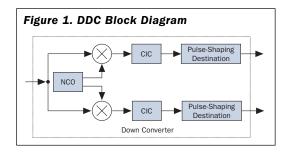

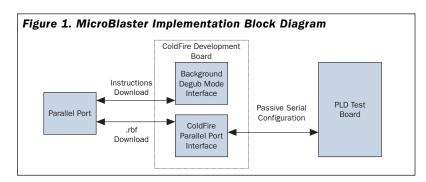

### ACEX 1K Availability