**Newsletter for Altera Customers**

Stratix II

# Innovation to the Power of II

# Altera's Legacy of Innovation Lives On

Innovation has been the cornerstone of the semiconductor industry. Constantly challenged by Moore's law, Metcalf's Law, Gilder's Law, and other phenomena, we thrive when faced with seemingly daunting and insurmountable challenges. Time and time again, through pure genius and just plain entrepreneurial drive, we as an industry have overcome dire predictions and consistently raised the technology bar. At Altera, this passion and burning desire to break barriers and set new standards is in our blood.

As we conclude our twentieth anniversary, we ring in our twenty-first year with the introduction of new architectures that represent significant breakthroughs in programmable logic technology. Just as we've reached new heights in performance, density, and cost over the past two years, we are now launching two new families: Stratix<sup>TM</sup> II and MAX<sup>®</sup> II devices—the industry's largest and fastest FPGAs and the lowest-cost CPLDs—once again pushing the envelope of product leadership.

With the intent of expanding FPGA penetration beyond traditional PLD applications within a system, our engineers took a fresh look at the nearly fifteen-year-old 4-input look-up table (LUT) structure and developed the Stratix II family. Based on an innovative new logic structure, Stratix II devices deliver much greater levels of integration and performance that now give you even more compelling reasons to exploit the flexibility and time-to-market capabilities of FPGAs. For example, Stratix II devices have significant memory and performance bandwidth that makes them ideal for data processing on high-performance line cards in a broad range of routers and edge switchers. Or, for wireless base station applications, we've made significant improvement to performance features that make Stratix II devices ideal for VoIP gateways. Many other applications that were once exclusively ASIC territory are now addressable by Stratix II devices. Our intent is to make Altera a larger part of your bill of materials. Significant savings are realized in overall system and supply chain costs, while risk is also substantially reduced.

Altera maintains the CPLD market leadership it has held for more than ten years, led by the MAX 7000 architecture, introduced in 1991. Purchased annually by over 10,000 customers around the globe, MAX devices populate a multitude of systems, performing functions anywhere from glue logic to bus bridging, power-up sequencing, device configuration, and I/O expansion. With the introduction of MAX II devices, we've redefined the CPLD architecture to deliver much greater densities at unheard of prices. Ultimately, MAX II devices will not only address traditional CPLD applications, but will also find their way into applications that small ASSPs and standard logic devices used to address.

This quarter, we treat you to a special issue of *News & Views* to give you an in depth look at the Stratix II and MAX II families. As we pave our path towards the next twenty years, our mission remains clear—to deliver high-value programmable solutions to our customers. To that end, our focus and commitment to continuous innovation only gets stronger. We're not done innovating at Altera—not by a long shot.

Erik Cleage, Senior Vice President of Marketing

# MAX II CPLDs

Stratix II FPGAs

Quartus II Version 4.0

# Features

| MAX II—The Lowest-Cost CPLD Ever                             | 4  |

|--------------------------------------------------------------|----|

| Stratix II—The Latest High-Performance, High-Density FPGAs   | 8  |

| Make the Move from the MAX+PLUS II to Quartus II Software    | 11 |

| Quartus II Version 4.0—Design Software Technology Leadership | 13 |

# **Devices & Tools**

| HardCopy Structured ASICs: ASIC Gain without the Pain16          |  |

|------------------------------------------------------------------|--|

| Stratix GX Devices Shipping in Production                        |  |

| Quartus II Software Version 4.0—Software Technology Leadership20 |  |

| Nios Processor Version 3.2 Now Shipping                          |  |

# **Contributed Articles**

| Tips for Improving Synplify Pro Performance for Stratix II Devices |

|--------------------------------------------------------------------|

| Using the Mentor Graphics Precision RTL Synthesis Tool for         |

| Advanced Stratix II Designs                                        |

| System Design with Multi-GHz Serial Links: Clearing the Hurdle     |

# **Technical Articles**

| MAX II CPLDs: Addressing the Increasing Requirements of<br>Control Path Applications               | .27  |

|----------------------------------------------------------------------------------------------------|------|

| Effective FPGA Performance Benchmarking—Comparisons Between<br>Leading FPGA Architectures          | . 30 |

| Secure Your Design with Stratix II FPGAs                                                           | . 31 |

| New & Innovative Stratix II Logic Structure Brings Unprecedented<br>Performance & Logic Efficiency | . 33 |

| SerialLite Protocol Overview                                                                       | . 37 |

Altera, ACAP, ACCESS, ACEX, ACEX 1K, AMPP, APEX, APEX 20K, APEX 20KC, APEX 20KC, APEX II, Atlantic, Avalon, BitBlaster, ByteBlaster II, ByteBlasterMV, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, Cyclone, DirectDrive, E+MAX, Excalibur, FastLUT, FastTrack, FineLine BGA, FLEX, FLEX 10K, FLEX10KE, FLEX 10KA, FLEX 8000, FLEX 6000, FLEX 6000A, Flexible-LVDS, HardCopy, HardCopy Stratix, IP MegaStore, Jam, LogicLock, MasterBlaster, MAX, MAX II, MAX 9000, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000B, MAX 7000A, MAX 7000A, MAX 7000A, MAX 9000A, MAX 900A, MAX 9000A, M MegaCore, MegaLAB, MegaWizard, Mercury, MultiCore, MultiVolt, MultiTrack, NativeLink, Nios, nSTEP, OpenCore, OptiFLEX, PowerFit, PowerGauge, Quartus, Quartus II, RapidLAB, SignalCore, SignalProbe, SignalTap, SignalTap Plus, SignalTap II, SoftMode, Stratix, Stratix II, Stratix GX, Terminator, The Programmable Solutions Company, TriMatrix, True-LVDS, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: Adobe and Acrobat are registered trademarks of Adobe Systems Incorporated. ARM and Multi-ICE are registered trademarks and ARM922T and ETM9 are trademarks of ARM limited. HP-UX is a trademark of Hewlett-Packard Company. HyperTransport is a trademark of HyperTransport Consortium. Intel and StrongARM are registered trademarks of Intel. Mentor Graphics is a registered trademark and Exemplar, LeonardoSpectrum, and ModelSim are trademarks of Mentor Graphics Corporation. Microsoft, Windows, Windows 98, and Windows NT are registered trademarks of Microsoft Corporation. PALACE is a trademark of Aplus Design Technologies, Inc. RapidIO is a trademark of RapidIO Trade Association. Rochester Electronics is a registered trademark of Rochester Electronics, Inc. Sun is a registered trademark and Solaris is a trademark of Sun Microsystems, Inc. Synplicity, Synplify, Synplify Pro are registered trademarks of Synplicity, Inc. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. The actual availability of Altera's products and features could differ from those projected in this publication and are provided solely as an estimate to the reader. Copyright@ 2004 Altera Corporation. All rights reserved.

# Publisher:

John Panattoni

**Technical Editor:** Justin Bennett

Cover Layout: Chandra Spence

101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 n\_v@altera.com

# MAX II—The Lowest-Cost CPLD Ever

Building on more than a decade of CPLD leadership and innovation, Altera introduces the MAX® II device family, the lowest-cost CPLDs ever. MAX II devices are based on a groundbreaking new CPLD architecture that delivers the lowest cost and the lowest power consumption of any CPLD family. At less than half the price of other CPLDs, this instant-on, non-volatile device family targets general-purpose, low-density logic applications. In addition, MAX II devices extend cost and power improvements to higher densities, enabling designers to use MAX II devices in place of higher-cost or higher-power ASSPs, ASICs, and standard logic devices.

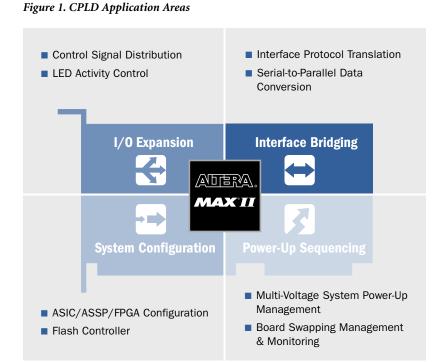

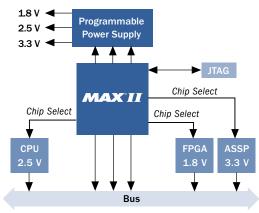

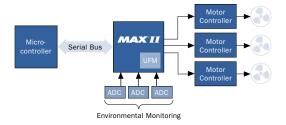

CPLDs are commonly used for control path applications (see Figure 1) in a wide range of electronic systems. These applications require more performance and density than macrocell-based CPLDs can cost-effectively deliver. As a result, engineers building complex systems often use ASICs and ASSPs. However, these alternatives complicate design because they lack the flexibility, ease-of-use, and low cost that are critical to these applications.

Because ASICs and ASSPs offer a poor solution for control path applications, there was a growing need in the industry for a new CPLD architecture to deliver cost-effective, instant-on, non-volatile devices at higher densities. Altera meets this need with its new MAX II family, which offers unprecedented levels of CPLD density (see Table 1). Based on a 0.18- $\mu$ m flash process, the MAX II family is optimized for the lowest possible cost per I/O pin. It delivers the higher densities required for system control in a non-volatile, instant-on device at half the cost and one-tenth the power consumption of prior MAX CPLD generations.

# Groundbreaking New CPLD Architecture

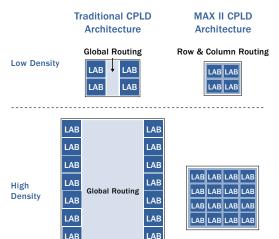

Based on a groundbreaking new CPLD architecture, MAX II devices redefine the value proposition for CPLDs. Historically, CPLDs differ from FPGAs because of their macrocell-based architecture. Unlike FPGAs, traditional CPLDs are designed around a base unit called the product-term, and have a global routing structure. However, the macrocellbased architecture is not efficiently scalable beyond approximately 1,000 macrocells because its routing area increases quadratically with density. At higher densities, the look-up table (LUT) architecture with row-and-column routing is more die-size efficient (see Figure 2), providing a significant cost advantage as well as delivering faster performance, smaller die size, and lower power consumption per gate.

MAX II devices are classified as CPLDs because they target the non-data path applications in which CPLDs are used. Classifying these devices based on intended application, rather than architecture emphasizes the benefits of technology, rather than the technology itself.

The MAX II architecture was developed to reduce the cost of general-purpose programmable logic designs by delivering the lowest cost per I/O pin in the smallest possible die size. Altera employed the following design techniques to develop this new architecture.

# MAX°II

| Device  | Logic<br>Elements | Equivalent<br>Macrocells | Maximum User<br>I/O Pins | User Flash<br>Memory<br>(Kbits) | Available<br>Packages (1)                                 |

|---------|-------------------|--------------------------|--------------------------|---------------------------------|-----------------------------------------------------------|

| EPM240  | 240               | 192                      | 80                       | 8,192                           | 100-pin TQFP (2)                                          |

| EPM570  | 570               | 440                      | 160                      | 8,192                           | 100-pin TQFP<br>144-pin TQFP<br>256-pin FineLine BGA® (3) |

| EPM1270 | 1,270             | 980                      | 212                      | 8,192                           | 144-pin TQFP<br>256-pin FineLine BGA                      |

| EPM2210 | 2,210             | 1,700                    | 272                      | 8,192                           | 256-pin FineLine BGA<br>324-pin FineLine BGA              |

#### Notes to Table 1:

(1) All packages support vertical migration across all densities.

(2) TQFP: thin quad flat pack.

(3) FineLine BGA package (1.0-mm pitch)

First, the MAX II I/O cells were optimized for size and placed in a staggered ring to minimize die size. Then, the devices were targeted to a set of popular, low-cost TQFP and FineLine BGA packages. Because of the focus on low cost per I/O pin, MAX II devices are pad-limited. In other words, device die size is defined by the number and size of I/O cells. It is critical to define the smallest I/O cell dimension possible because they, in turn, define the device's absolute die area and directly impact device cost.

Second, Altera selected a low-cost, low-power process technology on which to manufacture the MAX II family. TSMC's 0.18-µm flash process technology was selected to meet customers' instant-on and non-volatility requirements, while offering a dramatic reduction in device cost and power consumption.

#### Figure 2. Low-Cost MAX II Architecture Delivers Smaller Die Size

Routing increases quadratically with the number of LABs, resulting in a routingdominated die.

I AB

Routing increases linearly with the number of LABs, resulting in efficient die size. Finally, a new logic architecture was applied to deliver the highest density and performance within the available silicon area. The result is the MAX II device, the industry's lowest-cost CPLD ever.

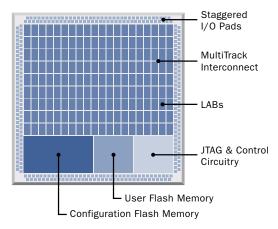

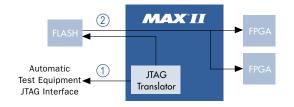

Figure 3 shows the groundbreaking MAX II CPLD architecture, consisting of an array of LUT-based logic array blocks (LABs), a bank of non-volatile flash memory, a staggered ring of area-optimized I/O cells, and Joint Test Action Group (JTAG) control circuitry. The MultiTrack<sup>™</sup> interconnect is designed to maximize performance and minimize power by using the most efficient direct connection from input to logic to output.

#### Figure 3. MAX II Device Floorplan

## **Board-Management Features**

In addition to reducing the cost of the CPLD itself, the MAX II architecture includes a number of boardmanagement features that help reduce costs and board space, while improving reliability at the board level.

#### User Flash Memory—An Industry First

The user flash memory is a non-volatile 8-Kbit memory block embedded within the MAX II device. It reduces cost and board space by delivering on-board electrically erasable programmable read-only memory (EEPROM) functionality that would otherwise require a separate device. MAX II devices are the first CPLDs to offer this feature. Typical applications for the user flash memory include storage of common board "housekeeping" information, such as manufacturing IDs, board revision or software revision information or power management diagnostic statistics.

#### MultiVolt Core

The MultiVolt<sup>™</sup> core—another industry first—allows users to power MAX II devices with any of three different supply voltages. It leverages the performance, cost, and power benefits of the 0.18-µm manufacturing process while supporting 3.3-V, 2.5-V, and 1.8-V power rails. An internal voltage regulator regulates the incoming voltage down to 1.8 V, enabling the user to choose whichever power rail is most convenient for a particular board-level design.

#### I/O Features

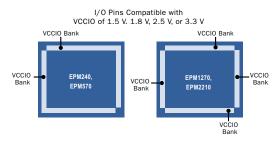

The new CPLD architecture also improves I/O usability. There are two I/O banks in EPM240 and EPM570 devices and four I/O banks in the EPM1270 and EPM2210 devices. Each I/O bank has its own VCCIO pin and can be configured independently to support 1.5-V, 1.8-V, 2.5-V, and 3.3-V interfaces. Each can also independently support a different I/O standard. Figure 4 highlights the I/O bank configurations, and Table 2 shows the I/O features available in MAX II devices.

#### Figure 4. MAX II I/O Bank Configurations

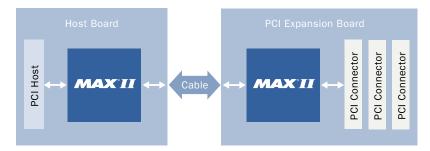

#### **Real-Time ISP**

Real-time in-system programmability (ISP) provides a flexible field upgrade solution designed to reduce the cost of remote field updates. MAX II devices include the capability to update the configuration flash memory block while the logic is running, with the new programming file taking effect without requiring the system to be turned off and initiate reconfiguration. This feature permits board management function updates without expensive system downtime or the cost of sending engineers to remote sites.

#### Ease-of-Use

In addition to having new board management features, the MAX II architecture is optimized for ease of use with features such as improved second-time fitting. The MultiTrack<sup>TM</sup> interconnect decouples the LABs from the I/O pins, allowing a pin-locked design to have a very high success rate for second-time fitting. This accommodates last-minute design changes.

| Table 2. MAX II I/O Features                               |                                                                                                                                                              |                                                                                                 |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Feature                                                    | Description                                                                                                                                                  | Benefit                                                                                         |

| MultiVolt I/O Banks                                        | Each bank of I/O contains a unique set of VCCIO pins for setting the voltage of that bank to either 3.3 V, 2.5 V, 1.8 V, or 1.5 V.                           | Supports multiple voltage standards on one device.                                              |

| 3.3-V/2.5-V/1.8-V/1.5-V LVTTL/<br>LVCMOS                   | Support for LVTTL/LVCMOS standards down to 1.5 V with multiple I/O banks.                                                                                    | Enables broad application support and compatibility with LVTTL standards.                       |

| PCI Support                                                | The EPM1270 and EPM2210 devices support PCI I/O capability.                                                                                                  | Enables support for 32-bit, 33-MHz PCI and use of MAX II devices as a PCI slave and arbiter.    |

| Schmitt Triggers                                           | Programmable hysteresis on any input pin.                                                                                                                    | Enables noise tolerance on inputs with up to 300 mV on 3.3-V inputs and 160 mV on 2.5-V inputs. |

| Programmable Drive Strength and Slew Rate                  | High and low drive strength settings not<br>available in prior MAX families. Slew rate<br>control has more dramatic effect than in<br>previous MAX families. | Enables user control to improve signal integ-<br>rity.                                          |

| Unique OE (tri-state control) per Pin                      | No limit to the number of OE signals in the design except I/O count.                                                                                         | Improvement over deficiency in prior MAX architectures.                                         |

| Programmable Bus-Hold, Pull-Up<br>Resistor, and Open-Drain | Programmable I/O features that are also available in MAX 7000B.                                                                                              | More user control of on-chip I/O behavior sav-<br>ing the user from using external components.  |

# **Free Design Software**

MAX II devices are supported by Altera's Quartus® II software, the easiest-to-use design software available for CPLD design. Now featuring a built-in MAX+PLUS® II look-and-feel option, MAX+PLUS II users can benefit from the Quartus II software without having to learn a new user interface. The Quartus II software also integrates seamlessly with all of the leading third-party synthesis and simulation tools.

A free version of the software, Quartus II Web Edition, can be downloaded from the Altera web site at **www.altera.com** and is also available on the Quartus II Software Starter Suite CD-ROM.

# Conclusion

Today's system designers continue to be challenged to deliver smaller and less costly electronics systems. While CPLDs have traditionally been the device of choice for control path functions, limits in density and performance have driven designers of advanced systems to consider more costly alternatives such as ASICs and ASSPs. Altera's new MAX II family of CPLDs leverages a LUT-based architecture that delivers significant new benefits for designers low-cost, low-power logic needs. To learn more about MAX II CPLDs, visit www.altera.com/max2.

# Stratix II—The Latest High-Performance, High-Density FPGAs

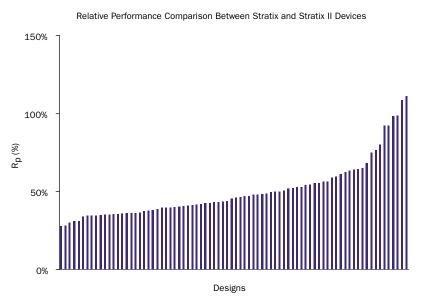

FPGA performance and density reaches new heights with the Stratix<sup>TM</sup> II device family, the latest FPGA product from Altera. Built on a new and innovative logic structure, Stratix II devices deliver on average 50% faster performance and offer more than twice the logic capacity of first-generation Stratix FPGAs. Stratix II devices extend the possibilities of FPGA design, allowing designers to meet the high-performance requirements of today's advanced systems and avoid developing with costly, time-consuming ASICs. Based on the award-winning Stratix device family architecture, Stratix II devices cost 40% less than first-generation Stratix devices and are outfitted with a powerful set of system-level features and incorporate many significant enhancements and new capabilities.

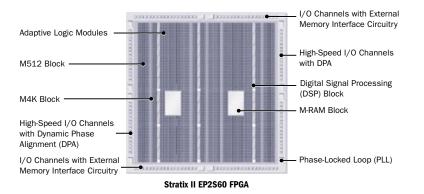

Stratix II FPGAs are manufactured on 300-mm wafers using TSMC's 90-nm, low-k dielectric process technology. Featuring numerous technological innovations and industry firsts, Stratix II FPGAs contain a new FPGA logic structure that increases device performance and densities to unprecedented levels. The innovative logic structure is built with adaptive logic modules (ALMs), which use logic resources more efficiently than traditional 4-input look-up table (LUT)-based logic elements (LEs). As a result, Stratix II FPGAs require fewer resources and reduce the levels of logic for a given function, yielding higher performance at a lower system cost. Performance advantages include support for 500-MHz clock rates and 250-MHz system clock frequencies. Stratix II device densities approach 180K equivalent LEs and 9 Mbits of RAM, a more than two-fold increase over its predecessor (see Table 1).

# The Challenge of Today's Digital Systems

Consumers are demanding real-time access to upto-date data, pushing end-user and infrastructure equipment to their performance limits. Enterprise servers, video switcher systems, and digital subscriber line multiplexers all require logic devices that support faster performance. To meet the needs of today's digital systems, Altera went back to the drawing board and developed a completely new logic structure for achieving or exceeding these challenging performance and cost requirements.

# **Why FPGA Performance Matters**

An important but often overlooked point is that using an FPGA with support for higher clock frequencies can be more cost-effective than using one with lower performance, even though faster speed grade FPGAs often have an associated cost premium. This is because the faster performance can be used to reduce the size of a design by dividing the bus structure in half and operating at twice the frequency, allowing the user to fit the design into a smaller device density.

To illustrate this, consider a SPI-4.2 interface, typically found in backplane applications, that can be implemented in both Stratix and Stratix II FPGAs. A 16-channel configuration of this design consumes approximately 16,000 LEs in a Stratix FPGA and requires the fastest speed grade to function correctly. Because Stratix II devices support much higher core logic and I/O speeds, this same design running at twice the speed with the bus divided into half consumes less than half the number of logic resources

| Table 1. Sti | ratix II Devic | e Family Overview |                    |                   |           |                      |                                               |          |              |

|--------------|----------------|-------------------|--------------------|-------------------|-----------|----------------------|-----------------------------------------------|----------|--------------|

| Device       | ALMs           | Equivalent LEs    | M512 RAM<br>Blocks | M4K RAM<br>Blocks | M-RAM     | Total Memory<br>Bits | <b>18- x 18-Bit</b><br>Multipliers <i>(1)</i> | PLLs (2) | Availability |

| EP2S15       | 6,240          | 15,600            | 104                | 78                | 419,328   | 0                    | 48                                            | 6        | Q4 2004      |

| EP2S30       | 13,552         | 33,880            | 202                | 144               | 1,369,728 | 1                    | 64                                            | 6        | Q4 2004      |

| EP2S60       | 24,176         | 60,440            | 329                | 255               | 2,544,192 | 2                    | 144                                           | 12       | July 2004    |

| EP2S90       | 36,384         | 90,960            | 488                | 408               | 4,520,448 | 4                    | 192                                           | 12       | Q4 2004      |

| EP2S130      | 53,016         | 132,540           | 699                | 609               | 6,747,840 | 6                    | 252                                           | 12       | October 2004 |

| EP2S180      | 71,760         | 179,400           | 930                | 768               | 9,383,040 | 9                    | 384                                           | 12       | Q4 2004      |

Notes to Table 1:

(1) Does not include soft multipliers implemented in memory blocks.

(2) Includes enhanced and fast PLLs.

than the Stratix implementation. This translates to a reduction in cost by approximately 75% with the Stratix II device. Further reductions in logic usage are also gained as a result of the more efficient packing capabilities of the Stratix II ALM, as discussed later in this issue of *News & Views*.

Developing and manufacturing semiconductors at deep submicron nodes with support for faster performance and larger densities is no longer academic. At the same time, porting an older FPGA architecture to a new process technology node does not necessarily result in faster performance as in the past. Rather, careful design considerations such as areaperformance-power trade-offs and new architectural innovations are critical and must be made to reach the FPGA performance-price requirements of nextgeneration systems.

# Breaking from Tradition to Address Submicron Challenges

Issues associated with designing semiconductors at the submicron level have drawn significant attention over the past few years. This is not without good reason—nanometer effects, whether from leakage current, inductive coupling, or supply drop—result in formidable challenges for FPGAs in the areas of performance and power management.

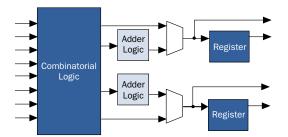

As a result, Altera has made significant changes in the logic array, developing an innovative, new logic structure, far ahead, in terms of performance and efficiency, of the 4-input LUT architectures that have been the basis of FPGAs for the last two decades. As shown in Figure 1, the logic structure of the Stratix II device family is built using ALMs that are composed of combinational, arithmetic, and register logic.

#### Figure 1. The New Stratix II Adaptive Logic Module

The Stratix II ALM is much more than two conjoined LEs with shared resources. What sets the ALM apart from all other FPGA architectures is its ability to adapt. The ALM can support either a single function that ranges in input width from 1 to 7, or it can support multiple, independent functions of different (or the same) widths. For example, a design may be synthesized into multiple functions of varying widths, say 5- and 3-input functions. Rather than having to build these functions across multiple levels (for the 5-input functions) or to waste resources (for the 3-input functions) when implemented in a fixed 4-input based architecture, both the 3- and 5-input functions can be placed within a single Stratix II ALM. Inputs and combinational LUT logic can be shared across the functions, saving even more resources. This is the case whether the design is synthesized as a combination of 7-, 5-, and 2-input functions, or any other combination of functions with up to 8 inputs. The end result is an average performance increase of 50% and a drastic increase in logic usage efficiency, reaching a 4-to-1 ratio in some cases.

## **Enhancing a Proven Feature Set**

In addition to a new logic structure, the Stratix II device family is optimized for the 90-nm process and offers many performance enhancements to the award-winning features of the original Stratix FPGA family (see Figure 2 on page 10). These enhancements include:

- TriMatrix<sup>TM</sup> Memory: More than 9 Mbits per device, up to 370-MHz performance with new capabilities for more efficient resource usage

- Digital Signal Processing Blocks: Up to 4× more bandwidth, support for rounding and saturation, and mixed-modes

- External Memory Interfaces: Support for the latest memory devices, including DDR2, SDRAM, QDR SRAM, and RLDRAM II (see Table 2 on page 10)

- Phase-Locked Loops: Enhanced jitter performance and on-the-fly reconfiguration capabilities

- High-Speed I/O Pins: Up to 1-Gbps performance on over 150 receive and 150 transmit channels with dynamic phase alignment (DPA)

| Table 2. Stratix II External Memory Interface Support |                          |  |  |  |  |

|-------------------------------------------------------|--------------------------|--|--|--|--|

| Memory Technology                                     | Maximum Clock Rate (MHz) |  |  |  |  |

| SDR SDRAM                                             | 166                      |  |  |  |  |

| DDR SDRAM                                             | 200                      |  |  |  |  |

| DDR2 SDRAM                                            | 266                      |  |  |  |  |

| RLDRAM II                                             | 300                      |  |  |  |  |

| QDRII SDRAM                                           | 250                      |  |  |  |  |

#### Figure 2. EP2S260 Device Floorplan

## **High-Speed Signal Integrity**

A true all-purpose FPGA, the Stratix II device family includes support for high-speed interfaces with dedicated DPA circuitry. DPA was first introduced to the FPGA market by Altera in the Stratix GX device family, Altera's transceiver-based family of FPGAs. As maximum system performance specifications rise and as backplane interfaces become chip-to-chip interfaces, there is an increasing need for a flexible, robust FPGA solution for high-speed signal alignment.

High-speed interfaces with source-synchronous clocking schemes are rapidly approaching one gigabit per second (Gbps) transfer rates. Due to these high speeds, digital designs require highly accurate data and clock synchronization and must meet very tight clock-to-channel and channel-to-channel skew specifications. To stay within the permitted skew, designers must use precise printed circuit board (PCB) design techniques because the slightest mismatch in trace lengths could result in erroneous data transfer. Other effects such as jitter, temperature, and voltage variations compound the problem, making simpler, static phase alignment techniques ineffective. Recognizing the challenges that engineers face when designing systems that transfer high-speed data, Altera developed the DPA feature to dramatically simplify PCB design, eliminating the signal alignment problems that result from skew-inducing effects.

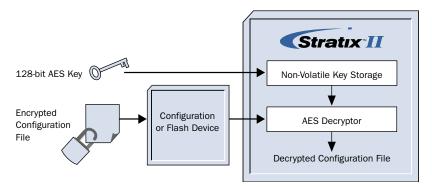

# **Ensuring Design Security**

In today's highly competitive commercial and military environments, design security is becoming an important consideration for digital designers. As FPGAs continue to play more critical functions in these systems, companies and governments will have increasing concerns about their intellectual property (IP) contained within FPGAs. Altera's Stratix II devices are the industry's first FPGAs to support configuration bitstream encryption using 128-bit Advanced Encryption Standard (AES). The new AES algorithm was developed by the U.S. National Security Association (NSA) as a successor to the older Data Encryption Standard (DES) and triple-DES algorithms. Starting with a user-defined 128-bit key, a user can generate an encrypted programming file in the Quartus® II software that is used to configure a Stratix II FPGA. That same key is securely stored in a non-volatile location in the FPGA and is used to decrypt the incoming programming file from the memory or configuration device.

# High-Volume Production Support: Altera's HardCopy Device Family

For high-volume designs, Stratix II devices are supported by Altera's HardCopy<sup>™</sup> structured ASIC family. HardCopy devices for Stratix II FPGAs deliver additional increases in performance and reduced power consumption, at a significant risk reduction and cost savings. The HardCopy design methodology provides volume-driven customers with a unique prototype-to-production solution not offered by any other semiconductor company.

# Conclusion

The new Stratix II device family—with an average 50% faster performance, 2× more density, an all-new logic structure, DPA circuitry, and design security features—is just the beginning of what you will see from Altera in 2004. Much more is on the way, including HardCopy for Stratix II devices and a host of new development kits and IP. Get your next high-performance design on its way—install the new Quartus II software version 4.0 to start designing with Stratix II devices.

For more detailed information on Stratix II devices, see "Secure Your Design with Stratix II FPGAs" on page 31 and "New & Innovative Stratix II Logic Structure Brings Unprecedented Performance & Logic Efficiency" on page 33.

# Make the Move from the MAX+PLUS II to Quartus II Software

The Quartus<sup>®</sup> II software is now the best and easiest-to-use software for designing with CPLDs, FPGAs, and structured ASICs. MAX+PLUS<sup>®</sup> II software users will be amazed at how familiar the Quartus II software version 4.0 looks and feels while delivering better performance, more features, and access to exciting new CPLD and FPGA device families.

# **Quartus II Software Benefits**

Version 4.0 of the Quartus II software offers MAX+PLUS II users faster push-button performance, superior integrated synthesis support, a familiar MAX+PLUS II look-and-feel, and enhancements to better support converting MAX+PLUS II projects to Quartus II projects. Along with support for your favorite MAX<sup>®</sup> and FLEX<sup>®</sup> 10K devices, the Quartus II software version 4.0 adds support for the MAX II CPLD family and supports all of Altera's latest FPGA and structured ASIC devices.

Table 1 summarizes the Quartus II software's advantages for MAX+PLUS II software customers.

# Quartus II Software's New MAX+PLUS II Look-&-Feel Optional Setting

With the built-in MAX+PLUS II look-andfeel option, users can get the full benefit of the Quartus II software without learning a new user interface. This option provides Quartus II users the same basic menu structure and toolbar as seen in the MAX+PLUS II software (see Figure 1). Figure 1. MAX+PLUS II Look & Feel Toolbar in the Quartus II Software

| 🖏 Quartus II - C:/qdesigns/chiptrip/chiptrip - chiptrip |      |            |      |         |             |            |       |        |      |

|---------------------------------------------------------|------|------------|------|---------|-------------|------------|-------|--------|------|

| MAX+PLUS II                                             | File | Edit       | View | Project | Assignments | Processing | Tools | Window | Help |

|                                                         | 影目   | a <b>R</b> | IO N | ? 🛆 🖻   | 5888        |            |       |        |      |

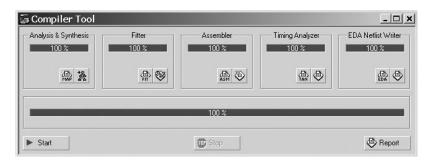

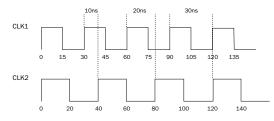

The new Quartus II compiler tool is similar to the MAX+PLUS II compiler tool and offers the same one-click compilation capability (see Figure 2).

#### Figure 2. Quartus II Compiler Window

New in version 4.0 of the Quartus II software are timing analyzer and simulator tools with similar interfaces to those in the MAX+PLUS II software. The Quartus II simulator tool (see Figure 3 on page 12) has been enhanced to emulate MAX+PLUS II simulator functionality by allowing users to overwrite simulation input files with simulation results. Users can generate functional simulation netlists separately from the compilation process to accelerate compilation and simulation run times.

MAX+PLUS II Users

| Table 1. Quartus II Advantages over the MAX+PLUS II Software |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Design Method                                                | Supported Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Device Support                                               | <ul> <li>Supports the new MAX II family in addition to MAX 3000A, 7000S, MAX 7000AE, and MAX 7000B families</li> <li>Supports the latest FPGA devices such as Stratix II, Cyclone<sup>™</sup>, and Stratix<sup>™</sup> families, in addition to FLEX 10KE, FLEX 10K, FLEX 10KA, ACEX<sup>®</sup> 1K, and FLEX 6000 families</li> </ul>                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Performance                                                  | <ul> <li>Twice the design performance of the CPLD push-button design using MAX II devices         <ul> <li>The Quartus II design space explorer script can raise performance an average of an additional 35%</li> </ul> </li> <li>Offers better average performance than MAX+PLUS II software version 10.2 for MAX 3000A, MAX 7000AE, MAX 7000S, MAX 7000B, FLEX 10K, and ACEX 1K designs         <ul> <li>15% faster average design performance than MAX designs originally compiled with the MAX+PLUS II software version 10.2</li> <li>Requires an average of 5% fewer device resources for any given MAX design</li> </ul> </li> </ul> |  |  |  |  |  |

| Synthesis                                                    | <ul> <li>Integrates RTL synthesis support for the latest VHDL and Verilog HDL standards in addition to AHDL support</li> <li>RTL viewer provides a graphical representation of VHDL or Verilog HDL designs before synthesis and design implementation (Quartus II software only)</li> <li>Supports all leading third-party synthesis flows</li> </ul>                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

Figure 3. New Quartus II Timing Analyzer & Simulator Tools

| &Quartus II - C:/qdesigns/chiptrip/chiptrip - chiptrip<br>MAX+PLUS II Fle Edit View Project Assignments Processing Tools                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCHE XDE O M ARBADS BIX 99                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                    |

| 🛎 Timing Analyzer Tool                                                                                                                                                                                                                                                                                              | Simulator Tool                                                                                                                                                                                                                                                                                                     |

| Registered Performance tod tou to th Custom Delays                                                                                                                                                                                                                                                                  | Simulation mode: Timing  Generate Functional Simulation Nether                                                                                                                                                                                                                                                     |

| Clock clock                                                                                                                                                                                                                                                                                                         | Simulation input C:/qdesigns/chiptrip.scf                                                                                                                                                                                                                                                                          |

| Value         From         speed, ch.2typ           To         upeed, ch.2typ         speed, ch.2typ           Clock preied         5500 ns         Freesempy           Freesempy         181.82 Mdz         75           50         25         200           25         4         225           0         MHz 2500 | Simulation period  C Run nimulation until all vector stimuli are used  C End simulation etc.  Simulation options  C Automatically add pris to simulation output wereforms  C Dock outputs  S Sings and held time violation detection  Blitch detection.  D Unerwalte simulation input life with simulation results |

| 02                                                                                                                                                                                                                                                                                                                  | 0z                                                                                                                                                                                                                                                                                                                 |

| Po Start Stop Breport Number of paths to list 10 List Paths                                                                                                                                                                                                                                                         | 🖹 Start 💭 Stop 😥 Open 🔗 Report                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                     | (http://www.altera.com)                                                                                                                                                                                                                                                                                            |

| 2 9 × mm × m                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                    |

| For Help, press F1                                                                                                                                                                                                                                                                                                  | ि≑≣≠≣ ide                                                                                                                                                                                                                                                                                                          |

# Experience the Power of the Quartus II Software Now

Many designers are already enjoying the benefits of the Quartus II software:

- "The Quartus II software is more reliable and user-friendly than MAX+PLUS II..." Hussein Moradi, President, Quintessence Technologies Corporation

- "...I found it very easy to switch from the MAX+PLUS II software to the Quartus II software, which I now use for all of my new Altera designs..." Bill Swanson, Principal Engineer, Vytek Corporation

- "I am very impressed with the ease-of-use, speed, and exceptional quality of results yielded by the Quartus II software..." Alfredo Mendez, Principal Consultant, Intrinsix Corporation

You can download the free Quartus II Web Edition software from the Altera® web site download center or request the Quartus II Software Starter Suite CD-ROM from the literature section of the Altera web site.

Also available is a new online demonstrations that shows how easy it is to convert a MAX+PLUS II project into a Quartus II project. For more detailed information you can also refer to the *Quartus II Design Flow for MAX+PLUS II Users* chapter of the new *Quartus II Development Software Handbook*.

The Quartus II software is now recommended for all new CPLD, FPGA, and structured ASIC designs. MAX+PLUS II users who try the Quartus II software will realize performance and productivity gains and get access to advanced features and exciting new device families. Making the move to the Quartus II software is risk-free—the free Quartus II Web Edition version 4.0, including the MAX+PLUS II look-andfeel-option and MAX II device support is now available on the Altera web site.

# Quartus II Version 4.0—Design Software Technology Leadership

Version 4.0 of the Quartus<sup>®</sup> II software extends Altera's software technology leadership for high-density FPGA design and continues Altera's tradition of CPLD design tool leadership.

# Design for Stratix II FPGAs Today

Stratix<sup>TM</sup> II devices are 50% faster than previous FPGA families and can reach even higher performance levels by taking advantage of the Quartus II software's advanced physical synthesis and timing closure methodologies. The Quartus II software technology leadership and the Stratix II device family delivers the highest performance and efficiency for high-density FPGA designs.

# **Design for MAX II CPLDs Today**

The Quartus II software continues Altera's tradition of CPLD design tool leadership with an easy-to-use and complete design environment for CPLD design entry, synthesis, place-and-route, and verification. In addition to supporting the new MAX® II CPLD family, the Quartus II software now includes a MAX+PLUS® II look-and-feel option, so thousands of MAX+PLUS II designers can make the move to the Quartus II software without having to learn a new software interface. See the "Make the Move from MAX+PLUS II to Quartus II Software" on page 11 for more information.

# Quartus II On-line Demos & Software Handbook Now Available

There are now over 20 short video demonstrations of Quartus II software features and design methodologies available from the Altera web site at **www.altera.com/quartusdemos**. This is the easiest way to see the latest Quartus II software features in action and learn where to get more information. See Figure 1.

The new *Quartus II Developmant Software Handbook* includes detailed applications information on design and synthesis, design implementation and optimization, and verification. The Quartus II software handbook is now available from the Altera® web site. Figure 1. Quartus II On-Line Demonstrations

# New Features Extending Software Technology Leadership

The Quartus II software version 4.0 includes new technology to simplify and accelerate high-density FPGA designs.

#### Memory Compiler Waveform Generation

The Quartus II software memory compiler can now produce waveform displays of RAM and first-in firstout (FIFO) memory operation based on memory parameterization and configuration selections. This feature makes it easier to understand the effects of different memory configuration settings. See Figure 2.

#### Figure 2. Memory Compiler Waveform Generation

| wren      |     |     |

|-----------|-----|-----|

| data      | 0   |     |

| wraddress | 0_X | 1   |

| rdaddress | 0   | Х 3 |

| clock     |     |     |

| P         | X   | FO  |

| memory4   |     |     |

| memory3   |     |     |

#### **RTL** Viewer

The new register transfer level (RTL) viewer feature provides a schematic representation of designs that can be used to analyze a design's structure before further behavioral simulation, synthesis, and placeand-route steps are performed (see Figure 3). The RTL viewer allows designers to navigate a design's hierarchy and easily locate particular items of interest easily to aid in debugging and optimization. Selected items in the RTL viewer can be directly traced back to source design files.

#### Figure 3. RTL Viewer

#### Revisions

The Quartus II software now allows designers to easily experiment using different compilation settings and assignments for a given design. A group of settings, assignments, and compilation results can be stored and processed separately as an individual design revision.

#### Physical Synthesis Enhancements

Version 4.0 of the Quartus II software adds physical synthesis optimization support for the Stratix II FPGA family in addition to the support included previously for Stratix, Stratix GX, and Cyclone<sup>TM</sup> device families.

## Design Space Explorer Distributed Computing Support

The Quartus II software design space explorer script provides an automated option to increase average design performance by 20% by applying combinations of compilation settings and physical synthesis settings. The Quartus II software version 4.0 enhances the design space explorer feature to support distributed environments where multiple computers can run simultaneous compilations using different optimization settings to dramatically reduce design space explorer run times.

#### SignalTap II Advanced Triggering Feature

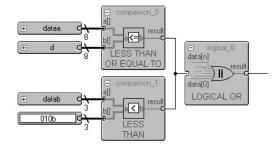

SignalTap<sup>®</sup> II logic analysis facilitates the verification process by integrating the functionality of a logic analyzer within the software. Version 4.0 of the Quartus II software adds a new graphical environment to implement complex user-defined trigger logic to compare bus states with individual signals to initiate SignalTap II embedded logic analyzer data capture. This feature gives FPGA designers unprecedented flexibility to isolate system design problems in-system and at system speeds. See Figure 4.

#### Figure 4. SignalTap II Advanced Triggering Example

Result: dataa<=d||datab<010b

#### Faster Compile Times on Linux Platforms

New software optimizations improves compile times by an average of 40% when using the Quartus II software for Red Hat Linux 7.3 or 8.0.

# Experience Quartus II Software Version 4.0 Today

The Quartus II software version 4.0 delivers unmatched performance, efficiency, and ease-of-use for CPLD, FPGA, and structured ASIC designs. The Quartus II software version 4.0 is now shipping to all customers with active software subscriptions. The Quartus II Web Edition software is available for downloading from the Altera web site or as part of the Quartus II Software Starter Suite CD-ROM.

# **Altera Devices**

Tables 1 through 14 list the logic element (LE), macrocell and gate counts, pin/package options, I/O pin counts, supply voltage, RAM bits, and other device-specific features of Altera® CPLDs, FPGAs, HardCopy<sup>TM</sup> devices, and configuration devices.

| Table 1. MAX | Table 1. MAX II Devices |                                  |                                         |                          |                     |                           |  |  |  |  |

|--------------|-------------------------|----------------------------------|-----------------------------------------|--------------------------|---------------------|---------------------------|--|--|--|--|

| Device       | LEs                     | Typical Equivalent<br>Macrocells | Pin/Package Options (1)                 | Maximum User I/O<br>Pins | Supply Voltage      | User Flash<br>Memory Bits |  |  |  |  |

| EPM240       | 240                     | 192                              | 100-Pin TQFP                            | 80                       | 3.3 V, 2.5 V, 1.8 V | 8,192                     |  |  |  |  |

| EPM570       | 570                     | 440                              | 100-Pin TQFP, 144-Pin TQFP, 256-Pin BGA | 76, 116, 160             | 3.3 V, 2.5 V, 1.8 V | 8,192                     |  |  |  |  |

| EPM1270      | 1,270                   | 980                              | 144-Pin TQFP, 256-Pin BGA               | 116, 212                 | 3.3 V, 2.5 V, 1.8 V | 8,192                     |  |  |  |  |

| EPM2210      | 2,210                   | 1,700                            | 256-Pin BGA, 324-Pin BGA                | 204, 272                 | 3.3 V, 2.5 V, 1.8 V | 8,192                     |  |  |  |  |

#### Note to Table 1:

(1) All BGA packages are 1.0-mm FineLine BGA® packages.

| Table 2. Str | atix II Devices                                   |                       |                       |                      |                 |                   |                                               |                             |               |                                |                   |             |

|--------------|---------------------------------------------------|-----------------------|-----------------------|----------------------|-----------------|-------------------|-----------------------------------------------|-----------------------------|---------------|--------------------------------|-------------------|-------------|

| Device       | Adaptive<br>Logic<br>Modules<br>(ALMs) <i>(1)</i> | Equivalent<br>LEs (1) | M512<br>RAM<br>Blocks | M4K<br>RAM<br>Blocks | M-RAM<br>Blocks | Total RAM<br>Bits | Pin/Package<br>Options                        | Maximum<br>User I/O<br>Pins | DSP<br>Blocks | Embedded<br>Multipliers<br>(2) | Supply<br>Voltage | PLLs<br>(3) |

| EP2S15       | 6,240                                             | 15,600                | 104                   | 78                   | 0               | 419,328           | 484-Pin BGA,<br>672-Pin BGA                   | 341<br>365                  | 12            | 48                             | 1.2 V             | 6           |

| EP2S30       | 13,552                                            | 33,880                | 202                   | 144                  | 1               | 1,369,728         | 484-Pin BGA,<br>672-Pin BGA                   | 341<br>499                  | 16            | 64                             | 1.2 V             | 6           |

| EP2S60       | 24,176                                            | 60,440                | 329                   | 255                  | 2               | 2,544,192         | 484-Pin BGA,<br>672-Pin BGA,<br>1,020-Pin BGA | 341<br>499<br>717           | 36            | 144                            | 1.2 V             | 12          |

| EP2S90       | 36,384                                            | 90,960                | 488                   | 408                  | 4               | 4,520,448         | 1,020-Pin BGA,<br>1,508-Pin BGA               | 757<br>901                  | 48            | 192                            | 1.2 V             | 12          |

| EP2S130      | 53,016                                            | 132,540               | 699                   | 609                  | 6               | 6,747,840         | 1,020-Pin BGA<br>1,508-Pin BGA                | 741<br>1,109                | 63            | 252                            | 1.2 V             | 12          |

| EP2S180      | 71,760                                            | 179,400               | 930                   | 768                  | 9               | 9,383,040         | 1,020-Pin BGA<br>1,508-Pin BGA                | 741<br>1,173                | 96            | 484                            | 1.2 V             | 12          |

#### Notes to Table 2:

(1) Each Stratix<sup>TM</sup> II ALM is equivalent to 2.5, 4-input look-up table (LUT)-based LEs.

Each DSP block supports four 18-bit  $\times$  18-bit multipliers. Includes enhanced and fast PLLs. (2)

(3)

| Table 3. Stra | atix Devices | Note (1)                                                           |                    |                   |                   |            |

|---------------|--------------|--------------------------------------------------------------------|--------------------|-------------------|-------------------|------------|

| Device        | LEs          | Pin/Package Options                                                | l/0 Pins           | Supply<br>Voltage | Total RAM<br>Bits | DSP Blocks |

| EP1S10        | 10,570       | 484-Pin BGA (2), 672-Pin BGA, 672-Pin BGA (2), 780-Pin BGA (2)     | 335, 345, 345, 426 | 1.5 V             | 920,448           | 6          |

| EP1S20        | 18,460       | 484-Pin BGA (2), 672-Pin BGA, 672-Pin BGA (2), 780-Pin BGA (2)     | 361, 426, 426, 586 | 1.5 V             | 1,669,248         | 10         |

| EP1S25        | 25,660       | 672-Pin BGA, 672-Pin BGA (2), 780-Pin BGA (2), 1,020-Pin BGA (2)   | 473, 473, 597, 706 | 1.5 V             | 1,944,576         | 10         |

| EP1S30        | 32,470       | 780-Pin BGA (2), 956-Pin BGA, 1,020-Pin BGA (2)                    | 589, 683, 726      | 1.5 V             | 3,317,184         | 12         |

| EP1S40        | 41,250       | 780-Pin BGA (2), 956-Pin BGA, 1,020-Pin BGA (2), 1,508-Pin BGA (2) | 615, 683, 773, 822 | 1.5 V             | 3,423,744         | 14         |

| EP1S60        | 57,120       | 956-Pin BGA, 1,020-Pin BGA (2), 1,508-Pin BGA (2)                  | 683, 773, 1,022    | 1.5 V             | 5,215,104         | 18         |

| EP1S80        | 79,040       | 956-Pin BGA, 1,020-Pin BGA (2), 1,508-Pin BGA (2)                  | 683, 773, 1,203    | 1.5 V             | 7,427,520         | 22         |

#### Notes to Table 3:

The ordering code for Stratix devices is based on the number of LEs; therefore, gate count numbers are not included. Space-saving FineLine BGA package. (1)

(2)

| Table 4. APEX                      | Table 4. APEX 20K Devices     |                                                                                                                                                                                                                   |                                                                             |                         |                            |                               |  |  |  |  |

|------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------|----------------------------|-------------------------------|--|--|--|--|

| Device                             | Gates                         | Pin/Package Options                                                                                                                                                                                               | I/O Pins                                                                    | Supply<br>Voltage       | LEs                        | RAM<br>Bits                   |  |  |  |  |

| EP20K30E                           | 30,000                        | 144-Pin TQFP, 144-Pin BGA (1), 208-Pin PQFP                                                                                                                                                                       | 92, 93, 125                                                                 | 1.8 V                   | 1,200                      | 24,576                        |  |  |  |  |

| EP20K60E                           | 60,000                        | 144-Pin TQFP, 144-Pin BGA <i>(1)</i> , 208-Pin PQFP, 324-Pin BGA <i>(1)</i> , 356-Pin BGA                                                                                                                         | 1.8 V                                                                       | 2,560                   | 32,768                     |                               |  |  |  |  |

| EP20K100<br>EP20K100E              | 100,000<br>100,000            | 144-Pin TQFP, 208-Pin PQFP, 240-Pin PQFP, 324-Pin BGA <i>(1),</i><br>356-Pin BGA<br>144-Pin TQFP, 144-Pin BGA <i>(1),</i> 208-Pin PQFP, 240-Pin PQFP,<br>324-Pin BGA <i>(1),</i> 356-Pin BGA                      | 2.5 V<br>1.8 V                                                              | 4,160<br>4,160          | 53,248<br>53,248           |                               |  |  |  |  |

| EP20K160E                          | 160,000                       | 144-Pin TQFP, 208-Pin PQFP, 240-Pin PQFP, 356-Pin BGA, 88, 143, 175, 27<br>484-Pin BGA <i>(1)</i>                                                                                                                 |                                                                             | 1.8 V                   | 6,400                      | 81,920                        |  |  |  |  |

| EP20K200<br>EP20K200E<br>EP20K200C | 200,000<br>200,000<br>200,000 | 208-Pin PQFP, 240-Pin RQFP, 356-Pin BGA, 484-Pin BGA (1)<br>208-Pin PQFP, 240-Pin RQFP, 356-Pin BGA, 484-Pin BGA (1),<br>652-Pin BGA, 672-Pin BGA (1)<br>208-Pin PQFP, 240-Pin PQFP, 356-Pin BGA, 484-Pin BGA (1) | 144, 174, 277, 382<br>136, 168, 271, 376,<br>376, 376<br>136, 168, 271, 376 | 2.5 V<br>1.8 V<br>1.8 V | 8,320<br>8,320<br>8,320    | 106,496<br>106,496<br>106,496 |  |  |  |  |

| EP20K300E                          | 300,000                       | 240-Pin PQFP, 652-Pin BGA, 672-Pin BGA (1)                                                                                                                                                                        | 152, 408, 408                                                               | 1.8 V                   | 11,520                     | 147,456                       |  |  |  |  |

| EP20K400<br>EP20K400E<br>EP20K400C | 400,000<br>400,000<br>400,000 | 652-Pin BGA, 672-Pin BGA (1)<br>652-Pin BGA, 672-Pin BGA (1)<br>652-Pin BGA, 672-Pin BGA (1)                                                                                                                      | 502, 502<br>488, 488<br>488, 488                                            | 2.5 V<br>1.8 V<br>1.8 V | 16,640<br>16,640<br>16,640 | 212,992<br>212,992<br>212,992 |  |  |  |  |

| EP20K600E<br>EP20K600C             | 600,000<br>600,000            | 652-Pin BGA, 672-Pin BGA (1), 1,020-Pin BGA (1)<br>652-Pin BGA, 672-Pin BGA (1), 1,020-Pin BGA (1)                                                                                                                | 488, 508, 588<br>488, 508, 588                                              | 1.8 V<br>1.8 V          | 24,320<br>24,320           | 311,296<br>311,296            |  |  |  |  |

| EP20K1000E<br>EP20K1000C           | 1,000,000<br>1,000,000        | 652-Pin BGA, 672-Pin BGA (1), 1,020-Pin BGA (1)<br>652-Pin BGA, 672-Pin BGA (1), 1,020-Pin BGA (1)                                                                                                                | 488, 508, 708<br>488, 508, 708                                              | 1.8 V<br>1.8 V          | 38,400<br>38,400           | 327,680<br>327,680            |  |  |  |  |

| EP20K1500E                         | 1,500,000                     | 652-Pin BGA, 1,020-Pin BGA (1)                                                                                                                                                                                    | 488, 808                                                                    | 1.8 V                   | 51,840                     | 442,368                       |  |  |  |  |

Note to Table 4:

(1) Space-saving FineLine BGA package.

# HardCopy Structured ASICs: ASIC Gain without the Pain

HardCopy structured ASICs provide a comprehensive alternative to standard cell ASICs. Engineers can directly design HardCopy structured ASICs using the advanced features of the Quartus® II design software with the added capability to prototype and verify functionality in-system. The in-system verification feature not only facilitates changes to the design while testing the design in-silicon, but also helps develop the total system including software thus offering true time-to-market benefits. Further, the seamless migration of this proven design to the HardCopy structured ASIC guarantees first-silicon functionality.

HardCopy devices are now available in LE densities ranging from 16K to 79M, or an equivalent of 200K to 1 million standard cell gates. Fully tested first samples of HardCopy devices are available in as little as 8 weeks after the design is accepted by Altera.

HardCopy Stratix<sup>TM</sup> HC1S25, HC1S60, and HC1S80 devices are shipping in volume. HC1S30 and HC1S40 devices will begin shipping in volume by Q3 2004.

With numerous design wins in the first generation HardCopy devices, Altera has been shipping HardCopy APEX 20KC<sup>TM</sup> and HardCopy APEX 20KE<sup>TM</sup> devices in volume since 2001.

For more information on HardCopy devices, refer to www.altera.com/hardcopy.

# What Customers are Saying about HardCopy Structured ASICs

"Altera HardCopy Stratix devices provide a low-risk, cost-optimized, high-volume solution for our nextgeneration 3G base station, eliminating the need for us to use an ASIC or standard product. By offering industry-leading density and a seamless migration path from Stratix FPGAs to HardCopy devices, Altera improves our time-to-market and lowers our costs, enabling us to penetrate new markets."

#### Bong-Bin Park

Senior Vice President of CDMA System Research Lab LG Electronics

| Table 5. Hard | Table 5. HardCopy Devices                    |               |                   |                                  |        |           |  |  |  |

|---------------|----------------------------------------------|---------------|-------------------|----------------------------------|--------|-----------|--|--|--|

| Device        | Pin/Package Options                          | I/O Pins      | Supply<br>Voltage | Estimated Logic Gates<br>(K) (1) | LEs    | RAM Bits  |  |  |  |

| HC1S25        | 672-Pin BGA <i>(2)</i>                       | 473           | 1.5 V             | 325                              | 25,660 | 1,944,576 |  |  |  |

| HC1S30        | 780-Pin BGA <i>(2)</i>                       | 597           | 1.5 V             | 400                              | 32,470 | 2,137,536 |  |  |  |

| HC1S40        | 780-Pin BGA <i>(2)</i>                       | 615           | 1.5 V             | 500                              | 41,250 | 2,244,096 |  |  |  |

| HC1S60        | 1,020-Pin BGA (2)                            | 773           | 1.5 V             | 700                              | 57,120 | 5,215,104 |  |  |  |

| HC1S80        | 1,020-Pin BGA <i>(2)</i>                     | 773           | 1.5 V             | 1,000                            | 79,040 | 5,658,048 |  |  |  |

| HC20K400      | 652-Pin BGA, 672-Pin BGA (2)                 | 488, 488      | 1.8 V             | 200                              | 16,640 | 212,992   |  |  |  |

| HC20K600      | 652-Pin BGA, 672-Pin BGA (2)                 | 488, 508      | 1.8 V             | 300                              | 24,320 | 311,296   |  |  |  |

| HC20K1000     | 652-Pin BGA, 672-Pin BGA1, 1,020-Pin BGA (2) | 488, 508, 708 | 1.8 V             | 460                              | 38,400 | 327,680   |  |  |  |

| HC20K1500     | 652-Pin BGA, 1,020-Pin BGA (2)               | 488, 808      | 1.8 V             | 625                              | 51,840 | 442,368   |  |  |  |

#### Notes to Table 5:

Does not include digital signal processing (DSP) blocks or memories.

Space-saving FineLine BGA package.

| Table 6. Cyclo | Table 6. Cyclone Devices |                                                |                                                        |                   |          |  |  |  |  |

|----------------|--------------------------|------------------------------------------------|--------------------------------------------------------|-------------------|----------|--|--|--|--|

| Device         | LEs                      | Pin/Package Options                            | l/0 Pins                                               | Supply<br>Voltage | RAM Bits |  |  |  |  |

| EP1C3          | 2,910                    | 100-Pin TQFP, 144-Pin TQFP (1)                 | 65, 104                                                | 1.5 V             | 59,904   |  |  |  |  |

| EP1C4          | 4,000                    | 324-Pin BGA (1), 400-Pin BGA (1)               | 249, 301                                               | 1.5 V             | 78,336   |  |  |  |  |

| EP1C6          | 5,980                    | 144-Pin TQFP, 240-Pin PQFP, 256-Pin BGA (1)    | 98, 185, 185                                           | 1.5 V             | 92,160   |  |  |  |  |

| EP1C12         | 12,060                   | 240-Pin PQFP, 256-Pin BGA (1), 324-Pin BGA (1) | 173, 185, 249                                          | 1.5 V             | 239,616  |  |  |  |  |

| EP1C20         | 20,060                   | 324-Pin BGA (1), 400-Pin BGA (1)               | 24-Pin BGA (1), 400-Pin BGA (1) 233, 301 1.5 V 294,912 |                   |          |  |  |  |  |

Note to Table 6: (1) Space-saving FineLine BGA package.

| Table 7. ACEX | Table 7. ACEX Devices |                                                              |                    |                   |       |          |  |  |  |

|---------------|-----------------------|--------------------------------------------------------------|--------------------|-------------------|-------|----------|--|--|--|

| Device        | Gates                 | Pin/Package Options                                          | l/0 Pins           | Supply<br>Voltage | LEs   | RAM Bits |  |  |  |

| EP1K10        | 10,000                | 100-Pin TQFP, 144-Pin TQFP, 208-Pin PQFP, 256-Pin BGA (1)    | 66, 92, 120, 136   | 2.5 V             | 576   | 12,288   |  |  |  |

| EP1K30        | 30,000                | 144-Pin TQFP, 208-Pin PQFP, 256-Pin BGA (1)                  | 102, 147, 171      | 2.5 V             | 1,728 | 24,576   |  |  |  |

| EP1K50        | 50,000                | 144-Pin TQFP, 208-Pin PQFP, 256-Pin BGA (1), 484-Pin BGA (1) | 102, 147, 186, 249 | 2.5 V             | 2,880 | 40,960   |  |  |  |

| EP1K100       | 100,000               | 208-Pin PQFP, 256-Pin BGA (1), 484-Pin BGA (1)               | 147, 186, 333      | 2.5 V             | 4,992 | 49,152   |  |  |  |

#### Note to Table 7:

(1) Space-saving FineLine BGA package.

# Stratix GX Devices Shipping in Production

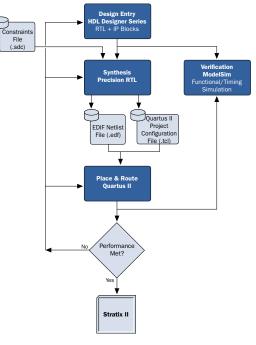

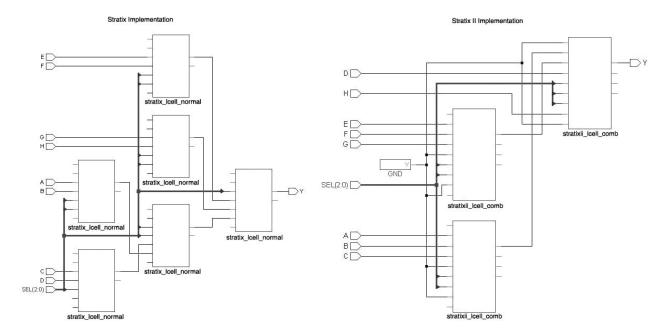

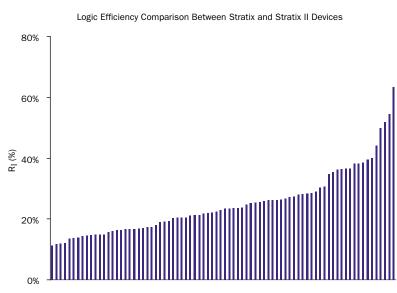

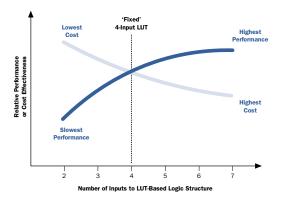

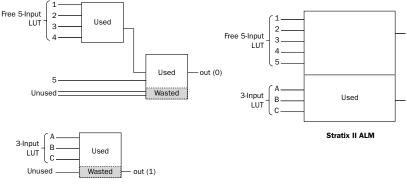

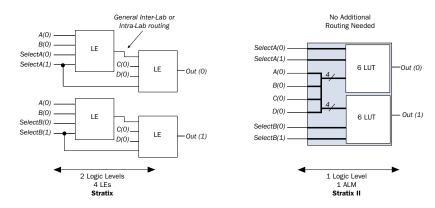

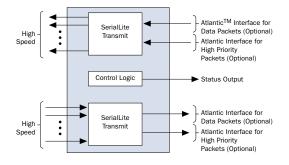

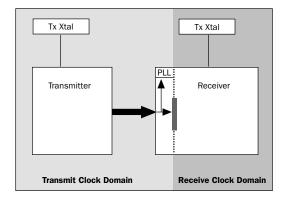

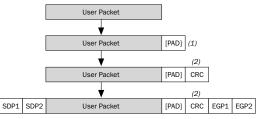

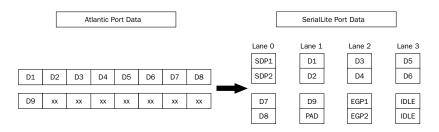

All Stratix GX devices have been qualified for production and are now shipping in volume quantities (see Table 8). In addition, the High-Speed Development Kit, Stratix GX Edition is now shipping. The kit includes a development board, layout files, schematics, design examples, and high-speed board layout guidelines.