**Newsletter for Altera Customers**

Cycio

The Lowest-Cost FPGAs Ever

# **Altera's Summer Blockbusters** Featuring Quartus II Version 4.1

Aller

The World's Most Versatile Processor

### Sequels that Improve on the Originals—The Power of II

In his keynote address to the 2003 SIA Annual Forecast and Awards dinner, Altera CEO John Daane predicted that 2004 would be a "vintage year," one that would be highlighted by strong growth and considerable change in the semiconductor industry. Here we are half way into the year, and sure enough, the chip industry is experiencing a strong rebound. There is one significant change, however. While past up cycles were largely driven by communications or PC industry growth, today's expansion is driven by digital consumer applications. This is the era of the consumer, and, subsequently, it's also a period of fierce competition.

Because of our concerted effort to get closer to our customers and involve them in our productdefinition process, we have gained deep and valuable insight into their end markets. What we saw early on, particularly in the consumer market, was the collision between radically shortened end-product lifecycles and the expensive and lengthy ASIC design cycle. Shortened product lifecycles and the resulting need to quickly innovate is a natural fit for FPGAs. It was with this in mind that Altera developed the

first-generation low-cost Cyclone<sup>TM</sup> devices in 2002—specifically to address the needs of high-volume manufacturers who wanted to stay ahead in the race to the store shelves. As of this writing, over 3,000 customers are designing with Cyclone devices and we've shipped over three million Cyclone units around the world—setting a new Altera record for the fastest ramping product in company history.

Likewise, we developed the Nios® soft core processor to address processor obsolescence issues our customers were facing with hard embedded processors. By the time their design was finalized, the hard embedded core in the design was obsolete. The obsolescence-proof Nios processor can grow with design requirements—from one processor to as many as needed for higher processing power. The Nios processor has grown to over 12,000 licenses and counting. It is undoubtedly a smashing success!

This summer, Altera is proud to bring you sequels to those blockbusters—Cyclone II FPGAs and the Nios II embedded processor family. We've taken these two highly successful products and made them even better. This next generation of the Cyclone series maintains its low-cost leadership and offers even higher densities. The Nios II processor family delivers high-performance (200 DMIPS) and low-cost options with a new integrated development environment.

By combining the Nios II processor with Cyclone II FPGAs, you can build your own powerful 32-bit microprocessor for as little as \$0.35 cents of logic—possibly the lowest-cost microprocessor in the market. And there's more: the free Web Edition of the Quartus<sup>®</sup> II software version 4.1 has full support for the entire Cyclone II family!

Also in this issue, our customers share their experiences using Cyclone FPGAs and the Nios processor to gain a competitive edge. In fact, Altera's drive for continuous innovation—three new silicon architectures, a new 90-nm process geometry, and a new family of embedded processor cores this year alone—is the result of a single objective: to give our customers the blockbuster solutions they need to win in this highly competitive marketplace.

Happy summer to all,

Inda

Jordan Plofsky, Senior Vice President, Applications Business Groups

Nios II Processor

Quartus II Version 4.1

CycloneBot

#### Features

| Cyclone II: The Lowest-Cost FPGAs Ever                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------|

| Nios II: The World's Most Versatile Processor7                                                                                    |

| Quartus II Software Version 4.1 Adds Support for Cyclone II Devices &<br>Extends Software Technology Leadership12                 |

| Devices & Tools                                                                                                                   |

| MAX II Devices & PCI Compiler 3.1.0 Deliver Complete PCI Solutions                                                                |

| Customer Applications                                                                                                             |

| Cyclone Devices: The Fastest Ramping FPGAs Ever                                                                                   |

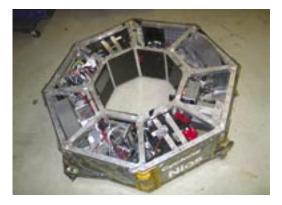

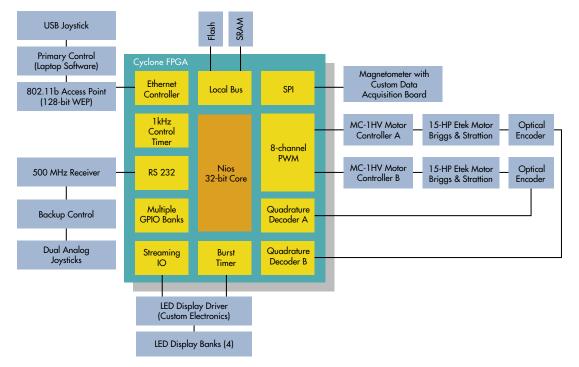

| CycloneBot Knocks Out the Competition with Cyclone & Nios 1-2 Punch                                                               |

| Cyclone FPGAs Enable Affordable, High-Performance Media Storage                                                                   |

| Cyclone FPGAs & Nios Processor Power Enhanced Capabilities in<br>Automotive Diagnostic Tool                                       |

| Cyclone FPGAs Drive Industry's First Low-Cost OEM Solution for<br>High-Performance Data Streaming over GigE                       |

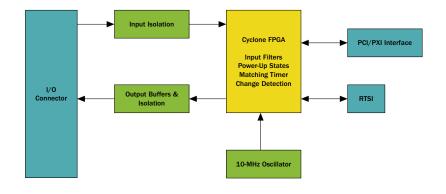

| National Instruments Announces Cyclone FPGA-Based Digital I/O<br>Products Ideal for Industrial Measurement & Control Applications |

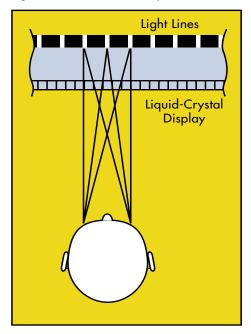

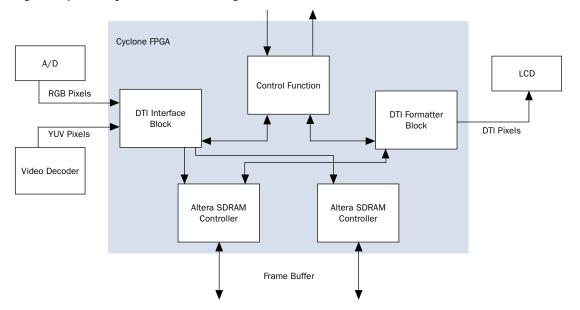

| DTI & Altera Displaying the Future in Real-Depth 3D                                                                               |

|                                                                                                                                   |

| Contributed Articles                                                                                                              |

#### ontributed Articles

| Cadence Incisive Platform: The Industry's Fastest, Most Effcient<br>Verification Platform | 36 |

|-------------------------------------------------------------------------------------------|----|

| Fast Signal Integrity Analysis with IEEE & IBIS Standards                                 | 38 |

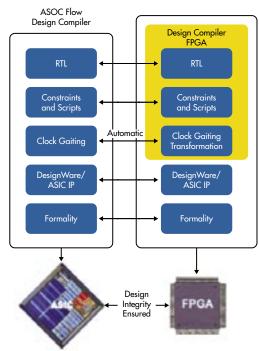

| Maximize Your Tool Investment & Speed & Lower Device Cost with<br>Design Compiler FPGA    | 40 |

| Layer 2 Switch Implementation with Altera FPGAs                                           | 42 |

| 5 x 5 Real-Time Monochrome Convolution Function Implemented<br>with Altera Cyclone FPGAs  | 44 |

| It's Showtime for Stratix Devices in Video Processing                                     | 45 |

#### Altera News

| Free IP to Quartus II Subscribers |

|-----------------------------------|

| Questions & Answers               |

| Cyclone II Questions & Answers    |

Publisher John Panattoni

**Technical Editor** Justin Bennett

Cover Layout Paula Cruz

101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 n\_v@altera.com www.altera.com

Altera, ACAP, ACCESS Program, ACEX, ACEX 1K, AMPP, APEX, APEX 20K, APEX 20KC, APEX 20KE, APEX II, Atlantic, Avalon, BitBlaster, ByteBlaster, III, ByteBlasterMV, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, Cyclone, Cyclone II, DirectDrive, E+MAX, Excalibur, FastLUT, FastTrack, FineLine BGA, FLEX, FLEX 10K, FLEX10KE, FLEX 10KA, FLEX 8000, FLEX 6000, FLEX 6000A, Flexible-IVDS, HardCopy, HardCopy Stratix, IP MegaStore, Jam, LogicLock, MasterBlaster, MAX, MAX II, MAX 9000, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000A, MAX 7000B, MAX 3000, MAX 3000A, MAX+PLUS, MAX+PLUS II, MegaCore, MegaLAB, MegaWizard, Mercury, MultiCore, MultiTrack, MultiVolt, NativeLink, Nios, Nios II, nSTEP, OpenCore, OpenCore Plus, OptiFLEX, PowerFit, PowerGauge, Quartus, Quartus II, RapidLAB, SignalCore, SignalProbe, SignalTap, SignalTap Plus, SignalTap II, SoftMode, Stratix, Stratix II, Stratix GX, Terminator, The Programmable Solutions Company, TriMatrix, True-LVDS, USB Blaster, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: ARM and Multi-ICE are registered trademarks and ARM922T and ETM9 are trademarks of ARM limited. HyperTransport is a trademark of HyperTransport Consortium. Mentor Graphics is a registered trademark and Exemplar, LeonardoSpectrum, and ModelSim are trademarks of Mentor Graphics Corporation. RapidIO is a trademark of RapidIO Trade Association. Rochester Electronics is a registered trademark of Rochester Electronics, Inc. All other third party marks and brands are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. The actual availability of Altera's products and features could differ from those projected in this publication and are provided solely as an estimate to the reader. Cover photo copyright@ 2004 David Nance. Copyright© 2004 Altera Corporation. All rights reserved.

# Cyclone II: The Lowest-Cost FPGAs Ever

#### **Cyclone** *II*

Furthering its low-cost FPGA leadership, Altera introduces the Cyclone<sup>™</sup> II family, the latest in the Cyclone series of low-cost FPGAs. Altera forever changed the FPGA industry with the introduction of the Cyclone device family in 2002—bringing to market the first and only FPGA family designed from the ground up for the lowest cost. The Cyclone II FPGA family offers the same benefits as its predecessor—a customerdefined feature set, industry-leading performance, and low power consumption—but with more density and features—at dramatically lower costs. Cyclone II devices extend the low-cost FPGA density range up to 68,416 logic elements (LEs) and up to 1.1 Mbits of embedded memory.

Cyclone II devices are manufactured on 300-mm wafers using TSMC's 90-nm low-k dielectric process, the same proven process used with Altera's Stratix<sup>®</sup> II devices. To ensure rapid availability and low cost, by minimizing silicon area, Cyclone II devices can support complex digital systems on a single chip at a cost that rivals that of ASICs.

#### **The Ideal ASIC Alternative**

The evolution of the programmable logic industry has fundamentally changed the value proposition of FPGAs to include high-volume, low-cost applications. A few years ago, the closest an FPGA could get to low-cost applications was as an ASIC prototyping tool. With the increasing development and production cost of ASICs, FPGAs today are becoming the de facto standard for system design in the consumer, industrial, data communications, telecommunications, wireless, medical, and automotive markets. At prices comparable to ASICs, Altera's new Cyclone II device family delivers a low-risk, low-cost, and fast time-to-market solution. The Cyclone II family was developed with the objective of building the lowest-cost FPGA and making it easy to adopt in high-volume, traditionally ASIC applications. The Cyclone II product-development process was based on extensive interaction with customers in markets that traditionally rely on ASICs. These customers identified the threshold price points, key features, and performance required to make FPGAs a viable solution in high-volume systems. Cyclone II devices are offered in low-cost packages with a wide range of user I/O pins.

For applications that currently use low- to middensity ASICs, Cyclone II FPGAs provide a flexible, risk-free option without up-front non-recurring engineering (NRE) charges or minimum order quantities. With a feature set unmatched by any other low-cost FPGA—such as embedded  $18 \times 18$ multipliers for high-performance digital signal processing (DSP) applications and support for DDR2 and QDRII memory interfaces at up to 668 Mbps— Cyclone II devices are well equipped to integrate complex, system-level functions.

#### **Key Cyclone II Features**

Cyclone II FPGAs offer several system-level features to meet the needs of the low-cost, high-volume marketplace. See Table 1.

Logic Density: Cyclone II devices continue the success of the first-generation Cyclone device family and extend the reach of FPGAs further into cost-sensitive, high-volume applications by offering up to 68,416 LEs—three times more logic density than Cyclone devices.

| Table 1. Cyclone II Family Overview |                                              |                                              |                                              |                              |                              |                              |

|-------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------|------------------------------|------------------------------|

| Feature                             | EP2C5                                        | EP2C8                                        | EP2C20                                       | EP2C35                       | EP2C50                       | EP2C70                       |

| Logic Elements                      | 4,608                                        | 8,256                                        | 18,752                                       | 33,216                       | 50,528                       | 68,416                       |

| M4K RAM Blocks                      | 26                                           | 36                                           | 52                                           | 105                          | 129                          | 250                          |

| Total RAM Bits                      | 119,808                                      | 165,888                                      | 239,616                                      | 483,840                      | 594,432                      | 1,152,000                    |

| Embedded 18 $	imes$ 18 Multipliers  | 13                                           | 18                                           | 26                                           | 35                           | 86                           | 150                          |

| Phase-Locked Loops                  | 2                                            | 2                                            | 4                                            | 4                            | 4                            | 4                            |

| Maximum User I/O Pins               | 142                                          | 182                                          | 315                                          | 475                          | 450                          | 622                          |

| Package Offerings                   | 144-pin TQFP<br>208-pin PQFP<br>256-pin FBGA | 144-pin TQFP<br>208-pin PQFP<br>256-pin FBGA | 208-pin PQFP<br>256-pin FBGA<br>484-pin FBGA | 484-pin FBGA<br>672-pin FBGA | 484-pin FBGA<br>672-pin FBGA | 672-pin FBGA<br>896-pin FBGA |

- Embedded Memory: Typical systems require on-chip memory capabilities for system cache, data buffering, clock domain translation, and first-in first-out (FIFO) applications. Cyclone II devices contain M4K embedded memory blocks consisting of 4,608 bits per block (4,096 bits plus 512 parity bits). With up to 1.1 Mbits of on-chip memory, Cyclone II embedded memory blocks support multiple configurations, including true dual-port and single-port RAM, ROM, and FIFO buffers.

- External Memory Interface: Cyclone II devices provide ample on-chip memory for many low-cost applications. However, many other applications also require external memory devices for additional storage resources. As storage requirements exceed the abundant onchip memory resources, devices must be able to interface to external memory devices. Altera worked with leading memory vendors to ensure that users can connect the very latest memory devices to Cyclone II FPGAs. Cyclone II devices have been designed for high-speed data transfer to and from external memory devices. Cyclone II devices are designed to communicate with double data rate (DDR and DDR2), single data rate (SDR) SDRAM devices and quad data rate (QDRII) SRAM devices through a dedicated interface that ensures fast, reliable data transfer at up to 668 Mbps.

- Embedded Multipliers: A convergence of data, audio, and video in DSP applications has led to increased performance requirements to support emerging protocols such as JPEG 2000, MPEG-4, 802.11×, CDMA2000, 1× EV DV, HSDPA, and

W-CDMA. Cyclone II devices feature up to 150 embedded  $18 \times 18$  multipliers that are ideal for low-cost DSP applications such as consumer, wireless, and image processing. Cyclone II embedded  $18 \times 18$  multipliers are capable of implementing common DSP functions such as finite impulse response (FIR) filters, fast Fourier Transfers (FFTs), correlators, and encoders/decoders. Capable of running at 250 MHz, the embedded multipliers in Cyclone II devices eliminate the performance bottleneck in complex arithmetic calculations and increase overall DSP system throughput by orders of magnitude. Cyclone II devices can be used as "FPGA co-processors" for DSP applications that offload complex arithmetic computations from the digital signal processor and boost overall system performance for lower system costs.

I/O Standards: Cyclone II devices support a variety of single-ended and differential I/O standards commonly used for interfacing with other devices on the board. This capability gives designers flexibility in designing their highperformance systems. New to Cyclone II devices is support for the mini-LVDS and LVPECL differential I/O standards, and PCI-X and HSTL single-ended I/O standards. Single-ended I/O standards are critical when working with advanced memory devices such as double-data rate (DDR/DDR2) SDRAM and QDRII SRAM. Additional Cyclone II supported single-ended and differential I/O standards include LVTTL, LVCMOS, PCI, SSTL, LVDS, and RSDS.

| Table 2. Cyclone Series Target Applications                                                                                                                           |                                                                                                                                                                                                |                                                                                                                                                   |                                                                                                                          |                                                                                                                                                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Consumer                                                                                                                                                              | Wireline & Wireless<br>Communications                                                                                                                                                          | Automotive                                                                                                                                        | Computers &<br>Storage Devices                                                                                           | Military, Industrial & Medical                                                                                                                            |  |

| <ul> <li>Cameras</li> <li>A/V Conference Equipment</li> <li>Plasma Displays</li> <li>HDTVs</li> <li>DVD Players</li> <li>Camcorders</li> <li>Set-Top Boxes</li> </ul> | <ul> <li>Modems</li> <li>DSLAM Systems</li> <li>Low-End Routers &amp; Switches</li> <li>High-Speed Wireless CPEs</li> <li>Wireless LAN Access Points</li> <li>Wireless Basestations</li> </ul> | <ul> <li>Navigation Systems</li> <li>Satellite Radio Receivers</li> <li>Hybrid TV Receivers</li> <li>Telematics</li> <li>Entertainment</li> </ul> | <ul> <li>Printers</li> <li>Copiers</li> <li>SAN Subsystems</li> <li>Storage Servers</li> <li>Storage Switches</li> </ul> | <ul> <li>Factory Automation</li> <li>Process Control</li> <li>MRIs</li> <li>X-Rays</li> <li>Radar</li> <li>SDR</li> <li>Network Test Equipment</li> </ul> |  |

continued on page 6

#### **New Applications for FPGAs**

With its higher densities, enhanced features, and lower price points, Cyclone II devices extend the use of FPGAs in cost-sensitive, high-volume applications that previously required an ASIC. Over 3,000 customers have used the first-generation Cyclone devices since its introduction, and Cyclone II devices will extend this success in the consumer, computer and storage, wireless, wireline, industrial, medical, and automotive markets. Table 2 provides examples of applications that benefit from using the Cyclone series.

#### Low-Cost Processor Solution: Cyclone II Devices & Nios II Processor

Cyclone II devices support the Nios® II family of embedded processors, a widely adopted (and obsolescence free) user-configurable, general-purpose RISC embedded processor. The Nios II processor family extends Altera's soft embedded processor leadership with better performance, lower cost, and the most complete set of software development tools available anywhere. Cyclone II dedicated multipliers help improve Nios II processor performance and efficiency. The Cyclone II family can incorporate multiple processors in one device, providing savings in cost, footprint, and power efficiency. Cyclone II devices provide designers with maximum flexibility, and balance performance needs and device resource usage by supporting all three Nios II processor cores, each optimized for a particular price and performance range. All three cores support a single instruction set architecture, making them 100% code compatible:

- Nios II /f (fast) Highest performance, moderate FPGA utilization (~ 1,800 LEs)

- Nios II /s (standard) High performance, low FPGA utilization (~ 1,200 LEs)

- Nios II /e (economy) Lower performance, smallest FPGA utilization (~ 600 LEs)

#### **Low-Cost Configuration Devices**

To offer the lowest total solution cost, Altera created a low-cost serial configuration device family for the Cyclone series. Serial configuration devices are priced for volume applications as low as 10% of the price of the corresponding Cyclone series device. Four serial configuration devices (1 Mbit, 4 Mbits, 16 Mbits, and 64 Mbits) are offered in a space-saving 8-pin and 16-pin small-outline integrated circuit (SOIC) package, as shown in Table 3. To add even more value, any unused memory in these devices can be used for general-purpose storage, such as storing the software code for Nios II embedded processors.

#### **Free Design Software**

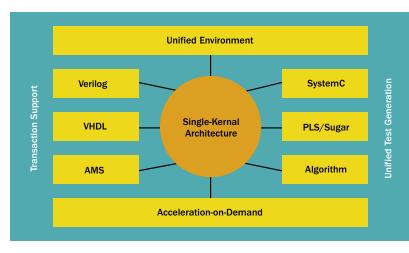

All Cyclone II devices are fully supported in the free Web Edition of the Quartus® II version 4.1 development software. Additionally, subscribers to the Altera Subscription Program will receive full Cyclone II support in the subscription edition of the Quartus II software version 4.1. The Quartus II software is the industry's most advanced development tool for FPGAs, providing a comprehensive suite of synthesis, optimization, and verification tools in a single, unified design environment. The Quartus II software technology advantage enables designers to select, integrate, and evaluate intellectual property (IP) in Cyclone II designs in a matter of minutes. Quartus II advanced technology reduces development costs and helps bring products to market faster. The Quartus II software also integrates seamlessly with all leading third-party synthesis and simulation tools. The free Quartus II Web Edition can be downloaded at no cost from www.altera.com/q2webedition.

Learn more about the advantages of the Cyclone II family by visiting the Altera web site today at **www.altera.com/cyclone2**.

|                         | nfiguration Devices | 1           |                           |                                 |

|-------------------------|---------------------|-------------|---------------------------|---------------------------------|

| Configuration<br>Device | Capacity            | Package     | Cyclone Devices Supported | Cyclone II Devices<br>Supported |

| EPCS1                   | 1 Mbit              | 8-pin SOIC  | EP1C3, EP1C4, EP1C6       | EP2C5                           |

| EPCS4                   | 4 Mbit              | 8-pin SOIC  | All                       | EP2C5, EP2C8,<br>EP2C20         |

| EPCS16                  | 16 Mbit             | 16-pin SOIC | All                       | All                             |

| EPCS64                  | 64 Mbit             | 16-pin SOPC | N/A                       | All                             |

# Nios II: The World's Most Versatile Processor

With widespread customer adoption, the 16-bit Nios® processor has set the standard for soft-core processors in programmable logic, and Altera sold over 13,000 development kits in under three years. The 32-bit Nios II family of embedded processors builds upon this success, delivering higher performance and lower cost with a robust set of software development tools.

#### **Family of Embedded Processors**

The Nios II family consists of three members—fast, standard, and economy—each optimized for a specific price and performance range. All three cores use a common 32-bit instruction set architecture (ISA) and are 100% binary code compatible. See Table 1.

- Nios II /f Fast CPU: Optimized for maximum performance, the Nios II /f processor delivers 220 DMIPs performance in the Stratix® II family of high-performance FPGAs, placing it squarely in the ARM® 9 class of processor. Four times faster than the original Nios CPU, it is 40% smaller as well.

- Nios II /s Standard CPU: The Nios II /s core strikes a balance between processing performance and logic element (LE) usage. It is 60% faster than the fastest Nios CPU, and smaller than the smallest Nios CPU, achieving over 120 DMIPS and consuming only 930 equivalent LEs in Stratix II devices.

Nios II /e Economy CPU: Optimized for lowest cost, the Nios II /e core achieves a smaller FPGA footprint (less than 600 LEs), consuming as little as \$0.35 worth of logic in a Cyclone<sup>TM</sup> II device. The Nios II /e core is half the size of the smallest Nios core and four times the performance.

# Nios<sup>®</sup>II

#### **Getting the Perfect Fit Processor**

Designers of embedded systems often think of processor performance in terms of clock frequency, or benchmarks (e.g., Dhrystones, EEMBC, etc.). The true performance of an embedded system has less to do with its clock frequency or DMIPS alone, and more with the system that surrounds it. With the Nios II processor, designers can create in minutes a system with the exact mix of processors, peripherals, and interfaces required using the SOPC Builder design tool. Over 60 peripherals are available from Altera and third-party partners that integrate seamlessly with the Nios II family of processors, including a wide range communications, memory, signal processing, and interface cores. Developers can also incorporate their own logic with the "Interface to User Logic" wizard, providing the ultimate in versatility.

#### continued on page 8

| Table 1. Nios II Architectural Overview |                                    |                       |                              |              |  |  |

|-----------------------------------------|------------------------------------|-----------------------|------------------------------|--------------|--|--|

| Featu                                   |                                    | Core                  |                              |              |  |  |

| reatu                                   | re                                 | Nios II /f Nios II /s |                              | Nios II /e   |  |  |

| Object                                  | Objective                          |                       | Performance/ Size<br>Balance | Minimal Size |  |  |

| Performance (1)                         | Max DMIPS (2)                      | 220                   | 128                          | 31           |  |  |

|                                         | Max f <sub>max</sub>               | 188                   | 170                          | 201          |  |  |

| Address and                             | Address and Data Bus               |                       | 32 bit                       | 32 bit       |  |  |

| Pipeli                                  | Pipeline                           |                       | 5 Stages                     | None         |  |  |

| External Addr                           | ess Space                          | 32 Gigabytes          | 32 Gigabytes                 | 32 Gigabytes |  |  |

| Cache                                   | Instruction                        | 512 bytes- 64 Kbytes  | 512 bytes - 64 Kbytes        | None         |  |  |

| (Configurable)                          | Data                               | 512 bytes- 64 Kbytes  | None                         | None         |  |  |

| Area                                    | Cyclone,<br>Cyclone II,<br>Stratix | × < 1,800 LEs         | × < 1400 LEs                 | × < 700 LEs  |  |  |

|                                         | Stratix II                         | × < 1,050 LEs         | × < 950 LEs                  | × < 500 LEs  |  |  |

Notes to Table 1:

(1) Performance varies based on the target device architecture. Numbers shown above are for Stratix II devices.

(2) DMIPS: Dhrystone MIPS (Utilizing Dhrystone 2.1 Benchmark)

#### **Flexible Performance & Cost**

Nios II system performance can scale to fit the application. Designers can choose any combination of CPU cores, and place as many as needed, in an Altera® FPGA. For example, a single Nios II /f core in a Stratix II device achieves 220 DMIPS performance in approximately 1,800 equivalent LEs. For low cost systems, the Nios II /e core consumes less than \$0.35 of logic in a Cyclone II device, leaving plenty of logic for implementing functions previously handled by external devices, which reduces board cost, complexity, and power consumption. See Table 2.

#### **Accelerating System Performance**

Developers of embedded systems must pick a processor that delivers the system performance they need. Conventional benchmarks have limited value since the final measure is a system running the user's application code. Designers often select a processor with higher performance (and higher cost) than they need to gain a margin of safety. Performance of Nios II systems can scale to fit the application using custom instructions, high bandwidth switch fabric, and hardware accelerators.

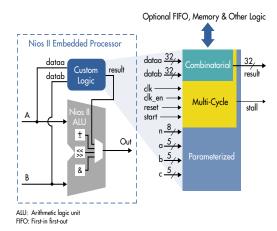

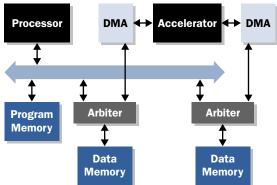

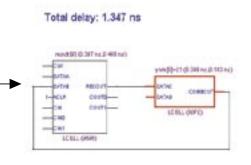

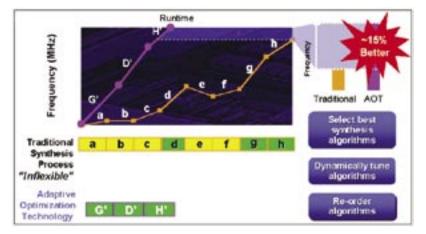

The Nios II family of processors supports up to 256 custom instructions to accelerate logic or mathematically complex algorithms normally handled in software. For example, a block of logic that performs a cyclic redundancy code (CRC) calculation on a 64-Kb buffer operated 27 times faster as a custom instruction than when performed by software. Nios II processors support fixed and variable cycle operations, include a wizard for importing user logic as a custom instruction, and automatically create software macros for use in developers' code. See Figure 1.

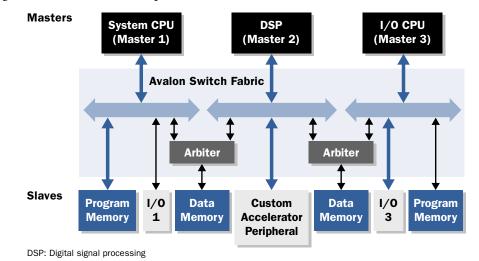

Traditional processors share a single system bus with DMA channels and other "master" functions limiting

#### Figure 1. Nios II Custom Instruction Implementation

bus access to one master at a time. Nios II systems benefit from the Avalon<sup>TM</sup> switch fabric, which provides a dedicated data path to each master, allowing all masters to transfer data simultaneously. Only when two (or more) masters try to access the same slave peripheral at the same time is one master forced to wait for access. Simultaneous transactions provide orders-of-magnitude greater system performance than bus-based embedded processors. See Figure 2.

Large blocks of data can be processed concurrently with CPU operation by adding application-specific hardware accelerators. The Avalon switch fabric provides a flexible interconnect path that allows multiple cores (e.g., CPU and accelerator) to perform simultaneous reads and writes using dedicated data paths, dramatically boosting system throughput. Hardware accelerators act as a custom co-processor within the FPGA, typically by having the processor initiate the operation (i.e., instruct the DMA to feed the accelerator from one buffer, empty it into another buffer and notify the CPU when it is complete). The previously mentioned CRC example runs over 530 times faster using the hardware accelerator. See Figure 3.

| Table 2. Nios II Performance & Size |                   |       |       |                                         |       |       |                      |       |     |

|-------------------------------------|-------------------|-------|-------|-----------------------------------------|-------|-------|----------------------|-------|-----|

|                                     | Nios II /f (fast) |       |       | Nios II /f (fast) Nios II /s (standard) |       |       | Nios II /e (economy) |       |     |

| Family                              | f <sub>max</sub>  | DMIPS | LEs   | f <sub>max</sub>                        | DMIPS | LEs   | f <sub>max</sub>     | DMIPS | LEs |

| Stratix II (1)                      | 188               | 220   | 1,012 | 170                                     | 128   | 930   | 201                  | 31    | 527 |

| Stratix                             | 141               | 165   | 1,849 | 130                                     | 97    | 1,313 | 144                  | 22    | 571 |

| Cyclone                             | 125               | 92    | 1,732 | 124                                     | 54    | 1,207 | 140                  | 17    | 583 |

| Cyclone II (1)                      | 125               | 105   | 1,732 | 124                                     | 60    | 1,207 | 140                  | 22    | 583 |

| HardCopy                            | 143               | 167   | 1836  | 138                                     | 103   | 1368  | 152                  | 24    | 568 |

Note to Table 2:

(1) Estimated performance.

#### Figure 2. Avalon Switch Fabric Operation

DMA: Direct memory access

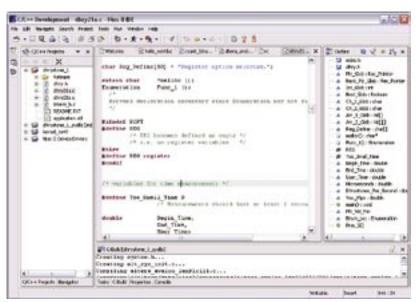

#### Nios II Integrated Development Environment

The Nios II Integrated Development Environment (IDE) provides a complete software development environment, including automatic library generation, editing, compiling, debugging, and flash programming facilities (see Figure 4). The Nios II IDE features include:

- Library Generation: The Nios II IDE automatically generates a custom software library based on the hardware configuration (i.e., peripheral driver support).

- Project Templates: The Nios II IDE provides a set of example projects that provide a starting point for application development. Project templates include a web server, a board diagnostic

program, and a custom instruction example. Users can add their own templates to facilitate design reuse.

- *Editor*: The Nios II IDE includes a C/C++ aware editor with code completion and advance search capabilities.

- *Compiler*: The Nios II IDE provides seamless integration with the GNU compiler, assembler, and linker.

#### Figure 4. Nios II IDE

continued on page 10

- Multi-Target Support:

- Hardware Debugging: Debugging connection to physical target through any Altera JTAG cable. High-speed USB Blaster included in Nios II kit.

- Instruction set simulator: The Nios II IDE enables a virtual software debug session on the user's workstation, requiring no physical hardware.

- ModelSim<sup>®</sup> simulator: Run software on an RTL model of the Nios II processor and system (Verilog or VHDL).

- Debugger:

- Debugging controls: Set breakpoints, run, stop, and step through program execution.

- Two hardware breakpoints: The Nios II IDE allows the debugging of code in non-volatile memory regions.

- Two data triggers: Locate troublesome software bugs by triggering on any address, data, and bus cycle (load/store) combination.

Diagnose complex system problems by combining two data triggers into a "Super Trigger" for triggering on address ranges and data patterns with mask.

- Flash Programmer: The Nios II IDE enables users to program FPGA configurations (SRAM Object File (.sof)), system firmware, and arbitrary data into any common flash interface (CFI).

- On-chip trace: Analyze a program's execution by capturing up to 16 frames of instruction trace into on-chip memory, and viewing in source, assembly, or mixed display.

| Table 3. Third-Par | ty Support       |                                                                   |

|--------------------|------------------|-------------------------------------------------------------------|

| Product            | Description      | Provider                                                          |

| Nios II IDE (1)    | IDE/Debugger     | Altera ( <b>www.altera.com</b> )                                  |

| Code lab (2)       | IDE/Debugger     | Mentor/Accelerated Technology<br>(www.acceleratedtechnology.com)  |

| MicroC/OS-II (2)   | RTOS             | Micrium (www.micrium.com)                                         |

| Nucleus Plus (2)   | RTOS             | Mentor/ Accelerated Technology<br>(www.acceleratedtechnology.com) |

| uCLinux            | OS               | Open Source (www.niosforum.com)                                   |

| KROS               | RTOS             | KROS Technologies (www.krostech.com)                              |

| NORTi              | RTOS             | MiSPO (www.mispo.co.jp)                                           |

| PrKERNELv4         | RTOS             | eSOL (www.esol.co.jp)                                             |

| Lightweight IP (1) | TCP / IP Stack   | Altera (www.altera.com)                                           |

| ISA-Nios/T         | JTAG Trace Probe | First Silicon Solutions (FS2) (www.fs2.com)                       |

#### Notes to Table 3:

- Advanced debugging solutions (add-on packages): Developers can expand their debug capabilities to include two additional hardware breakpoints, two additional data triggers, and boost on-chip trace capture to 128 frames through a software upgrade package for \$695. Users seeking complete debugging coverage can get all the features mentioned above, plus 128,000 frames of external trace capture via the ISA-NIOS/T system probe for \$4,995. Both packages are available for purchase from the First Silicon Solutions (FS2) Corporation.

#### **RTOS & Middleware Included**

Nios II development kits ship with a complete, portable, ROMable, pre-emptive real-time kernel from Micrium (MicroC/OS-II) that includes full source code, printed reference documentation, and a license to develop applications using Altera development boards. Once developers migrate their designs to their own board, they must purchase a license from Micrium. The Nios II processors also include Lightweight IP, a sockets based, open source TCP/IP stack that can be used in MicroC/OS-II applications.. The software is shipped as source code with documentation, reference designs, and technical support from Altera. See Table 3.

The Nios II development kits also ship with an evaluation version of Accelerated Technology's Nucleus Plus RTOS and code|lab debugger, providing developers with an opportunity to evaluate these powerful software packages.

#### Availability

The Nios II processor family is available in complete development kits from Altera for the Stratix, Stratix II, Cyclone, and Cyclone II FPGA device families. These kits include the Nios II development tools, the Quartus<sup>®</sup> II design software (development kit edition), a development board, and the USB Blaster download cable.

An evaluation version of the Nios II processor family and tool chain will be provided to all active Quartus II subscribers through their Altera Software Subscription, and is available for download at www.altera.com/testdriveniosii. Additionally, customers can go to www.niosforum.com to exchange ideas, designs, and exchange information with other Nios II processor users.

<sup>(1)</sup> The full version is included in the Nios II development kits from Altera.

<sup>(2)</sup> The evaluation version is included in the Nios II development kits from Altera.

# Introducing Nios II.

# Nios II

# The world's most versatile processor!

## Nios<sup>•</sup>II The ultimate in design flexibility.

The world's most popular soft-core processor just got better! Altera introduces the Nios® II family of embedded processors, featuring three CPU cores offering unprecedented performance and cost options. With Nios II processors, designers can define the exact features, performance, and cost they need in Altera's high-performance Stratix® series, low-cost Cyclone™ series, and HardCopy® device families.

The Nios II development kits provide a complete, easy to use tool set including

the new Nios II integrated development environment to accelerate software design. Try the Nios II processor today and experience the ultimate in design flexibility.

- Over 200 DMIPs performance

- Consumes as little as \$0.35 of logic

- Supports multi-processor systems

- Library of over 60 programmable peripherals

- Industry's most complete development kits

- Royalty-free & obsolescence-proof

The Programmable Solutions Company®

#### www.altera.com/nios2

Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

# Leading through innovation.

# Quartus II Software Version 4.1 Adds Support for Cyclone II Devices & Extends Software Technology Leadership

Version 4.1 of the Quartus<sup>®</sup> II design software extends Altera's software technology leadership by adding support for the Cyclone<sup>TM</sup> II FPGA family—the lowest cost FPGAs ever—and lowering development costs with new verification, optimization, and easeof-use features.

#### **Design for Cyclone II Devices Today**

Cyclone<sup>™</sup> II devices are low-cost, general-purpose FPGAs that are based on TSMC's 90-nm, 1.2-V, 9-layer-metal low-k dielectric process technology and built on 300-mm wafers. Cyclone II devices, the second generation in the Cyclone series, are designed with the same approach as their first-generation predecessors, meaning they built to specifically minimize silicon area, while being armed with a full set of robust, system-enabling features. For more information on Cyclone II devices, refer to "Cyclone II: The Lowest-Cost FPGAs Ever" on page 4.

#### Quartus II On-Line Demos & Software Handbook Updated

Quartus II on-line demonstrations (see Figure 1) available on the Altera® web site are the easiest way to see the latest Quartus II software features in action and learn where to get more information.

#### Figure 1. Quartus II On-Line Demonstrations

Existing videos have been updated with the latest Quartus II software version 4.1 enhancements and the following new video demonstrations:

- Scripting

- Interfacing to External Memory

- Optimization Assistant

- Using the RTL Viewer and Tech Map Viewer

- Updating RAM/ROM via JTAG

The Quartus II Software Handbook has been updated with the latest Quartus II software version 4.1 enhancements and the following new chapters:

- Synopsys DC FPGA Support

- Analyzing Designs with the Quartus II RTL Viewer and Technology Map Viewer

- Effective Use of Revisions

- In-System Updating of Memory and Constants

The Quartus II Handbook is available from the Altera web site.

#### Quartus II Subscriptions Now Include Altera MegaCore IP Library CD-ROM

Quartus II software subscriptions now include the Altera MegaCore® IP Library CD-ROM, including OpenCore® Plus evaluation versions of all Altera MegaCore functions, and the Nios® II embedded processor evaluation edition. The MegaCore IP Library CD-ROM includes off-the-shelf MegaCore intellectual property (IP) functions optimized for Altera devices. Only the Quartus II software offers OpenCore Plus infrastructure technology to support IP evaluation in third-party simulation environments and in hardware before making any IP purchases.

# New Features—Extending Software Technology Leadership

The Quartus II software version 4.1 includes new technology that lowers development costs and further simplifies and accelerates high-density FPGA design.

#### Stratix II Physical Synthesis Optimization

Physical synthesis optimizations now provide an average of 9% faster performance for Stratix<sup>®</sup> II designs. This gain is on top of the 50% performance gain delivered over Stratix designs without using physical synthesis. Synthesis Multiplexer Optimizations Reduce Area Up to 30%

Designers using the Quartus II integrated synthesis feature can now reduce device area usage up to 30% to fit into a smaller device and save cost. Area reductions come from a new Quartus II integrated synthesis optimization option optimizes multiplexer usage to take advantage of Altera FPGA architectural features. Results will vary depending on the amount of multiplexers included in your design.

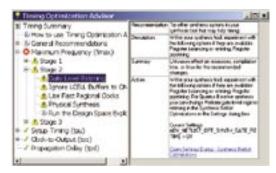

#### New Tools Simplify Design Optimization

New timing and resource optimization advisor tools are included in Quartus II software version 4.1 to provide specific advice on optimizing design timing performance and/or resource utilization based on the current design project settings and assignments. Detailed instructions and links to recommended software features to implement the proposed suggestions are included. Figure 2 shows an example of the timing optimization advisor interface. Figure 3 shows a legend for the symbols displayed in the optimization advisors.

#### Figure 2. Timing Optimization Advisor Example

Figure 3. How to Use the Timing Optimization Advisor

| Recommendatio | <ul> <li>Use the recommendations in the Timing<br/>Optimization advisor to optimize the timing in your<br/>design.</li> </ul>                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description   | For each problem area, there are a set of<br>recommendations. It is recommended to follow the<br>order of the recommendations to make your<br>changes.                                                                                         |

| Legend        | • means there are some violations in the specified area. • means the settings in your design don't match what are recommended in Optimization Advisor. • means the settings in your design match what are recommended in Optimization Advisor. |

|               | (3)- means you need to check it and do as<br>recommended, but Optimization Advice has no way<br>to detect if the recommended changes are made or<br>not.                                                                                       |

| Action        | Follow the recommendations to make your<br>changes.                                                                                                                                                                                            |

#### Time Groups Simplify Timing Constraint Entry

The new time group feature allows users to organize nodes into a group so that timing assignments can be made to the group instead of to each individual node. The time group feature is available through the graphical user interface and can be set through toolcommand language (Tcl) commands.

# Incrementally Update RAM & Constants In-System

Using the new in-system memory content editor feature, engineers can now easily perform "what if" type experiments in-system in just seconds. The Quartus II software enables FPGA memory contents and design constants to be updated in-system without recompiling a design or reconfiguring the rest of the FPGA.

#### **Technology Map Viewer**

The new technology map viewer feature included in the Quartus II software version 4.1 can be used after the synthesis step to debug designs at a detailed level by viewing a logical representation of the design implementations mapped into Altera device primitives. Once the fitting and timing analysis steps have been performed, critical timing paths and timing information can be highlighted and cross-probed to the technology map viewer display. From the technology map viewer display, users can cross-probe to design source files, the assignment editor, the Timing Closure Floorplan Editor, or the Quartus II Chip Editor for design optimization. See Figure 4 on page 14.

More information is available in the new *Analyzing Designs with the Quartus II RTL Viewer and Technology Map Viewer* chapter of the Quartus II handbook.

#### Import/Export Assignments in CSV Format

Engineers can now easily transfer assignments between the Quartus II software and Excel spreadsheets using the comma-separated value (CSV) format. This capability can aid in transferring pin-out information to printed circuit board design software packages that support interfaces with Excel spreadsheets.

continued on page 14

#### Figure 4. Technology Map Flow

|      | Slack              | Actual Insu (period)                         |

|------|--------------------|----------------------------------------------|

| 804  | 347476             | Rentacted to 422 12 NHz ( period + 2.37 ks ) |

| 405  | 343 <sup>7</sup> m | Restacted to 422 12 NHz   period = 2 37 es   |

| 806  | 3505 ms            | Renticted to 42212NHz [period + 2:37 ns]     |

| 207  | 3508 mi            | Renticted to 42212 MHz ( period = 2.17 ns )  |

| 500  | 3756 nr            | Rentacted to 422 12 MHz (period = 2.57 mz)   |

| 805  | 3 903 mi           | Restacted to 42212NHz [period = 2.07 na]     |

| 418  | 3 938 m            | Renticted to 422 12 MHz ( period = 2.57 ml)  |

| 411  | 3942rs             | Restacted to 42212NHz [period + 237 ml]      |

| \$12 | 3943mt             | Restricted to 42212NHz [period = 2.37 ns]    |

|     | End<br>Gri To                                                                                                                        | Celei:       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|--------------|

|     | Zoom                                                                                                                                 |              |

|     | rienestre Up<br>Heraldhe Quers                                                                                                       | 01-0<br>01+0 |

|     | Stor                                                                                                                                 |              |

| 1   | Facture .                                                                                                                            |              |

| 新聞題 | Locate in Assignment Edit<br>Locate in Design Mis<br>Locate in Timing Choure (<br>Locate in Livit Completion<br>Coole in Q ig Editor | Boottikin    |

|     | Locate In Electrone Proper                                                                                                           | ty Edux      |

|     | Çup <del>y</del>                                                                                                                     | Col+C        |

|     | Vewer Options                                                                                                                        |              |

#### SignalTap II Embedded Logic Analyzer Enhancements

The free Quartus II programmer software now includes device configuration and the SignalTap® II embedded logic analyzer viewer, allowing easy deployment of in-system logic analysis capabilities to multiple lab locations or field service personnel. The Quartus II programmer software is a no-cost, standalone version of the Quartus II device programming and configuration functions available from the download center of the Altera web site. The SignalTap II embedded logic analyzer advanced trigger feature has also been updated with an event counter trigger condition function. This feature provides the ability not just to trigger on an event, but also to trigger after an event is satisfied a specified number of times. To improve usability, users now have the choice to configure SignalTap II embedded logic analyzers using the MegaWizard® Plug-In Manager and to instantiate them directly in HDL source code, in addition to the graphical user interface instantiation method.

#### Figure 5. Compare Revisions Feature

|                                   | C:/atera/gdesignol1/tr_titles/c<br>Revison Stratix_II | C./atera/adesigns41/fg_titter/c<br>Revison filter |

|-----------------------------------|-------------------------------------------------------|---------------------------------------------------|

| Clock Setup: 'ck'                 |                                                       |                                                   |

| - Slack                           | 0.140 ns                                              | -2.590 ns                                         |

| <ul> <li>Required Time</li> </ul> | 200.00 MHz [ period = 5.000 ns ]                      | 200.00 MHz [ period = 5.000 no ]                  |

| <ul> <li>Actual Time</li> </ul>   | 205.76 MHz [ period = 4.060 ns ]                      | 131.75 MHz [ period + 7.590 ns ]                  |

| - From                            | state minut18/ter~27                                  | state minor18her*27                               |

| - To                              | acc.inst3kesu#[11]                                    | accinst3eeu#[11]                                  |

| - From Clock                      | ck                                                    | ck                                                |

| - To Clock                        | dk                                                    | ck                                                |

| - Faled Paths                     | 0                                                     | 236                                               |

#### Version Support & Compare Revisions Feature

Version support gives designers the ability to easily experiment with different versions of design source files and settings. This feature complements the previously introduced revisions feature, which has been updated to allow users to easily compare the results of two more project revisions side by side in a spreadsheet display format (see Figure 5). Users can also compare results of a revision settings to the results obtained in other projects.

#### Version Compatible Database

Designers can now analyze designs in future versions of the Quartus II software without recompiling the design, thus preserving design results and saving time. The Quartus II software can generate a versioncompatible database that allows designers to export a design database from a project and import the database into a future version of the Quartus II software for analysis.

# Experience Quartus II Software Version 4.1 Today

The Quartus II software version 4.1 delivers unmatched performance, efficiency, and ease of use for CPLD, FPGA, and structured ASIC designs. Quartus II software version 4.1 is now shipping to all customers with active software subscriptions. The Quartus II version 4.1 Web Edition software is available for downloading from the Altera web site or as part of the Quartus II Web Edition Software Suite CD-ROM.

## **Altera Devices**

Tables 1 through 16 list the logic element (LE), macrocell and gate counts, pin/package options, I/O pin counts, supply voltages, RAM bits, and other device-specific features of Altera® CPLDs, FPGAs, HardCopy® structured ASICs, and configuration devices.

| Table 1. | Cyclone II De              | evices                |                   |                                |      |                   |                                                                         |                             |

|----------|----------------------------|-----------------------|-------------------|--------------------------------|------|-------------------|-------------------------------------------------------------------------|-----------------------------|

| Device   | Logic<br>Elements<br>(LEs) | M4K RAM<br>Blocks (1) | Total RAM<br>Bits | Embedded<br>Multipliers<br>(2) | PLLs | Supply<br>Voltage | Pin/Package Options (3)                                                 | Maximum<br>User I/O<br>Pins |

| EP2C5    | 4,608                      | 26                    | 119,808           | 13                             | 2    | 1.2 V             | 144-Pin TQFP (4), 208-Pin PQFP, 256-Pin FineLine BGA® (5)               | 89, 142                     |

| EP2C8    | 8,256                      | 36                    | 165,888           | 18                             | 2    | 1.2 V             | 144-Pin TQFP, 208-Pin PQFP, 256-Pin FineLine BGA                        | 85, 138, 182                |

| EP2C20   | 18,752                     | 52                    | 239,616           | 26                             | 4    | 1.2 V             | 208-Pin PQFP <i>(5) (6),</i> 256-Pin FineLine BGA, 484-Pin FineLine BGA | 152, 315                    |

| EP2C35   | 33,216                     | 105                   | 483,840           | 35                             | 4    | 1.2 V             | 484-Pin FineLine BGA, 672-Pin FineLine BGA                              | 322, 475                    |

| EP2C50   | 50,528                     | 129                   | 594,432           | 86                             | 4    | 1.2 V             | 484-Pin FineLine BGA, 672-Pin FineLine BGA                              | 294, 450                    |

| EP2C70   | 68,416                     | 250                   | 1,152,000         | 150                            | 4    | 1.2 V             | 672-Pin FineLine BGA, 896-pin FineLine BGA                              | 422, 622                    |

#### Notes to Table 1:

(1) Each RAM block has 4 Kbits and 512 parity bits.

(2) Total number of 18-bit × 18-bit multipliers. For the total number of 9-bit × 9-bit multipliers per device, multiply the total number of 18-bit × 18-bit multipliers by 2.

(3) Cyclone II devices support vertical migration within the same package.

(4) TQFP: thin quad flat pack.

(5) Contact your local Altera sales representative for more information.

(6) PQFP: plastic quad flat pack.

| Table 2. C | yclone Devi | ces                   |                   |      |                   |                                                          |                          |

|------------|-------------|-----------------------|-------------------|------|-------------------|----------------------------------------------------------|--------------------------|

| Device     | LEs         | M4K RAM<br>Blocks (1) | Total RAM<br>Bits | PLLs | Supply<br>Voltage | Pin/Package Options (2)                                  | Maximum<br>User I/O Pins |

| EP1C3      | 2,910       | 13                    | 59,904            | 1    | 1.5 V             | 100-Pin TQFP, 144-Pin TQFP                               | 65, 104                  |

| EP1C4      | 4,000       | 17                    | 78,336            | 2    | 1.5 V             | 324-Pin FineLine BGA, 400-Pin FineLine BGA               | 249, 301                 |

| EP1C6      | 5,980       | 20                    | 92,160            | 2    | 1.5 V             | 144-Pin TQFP, 240-Pin PQFP, 256-Pin FineLine BGA         | 98, 185, 185             |

| EP1C12     | 12,060      | 52                    | 239,616           | 2    | 1.5 V             | 240-Pin PQFP, 256-Pin FineLine BGA, 324-Pin FineLine BGA | 173, 185, 249            |

| EP1C20     | 20,060      | 64                    | 294,912           | 2    | 1.5 V             | 324-Pin FineLine BGA, 400-Pin FineLine BGA               | 233, 301                 |

#### Notes to Table 2:

(1) Each RAM block has 4 Kbits and 512 parity bits.

(2) Cyclone devices support vertical migration within the same package.

| Table 3. Sti | ratix II Devices                           | ;                     |                       |                      |                 |                   |               |                                |             |                   |                                                            |                             |

|--------------|--------------------------------------------|-----------------------|-----------------------|----------------------|-----------------|-------------------|---------------|--------------------------------|-------------|-------------------|------------------------------------------------------------|-----------------------------|

| Device       | Adaptive<br>Logic<br>Modules<br>(ALMs) (1) | Equivalent<br>LEs (1) | M512<br>RAM<br>Blocks | M4K<br>RAM<br>Blocks | M-RAM<br>Blocks | Total RAM<br>Bits | DSP<br>Blocks | Embedded<br>Multipliers<br>(2) | PLLs<br>(3) | Supply<br>Voltage | Pin/Package<br>Options (4)                                 | Maximum<br>User I/0<br>Pins |

| EP2S15       | 6,240                                      | 15,600                | 104                   | 78                   | 0               | 419,328           | 12            | 48                             | 6           | 1.2 V             | 484-Pin FBGA <i>(5)</i><br>672-Pin FBGA <i>(5)</i>         | 341<br>365                  |

| EP2S30       | 13,552                                     | 33,880                | 202                   | 144                  | 1               | 1,369,728         | 16            | 64                             | 6           | 1.2 V             | 484-Pin FBGA <i>(5)</i><br>672-Pin FBGA <i>(5)</i>         | 341<br>499                  |

| EP2S60       | 24,176                                     | 60,440                | 329                   | 255                  | 2               | 2,544,192         | 36            | 144                            | 12          | 1.2 V             | 484-Pin FBGA (5)<br>672-Pin FBGA (5)<br>1,020-Pin FBGA (5) | 341<br>499<br>717           |

| EP2S90       | 36,384                                     | 90,960                | 488                   | 408                  | 4               | 4,520,448         | 48            | 192                            | 12          | 1.2 V             | 1,020-Pin FBGA (5)<br>1,508-Pin FBGA (5)                   | 757<br>901                  |

| EP2S130      | 53,016                                     | 132,540               | 699                   | 609                  | 6               | 6,747,840         | 63            | 252                            | 12          | 1.2 V             | 1,020-Pin FBGA (5)<br>1,508-Pin FBGA (5)                   | 741<br>1,109                |

| EP2S180      | 71,760                                     | 179,400               | 930                   | 768                  | 9               | 9,383,040         | 96            | 484                            | 12          | 1.2 V             | 1,020-Pin FBGA <i>(5)</i><br>1,508-Pin FBGA <i>(5)</i>     | 741<br>1,173                |

#### Notes to Table 3:

(1) Each Stratix<sup>®</sup> II ALM is equivalent to 2.5, 4-input look-up table (LUT)-based LEs.

(2) Each DSP block supports four 18-bit × 18-bit multipliers.

(3) Includes enhanced and fast PLLs.

(4) Stratix II devices support vertical migration within the same package.

(5) FBGA: FineLine BGA.

continued on page 16

| Table 4. Stra | ntix Devices | Note (1)                                                           |                    |                   |                   |            |

|---------------|--------------|--------------------------------------------------------------------|--------------------|-------------------|-------------------|------------|

| Device        | LEs          | Pin/Package Options                                                | l/0 Pins           | Supply<br>Voltage | Total RAM<br>Bits | DSP Blocks |

| EP1S10        | 10,570       | 484-Pin BGA (2), 672-Pin BGA, 672-Pin BGA (2), 780-Pin BGA (2)     | 335, 345, 345, 426 | 1.5 V             | 920,448           | 6          |

| EP1S20        | 18,460       | 484-Pin BGA (2), 672-Pin BGA, 672-Pin BGA (2), 780-Pin BGA (2)     | 361, 426, 426, 586 | 1.5 V             | 1,669,248         | 10         |

| EP1S25        | 25,660       | 672-Pin BGA, 672-Pin BGA (2), 780-Pin BGA (2), 1,020-Pin BGA (2)   | 473, 473, 597, 706 | 1.5 V             | 1,944,576         | 10         |

| EP1S30        | 32,470       | 780-Pin BGA (2), 956-Pin BGA, 1,020-Pin BGA (2)                    | 589, 683, 726      | 1.5 V             | 3,317,184         | 12         |

| EP1S40        | 41,250       | 780-Pin BGA (2), 956-Pin BGA, 1,020-Pin BGA (2), 1,508-Pin BGA (2) | 615, 683, 773, 822 | 1.5 V             | 3,423,744         | 14         |

| EP1S60        | 57,120       | 956-Pin BGA, 1,020-Pin BGA (2), 1,508-Pin BGA (2)                  | 683, 773, 1,022    | 1.5 V             | 5,215,104         | 18         |

| EP1S80        | 79,040       | 956-Pin BGA, 1,020-Pin BGA (2), 1,508-Pin BGA (2)                  | 683, 773, 1,203    | 1.5 V             | 7,427,520         | 22         |

#### Notes to Table 4:

(1) The ordering code for Stratix devices is based on the number of LEs; therefore, gate count numbers are not included.

(2) Space-saving FineLine BGA package.

| Table 5. Strati | x GX Devices |                         |                                    |          |                   |           |                                |

|-----------------|--------------|-------------------------|------------------------------------|----------|-------------------|-----------|--------------------------------|

| Device          | LEs          | Transceiver<br>Channels | Pin/Package Options                | l/O Pins | Supply<br>Voltage | RAM Bits  | Source-Synchronous<br>Channels |

| EP1SGX10C       | 10,570       | 4                       | 672-Pin BGA <i>(1)</i>             | 330      | 1.5 V             | 920,488   | 22                             |

| EP1SGX10D       | 10,570       | 8                       | 672-Pin BGA (1)                    | 330      | 1.5 V             | 920,488   | 22                             |

| EP1SGX25C       | 25,660       | 4                       | 672-Pin BGA <i>(1)</i>             | 426      | 1.5 V             | 1,944,576 | 39                             |

| EP1SGX25D       | 25,660       | 8                       | 672-Pin BGA (1), 1,020-Pin BGA (1) | 426, 542 | 1.5 V             | 1,944,576 | 39                             |

| EP1SGX25F       | 25,660       | 16                      | 1,020-Pin BGA (1)                  | 542      | 1.5 V             | 1,944,576 | 39                             |

| EP1SGX40D       | 41,250       | 8                       | 1,020-Pin BGA (1)                  | 548      | 1.5 V             | 3,423,744 | 45                             |

| EP1SGX40G       | 41,250       | 20                      | 1,020-Pin BGA (1)                  | 548      | 1.5 V             | 3,423,744 | 45                             |

Note to Table 5:

(1) Space-saving FineLine BGA package.

#### MAX II Devices & PCI Compiler 3.2.0 Deliver Complete PCI Solutions

Altera's PCI Compiler has been used in over 1,000 FPGA-based PCI designs, and now it provides 32-bit, 33-MHz PCI IP support for the MAX<sup>®</sup> II CPLD device family. PCI Compiler version 3.2.0 IP cores support both bus mastering and targetonly MAX II PCI control path applications in very compact implementations, providing designers with ample logic and I/O resources for their value-add design components. The PCI/T32 target-only core is supported in both EPM1270 and EPM2210 devices; the PCI/MT32 master/target core is supported in EPM2210 devices. For a limited time, the PCI/T32 core is available to MAX II designers for the special price of \$1,995, a \$3,000 discount from the list price. The PCI/MT32 core is available for \$8,995. See your Altera sales representative for details.

| Table 6. MA) | K II CPLDs |                                  |                                         |                          |                     |                           |

|--------------|------------|----------------------------------|-----------------------------------------|--------------------------|---------------------|---------------------------|

| Device       | LEs        | Typical Equivalent<br>Macrocells | Pin/Package Options (1)                 | Maximum User I/O<br>Pins | Supply Voltage      | User Flash<br>Memory Bits |

| EPM240       | 240        | 192                              | 100-Pin TQFP                            | 80                       | 3.3 V, 2.5 V, 1.8 V | 8,192                     |

| EPM570       | 570        | 440                              | 100-Pin TQFP, 144-Pin TQFP, 256-Pin BGA | 76, 116, 160             | 3.3 V, 2.5 V, 1.8 V | 8,192                     |

| EPM1270      | 1,270      | 980                              | 144-Pin TQFP, 256-Pin BGA               | 116, 212                 | 3.3 V, 2.5 V, 1.8 V | 8,192                     |

| EPM2210      | 2,210      | 1,700                            | 256-Pin BGA, 324-Pin BGA                | 204, 272                 | 3.3 V, 2.5 V, 1.8 V | 8,192                     |

#### Note to Table 6:

(1) All BGA packages are 1.0-mm FineLine BGA packages.

| Table 7. MAX | Table 7. MAX 3000 CPLDs |                                                |               |                   |             |  |  |  |  |  |

|--------------|-------------------------|------------------------------------------------|---------------|-------------------|-------------|--|--|--|--|--|

| Device       | Macrocells              | Pin/Package Options                            | I/O Pins      | Supply<br>Voltage | Speed Grade |  |  |  |  |  |

| EPM3032A     | 32                      | 44-Pin Plastic J-Lead Chip Carrier (PLCC)/TQFP | 34            | 3.3 V             | -4, -7, -10 |  |  |  |  |  |

| EPM3064A     | 64                      | 44-Pin PLCC/TQFP, 100-Pin TQFP                 | 34, 66        | 3.3 V             | -4, -7, -10 |  |  |  |  |  |

| EPM3128A     | 128                     | 100-Pin TQFP, 144-Pin TQFP, 256-Pin BGA (1)    | 80, 96, 98    | 3.3 V             | -5, -7, -10 |  |  |  |  |  |

| EPM3256A     | 256                     | 144-Pin TQFP, 208-Pin PQFP, 256-Pin BGA (1)    | 116, 158, 161 | 3.3 V             | -7, -10     |  |  |  |  |  |

| EPM3512A     | 512                     | 208-Pin PQFP, 256-Pin BGA (1)                  | 172, 208      | 3.3 V             | -7, -10     |  |  |  |  |  |

Note to Table 7: (1) 1.0-mm pitch FineLine BGA package.

| Table 8. MAX 2 | 7000 CPLDs |                                                                                           | _                       |                   | _                |

|----------------|------------|-------------------------------------------------------------------------------------------|-------------------------|-------------------|------------------|

| Device         | Macrocells | Pin/Package Options                                                                       | I/O Pins                | Supply<br>Voltage | Speed Grade      |

| EPM7032S       | 32         | 44-Pin PLCC/TQFP                                                                          | 36                      | 5.0 V             | -5, -6, -7, -10  |

| EPM7032AE      | 32         | 44-Pin PLCC/TQFP                                                                          | 36                      | 3.3 V             | -4, -7, -10      |

| EPM7032B       | 32         | 44-Pin PLCC/TQFP, 49-Pin BGA <i>(2)</i>                                                   | 36, 36                  | 2.5 V             | -3, -5, -7       |

| EPM7064S       | 64         | 44-Pin PLCC/TQFP, 84-Pin PLCC, 100-Pin TQFP                                               | 36, 68, 68              | 5.0 V             | -5, -6, -7, -10  |

| EPM7064AE      | 64         | 44-Pin PLCC/TQFP, 100-Pin TQFP, 100-Pin BGA (1)                                           | 36, 68, 68              | 3.3 V             | -4, -7, -10      |

| EPM7064B       | 64         | 44-Pin TQFP, 49-Pin BGA (2), 100-Pin TQFP, 100-Pin BGA (1)                                | 36, 41, 68, 68          | 2.5 V             | -3, -5, -7       |

| EPM7128S       | 128        | 84-Pin PLCC, 100-Pin PQFP/TQFP, 160-Pin PQFP                                              | 68, 84, 100             | 5.0 V             | -6, -7, -10, -15 |

| EPM7128AE      | 128        | 84-Pin PLCC, 100-Pin TQFP, 100-Pin BGA (1), 144-Pin TQFP, 256-Pin BGA (1)                 | 68, 84, 84, 100, 100    | 3.3 V             | -5, -7, -10      |

| EPM7128B       | 128        | 100-Pin TQFP, 100-Pin BGA (1), 144-Pin TQFP, 256-Pin BGA (1)                              | 84, 84, 100, 100        | 2.5 V             | -4, -7, -10      |

| EPM7160S       | 160        | 84-Pin PLCC, 100-Pin TQFP, 160-Pin PQFP                                                   | 64, 84, 104             | 5.0 V             | -6, -7, -10      |

| EPM7192S       | 192        | 160-Pin PQFP                                                                              | 124                     | 5.0 V             | -7, -10, -15     |

| EPM7256S       | 256        | 208-Pin PQFP/RQFP                                                                         | 164                     | 5.0 V             | -7, -10, -15     |

| EPM7256AE      | 256        | 100-Pin TQFP, 100-Pin BGA (1), 144-Pin TQFP, 208-Pin PQFP, 256-Pin BGA (1)                | 84, 84, 120, 164, 164   | 3.3 V             | -5, -7, -10      |

| EPM7256B       | 256        | 100-Pin TQFP, 144-Pin TQFP, 169-Pin BGA (2), 208-Pin PQFP, 256-Pin BGA (1)                | 84, 120, 141, 164, 164  | 2.5 V             | -5, -7, -10      |

| EPM7512AE      | 512        | 144-Pin TQFP, 208-Pin PQFP, 256-Pin BGA <i>(1)</i> , 256-Pin BGA                          | 120, 176, 212, 212      | 3.3 V             | -7, -10, -12     |

| EPM7512B       | 512        | 144-Pin TQFP, 169-Pin BGA <i>(2)</i> , 208-Pin PQFP, 256-Pin BGA <i>(1)</i> , 256-Pin BGA | 120, 141, 176, 212, 212 | 2.5 V             | -5, -7, -10      |

#### Notes to Table 8:

1.0-mm pitch FineLine BGA package.

0.8-mm pitch Ultra FineLine BGA package.

| Table 9. ACEX | Devices |                                                              |                    |                   |       |          |

|---------------|---------|--------------------------------------------------------------|--------------------|-------------------|-------|----------|

| Device        | Gates   | Pin/Package Options                                          | I/O Pins           | Supply<br>Voltage | LEs   | RAM Bits |

| EP1K10        | 10,000  | 100-Pin TQFP, 144-Pin TQFP, 208-Pin PQFP, 256-Pin BGA (1)    | 66, 92, 120, 136   | 2.5 V             | 576   | 12,288   |