**Newsletter for Altera Customers**

# Design to Win

# Quartus II Software Version 4.2

- Performance Leadership

- Power Management

- System-Level Design

- Winning Partnerships

# 187 Designs Conclusively Validate Altera's Performance Advantage

Altera® devices lead the industry in performance, beating competing devices by 39% to 60%. Data supporting this performance advantage includes third-party benchmark and analysis data for 187 designs using methodology endorsed by industry experts including Kevin Morris, Editor of the FPGA and Programmable Logic Journal and Russell Tessier, Associate Professor of Electrical and Computer Engineering at the University of Massachusetts, Amherst. The results, based on 187 designs evaluated with a third-party, industry-expert-endorsed benchmarking methodology, shows that:

- Stratix<sup>®</sup> II devices outperform Virtex-4 devices by 39%

- Cyclone<sup>™</sup> and Cyclone II devices outperform Spartan-3 devices by 60%

Russell Tessier commented on the methodology. "To evaluate its FPGAs, Altera has created a benchmarking methodology which fairly considers the intricacies and optimizations of its competitors' tools and devices, as well as its own. Experiments which consider a variety of end-user operating conditions have been run on a suite of industrial benchmark circuits. The results of these experiments have been analyzed to accentuate experimental variations and to clearly identify result trends. I am convinced that the experimental methodology that has been used fairly characterizes appropriate user expectations for Altera's devices in terms of area utilization and speed versus their competitors."

According to Kevin Morris. "Altera has created an impressive methodology for measuring and monitoring key performance characteristics of theirs and competitors' devices and tools. Designing a fair and accurate test methodology that yields reasonable metrics is a daunting task...Their system includes a comprehensive and representative test suite, automatic compensation for technology and IP differences between various FPGA families, and automatic generation of design constraints to get optimal results from synthesis and layout tools."

You can experience this performance advantage yourself by downloading Altera's free Quartus® II Web Edition software today.

Results based on 77 designs targeting Stratix II and Virtex-4 FPGAs and 110 designs targeting Cyclone/Cyclone II and Spartan-3 FPGAs. Benchmark development tools include Synplicity's Synplify Pro 7.7, Altera's Quartus II, and Xilinx's ISE tools. For details, see Altera's FPGA Performance Benchmarking Methodology White Paper.

# If Performance Matters, There's Only One Solution

350 The 00 20 300 .....  $\bigcirc$ Zone O  $\bigcirc$ 250 Altera® FPGA Design f<sub>MAX</sub> (MHz)  $\bigcirc$  $\bigcirc$ 200 150 100 50 **Xilinx** 0 50 100 200 250 300 150 350 Xilinx<sup>®</sup> FPGA Design f<sub>MAX</sub> (MHz) O Stratix<sup>®</sup> II vs. Virtex-4<sup>™</sup> Cyclone<sup>™</sup>/Cyclone II vs. Spartan-3<sup>™</sup>

187 Designs Conclusively Validate Altera's Performance Advantage

# Don't Stay in the Dark—Get Into the Altera Zone

# www.altera.com/alterazone

77 Designs Target Stratix II & Virtex-4; 110 Designs Target Cyclone/Cyclone II & Spartan-3 FPGAs Benchmarking Methodology Endorsed by Third-Party Experts—See www.altera.com/alterazone for Details For Details on Methodology, See Altera's *FPGA Performance Benchmarking Methodology* White Paper

### The Programmable Solutions Company®

Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights.

Performance Leadership

Quartus II Expertise

**Power Analysis**

**Managing Editor Guy Spencer**

**Production Editor** John Panattoni

**Technical Editor** Justin Bennett

Design & Layout Paula Cruz

| 187 Designs Conclusively Validate Altera's Performance Advantage2                                                          |

|----------------------------------------------------------------------------------------------------------------------------|

| Quartus II Software Technology Leadership Delivers Highest FPGA &<br>CPLD Performance                                      |

| Quartus II Software Version 4.2—Performance Leadership & Advanced<br>Power Management                                      |

| Which Quartus II Software is Best for Me?                                                                                  |

| Learn How to Become a Quartus II Software Expert9                                                                          |

| Take Advantage of Free Quartus II On-Line Software Training9                                                               |

| FPGA Journal Awards Quartus II Tools Highest Marks in Reader &<br>Customer Satisfaction Survey10                           |

| Quartus II Development Software Handbook10                                                                                 |

| Low-Cost Programmable Logic Drives Innovation in Consumer Electronics11                                                    |

| Creating Hardware Accelerators for SOPC-Builder in C14                                                                     |

| Design Custom SOPC Builder Components & Streamline Integration16                                                           |

| A Comprehensive Management Process for High-Performance FPGA Design19                                                      |

| Improving Bit-Error-Rate Performance in Serial Digital Multi-Gigabit<br>Communication Systems With Error Correction Coding |

| Cyclone II FPGAs & Nios II Embedded Processor Offer Low-Cost<br>Performance Advantages                                     |

| Power Analysis for Efficient Power Planning                                                                                |

| Altera Development Kits                                                                                                    |

| Upcoming Events                                                                                                            |

101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 n\_v@altera.com www.altera.com

# Quartus II Software Technology Leadership Delivers Highest FPGA & CPLD Performance

The Quartus<sup>®</sup> II design software's technology leadership delivers the highest available performance for high-density FPGA designs, low-cost FPGA designs, and CPLD designs, as shown in Table 1. These metrics, which use a third-party, industry-expertendorsed benchmarking methodology, conclusively validate Altera's performance leadership for FPGA and CPLD designs.

# Software Development Methodology Helps Optimize Silicon

Traditional programmable logic device development techniques optimize silicon hardware architectures and then go back and develop software tool chains to support that architecture. Altera uses Quartus II software modeling tools and unique Altera-developed device modeling tools to experiment with thousands of device and software algorithm parameters. Using this information, Altera concurrently develops optimal silicon architectures and software support.

This process enabled Altera to develop Stratix II devices with a new and innovative logic structure that offers higher performance and higher density at a lower cost than comparable FPGAs. Because of the concurrent silicon and software development process, high-performance software support for Stratix II devices was available before silicon.

# FPGA Vendor-Integrated Physical Synthesis Technology

The Quartus II software includes the only integrated physical synthesis optimization technology available from an FPGA vendor. Quartus II physical synthesis options are applied during the fitting stage of the compilation process and can be applied regardless of the synthesis tool used.

# **Faster Timing Closure**

Quartus II software users can take advantage of powerful timing closure flow features to optimize designs beyond push-button results. Quartus II software's timing closure flow includes integrated physical synthesis tools and a rich set of graphical analysis and editing tools supported by unmatched cross-probing capabilities.

# Easy-to-Use Design Optimization Technology

The Quartus II software satisfies timing requirements using a push-button design flow for most designs. When you need to go beyond push-button results,

| Table 1. Quartus II Performance        | Leadership as Compa                            | red to Xilinx ISE | Note (1)       |

|----------------------------------------|------------------------------------------------|-------------------|----------------|

| Device Category                        | Device Comparison                              | Winner            | Winning Margin |

| High-Density FPGA<br>(90 nm, Estimate) | Stratix <sup>®</sup> II vs. Xilinx<br>Virtex-4 | Quartus II        | 39%            |

| Low-Cost FPGA (90 and 130 nm)          | Cyclone <sup>™</sup> II vs.<br>Spartan-3       | Quartus II        | 60%            |

| CPLD                                   | MAX <sup>®</sup> II vs.<br>CoolRunner-2        | Quartus II        | 50%            |

### Note to Table 1:

(1) The *Programmable Logic Performance Leadership* section of the Altera web site includes technical details, timing analysis techniques, and exact benchmarking methods.

The Quartus II software now includes exclusive tools to make design optimization simple:

- Design space explorer (DSE) uses automated technology to increase average register-toregister f<sub>MAX</sub> design performance by 21 percent.

- The timing optimization advisor tool gives you a virtual field application engineer inside the Quartus II software, providing specific advice on optimizing design timing performance based on the current design project settings and assignments.

# Maintain Performance When Implementing Late-Arriving Design Changes

A traditional problem with programmable logic design software has been maintaining performance as later design changes are introduced. However, the Quartus II software makes it easy to implement latearriving design changes. New fine-grained incremental design editing and compilation technologies give designers the best support for post-place-and-route design changes. These technologies include:

- Quartus II Chip Editor

- Ability to lock down placement and routing in LogicLock<sup>™</sup> regions

# Parallel Development for FPGAs & Structured ASICs

Only the Quartus II software provides seamless migration between FPGA design and structured ASIC design. By enabling compilation for HardCopy® Stratix devices, the Quartus II software provides a path to higher performance and lower device costs. HardCopy Stratix structured ASICs further strengthen the Stratix device family's 130-nm performance leadership by offering an average of 50 percent higher performance than Virtex-II Pro FPGAs.

# Quartus II Software Version 4.2–Performance Leadership & Advanced Power Management

The Quartus<sup>®</sup> II software version 4.2 demonstrates leadership in performance and power management. New benchmarks demonstrate that Altera delivers clear, complete performance superiority across all 90-nm FPGAs, as well as CPLDs. The Quartus II software's new PowerPlay power analysis and optimization technology as well as a wide range of new features enhance Quartus II software's technology leadership position.

In recognition of software technology leadership, *FPGA Journal* recently gave the Quartus II software its *Highest Reader/Customer Satisfaction With an FPGA Vendor's Tools* award.

The Quartus II software delivers the highest performance for high-density FPGA, low-cost FPGA, and CPLD design segments. Recent benchmarks show that the Quartus II software version 4.2 delivers an average of 39 percent higher performance than when the same design is compiled with Xilinx ISE software for Virtex-4 devices. See the Quartus II performance leadership article on page 5 for more information.

# PowerPlay Technology: Power Analysis & Optimization

Quartus II PowerPlay technology is designed to enable designers to accurately analyze and optimize both dynamic and static power consumption. Quartus II software version 4.2 includes the PowerPlay power analysis features that produce detailed reports. Users can use these reports to optimize thermal power dissipation on a block-type or design-hierarchy basis. An industry first, automated Quartus II PowerPlay optimization features will be introduced in 2005.

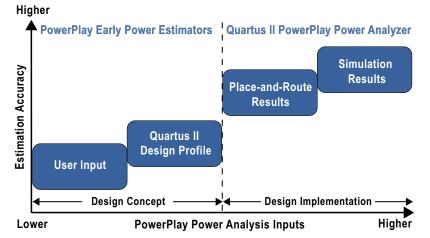

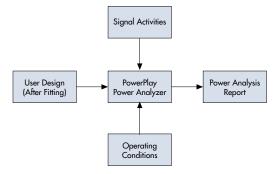

# Figure 1. PowerPlay Power Analysis

# Power Analysis From Design Concept Through Implementation

The new PowerPlay power analysis tools in the Quartus II software version 4.2 give designers the ability to estimate power consumption from early design concept through design implementation, as shown in Figure 1.

# **PowerPlay Early Power Estimators**

Designers can use the PowerPlay Early Power Estimator spreadsheets to estimate static and dynamic power consumption during the design concept stage. Early Power Estimation spreadsheets can be filled out manually or populated directly from the Quartus II software. Power estimations are refined during design implementation using the new Quartus II PowerPlay Power Analyzer feature.

# **PowerPlay Power Analyzer**

The Quartus II software now includes the PowerPlay Power Analyzer feature. This feature improves the accuracy of power consumption estimations given by the Early Power Estimator spreadsheets by:

- Accounting for device resource usage and placeand-route results

- Accounting for functional and timing simulation input/output stimuli

- Performing statistical analysis of expected design-node activity rates when simulation vector inputs are not available

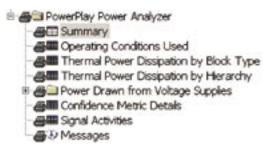

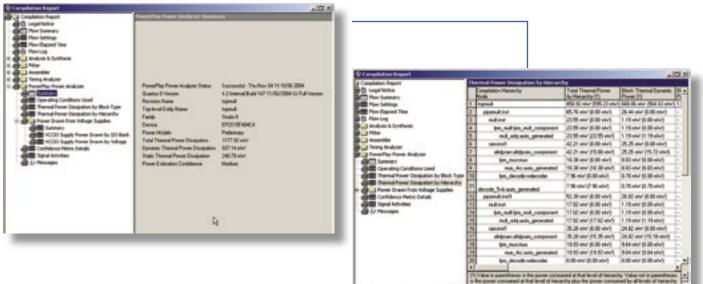

The Quartus II PowerPlay Power Analyzer produces detailed reports that can pinpoint which device structures, and even design hierarchy blocks, are dissipating the most thermal power. Figure 2 lists the PowerPlay Power Analyzer reports available. Quartus II users can now use these reports to optimize designs for lower power consumption.

# Figure 2. PowerPlay Power Analyzer Report Tabs

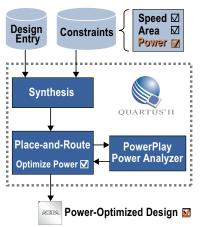

### **Push-Button Power Optimization**

Up to this point, FPGA and CPLD design tools can optimize designs for performance and area utilization automatically, but still leave power management largely to the designer. In 2005, push-button PowerPlay power optimization technology will be included in Quartus II software releases. PowerPlay power optimization technology will help you optimize power consumption in addition to speed and area constraints in FPGA, CPLD, and structured ASIC designs, as shown in Figure 3.

### Figure 3. PowerPlay Power Optimization Design Flow

The combination of Quartus II PowerPlay power analysis and optimization technology, Altera's advanced silicon design techniques, and partnerships with leading power management component suppliers gives Quartus II software users an edge in delivering high-performance, power-optimized designs on 90-nm and smaller process technologies.

## **Ease-of-Use & Productivity**

Version 4.2 adds several new features that improve ease-of-use and increase productivity:

- New Versions of Altera MegaCore® Functions: Altera subscriptions include the MegaCore intellectual property (IP) Library CD and the Nios® II embedded processor, evaluation edition, CD. These CDs allow you to evaluate all of Altera's MegaCore design-ready IP functions in hardware before purchasing a license for the IP.

- Early Timing Estimate Fitter Option: This feature provides very quick estimates of design performance without performing a full place-and-route. Estimates are within 10-15 percent of final timing results with about 5-6× less fitter time. The time savings go up more dramatically for larger designs, up to 20× on some of the largest Stratix<sup>®</sup> II and Stratix designs.

- *Soft LVDS Megafunction*: Simplifies implementing LVDS communication with Cyclone<sup>™</sup> II and Cyclone devices.

- Incremental Synthesis and 20 Percent Faster Run-Times for Quartus II Integrated Synthesis): Incremental synthesis provides designers more control over design changes and improves synthesis run-times. Other enhancements to the Quartus II integrated synthesis feature shorten average run-times by 20 percent even when not using the incremental synthesis feature.

## **SOPC Builder**

SOPC Builder is exclusive technology included in the Quartus II software to automate system integration and generation. The following new features are added to the Quartus II software version 4.2 release.

- Clock Domain Crossing Circuitry: SOPC Builder can now automatically add specialized circuitry to support transactions between peripherals operating on different clock domains.

- Component Editor: New feature to better support integrating customer user logic into SOPC Builder systems.

## Verification

New verification features allow Quartus II software users to analyze and control clock skew, model clock jitter, and enable better analysis and optimization of control signals. Beginning with version 4.2, the Quartus II software also supports new register transfer level (RTL)-to-gates functional equivalency checking with the Cadence Conformal LEC formal verification software. This is in addition to the Gatesto-Gates Conformal LEC checking supported by earlier Quartus II software releases.

### **OS Support**

The Quartus II software version 4.2 is now officially supported on Microsoft Windows XP SP2 and Sun Microsystems Solaris 9. The Quartus II software continues to be supported on Windows XP, Windows 2000, Windows NT 4.0, Solaris 8, Red Hat Linux 7.3, 8.0, and Enterprise WS 3.0, and HP-UX 11.0.

# Expanding Quartus II Device Support

The Quartus II software version 4.2 adds programming support for EPCS64 configuration devices and adds pin-out support for Cyclone II devices.

# Start Using the Quartus II Software Version 4.2 Today

All customers with active software subscriptions will automatically be sent the Quartus II software version 4.2 in December. Quartus II Web Edition software version 4.2 is available for downloading from the Altera® web site now at **www.altera.com**.

# Which Quartus II Software is Best for Me?

The free Quartus II Web Edition software includes most of the features included in the Quartus II software subscription and everything needed to design for Altera's latest CPLD and low-cost FPGA families. The Quartus II Web Edition software also includes support for entry-level members of Altera's high-density FPGA families.

In addition to Quartus II Web Edition features, Quartus II subscription software offers:

- Support for all Altera high-density FPGAs

- Support for the HardCopy® series of structured ASIC devices

- ModelSim®-Altera simulation software

- Additional productivity features

- Support on Linux, Solaris, and HP-UX operating systems in addition to PC versions

For a complete comparison, visit the Altera web site and click on the comparison link on the Quartus II Web Edition page.

Features

# Learn How to Become a Quartus II Software Expert

The Quartus<sup>®</sup> II software features unique advantages in design flow methodology support, place-and-route technology, timing closure methodology, and in-system verification technology. Furthermore, Quartus II software is the only tool that supports FPGA, CPLD, and structured ASIC designs.

Altera provides the resources to get up and running quickly as well as help on how to utilize the Quartus II software's technology advantages to get the most out of your designs in the shortest time possible. Table 1 shows some of the many resources available for designers of varying knowledge levels of the Quartus II software.

Table 2 lists resources to become an expert using Quartus II LogicLock<sup>™</sup> block-based design methodology to shorten your design cycles.

Resources for all of the Quartus II software features are available to familiarize designers of all levels, and allows experienced designers to take full advantage of these features to maximize their design performance and minimize their design cycles.

| Table 1. General Quartus II Resour | ces                                                                       |            |

|------------------------------------|---------------------------------------------------------------------------|------------|

| Resource                           | Location                                                                  | Experience |

| Quartus II Online Demonstrations   | www.altera.com/quartusdemos                                               | Beginner   |

| Altera Design Software Web Page    | www.altera.com/products/softare/products/quartus2web/sof-quarwebmain.html |            |

| Quartus II Tutorials               | Choose Tutorial (Help Menu)                                               |            |

| Introduction to Quartus II Manual  | www.altera.com/literature/manual/intro_to_quartus2.pdf                    |            |

| Quartus II Handbook                | www.altera.com/literature/lit-qts.jsp                                     |            |

| Altera Technical Training          | https://buy.altera.com/etraining/etraining.asp                            |            |

| Altera Net Seminars                | www.altera.com/education/net_seminars/ns-index.html                       | Expert     |

| Table 2. Resources for Gaining Exp                                                                                     | ertise in the Quartus II LogicLock Block-Based Design Methodology                              |            |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|

| Resource                                                                                                               | Location                                                                                       | Experience |

| Quartus II Demonstrations                                                                                              | www.altera.com/education/demonstrations/online/design-software/flows/<br>onl-design-flows.html | Beginner   |

| LogicLock Block-Based Designs                                                                                          | www.altera.com/products/software/products/quartus2/design/qts-logiclock.html                   |            |

| Quartus II LogicLock Tutorial                                                                                          | Choose Tutorial (Help Menu)                                                                    |            |

| Introduction to Quartus II Manual<br>(Chapter 6)                                                                       | www.altera.com/literature/manual/intro_to_quartus2.pdf                                         |            |

| Quartus II Handbook (Chapter 1,<br>Volume 1)                                                                           | www.altera.com/literature/hb/qts/qts_qii51001.pdf                                              |            |

| Using Quartus II: LogicLock Regions<br>Training Course                                                                 | https://buy.altera.com/etraining/etraining.asp                                                 |            |

| Hierarchical Design & New ECO<br>Flows Simplify High-Density FPGA<br>Design Net Seminar (Archived)                     | www.altera.com/education/net_seminars/past/ns-hi_design.html                                   |            |

| Using Third-Party Synthesis<br>Software with the LogicLock Design<br>Methodology (Section III, Quartus II<br>Handbook) | www.altera.com/literature/lit-qts.jsp                                                          | Expert     |

# Take Advantage of Free Quartus II On-Line Software Training

A new series of in-depth on-line trainings teach you to take advantage of the latest Quartus II software features. Topics include power analysis, command line operation and tool command language (Tcl) scripting, and timing analysis. Visit the training section of the Altera web site to access the free training sessions at **mysupport.altera.com/etraining**.

# UNARTUS'II Po OUARTUS'II Po Pader's Choice

# FPGA Journal Awards Quartus II Tools Highest Marks in Reader & Customer Satisfaction Survey

Continuing its history of innovation, Altera has been awarded the highest marks from *FPGA Journal* for its Quartus<sup>®</sup> II software. This award, which is based on reader feedback, measures customer satisfaction with the quality, performance, and feature set of software tools.

*FPGA Journal* described the results: "You told us that Altera has made great strides in its tool suite over the past two years, particularly with the performance and quality of the Quartus II place-and-route tools. They (Altera) also got high marks from many for SOPC Builder embedded system tools working with their Nios<sup>®</sup> embedded processor." This award reflects Altera's commitment to customers and to making its products easy to use while ensuring the highest performance and using the most advanced technology. Altera listens to customers throughout the product development cycle, which is largely driven by customer feedback. By delving into customer design needs and experiences, Altera identifies critical customer issues and then funnels that knowledge back into software engineering to deliver the products customers are looking for.

The results measuring customer satisfaction are based on formal reader surveys *FPGA Journal* conducted throughout the year on choosing devices, tools, and vendors for FPGA projects. The data for the results came from engineers who completed FPGA projects within the past year.

# **Quartus II Development Software Handbook**

The three-volume Quartus II Version 4.2 Handbook guides you through the programmable logic design cycle from design to verification. It details the benefits of using various features of the Quartus II software, and when and where each feature is best applied in the design cycle. This handbook also covers third-party EDA vendor tool interfaces in appropriate sections. Go to the Altera® web site at **www.altera.com/literature/lit-qts.jsp** to download the entire handbook, or any constituent volume, section, or chapter. For a general introduction to features and design flow in the Quartus software, see the Introduction to Quartus II Manual.

You can order your own hard copy of the Quartus II Development Software Handbook by clicking the Buy Now icon on **www.altera.com/literature/lit-qts.jsp**.

# Low-Cost Programmable Logic Drives Innovation in Consumer Electronics

### by Bernd Riemann Director of Hardware Engineering Pinnacle Systems, Inc.

The current state of the consumer electronics (CE) market is forcing product developers to re-evaluate their existing development models. The traditional methods of relying on ASSPs or custom ASICs to achieve the lowest cost are proving inadequate to the demands for rapid innovation and increased product differentiation. Instead, CE product developers are increasingly turning to programmable logic-based solutions to enable them to respond to rapidly changing needs of consumers and deliver new features and capabilities, a trend that has been encouraged by the recent proliferation of low-cost FPGA offerings.

Successful products in the CE market will quickly face a flood of competitive products from a variety of manufacturers. This swift reaction causes rapid price erosion and frustrates CE product developers' attempts to derive significant revenue from their products during their increasingly shorter life cycles. In addition, the rise in popularity of digital media formats for audio and video (A/V) content has resulted in a growing interest in appliances and methods to deliver this content to consumers. However, consumers have varying degrees of investment in analog and legacy A/V equipment, which CE product developers must take into account. The result is that the CE developers appear to have a great opportunity before them, but the exact nature, capabilities, and price points of the products that will be successful in this area are not well understood.

These conditions require greater flexibility and agility in product development than are provided by ASSPs and ASICs. CE product developers often use ASSPs for a wide variety of functions, including A/V encoding/ decoding, connection interfaces, format translations, and conversions. However, relying on ASSPs exclusively does not allow developers to significantly differentiate their products from others. Also, ASSPs are seldom available for the most current functions, and as a result, CE developers often turn to custom ASICs to deliver their intellectual property (IP) to their customers and differentiate their products.

ASICs also have the advantage of providing very low per-component prices, but unfortunately, the long development times that they require run counter to the need to innovate and quickly offer distinguishing features in markets that are saturated with similar products or that are otherwise changing. The high non-recurring engineering costs needed for custom ASICs are also a significant barrier for developers who either cannot make such investments or who are unwilling to take such a financial risk in a market where the requirements for a successful product are still in flux. As a result, CE developers are coming to the realization that programmable logic-based solutions, which enable rapid, flexible development and additional product innovation with a minimum of additional engineering resources, are increasingly desirable for their products.

Low-cost programmable logic devices (PLDs) are currently being employed in a wide variety of CE products, including digital televisions, DVD players, handheld media players, set-top boxes, "smart home" networks, and computer peripherals. The flexibility of a low-cost PLD can serve the CE product developer in a variety of ways. CE product manufacturers who incorporate programmable logic into the right areas in their products can rapidly develop new features simply by modifying the PLD design. This capability enables them to offer multiple versions of the same product at introduction, affords them the option to develop new products in response to changing market demands with a minimum of additional engineering effort, as well as provide upgrades to existing products in the field. In this way, CE product developers can take advantage of low-cost ASSPs for well-established functions, while relying on programmable logic to deliver the differentiating capabilities of their product. These differentiating capabilities can include features such as video or audio enhancements, security functions, user-programmable functions, or even completely different modes of operation.

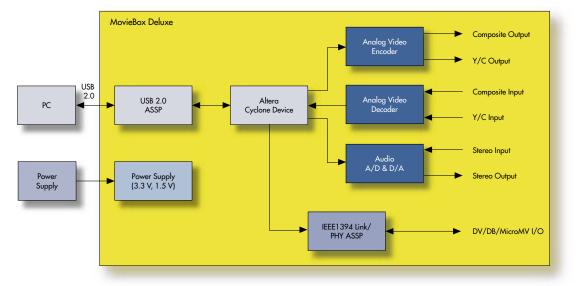

An example of this kind of innovation is the Studio MovieBox Deluxe from Pinnacle Systems. The MovieBox Deluxe is a device that allows multiple video formats from both analog and digital sources to be imported into a PC for editing with Pinnacle Studio 9 software. Many consumers have video content stored on analog tapes, and others have content stored in digital video (DV) format using a devicesuch as a DV camcorder-that includes a IEEE 1394 (or FireWire) interface, but they do not have an IEEE 1394 interface on their PC. The MovieBox Deluxe can connect all of these disparate types of video sources to a PC using a universal serial bus (USB) 2.0 interface. After editing, the MovieBox Deluxe can provide the connection between the PC and a TV, VCR, or digital camcorder for movie playback and/or storage.

**Company:** Pinnacle Systems, Inc.

**Industry:** Digital Video Solutions

Altera Products: Cyclone<sup>™</sup> FPGAs Pinnacle's MovieBox Deluxe includes several interfaces, including RCA and S-video inputs and outputs for analog devices, as well as IEEE 1394 for digital devices. These are all interfaced to the PC via the unit's USB 2.0 connection, and ASSPs are inside the MovieBox Deluxe to handle these interfaces. A single Cyclone FPGA handles the interaction between these ASSPs. Figure 1 shows a block diagram of the MovieBox Deluxe design.

The MovieBox Deluxe operates in one of a limited number of modes, depending on which video source is being used. Because the device only needs to operate in one of these modes at any given time, Pinnacle decided to leverage the FPGA reconfigurability such that the design configures the Cyclone device to function only in the required mode, depending on which cables are connected to the appliance. The time required to reconfigure the FPGA, which happens on the order of milliseconds, is undetectable by the user, compared to the time it takes to plug the cables into the MovieBox Deluxe. The resulting FPGA design uses far fewer logic resources (nearly one-third the amount) than it would have if Pinnacle had used a non-reconfigurable device. Pinnacle was able to use the smallest Cyclone FPGA, the cost of which was only about one-fifth of the total bill of materials, and well within their budget.

To further reduce costs, the Pinnacle engineering team decided to host the configuration files for the FPGA in the PC device driver for the MovieBox Deluxe. This scheme eliminated the need to include configuration memory devices in the MovieBox Deluxe hardware itself, reducing board space, device count, and corresponding costs. By taking advantage of FPGA reconfigurability in these innovative ways, Pinnacle kept their manufacturing costs to a minimum. Pinnacle's comprehensive evaluation of the alternatives revealed that no other device solution would have enabled them to achieve either their cost targets or meet their aggressive development schedule better than their Cylone FPGA-based design.

Figure 1. Pinnacle's MovieBox Deluxe

Pinnacle's MovieBox Deluxe automatically reconfigures the integrated Cyclone FPGA to operate only in the required mode, reducing logic utilization and lowering costs.

# Introducing Nios II.

Nios II

# The world's most versatile processor!

# **Nios**<sup>•</sup>II The ultimate in design flexibility.

The world's most popular soft-core processor just got better! Altera introduces the Nios<sup>®</sup> II family of embedded processors, featuring three CPU cores offering unprecedented performance and cost options. With Nios II processors, designers can define the exact features, performance, and cost they need in Altera's high-performance Stratix<sup>®</sup> series, low-cost Cyclone<sup>™</sup> series, and HardCopy<sup>®</sup> device families.

The Nios II development kits provide a complete, easy to use tool set including the new Nios II integrated development environment to accelerate software design. Try the Nios II processor today and experience the ultimate in design flexibility.

- Over 200 DMIPs performance

- Consumes as little as \$0.35 of logic

- Supports multi-processor systems

- Library of over 60 programmable peripherals

- Industry's most complete development kits

- Royalty-free & obsolescence-proof

The Programmable Solutions Company®

www.altera.com/nios2

Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. AD-NIOSII-1.0

# Leading through innovation.

# Creating Hardware Accelerators for SOPC-Builder in C

by David Pellerin CTO Impulse Accelerated Technologies, Inc. & Ralph Bodenner Senior Engineer Arboreal Design

By compiling from C to hardware, embedded systems designers can create hardware accelerators and connect them to other components in an FPGA-based system without the need to write low-level hardware description language (HDL) code. The combination of Impulse CoDeveloper and SOPC Builder makes this possible, and allows designers to use the Avalon<sup>™</sup> interface for hardware/software communication. For example, the designer of an imaging application can:

- Describe a streaming image filter (e.g., for edge detection, color conversion, etc.) in C

- Debug the code using Visual Studio, GDB, or another standard environment

- Accelerate the code by increasing system-level parallelism (multiple processes operating simultaneously) and by using automated compiler optimizations (e.g., loop unrolling)

- Automatically generate equivalent hardware and integrate it with the rest of the system via SOPC Builder and the Avalon interface

Using this approach, algorithm accelerations in excess of 300× over processor-based equivalent algorithms have been demonstrated.

# **Hardware Acceleration**

Accelerating software algorithms involves partitioning the application, perhaps multiple times, to find a balance between hardware resources, hardware/ software bandwidth limitations, and overall system performance. At its simplest, acceleration may mean replacing a single software-critical function with a functionally equivalent hardware module that takes advantage of the low-level parallelism inherent in hardware structures. Greater acceleration levels may be achieved through a multi-process approach, in which data streaming and system-level pipelines have a more important role. The latter approach (which is normally combined with the first) represents a communicating process programming model. Three elements make this programming model particularly effective for system-on-a-programmable-chip (SOPC) designs:

- Independently synchronized processes allow the programmer to create localized units of highspeed computation

- Streams provide a unifying model for highbandwidth, and low-latency communication between independently synchronized processes (either hardware or software)

- Signals allow processes to synchronize and coordinate their use of external resources, including shared memory resources

Interfacing to such a hardware-accelerated module is similar to calling a software function, the only difference being that the function now resides in hardware as a persistent object (which typically operates on a stream of data or via direct memory access) and is orders of magnitude faster than an equivalent processor-based function.

# **Optimization for Performance**

To squeeze out the highest possible performance, it is best to evaluate a given application as a whole and find higher levels of parallelism (system-level parallelism), as well as focus on more fine-grained parallelism with a given function or process. For this purpose, it helps to use a programming model that will allow an application to be described, simulated, and compiled to hardware or software targets as a collection of independent processes. Once partitioned in this way, it is relatively easy to experiment with moving some or all of the processes into hardware. Using such a programming model makes it possible to describe applications that are by nature parallel, and makes hardware/software partitioning easier. At the level of individual processes (which are analogous to subroutines in C), the types of parallelism that can be automated by software include:

- Instruction-level parallelism, in which one or more statements of untimed C code are collapsed into a single clock cycle

- Pipelining, which generates higher effective throughputs for many types of repetitive operations

- Loop unrolling, which generates parallel structures for repetitive operations (e.g., array computations)

# **Image Filter Example**

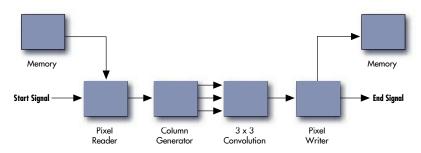

Opportunities for accelerating image filters via parallelism exist both at the system level and at the level of statements with individual processes. To create an edge-detection filter, for example, *n*-by-*n* windows of pixel data must be assembled from an input data stream and processed to create an output stream. Two pipelined hardware processes can be described in C for this function: one process generates three offset rows of pixels from the source image, and a second process accepts results of the first and apply a convolution to each pixel window, resulting in a single stream of convoluted pixels appearing on the output of the second process. The processes and streams can be declared and read/written using C-compatible stream I/O routines provided in the Impulse C<sup>TM</sup> libraries. If the image filter is to process pixel data directly from an image buffer, additional pipelined processes may be created at the front and back of the filter to read and write the pixel data, respectively, as shown in Figure 1.

This algorithm has been described in ANSI C with the addition of Impulse C library calls to set up and manage the processes, signals, and streams. A software test application has also been developed using Microsoft Visual Studio that exercises the image algorithm in a desktop simulation environment. This test application combines the four hardware processes associated with the image convolution function along with a software test bench application that reads data from a TIFF format file for processing (this software test bench application can be compiled and run as either the PCbased desktop application or as an embedded application running on the Nios® II embedded processor). This test was set up and run using standard desktop debugging tools and the CoDeveloper Application Monitor. In this way, the algorithm results could be verified before going to the next step and compiling for the target FPGA platform.

### **Compiling to Hardware**

After simulating the functionality of the image filter in software, we were ready to implement the application on a mixed FPGA/processor for actual hardware testing, using an embedded processor as a test generator. The Altera® Nios II development kit includes all the hardware and software needed to compile and synthesize hardware and software applications, which in this case consists of the automatically generated HDL source files representing the hardware processes, and the C source files representing the software test process that will run on the Nios II processor.

To generate hardware for the image filter, Impulse selected the Altera Nios II Platform Support Package from within the CoDeveloper tools and processed the relevant Impulse C source files. This generated approximately 1,200 lines of register transfer level (RTL) code and related SOPC Builder hardware/ software interface source files.

Figure 1. Four Pipelined Hardware Processes Used to Assemble & Process Streams of Pixel Data

Next, a project was created using the Altera SOPC Builder tools. As part of this process, a Nios II processor core was generated that included the necessary peripherals for testing. The generated hardware and software files were exported from CoDeveloper to the newly-created SOPC Builder project. Then, using the Altera block diagram tools Impulse connected the generated hardware processes to the Nios II processor via the Avalon<sup>™</sup> interface.

The complete system, including the Nios II processor and the generated image filter hardware were synthesized using Quartus® II software. The software portions of the application (consisting primarily of the test producer and consumer functions, including the main function) were also imported into the Nios II development environment and compiled using the supplied Nios II compiler. Lastly, a bit file was generated using the Quartus II software and downloaded to the platform via the provided parallel port interface cable, where it came up and ran as expected. In this example, the explicit pipelining of the four image filter processes, combined with automatically generated pipelines generated by the CoDeveloper hardware compiler, resulted in a best-case image processing rate of one pixel for every two FPGA clock cycles, which translates to a processing speed of approximately 10 ms for a full 512-by-512 image.

Impulse CoDeveloper is compatible with Visual Studio, GCC, CodeWarrior, and Eclipse. CoDeveloper is compatible with Quartus II and Synplify software. Full-featured CoDeveloper begins at \$2,000 (annual license, Altera only). Contact **info@ImpulseC.com** today for a free evaluation license or visit **www.ImpulseC.com**.

# Design Custom SOPC Builder Components & Streamline Integration

by Chris Sullivan Director, Strategic Alliances Celoxica

Efficiently designing and integrating algorithms into a system FPGA presents designers with interesting challenges. Intellectual property (IP) reuse using Altera's SOPC Builder tool goes a long way toward addressing these challenges, but the issue of custom IP generation and its integration into the system remains. Hence the question, how can designers take a custom algorithm, create a unique SOPC Builder component, and eliminate the integration effort? The answer lies in Celoxica's DKAccelerator design tool for systemon-a-programmable-chip (SOPC) development.

DKAccelerator allows you to create unique SOPC Builder components from algorithms already described in C. Without additional coding, they are automatically integrated into the design as library components. These could be specialized digital signal processing (DSP) functions, components on the local side of peripheral component interconnect (PCI), or other software algorithms and custom instructions that would benefit from acceleration in hardware. To illustrate this process, this article presents a straightforward 3D digital image and video processing design example.

# **Design Process Overview**

Because DKAccelerator was expressly built for Altera's SOPC Builder tool, the design process is driven using the familiar SOPC Builder methodology.

Figure 1. Celoxica's Custom Designed Application

DKAccelerator augments the SOPC Builder flow, and is used for the generation and automatic integration of custom components that are not already available in the SOPC Builder library. DKAccelerator handles the detail of the Avalon<sup>™</sup> interface and SOPC Builder integration, meaning to concentrate your effort on the functionality of the custom component. The following steps apply to each new component based on an existing or custom designed C algorithm:

- 1. Define the required external (non-Avalon interface/custom instruction) I/O signals.

- 2. Describe the desired functionality (e.g., from existing C software code or a C implementation of a higher-level algorithm).

- 3. Define the register map for the address space of the component.

- 4. Implement the desired register map behavior.

# Design Example: Digital Image & Video Processing

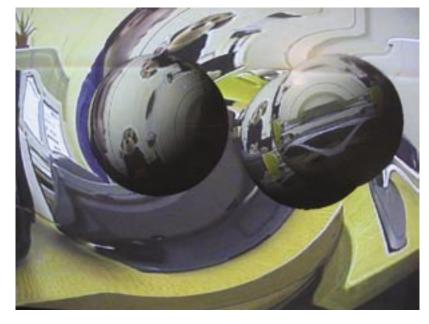

In this design example (summarily discussed on pages 26 and 27 of the third quarter 2004 issue of *News & Views*), the custom-designed application consists of three dynamically rendered and textured spheres that move across the screen (see Figure 1), bouncing off any edges they touch. Each sphere has a set of control registers that define the following properties:

- Angular velocity (DTheta[10..0])

- Linear velocity components

- (VX[3..0], VY[3..0])

- Surface color components (R, G, B)

From the SOPC Builder library, Celoxica used a general-purpose I/O pins, UART, on-chip memory, and a Nios<sup>®</sup> II processor. To complete the design, Celoxica then followed its four-step design process.

# Define External I/O Signals

The output signals are VGA display signals (R, G, B, VSync, HSync, etc.). The signals are exported using the following code:

unsigned 8 vgaR; ExportSOPCSignal(r, vgaR);

This code produces an 8-bit wide bus to carry red intensity information. vgaR can be used throughout the design as any variable would be used in C. For example: vgaR = 0xff; would produce full-intensity red.

# Describe the Desired Functionality

With system integration into the system automated by DKAccelerator, you can concentrate on describing the functionality of the component. Throughout the design phase, development remains at the C level of design abstraction by using DKAccelerator's systemlevel design capabilities. DKAccelerator uses C algorithms augmented with hardware constructs to create efficient hardware implementations. For example, the par statement inserted into the code allows true concurrency in a design, with par block assignments being executed in parallel (Figure 2). The chan statement (Channels) is used to communicate between and synchronize parallel processes.

This design example requires complex rendering, which uses a series of real-time rendered 3D Perlin noise functions, Phong shading, and lighting effects, all combined with axial rotations and linear translations.

The image is generated as follows:

1. In parallel, the functions

X = ScanX - SphereX; Y = ScanY - SphereY; $R^2 = X^2 + Y^2$

are calculated for each sphere. This allows the determination of whether the current scan position is within each sphere (i.e., is  $R^2 \ge SphereR^2$ ).

2. For the active sphere, the value Z is calculated

### Figure 2. Executing Sequential Code in Parallel

Software Implementation

from square root (Sphere  $\mathbb{R}^2 - \mathbb{R}^2$ ). The square root is pipelined. This gives a Cartesian point (X, Y, Z) on the surface of the rotated sphere.

- This point is inverse rotated through two axes by angles Phi and Theta (different for each sphere). Sine and Cosine are calculated through a fixed look-up table (LUT). This gives a Cartesian point (X, Y, Z) on the surface of the unrotated sphere.

- 4. This point is then passed into a series of 3D Perlin noise functions with different spatial frequencies. See **www.noisemachine.com**. These values are summed together to give a texture value for the current pixel.

- The normal surface of the sphere at a given 5. point is equal to (X/R, Y/R, Z/R). As the spheres are a fixed-power-of-two size, this calculation is trivial. By computing the dot-product with a fixed vector and adding a small ambient light value, the diffuse lighting value of the current pixel can be calculated. Multiplying this with the texture value gives the underlying shade of the current pixel. The specular component of the lighting is computed with a further dot-product and lookup in a table providing a Phong shading model. The diffuse and specular components are added together and the result is saturated. This gives the final output value for each pixel that lies on a sphere.

- 6. The spheres are moved by their current velocity. If the spheres impinge on the edge of the screen, a new velocity and rotational speed is randomly generated.

### continued on page 18

### Hardware Implementation

| <pre>void gen_table (void) /* build the crc table */ {     unsigned long crc, poly;     int i, j;     poly = 0xEDB88320L;     for (i = 0; i &lt; 256; i ++) {         crc = i;         for (j = 8; j &gt; 0; j) {             if (crc &amp; 1)                 crc = (crc &gt;&gt; 1) ^ poly;         else             crc &gt;&gt;= 1;         }         crc_table[i] = crc;     } }</pre> | <pre>macro proc CRCGenTab (Poly, Index) {     unsigned 32 CRC;     static unsigned 3 Bit = 0;     do {         CRC = 0 @ Index;         do {             par // execute statements in parallel         {                 if (CRC[0] &amp; 1)                       CRC = (CRC &gt;&gt; 1) ^ Poly;                 else</pre> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### Define the Register Map

Our custom image-processing component has three textured spheres, and each sphere holds motion and color information in registers. To connect the component to software, we simply define the register map. Table 1 shows the register map chosen for this example. Each sphere has a 32-bit register, with motion and color information packed into it.

| Table 1. Compo | nent Register    | Мар            |        |     |    |   |   |   |

|----------------|------------------|----------------|--------|-----|----|---|---|---|

| Offset         | Register<br>Name | Read/<br>Write | 2111   | 107 | 63 | 2 | 1 | 0 |

| 0              | Spheres(0)       | RW             | DTheta | VX  | VY | R | G | В |

| 1              | Spheres(1)       | RW             | DTheta | VX  | VY | R | G | В |

| 2              | Spheres(2)       | RW             | DTheta | VX  | VY | R | G | В |

### Implement the Desired Register Map Behavior

For this example, the register map implementation unpacks 32-bit data values written to the component and places them in the relevant sphere control registers. Reading does the reverse, concatenating the smaller control registers into a single 32-bit value to return to a master on a read.

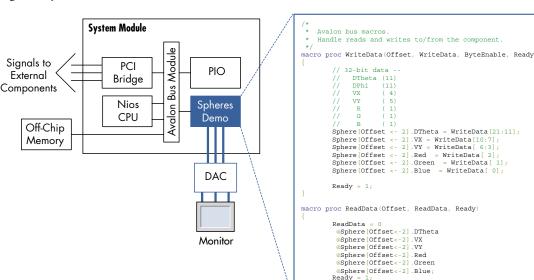

Figure 3 shows how the component fits into the system, along with a code snippet showing the register map implementation. The style of coding should be familiar to anyone familiar with C, though with some added operators (the @ operator performs bit concatenation).

### Figure 3. System Overview

### **Building the Component**

With our four steps completed, the component is ready to be built and integrated into SOPC Builder. DKAccelerator builds and optimizes the EDIF netlist for the target device and automatically integrates the component into the system. The supplied integration libraries and tools automatically generate the required Avalon signals in the EDIF and the SOPC Builder component description file.

The new component appears in SOPC Builder, and the remaining design effort is the same as for any SOPC Builder system.

### Conclusion

DKAccelerator allows you to rapidly move from a high-level concept to a functional component integrated into the SOPC Builder framework. Combined with SOPC Builder, Celoxica's proven C-based design and synthesis technology provides a C-based design flow for the generation of unique and custom, SOPC Builder components from ANSI C source. The integration effort is streamlined and dramatically reduced.

For more information email info@celoxica.com or visit www.celoxica.com/dka and see the online demonstration.

6:31

# A Comprehensive Management Process for High-Performance FPGA Design

### by Darron May Mentor Graphics

The continuing evolution of FPGAs has enabled design teams to develop larger and more complex designs. The increases in design size and complexity are enabled in part by CPUs and other cores that are not developed in-house. The broad availability of these rich resources places greater demands on design and verification teams.

The flexibility to use bigger and faster FPGAs also strains the capabilities of design creation, simulation, synthesis, and place-and-route tools. Each design start may require unique tool resources, placing a premium on the ability to change and adopt new tools in your flow. Changes can be influenced by many factors. For example, the required intellectual property (IP) may be in a different hardware description language (HDL). The chosen IP may be supported by a specific subset of tools, or a new verification language may be introduced into your methodology.

The time has come for a new class of design methods and tools that enable more thorough design entry, simulation, and implementation, as well as the management of these tasks. Ideally, the comprehensive process of FPGA design creation to realization should be managed from a single, flexible user interface, enabling a seamless design and verification flow for significant productivity gains.

# Solutions for FPGA Design Challenges

The ability to adapt to ever-changing customer needs and the necessity to improve productivity—plus the need to do both without impacting the other—are ubiquitous in the electronics industry. Because they are ideally suited to meeting these requirements, the market for FPGAs has grown rapidly.

Yet success brings its own set of new challenges. For example:

- How do you integrate and debug IP delivered in a different HDL?

- How can you train a new designer in your team to be productive sooner?

- How do you manage multiple synthesis tools as you attempt to target different devices or speed requirements?

Every successful team has the experience to meet these challenges, but not necessarily the tools and methodology. This has prompted Mentor Graphics<sup>®</sup> to develop a new Windows-based design environment for FPGAs, providing an easy-to-use, advanced-feature solution for FPGA design. This technology, called ModelSim® Designer (see Figure 1), combines the industry-leading capabilities of the ModelSim logic simulator with a built-in design creation engine. It is plug-in ready for the synthesis and place-and-route tools of your choice. The ability to easily manage the interconnection of the entire development flow gives you improved productivity in design creation, simulation, debug, synthesis, and place-and-route.

Figure 1. ModelSim Designer

# A Flexible Methodology Conforms to Designer Intent

Designers can freely mix text entry of VHDL and Verilog HDL code with graphical entry using block and state diagram editors. A single design unit can be represented in multiple graphical or abstract views. The management of compilation and simulation at all levels of abstraction is a single click away. This freedom to design according to the way you think extends to debugging, providing both graphical and text capabilities.

Alternatively, some teams choose a purely graphical approach to ensure a consistent coding style. This also facilitates design reuse and maintenance. Graphical editors use an intuitive methodology that shortens the learning curve, improving the time required for new designers to become productive. This method is also useful for designers who are migrating to HDL methodologies or changing their primary design language.

Design implementation tasks are achieved through tight integration with the most popular FPGA synthesis and place-and-route tools in the industry. The user can either run these tools directly in the simulator graphical user interface (GUI) or externally via scripts. Either way, the design data is maintained and used in a common and consistent way.

continued on page 20

To improve throughput and the distribution of design tasks, an intuitive mechanism to compile the necessary vendor libraries for post place-and-route simulation must be provided. With ModelSim Designer, the compiler detects which FPGA vendor tools have been installed and automatically compiles the necessary libraries as soon as the tool is launched. Engineers have access to the library compiler in case they want to compile additional vendor libraries.

Designers can automatically view or render diagrams from HDL code in block diagrams or state machines. When the design code changes, the graphical diagram can be updated instantly, thus ensuring its accuracy. This also helps designers understand legacy designs and aids in the debugging of current designs.

# Synthesis & Place-&-Route Integration

The industry's popular synthesis tools from Mentor Graphics, Synplicity, Altera, and others can be integrated into this solution with push-button convenience. The Altera® Quartus® II place-and-route software is fully integrated. Together with the ModelSim simulator, Quartus II software delivers an improved flow for power estimation and optimization. Placeand-route results, together with SDF information, are automatically re-read into ModelSim Designer after the process is complete, making it ready for postplace-and-route, gate-level simulation.

# Intelligent GUI for Enhanced Productivity

An intelligently engineered GUI makes efficient use of desktop real estate. An intuitive layout of graphical elements (windows, toolbars, menus, etc.) makes it easy to step through the design flow. Wizards help set up the design environment and make the design process seamless and efficient.

A memory window enables flexible viewing and switching of memory locations. VHDL and Verilog HDL memories are auto-extracted in the GUI, delivering powerful search, fill, load, and save functionality. The memory window allows pre-loading of memories, saving the time-consuming step of initializing sections of the simulation to load memories. All functions are available via the command line, making them available for scripting.

Creation wizards walk users through the construction of VHDL and Verilog HDL design units, using either text or graphics. In the case of the graphical editor, HDL code is generated from the graphical diagrams created. For text-based design, VHDL and Verilog HDL templates and wizards help engineers quickly develop HDL code without having to remember the exact language syntax. The wizards show how to create parameterizable logic blocks, testbench stimuli, and design objects. Novice and advanced HDL developers alike benefit from timesaving shortcuts.

A flexible and powerful project manager feature allows easy navigation through a design to understand design content. During compilation and simulation, the project manager stores the unique settings of each individual project and displays their hierarchy and dependencies in a separate pane.

# Active Design Visualization Enhances Simulation Debugging

During live simulation, design analysis capabilities are enhanced through graphical design views. From any diagram window, simulations can be fully executed and controlled. Enhanced debugging features include graphical breakpoints, signal probing, graphics-totext-source cross-highlighting, animation, and cause analysis. The ability to overlay live simulation results in a graphical context speeds up the debug process by allowing faster problem discovery and shorter design iterations.

# Automated Testbench Creation

ModelSim Designer offers an automated mechanism for testbench generation. The testbench wizard generates VHDL or Verilog HDL code through a graphical waveform editor, with output in either HDL or a tool command language (Tcl) script. Users can manually define signals in the waveform editor or use the builtin wizard to define the waveforms. Either way, it is intuitive, easy-to-use, and saves considerable time.

# **PowerPlay Support**

Quartus II software version 4.2 includes a new feature called PowerPlay. By importing the results of functional and timing simulation from the ModelSim software into Quartus II software, users can accurately analyze power consumption and optimize both dynamic and static power consumption for their FPGA designs.

# Conclusion

ModelSim Designer supports the entire FPGA design and verification flow from creation through simulation, synthesis, place-and-route, and post place-androute simulation. It is a straightforward process with a large number of steps performed automatically. ModelSim Designer combines easy-to-use, flexible creation with a powerful verification and debug environment. ModelSim Designer for FPGAs.Taking you where the others can't.

ModelSim\* Designer | Imagine how far you can go without roadblocks. Try our Windows\*-based, integrated design environment for managing FPGA design. Featuring proven technology from Mentor Graphics\*, the ModelSim Designer tool offers WHDL, Verilog, mixed-language

ModelSim

managing FPGA design. Featuring proven technology from Mentor Graphics<sup>®</sup>, the ModelSim Designer tool offers VHDL, Verilog, mixed-language and graphical design entry, management, and simulation. Push-button support for the leading FPGA synthesis tools and tight integration with leading place-and-route software makes the ModelSim Designer tool the ideal tool for demanding FPGA designers. It also delivers high-performance all the way through post place-and-route gate-level simulation. For more information visit: model.com/modelsimdesigner or call 1-877-435-4255 and request your free 30-day evaluation. Go where you want to go.

# Improving Bit-Error-Rate Performance in Serial Digital Multi-Gigabit Communication Systems With Error Correction Coding

by David T. Carney Plexus Corporation & Edward W. Chandler MSOE

Altera® Stratix® GX devices contain multi-gigabit serial transceivers for use in custom applications or standard protocols such as PCI-Express. Interconnection in digital systems has evolved from synchronous parallel buses to very high-speed, pointto-point serial interconnections with a switch-fabricbased architecture. This article discusses the application of the concepts of error correction coding to these new multi-gigabit serial systems.

# Model of Bit-Error-Rate vs. Jitter

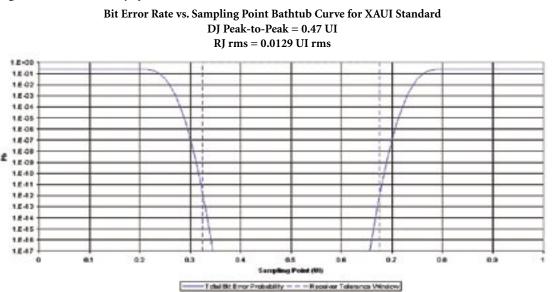

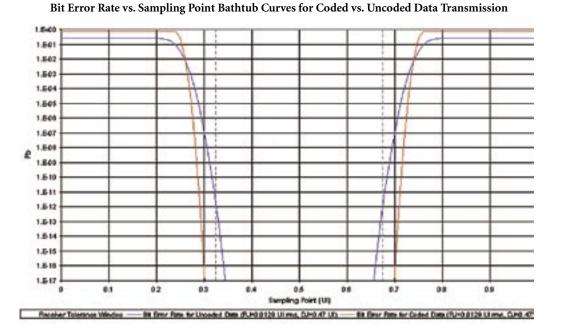

The fundamental measure of performance in a digital communication system is the bit-error-rate. Most of the current generation of standards for serial digital multi-gigabit communication systems specify a bit error rate of 10<sup>12</sup> (e.g., PCI-Express, Fibre Channel, and XAUI, [1][2][3]). In many digital communication systems, it is customary to plot the bit-error-rate as a function of Gaussian signal-to-noise ratio (Eb/N0). In wired digital communications systems, the National Committee for Information Technology Standards (in its Fibre Channel organization) has specified a different methodology for characterizing performance. This methodology plots the bit-error-rate vs. receiver sampling point in unit intervals (UI)

of time on a plot called a bathtub curve [4]. If the receiver is guaranteed to make a correct decision within some sample threshold, the bit-error-rate of the system can be determined from these bathtub curves at that point. For example, Stratix GX devices have a receiver jitter tolerance of 0.65 UI or a threshold window of 0.35 UI. The Fibre Channel organization specifies how these bathtub plots are created using random and deterministic jitter numbers, and an example using the jitter specifications for the XAUI specification is shown in Figure 1. The jitter is specified in two components, random and deterministic. Random jitter is assumed to have a Gaussian distribution and it is unbounded. Deterministic jitter has a defined distribution and a peak-to-peak value. Systems are designed with deterministic jitter specified to be less than the receiver jitter tolerance. Therefore, deterministic jitter by itself does not cause bit errors, but the unbounded random jitter added to the deterministic jitter leads to bit errors.

# **Error Correcting Code Design**

There are many considerations in choosing an error correcting code (ECC) for a serial digital multi-gigabit communication system. One of the most important is the maximum run length (MRL) of the code. The code must be able to meet the maximum run length requirements of the transceivers (80 bits for the Stratix GX devices) and also perform well in an AC-coupled system in which most serial digital multigigabit communication systems exist. The coding used

### Figure 1. XAUI Probability of a Bit Error Curve

in most existing systems is 8B/10B coding which maps 8-bit input data words into 10-bit code words. This code has excellent maximum run length performance and limits the maximum running disparity between 0s and 1s to allow good performance in AC-coupled systems where DC balance is important. However, the 8B/10B coding does not provide any mechanism for error correction. Using 8B/10B coding in addition to error correction coding would also be undesirable because it already has a code rate of 0.8 and error correction coding would add even more overhead. Additionally, there is the question of what order to perform the 8B/10B coding and the error correction coding. Ideally, the MRL coding would be performed inside of ECC because the ECC will likely upset the maximum run length constraints of the MRL code if done in the opposite order. However, if this order is used and errors occur, the MRL decoder could multiply a single bit error into multiple bit errors, which could overwhelm the error correcting capability. 8B/10B coding is particularly sensitive to this multiplying of bit errors. A better way to design an error correcting code for these systems is to perform the ECC inside of the MRL coding [5].

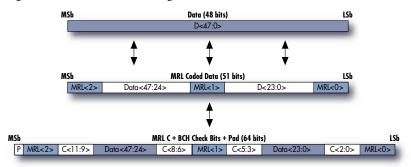

The ECC chosen in this design is a two-error correcting primitive BCH code of length 26 - 1. This code accepts a 51-bit input word and adds 12 parity bits to it for a total code word of 63 bits [6]. The MRL coding chosen is a scheme that maintains a running disparity count of the transmitted data including the parity bits from the ECC code [7]. The MRL code accepts 48 input data bits and adds 3 MRL code bits. Based on the running disparity and the disparity of the next input data word, the MRL code will either invert or not invert the incoming data in an attempt to force the running disparity toward 0. Two of the three MRL code bits indicate whether the data has been inverted or not and are set to 00 or 11. The third MRL code bit is a forced transition (1 or 0 depending on what the other two MRL bits were). This MRL code provides a means to minimize the running disparity, although it doesn't provide a guaranteed bound on running disparity like the 8B/10B coding does, and it also meets the maximum run length constraint by forcing a transition every 63 bits. It is inconvenient to connect 63 bits to the Stratix GX transceiver since it supports data word sizes of 8, 10, 16, and 20 bits. The solution is to add one extra pad bit to make the code word 64 bits, an even multiple of 16 bits. This pad bit could be used by a higher-level protocol as a frame or synchronization bit. The organization and order of the coding is shown in Figure 2. The code has a rate of 0.75, similar to the 8B/10B coding commonly used, with the advantage of being able to correct any two bit errors in each received code word.

### Figure 2. MRL + ECC Code Design

### Implementation

The design was implemented using an Altera Stratix GX (EP1SGX25F1020) device in a -5 speed grade. The size of the encoder is 450 logic cells (LCs) with 181 register LCs. The encoder design is pipelined in two stages, one stage for MRL encoding, and the second stage for ECC encoding. The maximum parallel clock frequency at which the design will operate is 67.79 MHz.

The size of the decoder is 989 LCs with 306 LC registers. The decoder design is pipelined into four stages, one stage for syndrome computation, one stage for error location polynomial coefficient calculation, one stage for error search, and a stage for MRL decoding. The maximum parallel clock frequency at which the design operates is 105.33 MHz. It may be possible to remove one pipeline stage to improve the latency performance since the decoder operates so much faster than the encoder.

The maximum serial data rate for the encoder and decoder would be 4.34 Gbps, which is beyond the capabilities of the Stratix GX transceivers. The design works at any data rate supported by the Stratix GX transceivers.

### Performance

The performance of the coding design was simulated using ModelSim<sup>®</sup> with two different data patterns, a  $2^{11-1}$  PRBS pattern and a  $2^{31-1}$  PRBS pattern. All possible single-, double-, and triple-bit-error patterns were inserted between the encoder and decoder. The design corrected all single- and double-bit-error patterns. The code was able to detect 52.4% of the triplebit-error patterns, while the others were decoded incorrectly. The maximum running disparity values for the  $2^{11-1}$  PRBS pattern simulated with 1,172 pattern repeats were 34 and -42. The maximum running disparity values for the  $2^{31-1}$  PRBS pattern simulated with 2 pattern repeats were 62 and -83.

continued on page 24

The improvement in bit-error-rate performance is shown on a bathtub curve in Figure 3. Figure 3 shows the coding gain for a system operating with 0.47 UI of deterministic jitter and 0.0129 UI rms of random jitter. The coding gain at a bit-error-rate of  $10^{-12}$  in this system is 0.033 UI of jitter. The coding gain is better for systems with more random jitter, and for a system with 0.0464 UI rms of random jitter and no deterministic jitter, the gain is 0.118 UI of jitter at a bit-error-rate of  $10^{-12}$ .

# Conclusion

The coding scheme discussed will provide some coding gain for serial digital multi-gigabit communication systems. The code rate is similar to 8B/10B coding, so lower bit error rates can be realized by systems currently using 8B/10B coding, with a small amount of added overhead. The latency performance on the decode side of four parallel clock cycles is reasonable for interconnection applications where serial digital multi-gigabit communication is common.

### References

- PCI-SIG. PCI Express Base Specification, Rev 1.0a. PCI Special Interest Group, Portland, OR, April 15, 2003.

- [2] IEEE Computer Society. IEEE Std 802.3ae 2002 (Amendment to IEEE Std 802.3 - 2002). The Institute of Electrical and Electronics Engineers, New York, NY, August 30, 2002.

- [3] National Committee for Information Technology Standards. Information technology-Fibre Channel - Physical Interfaces (FC-PI). ANSI INCITS 352-2002, November 19, 2002.

- [4] National Committee for Information Technology Standards. Information Technology-Fibre Channel - Methodologies for Jitter Specification. INCITS TR-25-1999, September 1, 1999.

- [5] A. J. van Wijngaarden and K. A. Schouhamer. "Maximum Runlength-Limited Codes with Error Control Capabilities." IEEE Journal on Selected Areas in Communications, Vol. 19 (4), April 2001, pp. 602-611.

- [6] Shu Lin and Daniel J. Costello. Error Control Coding: Fundamentals and Applications Second Edition. Prentice Hall, New Jersey, 2004.

- [7] A. Coles and D. Cunningham. "Low Overhead Block Coding for Multi-Gb/s Links." HP Labs Technical Reports, Extended Enterprise Laboratory HPL-98-168, October 1998.

Figure 3. Coding Gain for ECC

**Technical Articles**

# Cyclone II FPGAs & Nios II Embedded Processor Offer Low-Cost Performance Advantages

Building on the success of its industry-leading, lowcost Cyclone<sup>™</sup> FPGA family and Nios<sup>®</sup> soft embedded processor, Altera has now launched the second generation of each product. Cyclone II devices offer customers increased densities and new, performance-enhancing hardware features at a 30 percent lower cost than the previous generation. These new devices are more than 50 percent faster and cost up to 50 percent less than competitive FPGAs. In addition, the Nios II soft core embedded processor is more powerful and occupies fewer logic elements (LEs) than the original Nios processor.

# ASIC & ASSP Design Limitations

Today's design engineer is routinely tasked with providing products that offer the level of performance and selection of features needed to maintain a competitive edge, while also dealing with ever-tighter budgets and shrinking market windows. In the past, the challenge of meeting advanced performance requirements for high-volume products have been most cost-effectively met using either an ASIC or a suitable ASSP. While ASICs have historically offered the lowest-cost path to achieving the highest level of performance, that benefit has been offset by a lack of design flexibility, lengthy time to market and high development risks. ASSPs, on the other hand, are lower risk in terms of time-to-market, and development success, but still lack the flexibility offered by programmable logic.