# Altera Ships the New, Low-Cost FLEX 6000 Family

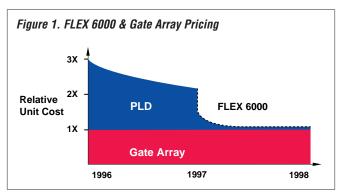

Altera recently began shipping the new, low-cost FLEX<sup>®</sup> 6000 programmable logic device family, which offers die size and cost that are directly comparable to those of gate arrays. See Figure 1. As a result of technological advances and architecture enhancements, the FLEX 6000 family combines the traditional PLD benefits of fast time-to-market and flexibility with exceptionally low cost for high-volume applications.

Gate array development often requires hidden costs that are commonly overlooked, including nonrecurring engineering (NRE) costs, the cost of a lengthy design cycle, and the cost of market opportunities that are missed due to slow time-to-market. In contrast, FLEX 6000 devices can cost less than comparable ASIC devices when these hidden costs are added into the unit cost of gate arrays. For example, a 10,000-gate EPF6010 device in a 144-pin TQFP package is expected to cost just \$6.00 for quantities of 50,000 by mid-1998.

#### **System-Level Features**

The FLEX 6000 device family contains a number of powerful system-level features to boost your design efficiency:

- Devices are fully compliant with the peripheral component interconnect (PCI) standard.

- Built-in JTAG boundary-scan test (BST) circuitry is available without consuming any device resources.

- The MultiVolt<sup>™</sup> I/O interface supports 5.0-V, 3.3-V, and 2.5-V mixed-voltage systems.

- Power consumption is less than 10 mA in standby mode.

- In-circuit

- reconfigurability (ICR)

is available via an external Configuration EPROM or intelligent controller.

#### OptiFLEX Architecture Redefines Programmable Logic Efficiency

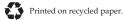

The competitive pricing of the FLEX 6000 device family is made possible by Altera's new OptiFLEX<sup>™</sup> architecture. Every feature in the OptiFLEX architecture is targeted at producing maximum performance and utilization in the smallest possible die area. The FLEX 6000 architecture is shown in Figure 2.

Through an innovative feature called interleaved logic array blocks (LABs), each logic element (LE) can drive two local interconnects, optimizing global row and column resource utilization within the FLEX device. FLEX□6000 logic arrays are routed through Altera's patented FastTrack<sup>™</sup> Interconnect, a series of fast, continuous row and column channels that run the entire length and width of the device. Each FastTrack row and column feeds multiple I/O elements (IOEs), which provide programmable slew-rate and individual tri-state output enable control for each pin.

The FLEX 6000 family also supports FastFLEX<sup>™</sup> I/O. This innovative feature provides a direct path from the LE to the I/O pin for fast clock-to-output timing. FLEX 6000 devices offer the benefits of dedicated peripheral registers with the smallest possible die size.

continued on page 3

## **Contents**

#### Features

| Altera Ships the New, Low-Cost FLEX 6000 Family1 |

|--------------------------------------------------|

| Altera Viewpoint: PLD Pricing Roadmap Shows      |

| Steeper Reductions                               |

| Customer Application: Bailey Controls Uses       |

| Megafunctions to Solve the PCI Challenge         |

#### Altera News

| Get ES Site License Authorization Codes via the Web . | 4  |

|-------------------------------------------------------|----|

| Nova Engineering Introduces Megafunction              |    |

| Development System                                    | 15 |

| The Advantages of EABs for PCI Applications           | 24 |

| The Altera Power Play Scores Big at DAC               | 24 |

| Altera Target Applications                            | 25 |

| Altera at DSP World Expo                              | 25 |

| Altera Has Moved                                      | 25 |

| MAX 7000 Beats Kasparov                               | 25 |

| Test-Drive Megafunctions with the OpenCore Feature .  | 26 |

#### **Devices & Tools**

| Altera Increases FLEX 10K Performance | 5 |

|---------------------------------------|---|

| FLEX 10K Pricing & Availability       | 5 |

| EPF10K100A Coming Soon                | 5 |

| MAX 9000A Update                      | 5 |

| MAX 7000S Pricing & Availability      | 5 |

| Faster MAX 7000S Speed Grades         | 6 |

| MAX 7000S Supports ATE                | 6 |

| Conventional MAX 7000S Device Programming         | . 6 |

|---------------------------------------------------|-----|

| MAX 7000 Product Transitions                      | . 6 |

| Product Transitions                               | . 7 |

| Improvement in High-Density Compilation Times     | . 7 |

| MAX+PLUS II Version 8.1 to Ship in September 1997 | . 7 |

| Discontinued Devices                              | . 8 |

#### **Technical Articles**

| Implementing an Encoder Using LPM Functions     | 9  |

|-------------------------------------------------|----|

| Configuring FLEX 6000 Devices                   | 10 |

| Introducing the Open-Standard Jam Programming & |    |

| Test Language                                   | 12 |

| Frequently Asked Jam Language Questions         | 13 |

| Customer Training Brings You Up to Speed        | 14 |

| The Advantages of the LPM                       | 14 |

| Questions & Answers                             | 16 |

| Altera's Failure Analysis Service               | 22 |

#### In Every Issue

| New Altera Publications             | 8  |

|-------------------------------------|----|

| Third-Party Programming Support     | 26 |

| Altera Programming Hardware Support | 27 |

| Current Software Versions           | 27 |

| Altera Device Selection Guide       | 28 |

| How to Access Altera                | 30 |

| Fax Response Form                   | 31 |

|                                     |    |

For information about this newsletter, or to submit questions, contact:

Erica Heidinger, Publisher Craig Lytle, Technical Editor 101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-0348 E-mail: n\_v@altera.com

Altera, AMPP, Atlas, BitBlaster, ByteBlaster, Classic, ClockLock, ClockBoost, FastFLEX, FastTrack, FLASHlogic, FLEX, FLEX::10K, FLEX::10KA, FLEX::000, FLEX 6000, FLEX DStPitch, MAX 9000, MAX 9000A, MAX 7000E, MAX::07000S, MAX 5000, MAX; MAX+PLUS::01F, MegaCore, MultiVolt, OpenCore, OptiFLEX, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: SuperBGA is a registered trademark of Amkor/Anam. Verilog is a registered trademark of Cadence Design Systems. Data::I/O is a registered trademark of Amkor/Anam. Verilog is a registered trademark of International Business Machines Corporation. Synopsys is a registered trademark of Synopsys, Inc. Viewlogic is a registered trademark periodic and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to

make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Copyright @ 1997 Altera Corporation. All rights reserved.

#### $\mu \text{Pitch Bond Pad Technology}$

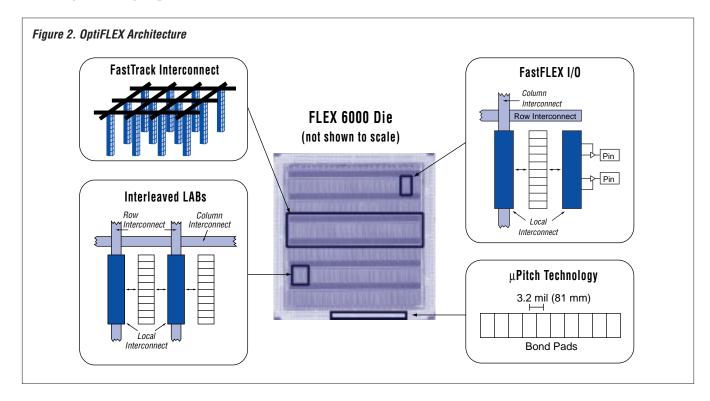

With the  $\mu$ Pitch<sup>TM</sup> bond pad feature, FLEX 6000 devices contain a bond pad pitch of just 3.2 mils (81 microns) to achieve maximum die size reduction. Therefore, a 16,000-gate FLEX 6000 device in a 240-pin package will be only 6% larger than a gate array with the same pin count, as shown in Figure 3.

#### FLEX 6000 Family Members

The FLEX 6000 device family offers from 5,000 to 24,000 usable gates of logic and is manufactured on a 0.5-micron, triple-layer metal SRAM process. Later in 1997, manufacturing will move to a 0.35-micron triple-layer metal process. Table 1 outlines the FLEX 6000 family.

#### Low Cost without Sacrificing Performance

The FLEX 6000 device family achieves die size efficiency without sacrificing utilization or performance. For example, the stringent timing requirements of PCI

Feature

compliance are achieved through FastFLEX I/O, without dedicated I/O element registers. In a FLEX 6000 device, a 16-bit loadable counter runs at 135 MHz, more than double the speed of competing field programmable gate arrays, which typically run at 60 MHz or slower. The performance of the FLEX 6000 device family is shown in Table 2.

continued on page 4

| Feature                    | EPF6010      | EPF6016      | EPF6016A     | EPF6024A     |

|----------------------------|--------------|--------------|--------------|--------------|

| Process<br>geometry        | 0.5 μ        | 0.5 μ        | 0.35 μ       | 0.35 μ       |

| Supply voltage             | 5.0 V        | 5.0 V        | 3.3 V        | 3.3 V        |

| Pin migration              | Yes          | Yes          | Yes          | Yes          |

| Gate count                 | 5,000 to     | 8,000 to     | 8,000 to     | 12,000 to    |

|                            | 10,000       | 16,000       | 16,000       | 24,000       |

| Logic elements             | 800          | 1,320        | 1,320        | 1,960        |

| User I/O pins<br>(maximum) | 160          | 197          | 197          | 215          |

| Package                    | 144-pin TQFP | 144-pin TQFP | 144-pin TQFP | -            |

| options                    | 208-pin PQFP | 208-pin PQFP | 208-pin PQFP | 208-pin PQFP |

|                            |              | 240-pin PQFP | 240-pin PQFP | 240-pin PQFP |

|                            |              | 256-pin BGA  | 256-pin BGA  | 256-pin BGA  |

Altera Ships the New, Low-Cost FLEX 6000 Family continued from page 3

#### Availability, Packaging & Pricing

The 16,000-gate EPF6016 is available now. The first 0.35-micron, 3.3-V family member, the 24,000-gate EPF6024A, will be available in January 1998. The rest of the FLEX 6000 family is expected to be available in the first half of 1998. Contact your local Altera sales representative for availability of specific packages. Examples of mid-1998 projected pricing for quantities of 50,000 units are shown in Table□3.

#### Conclusion

Altera's FLEX 6000 device family provides designers with an ideal programmable alternative to gate arrays for high-volume production. Using the efficient OptiFLEX architecture, the FLEX 6000 family delivers the flexibility and time-to-market of programmable logic at prices that are competitive with gate arrays. For

further details, refer to the *FLEX 6000 Programmable Logic Device Family Data Sheet* and *AN 87* (*Configuring FLEX 6000 Devices*), or contact your local Altera representative.

| Table 2. FLEX 6000 Performance                                 |          |                   |                   |  |  |  |

|----------------------------------------------------------------|----------|-------------------|-------------------|--|--|--|

| Benchmark                                                      | LEs Used | -2 Speed<br>Grade | -3 Speed<br>Grade |  |  |  |

| 16-bit loadable counter                                        | 16       | 135 MHz           | 99 MHz            |  |  |  |

| 16-bit accumulator                                             | 16       | 135 MHz           | 99 MHz            |  |  |  |

| 24-bit accumulator                                             | 24       | 99 MHz            | 72 MHz            |  |  |  |

| 16-to-1 multiplexer                                            | 10       | 5.5 ns            | 7.0 ns            |  |  |  |

| 16 x 16 multiplier, 4-stage<br>pipeline                        | 560      | 64 MSPS           | 50 MSPS           |  |  |  |

| 8-bit, 16-tap parallel finite<br>impulse response (FIR) filter | 599      | 78 MSPS           | 61 MSPS           |  |  |  |

| 8-bit, 512-point fast Fourier<br>transform (FFT)               | 1,162    | 155 μS<br>41 MHz  | 139 μS<br>34 MHz  |  |  |  |

| 16450 universal asynchronous receiver/transmitter (UART)       | 478      | 23 MHz            | 18 MHz            |  |  |  |

| PCI bus target with one wait state                             | 398      | 33 MHz            | 25 MHz            |  |  |  |

Table 3. FLEX 6000 Volume Price Projections

Note (1)

| Device   | Process     | Projected Pricing<br>50,000 Units |

|----------|-------------|-----------------------------------|

| EPF6010  | 0.5 micron  | \$6.00                            |

| EPF6016  | 0.5 micron  | \$7.50                            |

| EPF6016A | 0.35 micron | \$7.00                            |

| EPF6024A | 0.35 micron | \$10.00                           |

Note:

(1) Prices are in U.S. dollars for OEM direct orders.

## Get ES Site License Authorization Codes via the Web

Beginning with MAX+PLUS<sup>®</sup> II version 8.1 scheduled to ship in September 1997—you can obtain a MAX+PLUS II ES Site License authorization code via the world-wide web. Simply go to Altera's web site at http://www.altera.com/es and fill out the registration form. Your authorization code will be e-mailed to you within minutes. Using the Internet is a fast and easy way for you to get started with the MAX+PLUS II software.

# **Devices** & TOOLS

# FLEX 10K

#### Altera Increases FLEX 10K Performance

In August, Altera announced plans to increase FLEX<sup>®</sup> 10K performance by introducing new, faster -2 speed grade devices. These performance increases will allow Altera to continue to lead in high-density programmable logic performance. Contact your local Altera sales representative for more details regarding the new -2 speed grade devices.

#### FLEX 10K Pricing & Availability

On June 30, Altera reduced the prices of FLEX 10K devices by up to 49%. This price cut is a direct result of advances in process technology and reduced die size and cost. The price cuts in the high-density FLEX 10K family have been among the most aggressive in the industry, making the cost of these devices competitive with gate arrays. Since its introduction in 1995, the 100-unit list price of the 50,000-gate FLEX 10K/FLEX 10KA device has dropped from \$995 to \$99. FLEX 10K devices are available in a variety of quad flat pack (QFP), ball-grid array (BGA), and pin-grid array (PGA) packages. Sample 100-unit pricing is shown below:

| FLEX 10K Price Reductions Note (1) |                       |                       |                      |  |  |

|------------------------------------|-----------------------|-----------------------|----------------------|--|--|

| Device                             | Old 100-Unit<br>Price | New 100-Unit<br>Price | Percent<br>Reduction |  |  |

| EPF10K100GC503-4                   | \$595.00              | \$445.00              | 25%                  |  |  |

| EPF10K70RC240-4                    | \$261.00              | \$195.00              | 25%                  |  |  |

| EPF10K50VRC240-4                   | \$195.00              | \$99.00               | 49%                  |  |  |

| EPF10K50RC240-4                    | \$195.00              | \$145.00              | 26%                  |  |  |

| EPF10K40RC208-4                    | \$117.00              | \$92.00               | 21%                  |  |  |

| EPF10K30RC208-4                    | \$87.50               | \$70.00               | 20%                  |  |  |

| EPF10K20TC144-4                    | \$43.50               | \$34.00               | 22%                  |  |  |

| EPF10K10LC84-4                     | \$22.00               | \$19.00               | 14%                  |  |  |

Note:

(1) Prices are in U.S. dollars and are suggested resale.

#### EPF10K100A Coming Soon

Altera plans to ship the 100,000-gate EPF10K100A in November 1997. Initially, this device will be offered in

240-pin power quad flat pack (RQFP)packages. In the first quarter of 1998, Altera expects to provide devices in and 356-pin and 600-pin ball-grid array (BGA) packages.

Built on a 0.35-mm, quad-layer-metal (QLM) process, the EPF10K100A will be pin-compatible with current FLEX□10K devices in the 240-pin RQFP and 356-pin BGA packages. For instance, you will be able to migrate from the current 3.3-V, triple-layer-metal (TLM) EPF10K50V to a device of higher density without changing your board layout.

## **MAX 9000**

#### MAX 9000A Update

The MAX<sup>®</sup> 9000A family, manufactured on a 0.5micron, triple-layer-metal process, will offer speeds as fast as 7.5 ns. The family is pin-compatible with the MAX □9000 family and will offer you reduced power consumption. The family also supports Altera's MultiVolt I/O interface, making MAX 9000A devices ideal for mixed-voltage systems. The following table shows MAX 9000A device availability.

| MAX 9000A Device Availability |                                 |                   |                |                 |                 |                |

|-------------------------------|---------------------------------|-------------------|----------------|-----------------|-----------------|----------------|

| Device                        | Fastest<br>t <sub>PD</sub> (ns) | Availability      | 84-Pin<br>PLCC | 208-Pin<br>RQFP | 240-Pin<br>RQFP | 356-Pin<br>BGA |

| EPM9320A                      | 10                              | October<br>1997   | ~              | $\checkmark$    |                 | $\checkmark$   |

| EPM9320A                      | 7.5                             | Q1 1998           | $\checkmark$   | $\checkmark$    |                 | $\checkmark$   |

| EPM9400A                      | 10                              | Q1 1998           | $\checkmark$   | $\checkmark$    | $\checkmark$    |                |

| EPM9480A                      | 10                              | Q1 1998           |                | $\checkmark$    | $\checkmark$    |                |

| EPM9560A                      | 10                              | September<br>1997 |                | $\checkmark$    | $\checkmark$    | $\checkmark$   |

# **MAX 7000**

#### MAX 7000S Pricing & Availability

On June 30, Altera reduced the prices of MAX 7000S devices by up to 49%. This price cut is a direct result of advances in process technology and reduced die size and costs. The latest price reductions for the MAX 07000S family are the result of continuing process

continued on page 6

Devices & Tools continued from page 5

improvements and increased production volumes. Examples of the new 100-unit pricing are shown below:

| MAX 7000S Price Reductions (1) |                       |                       |                      |  |  |

|--------------------------------|-----------------------|-----------------------|----------------------|--|--|

| Device                         | Old 100-Unit<br>Price | New 100-Unit<br>Price | Percent<br>Reduction |  |  |

| EPM7256SRC208-15               | \$68.50               | \$51.00               | 26%                  |  |  |

| EPM7192SQC160-15               | \$42.00               | \$31.00               | 26%                  |  |  |

| EPM7128SLC84-15                | \$18.75               | \$11.25               | 40%                  |  |  |

| EPM7064SLC44-10                | \$9.70                | \$5.00                | 48%                  |  |  |

Note:

(1) Prices are in U.S. dollars and are suggested resale.

#### Faster MAX 7000S Speed Grades

The MAX 7000S family is now faster than ever with new 6-ns and 7.5-ns speed grade devices. The following table shows speed grades and availability.

| MAX 7000S Device Availability |              |              |              |

|-------------------------------|--------------|--------------|--------------|

| Device                        | Package      | Speed Grade  | Availability |

| EPM7064S                      | 44-pin PLCC  | -6, -7, -10  | Now          |

|                               | 44-pin TQFP  | -6, -7, -10  | Now          |

|                               | 100-pin TQFP | -6, -7, -10  | Now          |

| EPM7128S                      | 84-pin PLCC  | -7, -10, -15 | Now          |

|                               | 100-pin TQFP | -7, -10, -15 | Now          |

|                               | 100-pin PQFP | -7, -10, -15 | Now          |

|                               | 160-pin PQFP | -7, -10, -15 | Now          |

| EPM7192S                      | 160-pin PQFP | -7           | October 1997 |

|                               |              | -10, -15     | Now          |

| EPM7256S                      | 208-pin RQFP | -7, -10, -15 | Now          |

#### **MAX 7000S Supports ATE**

Altera plans to begin shipping MAX 7000S devices that support automated test equipment (ATE) beginning in September 1997. Products that support ATE have an "F" as the last character of the ordering code, e.g., EPM7128SQC100-7F.

Contact your local Altera sales representative for information on availability and lead times for MAX 7000S devices that support ATE.

#### Conventional MAX 7000S Device Programming

You can now program MAX 7000S devices using Altera's Master Programming Unit (MPU), the MAX+PLUS II software, and the appropriate programming adapter. The ordering codes for these adapters are shown below:

| MAX 7000S Devices that Support Socketed Programming       |                    |  |  |

|-----------------------------------------------------------|--------------------|--|--|

| Devices                                                   | Ordering Code      |  |  |

| All MAX 7000S devices in 100-pin<br>PQFP packages         | PLMQ7000-100NC     |  |  |

| All MAX 7000S devices in 100-pin<br>TQFP packages         | PLMT7000-100NC     |  |  |

| EPM7128S and EPM7160S devices<br>in 160-pin PQFP packages | PLMQ7128/160-160NC |  |  |

| EPM7192S devices in 160-pin PQFP packages                 | PLMQ7192/256-160NC |  |  |

Third-party programmers such as programmers from Data I/O and BP Microsystems also support socketed programming of MAX 7000S devices.

#### **MAX 7000 Product Transitions**

Altera is migrating existing MAX 7000 devices from a 0.65-micron process to a 0.5-micron process. Evaluation packets containing device samples and documentation are available from your local Altera sales

representative. The following table outlines the process migration schedule.

| MAX 7000 Migration Schedule, Note (1) |               |                   |            |

|---------------------------------------|---------------|-------------------|------------|

| Device                                | Reference (2) | Date              | Process    |

| EPM7256S                              | PCN9703       | September 1, 1997 | 0.5-micron |

| EPM7256E                              | ADV9708       |                   |            |

| EPM7192S                              | PCN9703       | November 1, 1997  | 0.5-micron |

| EPM7192E                              | ADV9708       |                   |            |

| EPM7128S                              | PCN9703       | Complete          | 0.5-micron |

|                                       | ADV9708       |                   |            |

| EPM7128E                              | PCN9703       | October 1, 1997   | 0.5-micron |

|                                       | ADV9708       |                   |            |

| EPM7064S                              | PCN9703       | September 1, 1997 | 0.5-micron |

| EPM7064                               | ADV9708       |                   |            |

Notes:

- (1) This process transition will not result in any changes to data sheet parameters or ordering codes.

- (2) Altera provides advisories and process change notices. Go to the Altera world-wide web site for these reference documents.

# MAX 5000 & Classic

#### **Product Transitions**

Altera is migrating existing MAX 5000 and Classic<sup>™</sup> devices from a 0.8-micron process to a 0.65-micron process. Evaluation packets containing device samples and documentation are available from your local Altera sales representative. Table 1 outlines the process migration schedule.

New Altera programming adapters are required to program the 0.65-micron MAX 5000 devices (0.65micron Classic devices do not require new adapters). Altera will exchange existing EPM5032, EPM5064, and EPM5130 programming adapters for new adapters *for free*. These new adapters are backwards-compatible and support all existing die revisions. Table 2 lists the existing MAX 5000 adapters that can be exchanged for new adapters. Contact your local Altera representative for more information.

| Table 1. Product Migration Schedule |               |                |                      |  |

|-------------------------------------|---------------|----------------|----------------------|--|

| Description (1)                     | Reference (2) | Device         | Date                 |  |

| MAX 5000 devices                    | PCN 9407      | EPM5032        | Complete             |  |

| fabricated on a                     | ADV 9515      | EPM5064        | October 1, 1997      |  |

| 0.65-micron process                 | ADV 9606      | EPM5128        | Complete             |  |

| Note (3)                            |               | EPM5130        | September 1,<br>1997 |  |

|                                     |               | EPM5192        | Complete             |  |

| Classic devices                     | PCN 9510      | EP6 <i>xx</i>  | Complete             |  |

| fabricated on a                     | ADV 9607      | EP9 <i>xx</i>  | Complete             |  |

| 0.65-micron process                 | ADV 9621      | EP18 <i>xx</i> | Complete             |  |

#### Notes:

- (1) Data sheet parameters or ordering codes will not change.

- (2) Go to the Altera world-wide web site for advisories and process change notices.

- (3) Devices manufactured on the 0.65-micron process must be programmed with new programming adapters.

| Table 2. MAX 5000 Replacement Adapters |             |  |

|----------------------------------------|-------------|--|

| Existing Adapter                       | New Adapter |  |

| PLEJ5064                               | PLMJ5064A   |  |

| PLMJ5064                               | PLMJ5064A   |  |

| PLEG5130                               | PLMG5130A   |  |

| PLEJ5130                               | PLMJ5130A   |  |

| PLMJ5130                               | PLMJ5130A   |  |

| PLEQ5130                               | PLMQ5130A   |  |

| PLMQ5130                               | PLMQ5130A   |  |

# MAX+PLUS II

#### Improvement in High-Density Compilation Times

MAX+PLUS II version 8.0 significantly reduces the compilation times required for FLEX devices.

For designs that target FLEX 8000 devices and FLEX 10K devices with up to 50,000-gates, MAX+PLUS III version 8.0 provides compilation times that are 2 times faster than the previous version of the MAX+PLUS III software for both PCs and UNIX workstations. For designs that target large FLEX 10K devices (up to 250,000 gates), compilation is 3 times faster. See the table below. Watch for additional new product announcements with MAX+PLUS II version 8.1.

| MAX+PLUS II Compilation Improvements |                                                                          |                                                                             |                       |

|--------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|

| Density                              | Median<br>Compilation Time<br>in MAX+PLUS II<br>Version 7.2<br>(minutes) | Median<br>Compilation<br>Time in<br>MAX+PLUS II<br>Version 8.0<br>(minutes) | Improvement<br>Factor |

| < 3,000 logic<br>elements (LEs)      | 21.24                                                                    | 8.41                                                                        | 2.5                   |

| 8,000 to 9,000<br>LEs                | 78                                                                       | 33                                                                          | 2.4                   |

| 9,000 to<br>10,000 LEs               | 183.75                                                                   | 39                                                                          | 4.7                   |

#### MAX+PLUS II Version 8.1 to Ship in September 1997

MAX+PLUS II version 8.1 provides a host of new features in a continuing effort to provide value to our customers. This latest release of MAX+PLUS II significantly improves the timing-driven compilation capability to support designers who want to create high-density designs.

Additional features in this version include:

- HP-UX 10.10 support

- Packed register support for the FLEX 6000 family

- Internal global support for the FLEX 10K family

Altera's software maintenance program keeps you upto-date with the latest features and gives you access to the newest devices. For more information on how to purchase a software maintenance agreement, contact your local Altera representative.

## **Discontinued Devices**

In recent months, Altera has announced that various products will be discontinued (see the table below). Altera distributes advisories (ADVs) and product discontinuance notices (PDNs) that provide information on discontinued devices. To obtain a copy of a specific ADV or PDN, contact your local Altera sales representative. Selected ADVs, PDNs, and a complete listing of discontinued devices are also available on Altera's world-wide web site at http://www.altera.com. Rochester Electronics, an aftermarket supplier, offers support for many discontinued Altera products. Contact Rochester Electronics at (508)□462-9332 for more information.

| Discontinued Device Ordering Codes |                                                                                                                                     |                    |                       |           |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-----------|

| Device Family                      | Device                                                                                                                              | Last Order<br>Date | Last Shipment<br>Date | Reference |

| FLASHlogic                         | EPX880 and EPX8160 (all packages, temperature grades, and speed grades)                                                             | 6/30/97            | 6/30/98               | PDN 9625  |

|                                    | EPX740 (all packages, temperature grades, and speed grades)                                                                         | 3/31/97            | 9/30/97               | PDN 9516  |

| MAX 5000                           | EPM5032SC-15                                                                                                                        | 6/30/97            | 12/31/97              | PDN 9624  |

|                                    | EPM5016 (all packages, temperature grades, and speed grades)                                                                        | 3/31/97            | 9/30/97               | PDN 9516  |

| Classic                            | EP220, EP224, EP312, EP324 (all packages, temperatures, and speed grades)                                                           |                    | 9/30/97               | PDN 9516  |

| Function-<br>Specific              | EPS448, EPS464 (all commercial and industrial temperature grades; military devices have earlier last order and last shipment dates) | 3/31/97            | 9/30/97               | PDN 9516  |

## **New Altera Publications**

New Altera publications are available from Altera Literature Services. Individual documents are available on the Altera world-wide web site. Document part numbers are shown in italics.

■ FLEX 6000 Programmable Logic Device Family Data Sheet A+DS-F6000-02 Describes the FLEX 6000 device architecture,

features, operating conditions, and pin-outs.

- AN 87 (Configuring FLEX 6000 Devices) A-AN-087-01 Describes how to use passive serial, passive serial asynchronous, or Configuration EPROM modes to configure FLEX 6000 devices.

- Jam Programming & Test Language Specification A-SP-JAM-01

Provides an overview and technical information for the Jam language.

- AN 88 (Using the Jam Language for ISP via an Embedded Processor) A+AN-088-01

Discusses how to use the Jam language to achieve the benefits of in-system programmability (ISP) with embedded processors.

- In-System Programmability Handbook *M*=*HB-ISP-01* Contains all current technical literature on the insystem programmability feature available in Altera MAX 9000 and MAX 7000S families.

- Microperipheral MegaCore Function Data Book A-DB-MEGA-02

This revised version provides information on the a8259 programmable interrupt controller, as well

as information on existing Altera microperipheral MegaCore functions.

- FLEX 10K Embedded Programmable Logic Family Data Sheet Supplement A+DSS-F10K-2.4 Summarizes device capacitance and PCI timing specifications for FLEX 10K devices.

- crc MegaCore Function Parameterized CRC Generator/ Checker Data Sheet A+DS-CRC-01 Describes parameter and port values of the fullyparameterized Altera crc MegaCore function.

- Altera Digital Library CD-ROM □ P+CD-ADL-02 This revised version provides an electronic version of all current Altera technical literature.

- TB 22: FLEX 10K Devices: The Density Leader □ □ *M-TB-022-01*

- TB 23: FLEX 10K Power Consumption □ M=TB-023-02

- TB 24: The Advantages of LPM □ M=TB-024-01

- **TB 25: Using the OpenCore Evaluation Feature** □ □ *M-TB-025-01*

- TB 26: FLEX 10K & pci\_a: The Complete PCI Solution \[ M=TB-026-01

- TB 27: Evaluating FLEX 6000 Performance M-TB-027-01

- TB 28: Advantages of Altera ISP-Based CPLDs □ □ *M*-TB-028-01

- SB 17: Early/Late Gate Synchronizer Megafunction □ □ A-SB-017-01

- SB 24: USB Function Controller Megafunction A-SB-024-01

- SB 28: USB Host Controller Megafunction A=SB-028-01

# Technical ARTICLES

## Implementing an Encoder Using LPM Functions

As devices grow in density, designs will use more prebuilt functions, such as functions from the library of parameterized modules (LPM). This article describes how to create an encoder using LPM functions. One implementation is written in VHDL, the other is written in the Altera Hardware Description Language (AHDL<sup>™</sup>). In both implementations, serial data enters a shift register. When the shift register is full, the counter will be at 7 and the coding of the 8-bit word will take place. Then, the 8-bit word is shifted out serially on the datax port as more data enters the shift register (the datax port provides the coded output). The data stream is constant, therefore, no handshaking is required.

The MAX+PLUS II VHDL example references the lpm library in the statements shown in blue text. A Generic Map Statement describes the parameters of the LPM function.

The AHDL example uses Include Statements (shown in blue text) to import the contents of the Include File containing the Function Prototypes for the LPM functions. An Instance Declaration (shown in red text) implements an instance of the function.

#### VHDL Encoder

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

LIBRARY lpm;

USE lpm.lpm_components.ALL;

ENTITY coder IS

PORT (

datain, clk : IN STD_LOGIC;

datax : OUT STD_LOGIC);

END coder;

ARCHITECTURE en OF coder IS

SIGNAL q : std_logic_vector(7 DOWNTO 0);

SIGNAL datacode :

std_logic_vector(7 DOWNTO 0);

SIGNAL eq :

std_logic_vector(15 DOWNTO 0);

```

#### BEGIN

```

shift : lpm_shiftreg

```

```

GENERIC MAP (LPM_WIDTH => 8,

LPM_DIRECTION => "RIGHT")

PORT MAP (data => datacode,

clock => clk,

shiftin => datain,

q => q,

load => eq(7),

shiftout => datax);

count : lpm_counter

GENERIC MAP (LPM_WIDTH => 3)

PORT MAP (clock => clk, eq => eq);

PROCESS BEGIN datacode <= ((datain xor

q(7)) & q(7) & not q(6 \text{ DOWNTO } 5) &

(q(4) xor q(3)) & q(3) & not

q(2 DOWNTO 1));

END PROCESS;

END en;

```

#### AHDL Encoder

```

INCLUDE "lpm_shiftreg.inc";

INCLUDE "lpm_counter.inc";

SUBDESIGN 'encoder'

(clk, datain : INPUT;

datax : OUTPUT;)

VARIABLE

```

```

shift : lpm_shiftreg WITH

(LPM_WIDTH = 8,

LPM_DIRECTION = "RIGHT");

count : lpm_counter WITH

(LPM_WIDTH = 3);

```

#### BEGIN

```

-- Connect the ports on the 8-bit shifter

shift.clock = clk;

shift.shiftin = datain;

shift.load = count.eq7;

shift.data[] = ((datain $ shift.q7),

shift.q7, !shift.q[6..5],

(shift.q4 $ shift.q3), shift.q3,

!shift.q[2..1]);

datax = shift.shiftout;

-- Connect the counter

count.clock = clk;

```

```

END;

```

## **Configuring FLEX 6000 Devices**

You can use an EPC1 Configuration EPROM or a microprocessor to configure FLEX 6000 devices using the following configuration schemes:

- Configuration EPROM

- Passive serial (PS)

- Passive serial asynchronous (PSA)

The Configuration EPROM and passive serial configuration schemes are similar to the Configuration EPROM and passive serial configuration schemes used to configure FLEX 8000 and FLEX 10K devices. This article focuses on the PSA scheme, a new configuration method that is supported only by FLEX 6000 devices.

#### **Configuration EPROM & PS Configuration**

The built-in clock in the EPC1 Configuration EPROM device controls configuration of FLEX 6000 devices. One Configuration EPROM device is large enough to configure any FLEX 6000 device, and you can configure multiple FLEX 6000 devices with one or more EPC1 Configuration EPROM devices. Programming support for the EPC1 Configuration EPROM is available via the Altera Master Programming Unit (MPU) and third-party programmers.

In PS mode, FLEX 6000 devices are controlled and clocked with one of the following configurations:

- BitBlaster download cable

- ByteBlaster download cable

- Microcontroller or other intelligent interface

The BitBlaster or ByteBlaster download cable generates a low-to-high transition on the nCONFIG pin to initiate configuration. The programming hardware then places the configuration data on the DATA pin of the FLEX 6000 device one bit at a time. The data is clocked into the FLEX 6000 device until nCONFIG goes high. The programming hardware is used in FLEX configuration mode, not in multi-device JTAG configuration or programming mode.

You can configure multiple FLEX 6000 devices with programming hardware by connecting the nCEO pin of a device to the nCE pin of the subsequent device. The other configuration pins are connected to all FLEX 6000 devices in the chain. All FLEX 6000 device CONF\_DONE pins must be tied together, so that all FLEX 6000 devices initialize and enter user mode at the same time.

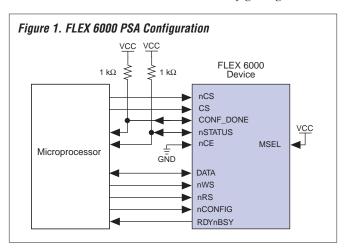

#### **PSA Configuration**

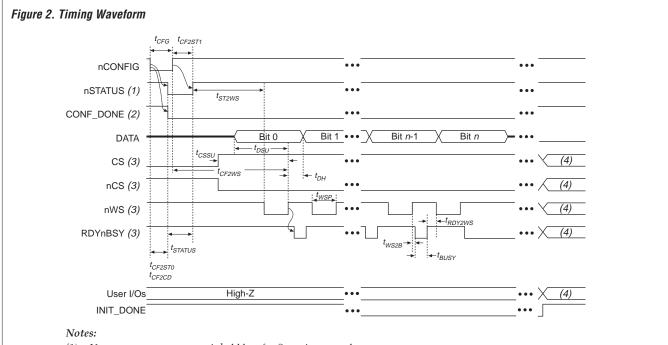

In PSA mode, configuration is controlled by a microprocessor. Configuration begins with the microprocessor driving nCONFIG high. The microprocessor then asserts the nCS and CS inputs to the FLEX 6000 device; these inputs must remain asserted until configuration and initialization are complete. The microprocessor places a configuration bit on the DATA input of the FLEX 6000 device and pulses nWS low on the FLEX 6000 device.

On the rising edge of nWS, the FLEX 6000 device latches the data and drives RDYnBSY low to indicate that it is processing the bit of data. While the bit of data is being processed, the microprocessor can perform other system functions.

The microprocessor can monitor CONF\_DONE and INIT\_DONE to ensure successful configuration. If the microprocessor has sent all configuration data and CONF\_DONE does not become asserted, the FLEX□6000 device must be reconfigured.

If an error is detected during configuration, the FLEX 6000 device drivenSTATUS low to alert the microprocessor. The microprocessor can then pulse nCONFIG low to restart the configuration. Alternatively, if the *Auto-Restart Configuration on Frame Error* option is turned on in the MAX+PLUS II software, the FLEX 6000 device releases nSTATUS after a reset time-out period. After nSTATUS is released, the microprocessor can reconfigure the FLEX 6000 device.

The FLEX 6000 device can initialize itself in PSA mode. Therefore, CONF\_DONE is asserted and the device initializes before all data is sent. The microprocessor can stop sending configuration data when CONF\_DONE is asserted.

Figure 1 shows the PSA configuration circuit and Figure 2 shows the state of the device during configuration, initialization, and user modes. Arrows show which signal transitions are dependent on other transitions.

PSA mode can be used to configure multiple FLEX 6000 devices. Multi-device PSA configuration is similar to single-device PSA configuration, except that the FLEX 6000 devices are cascaded. After the first FLEX 6000 device is configurednCEO is asserted, which asserts nCE on the second device, causing it to begin configuration. All FLEX 6000 device CONF\_DONE pins are tied together, so that all FLEX 6000 devices initialize and enter user mode simultaneously. Additionally, if any device detects an error, the entire chain will stop configuration because the nSTATUS lines are tied together. For additional information on FLEX 6000 devices, refer to *AN 87* (*Configuring*

*FLEX* 6000 *Devices* and the *FLEX* 6000 *Programmable Logic Device Family Data Sheet*.

| PSA Timing Parameters |                                                      |     |     |       |

|-----------------------|------------------------------------------------------|-----|-----|-------|

| Symbol                | Parameter                                            | Min | Max | Units |

| t <sub>CFG</sub>      | nCONFIG low pulse width                              | 2   |     | μs    |

| t <sub>STATUS</sub>   | nCONFIG low pulse width                              | 2.5 |     | μs    |

| t CF2ST1              | nCONFIG high to nSTATUS high                         |     | 4   | μs    |

| t <sub>ST2WS</sub>    | $\tt nSTATUS$ high to first rising edge on $\tt nWS$ |     | 1   | μs    |

| t <sub>CF2WS</sub>    | nCONFIG high to first rising edge on nWS             | 5   |     | μs    |

| t DSU                 | Data setup time before rising edge on nWS            | 50  |     | ns    |

| t <sub>DH</sub>       | Data hold time after rising edge on nWS              | 0   |     | ns    |

| t <sub>CSSU</sub>     | U Chip select setup time before rising edge on nWS   |     |     | ns    |

| t <sub>WSP</sub>      | nws low pulse width                                  | 50  |     | ns    |

| t <sub>WS2B</sub>     | nWS rising edge to RDYnBSY low                       |     | 50  | ns    |

| t <sub>BUSY</sub>     | RDYnBSY low pulse width                              |     | 200 | ns    |

| t <sub>RDY2WS</sub>   | RDYnBSY rising edge to nWS falling edge              | 50  |     | ns    |

| t CF2CD               | nCONFIG low to CONF_DONE high                        |     | 1   | μs    |

| t <sub>CF2ST0</sub>   | nCONFIG low to nSTATUS low                           |     | 1   | μs    |

(1) Upon power-up, nSTATUS is held low for five microseconds.

(2) Upon power-up, CONF\_DONE is low.

(3) After configuration, the state of CS, nCS, nWS, and RDYnBSY depends on the design programmed into the FLEX 6000 device.

(4) Device I/O pins are in user mode.

## Introducing the Open-Standard Jam Programming & Test Language

A coalition of leading programmable logic device (PLD) manufacturers, programming equipment makers, and test equipment manufacturers recently announced a new programming language, called Jam™, that is compatible with all in-system programmability (ISP)-capable PLDs. The Jam language is planned to be submitted as an industrystandard language to the Joint Electronic Devices Engineering Council (JEDEC).

Altera and Cypress Semiconductor support the Jam language as a method of simplifying ISP. Also endorsing the Jam language and its standardization are programming equipment vendors BP Microsystems and Data I/O Corporation, as well as test equipment manufacturers Asset InterTech Corporation, GenRad Corporation, Gopel Electronic, JTAG Technologies, and Teradyne Corporation.

#### Jam Addresses the ISP Dilemma

Currently, in-system programming is plagued by proprietary file formats, vendor-specific programming algorithms, large file sizes, and long programming times. The result is a confusing array of options, and poor return on investment for design and manufacturing engineers trying to implement ISP using PLDs. The Jam language addresses each of these issues by providing a software-level standard for ISP. The Jam standard is vendor-independent, produces small file sizes, and reduces programming times.

While created by Altera, the Jam language will be freely licensed to all interested parties. Brian Moyer, chairman of this JEDEC 23.1 subcommittee, said the Jam language will be considered at the next JEDEC meeting.

#### The Importance of ISP

In-system programmability is important to designers who use PLDs because it offers distinct time-to-market advantages throughout the product life-cycle. For example, with ISP, design revisions in the prototyping stage can be compiled and programmed into a device within minutes. In production, ISP simplifies the manufacturing flow by allowing devices to be programmed during board testing with automated test equipment (ATE), minimizing coplanarity in quad flat pack (QFP) packages and reducing the need to store programmed devices in inventory. In addition, systems using ISP-capable devices can be easily upgraded in the field by downloading new configurations via modem or other data links. There are three standard ISP programming methods:

- Download cable

- ATE

- Embedded processor

The download cable method has been the most popular with designers and is expected to remain so in the near future.

#### What Is the Jam Language?

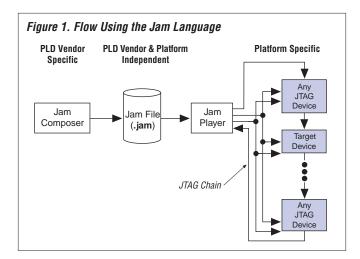

The Jam language allows the creation of a single file that specifies both the data to be programmed into a device and the algorithm required to accomplish programming. The language supports all ISP methods as well as standard programmers, which are used to program devices in bulk. The Jam language consists of two parts, the Jam Composer and the Jam Player. The Jam Composer writes files that contain the user data and programming algorithm for the device. The Jam Player interprets the Jam file and manages the JTAG port to program devices. The Jam instruction set includes JTAG-based and algorithmic instructions. These elements create a universal language and tools that address all PLDs and all programming methodologies. See Figure 1.

In addition, the Jam language addresses the issues associated with current ISP programming solutions, including smaller file sizes, faster programming times, and the ability to work with existing and future devices manufactured on different processes.

#### Smaller File Sizes

Currently, two file formats are used for ISP: ATE "bed of nails" vectors and ATE JTAG instructions. ATE vectors are a simple, low-level design representation ideal for testing. ATE JTAG instructions are ASCIIbased files that are generally created by silicon vendors. However, both methods create large files, making them impractical for some design flows using ISP. For example, file size is critical for ISP via an embedded processor, which must manage both the design data and programming algorithm. At the same time, fully expanded ISP vectors are impractical in an ATE environment. For instance, the fully expanded code required to program a 128-macrocell device typically exceeds 20 Mbytes in size. In contrast, a Jam file for the same 128-macrocell device would be about

8 Kbytes. This file, created using compression ratios of up to 50:1, is comparable in size to the Programmer Object File (**.pof**) generated by Altera's MAX+PLUS II software.

#### **Faster Programming Times**

The longer it takes system manufacturers to program a device, the more expensive testing becomes. Current ISP methods require that silicon vendors provide a programming pulse time that is long enough to guarantee that every device has been adequately programmed, which is a challenging requirement because the programming pulse is an exponential function of the oxide thickness in EEPROM, FLASH, and EPROM processes. Therefore, programming pulses are specified up to 2 orders of magnitude longer than any given device may require.

The Jam language allows the required programming pulse width to be determined real-time by reading it from each device. Devices that require a short pulse can be programmed quickly, while ensuring that devices requiring a longer pulse will meet all requirements. On average this technique reduces programming times by approximately a factor of 10.

#### Conclusion

In-system programmability is an increasingly important feature for systems designers and manufacturers seeking to shorten time-to-market. While several methods of programming and reprogramming are now in use, they have drawbacks in terms of file size and programming times. The Jam language addresses these concerns and, as an open standard, would benefit all silicon vendors, manufacturers, and programmers.

## **Frequently Asked Jam Language Questions**

With the release of MAX+PLUS II version 8.0 in June 1997, Altera began supporting a new open-standard programming and test language called Jam. The Jam language is designed for devices that support insystem programmability (ISP). This article answers some common questions about the Jam language.

#### What is the Jam Language?

The Jam language is an interpreted language optimized for programming devices via the standard IEEE 1149.1 TAP controller (i.e., the JTAG interface). This interpreted language supports both new and existing ISP-capable devices, has a small interpreter code and file size, provides faster programming times, is silicon vendor- and platform-independent, and is an open standard that can be freely licensed.

#### Who would use the Jam Language?

The Jam language could be used by any designer programming a JTAG-compliant ISP-capable device. Whether the device is programmed with a proprietary

download cable, embedded processor, or automated test equipment (ATE), the Jam language provides an efficient and quick solution.

#### Why use the Jam Language?

Many of the existing programming vector formats used with ISP-capable devices are large and difficult to work with. In many instances, the size of these existing vector format files is measured in Mbytes because they do not support data compression and algorithmic instructions. The small size of Jam files eliminates this problem.

#### How do I get the Jam Language?

Contact your local Altera sales representative to receive a Jam Developers Kit and an authorization code for enabling Jam support within MAX+PLUS II version 8.0. You can also download the kit via the Internet at http://www.altera.com/jam.

## **Customer Training Brings You Up to Speed**

Altera's Customer Training Department has revised and expanded its course offering. Classes are created specifically to meet different experience levels, provide realistic design examples and labs, and offer sound, realistic advice on hardware design techniques and software settings. These one-day sessions give you knowledge that might otherwise require months of trial and error work.

Introductory courses are ideal for designers beginning to use Altera devices. You will learn about the architecture and features of Altera device families, how to access these features with the MAX+PLUS II software, and how to analyze design results. Discussions include basic recommendations for design layout and software settings.

For experienced Altera users interested in gaining higher speed and utilization, advanced courses focus on fitting and performance for specific architectures. These classes contain more labs than the introductory courses. Faster paced and more challenging, the advanced labs require knowledge of the MAX+PLUS II software as well as a basic understanding of Altera device family architectures.

Valuable for both beginners and experienced users, *Designing with MAX+PLUS II* explores the features of the MAX+PLUS II software, including design entry

with the Text Editor and Graphic Editor, Floorplan Editor, Timing Analyzer, and Simulator as well as

synthesis and fitting. New users can discover what the MAX+PLUS□II software has to offer, and experienced users can learn about software options that they may not have used before.

Altera also offers VHDL and AHDL courses for all experience levels. These classes cover basic syntax and program structure, inferring and instantiating elements, and creating an overall design with the languages. Instructors emphasize the common problems of coding, particularly in the VHDL course.

A summary of available courses is shown below. You can also find more detailed information and a registration form on Altera's world-wide web site at http://www.altera.com.

- Introduction to Altera's MAX Device Families

- Introduction to Altera's FLEX Device Families

- Advanced Design Techniques for Altera's MAX Device Families

- Advanced Design Techniques for Altera's FLEX Device Families

- Designing with MAX+PLUS II

- Designing with MAX+PLUS II using AHDL

- Designing with MAX+PLUS II using VHDL

# The Advantages of the LPM

As designers seek to take full advantage of the capacity and performance of high-density PLDs, such as Altera's FLEX 10K family, design methodology has evolved. Instead of using traditional schematic-based design techniques, designers are turning to modern design techniques that use hardware description languages (HDLs), megafunctions, and the library of parameterized modules (LPM). LPM functions offer many advantages, especially when designing with FLEX devices.

#### Why LPM?

The LPM allows you to create architectureindependent designs, while still maintaining silicon efficiency. Instead of spending time replicating standard logic functions, using LPM functions enables you to focus on adding value to your design. Using the LPM also frees you from deciding on a target architecture until late in the design flow. Design entry and simulation are architecture-independent; a device is targeted during logic synthesis or fitting. As part of the EDIF standard, the LPM is supported by a wide range of EDA tools. For additional information about the LPM or to download synthesizable or simulatable models of LPM functions, you can refer to the worldwide web at http://www.edif.org.

Currently, the standard contains 25 LPM functions. Each function is parameterized, i.e., you can use parameters to customize a module to fit your design needs. For example, the LPM\_PIPELINE parameter can be used with the LPM multiplier, lpm\_mult, to specify the number of pipeline stages to be used. Altera, a member of the EIA's LPM committee, has the broadest software support for the LPM of any PLD vendor, as shown in Table 1.

#### A Parameterized Multiplier Example

Multipliers are basic building blocks that are used in a wide variety of applications, from digital modulation to image compression. Multiplier performance is

| le 1. LPM Modules |                     |  |

|-------------------|---------------------|--|

| LPM Module        | Supported by Altera |  |

| lpm_abs           | ~                   |  |

| lpm_add_sub       | $\checkmark$        |  |

| lpm_and           | $\checkmark$        |  |

| lpm_bipad         |                     |  |

| lpm_bustri        | $\checkmark$        |  |

| lpm_clshift       | $\checkmark$        |  |

| lpm_compare       | $\checkmark$        |  |

| lpm_constant      | $\checkmark$        |  |

| lpm_counter       |                     |  |

| lpm_decode        | $\checkmark$        |  |

| lpm_ff            | $\checkmark$        |  |

| lpm_fsm           |                     |  |

| lpm_inpad         |                     |  |

| lpm_inv           | $\checkmark$        |  |

| lpm_latch         | $\checkmark$        |  |

| lpm_mult          | $\checkmark$        |  |

| lpm_mux           | $\checkmark$        |  |

| lpm_or            | $\checkmark$        |  |

| lpm_outpad        |                     |  |

| lpm_ram_dq        | $\checkmark$        |  |

| lpm_ram_io        | $\checkmark$        |  |

| lpm_rom           | $\checkmark$        |  |

| lpm_shiftreg      | ✓                   |  |

| lpm_ttable        |                     |  |

| lpm_xor           | $\checkmark$        |  |

critical because it often limits overall system performance. Table 2 compares unsigned multiplier performance for FLEX devices.

Using the LPM function lpm\_mult and the MAX+PLUS II tools, you can create a multiplier of any size in minutes. For maximum performance, lpm\_mult has a pre-defined parameter, LPM\_PIPELINE, that allows you to automatically pipeline a multiplier. By modifying LPM\_PIPELINE, you can easily optimize the speed and efficiency of your multiplier application.

| Table 2. Multiplier Comparison          |                                         |                                          |                                          |

|-----------------------------------------|-----------------------------------------|------------------------------------------|------------------------------------------|

| Logic                                   | FLEX 10K<br>-3 Speed Grade<br>(MHz) (1) | FLEX 8000<br>-2 Speed Grade<br>(MHz) (1) | FLEX 6000<br>-2 Speed Grade<br>(MHz) (1) |

| 8 × 8 multiplier<br>pipelined           | 131                                     | 132                                      | 114                                      |

| 8 × 8 multiplier non-<br>pipelined      | 37                                      | 44                                       | 38                                       |

| $12 \times 12$ multiplier pipelined     | 80                                      | 81                                       | 78                                       |

| $12 \times 12$ multiplier non-pipelined | 21                                      | 22                                       | 22                                       |

| $16 \times 16$ multiplier pipelined     | 53                                      | 69                                       | 59                                       |

| $16 \times 16$ multiplier non-pipelined | 19                                      | 21                                       | 20                                       |

| $32 \times 32$ multiplier pipelined     | 28                                      | Note (2)                                 | Note (2)                                 |

Notes:

(1) Source: Altera Applications.

(2) The 32 × 32 multiplier is too large to fit in FLEX 8000 and FLEX 6000 devices.

### Nova Engineering Introduces Megafunction Development System

AMPP partner Nova Engineering introduced the Constellation FLEX 10K Hardware Development System as a megafunction companion. The system is ideal for real-time hardware verification, rapid prototype development, and reconfigurable computers/accelerators.

Constellation is a PLD-based, hardware development system with a modular architecture that can be easily molded into any prototype configuration. This system delivers the flexibility and ease of use necessary for rapid prototype development. It is a low-cost, off-theshelf product that provides support for a wide range of Altera's FLEX 10K devices, including 3.3-V and 5.0-V devices. The FLEX 10K development board can operate in a standalone configuration or can be expanded to include additional PLDs and analog subsystems. Modular interconnects provide "plugand-play" access to high-speed A/D and D/A converters, creating a base development system for communication, signal processing, data acquisition, control, and graphics products. For more information, go to Nova Engineering's web site at http://www.nova-eng.com.

# **Questions** & A N S W E R S

Q What problems may occur if I use Iomega software and hardware on my system with MAX+PLUS II version  $\Box$  7.1?

A MAX+PLUS II version 7.1 installation may fail if you have Iomega software and hardware installed on your system. If you remove the Iomega software and hardware, the MAX+PLUS II software will install correctly.

While you can reinstall the Iomega software and hardware after MAX+PLUS II version 7.1 installation, you should never use the MAX+PLUS II software guard and the Iomega Zip drive simultaneously. If the MAX+PLUS II software guard is connected to the Iomega Zip drive, the software guard will be destroyed.

Q How do I define a hexadecimal number using MAX+PLUS II VHDL?

A The following example shows how to define a hexadecimal number using MAX+PLUS II VHDL:

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

ENTITY hex IS

PORT(

D : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

END hex;

ARCHITECTURE a OF hex IS

BEGIN

-- The following line will convert the

-- hexadecimal value to a STD_LOGIC_VECTOR in

-- VHDL 1993.

D <= x"FC";

-- The following line will convert the

-- hexadecimal value to a STD_LOGIC_VECTOR in

-- VHDL 1987.

D(7 DOWNTO 0) <=TO_STD_LOGIC_VECTOR

(x"FC");

```

**C**an the DATA0 pin be used as an I/O pin in user mode for FLEX 10K designs?

A No, the DATA0 pin cannot be used as an I/O pin in user mode for FLEX 10K designs. To avoid conflicts between configuration and user mode, the FLEX 10K DATA0 pin is a dedicated configuration pin.

You can use the DATA1, DATA2, DATA3, DATA4, DATA5, and DATA7 pins as I/O pins in user mode because these pins are not used in all configuration modes.

Can I drive the I/O pins on an Altera device before power-up?

Applying power to the inputs of most devices before power-up can cause latch up. However, you can apply power to the inputs of FLEX 10KA devices before power-up (except for EPF10K130V and EPF10K50V devices).

**O** Can

*Can I use an Intel-format Hexadecimal File (.hex) to program an EPC1 Configuration EPROM device?*

You should not program EPC1 Configuration EPROM devices with Hex Files. You must use a Programmer Object File (**.pof**) to program EPC1 Configuration EPROM devices, regardless of whether you are using Altera or third-party programming hardware.

Can I program my revision C EPC1 Configuration EPROM using Data I/O programmers version 5.3?

A If you program revision C EPC1 Configuration EPROMs using Data I/O programmers version 5.3, you will receive device ID errors. This problem is corrected in Data I/O programming software version 5.4, which is available from the following sources:

- Data I/O FTP site (**ftp.data-io.com**)

- Data I/O Bulletin Board Service (BBS) at (206) 882-3211

Revision C EPC1 devices have date codes "yCxxxx" marked on the top of the device, where *y* is any letter and *x* is any number. For example, if the date code is AC9707, the device is a revision C device.

Q How can I provide licenses for multiple applications using the same license file?

A The following guidelines explain how to license multiple applications using the same license file.

END a;

- 1. Ensure that the host ID specified in each license file is the same.

- 2. If the version of **Imgrd** is different between applications, use the latest version. However, if an application uses **Imgrd** pre-version 3.0, the application must be licensed separately with its own copy of **Imgrd**.

After these requirements are met, use the following format for the combined license file:

SERVER <host name> <host ID> <TCP/IP port number> DAEMON <daemon application #1> <path/daemon file name> DAEMON <daemon application #2> <path/daemon file name> DAEMON <daemon application #3> <path/daemon file name> FEATURE <feature name> <daemon> <version> <expiration date> <authentication code>

The single SERVER line gives the TCP/IP port number used by all applications when accessing licensing information. Specifying multiple license files to the LM\_LICENSE\_FILE environment variable using the : operator indicates that separate TCP/IP ports should be used for communication.

The individual DAEMON lines, required by all applications being licensed, can be listed in any order. **Imgrd** will start daemons in the order in which they are listed.

You can list FEATURE lines in any order after the DAEMON lines. After the application daemon is started, the FEATURE lines are read.

How do I obtain the checksum for a device in a JTAG chain?

A If the **Multi-Device JTAG Chain** command is turned on (JTAG menu) and you are programming devices in a JTAG chain, the checksum will not appear in the MAX+PLUS II Programmer because each device has an individual checksum (there is no checksum for the entire JTAG chain).

However, you can view the checksum of individual devices in the JTAG Chain by turning off the **Multi-Device JTAG Chain** command and selecting each programming file individually.

*Q* How do I instruct the MAX+PLUS II Compiler to generate a timing Simulator Netlist File (.snf) for a device that supports a mixed-voltage interface with the MultiVolt feature? A In MAX+PLUS II version 8.0 and higher, perform the following steps in the Compiler:

- 1. Choose **Global Project Device Options** (Assign menu).

- 2. Turn on the *Low Voltage I/O* option.

- 3. Choose OK.

You cannot perform this action in MAX+PLUS II version 7.22 and lower. To obtain the correct timing parameters using these MAX+PLUS II software versions, refer to the appropriate device family data sheet. Substitute  $t_{OD2}$  for  $t_{OD1}$  to get the proper delay.

How is a "blind interrogation" of the devices in a JTAG chain accomplished?

A The IEEE 1149.1-1990 specification provides an optional IDCODE instruction mode that permits blind interrogation of the devices in a JTAG chain.

Upon power-up, any device that supports IDCODE will automatically load the IDCODE instruction into the instruction register. Any device that does not support IDCODE will automatically load the BYPASS instruction into the instruction register.

After power-up, the blind interrogation is accomplished by shifting data from the data register. Any device that supports IDCODE will shift out the 32-bit ID value with a "1" in the least significant bit (LSB) and any device that does not will shift out a "0" in the BYPASS register. To determine if a device supports IDCODE, simply check whether the first bit shifted out is a "1" or "0."

For additional information refer to *AN* 39 (*JTAG Boundary-Scan Testing in Altera Devices*).

**Q** Can I program a MAX 7000S device with a MAX□7000E Programmer Object File**.(pof**)?

A Yes, you can program a MAX 7000S device with a MAX 7000E POF. The MAX 7000S device features are a superset of the MAX 7000E device features. Therefore, if you program a MAX 7000S device with a MAX 7000E POF, the MAX+PLUS II software will automatically disable the superset features on the MAX 7000S device.

This programming (often called cross-programming) is supported by the MAX+PLUS II software, as well as by third-party programmers such as programmers from Data I/O (http://www.data-io.com) and BP Microsystems (http://www.bpmicro.com).

Cliff Tong Senior Director, Product Marketing

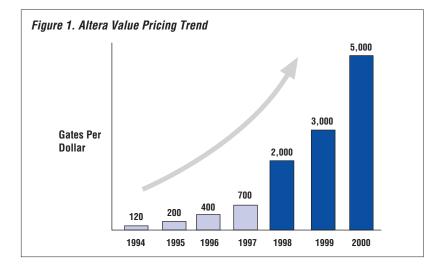

Altera expects to target PLD process technology at 0.18-micron by the year 2000.

The value of using highdensity programmable logic in high volume will increase from the current level of about 700 gates per dollar to about 5,000 gates per dollar by the year 2000.

# **PLD Pricing Roadmap Shows Steeper Reductions**

While ASIC and PLD suppliers provide a variety of information and tools to help designers determine performance and integration density, it is sometimes difficult for designers to obtain volume price projections. This difficulty is somewhat ironic, as device price is a significant factor in the up-front decision process of the system designer. In fact, several recent surveys of both programmable logic and ASIC users have shown that device price has commonly been identified as the most critical factor influencing device selection.

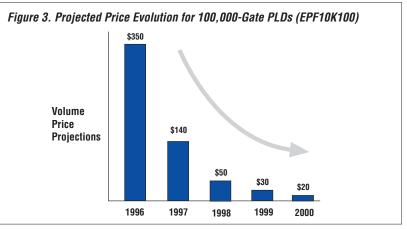

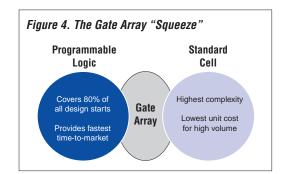

As the PLD price leader, Altera is more focused than ever on providing designers with the necessary insight on pricing, as well as the technical attributes of both existing and future products. Over the next three years, Altera anticipates an acceleration in cost reduction that will lead to price cuts of as much as 50% annually. The value of using high-density programmable logic in high volume is expected to increase from the current level of about 700 gates per dollar to about 5,000 gates per dollar by the year 2000 (see Figure 1). These price reductions, combined with the traditional time-tomarket and risk reduction benefits of PLDs, will serve to further increase the use

of high-density PLDs in volume applications where gate arrays were once used exclusively.

# Process Technology Advances Lead Die Size Reductions

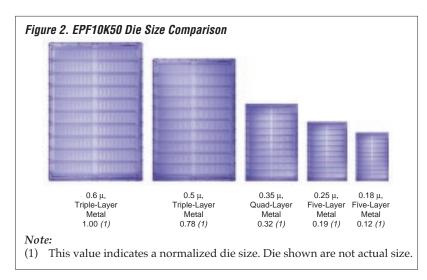

Altera has been among the industry leaders in developing advanced process technologies. Since 1992, Altera's SRAM process geometry has exhibited an average linear shrink of nearly 20% per year, compared to an industry average of 11%. Altera has already begun 0.25-micron process development and plans to release devices using this process in the first half of 1998. Altera also plans to launch a project this year with one of its wafer manufacturing partners, Taiwan Semiconductor Manufacturing Corporation (TSMC), to develop a 0.18micron SRAM process geometry for production in late 1999.

Further die size reductions may be obtained with the addition of metal layers in the circuit design. The continuous interconnect structure of Altera PLDs optimally leverages multilayer metal layout (see Figure 2). Current Altera devices are fabricated on a three-layer metal process, and Altera plans to ship devices using a four-layer metal process later this year. Five-layer metal process development is also underway for 1998.

#### Advanced Device Packaging Technology

As PLD process geometries continue to shrink, device packaging will take on added importance. Because device packaging is expected to become an increasing percentage of the total device cost, reducing package cost will become one of Altera's key objectives. Altera is working with packaging and assembly partners to develop lower-cost, production-worthy packages. Altera is also researching a variety of advanced packaging, including new types of ballgrid array and flip-chip packages.

In ASIC designs, bond pad limitations are often the pacing item for die size and perunit cost. Until recently, the amount of core logic has been the primary factor for determining PLD die size and cost. With the acceleration of process technologies, Altera PLDs are becoming "pad limited," where die size is no longer constrained by the total number of gates, but by bond-pad pitch. Altera is at the technology forefront of programmable logic suppliers by offering a bonding pad pitch of 81 µ for the recently introduced FLEX 6000 devices, and is aggressively developing an advanced bonding pad pitch of 55  $\mu$  for next-generation, 0.25-µ process devices.

#### **Other Technological Improvements**

In addition to process geometry and advanced packaging, Altera will evaluate other technological improvements to lower device costs. Ongoing improvements in the use of circuit redundancy can greatly enhance product yield, leading to a lower per unit cost. Additional refinement of the continuous interconnect structure will further enhance device performance and die size, while maintaining routability. Continued investment in advanced synthesis and placement and routing algorithms will allow further gains in device resource usage.

#### **Price Projections**

Device pricing is a critical factor in the system design process. During the next three years, Altera expects both FLEX and MAX family prices to decrease greatly. FLEX device pricing is expected to fall as much as 50% annually; MAX device pricing per macrocell is projected to fall by up to 37% annually. For example, the projected volume price for Altera's 100,000-gate EPF10K100 device is \$140 at the end of 1997; by the end of 1998, it is expected to drop to \$50; and by the end of the year 2000, pricing for this device is projected to be \$20 (i.e., 5,000 gates per dollar). See Figure 3.

#### Conclusion

Price reductions are often larger than anticipated by the PLD market. In the future, Altera will use advanced process technologies to further reduce die size and costs, which permits even lower prices as well as dramatic increases in device density, performance, and functionality. Advanced packaging, proprietary circuit redundancy, and improved development tools accelerate the increasing value of the

programmable logic solution. The combination of flexibility and faster time-to-market gives PLD users an increasingly attractive alternative to traditional gate-array solutions for highvolume applications (See Figure 4). Dramatic feature size reductions are expected to decrease cost and increase device density and performance.

# Customer Application

# **Bailey Controls Uses Megafunctions to Solve the PCI Challenge**

"New and faster processors started hitting the market every 11 months or so, and we just didn't have the engineering bandwidth to create a new design and develop a new product every year." —Bill Mohat, Senior Design Engineer, Bailey Controls Bailey Controls, part of the international Elsag Bailey Process Automation N.V. group, needed a PCI bus to create a new industrial controls product that enabled processor upgrading without imposing costly product redesign burdens. They found the solution by working with Eureka Technology, an independent megafunction developer specializing in architecture-independent PCI megafunction solutions.

#### The Challenge

The engineers at Bailey Controls were caught in a difficult situation: they needed the ability to easily upgrade the microprocessors in their industrial control products but did not have the resources to completely redesign their single-board system. For years, Bailey Controls designed products based on Motorola 68000 family of microprocessors and proprietary ASICs. "Up to a certain point, our typical product life cycle was five to eight years using a specific processor," said Bill Mohat, a senior design engineer. "But new and faster processors started hitting the market every 11 months or so, and we just didn't have the engineering bandwidth to create a new design and develop a new product every year."

Managers and engineers decided they needed to develop an entirely new product line. Designing in the ability to upgrade without obsoleting the entire printed circuit board (PCB) would require uncoupling all custom elements from the microprocessor, including proprietary networks and I/O channels. At the same time, the Bailey Controls staff decided to use off-the-shelf hardware as much as possible and remain with the Motorola 68000 family. On top of these requirements, they faced limited engineering resources.

To meet the basic criteria, the design needed a bus that was both processor and clock-rate independent. The peripheral component interconnect (PCI) bus—a common, but complex bus technology—fit the criteria, but was unfamiliar to Bailey engineers. Finally, Bailey staff settled on a PCI-to-68030 bridge that would enable them to create a modular system enabling easy upgrades.

Bailey engineers looked at a number of alternatives for implementing the PCI interface. However, general-purpose devices failed to provide the necessary flexibility. In addition, they studied hardware solutions developed by other divisions in their parent company Elsag Bailey Process Automation, but found these solutions to be too demanding of engineering resources to meet the specific needs of the project.

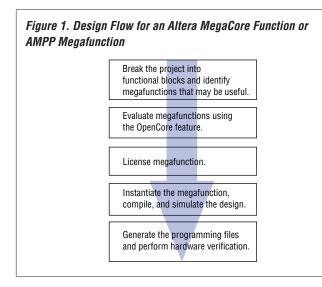

#### The Megafunction Solution