# APEX Devices & Quartus Software: The System-on-a-Programmable-Chip Solution

Designing for system-level integration requires devices with the density and flexibility to support a new design methodology and enhance productivity. Altera's new APEX<sup>TM</sup> device family and Quartus<sup>TM</sup> software have launched this new era in programmable logic design.

With over 1 million typical gates (2.67 million system gates), APEX devices are the first PLDs designed with the MultiCore<sup>™</sup> architecture, which integrates RAM, product-term logic, and look-up table (LUT) logic on a single device. To meet the challenges of designing for multi-million-gate devices, the powerful Quartus software offers features never before seen in a

programmable logic development tool. Together, APEX devices and Quartus software offer designers the ideal solution for implementing high-performance System-on-a-Programmable-Chip<sup>™</sup> designs.

#### **Matching Architecture & Software**

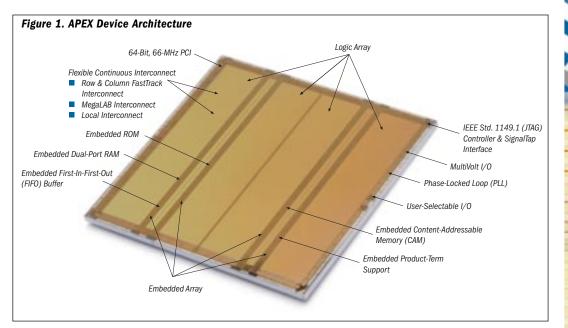

Altera's high-density, high-performance APEX MultiCore architecture is designed for systemlevel integration (see Figure 1). The MultiCore architecture combines LUT logic, product-term logic, and memory features into one embedded architecture. Designers can integrate a complex system design onto a single APEX device,

continued on page 4

- Simplified Designs through Selectable I/O Standards, pg. 13

- Design Tips: Hierarchical Instantiation Organizes Your Design, pg. 16

• SignalTap Embedded Logic Analyzer, pg. 24

# The System-on-a-Programmable-Chip Solution

Visit the Altera Main Booth 3016 and qualify for an Altera pool cue.

### Visit Our AMPP IP Partners at Booth 1716

ISS, Lexra, Nova, PLD Applications & Sapien

### **High Performance**

High-Speed Programmable Logic Devices with System Performance over 200 MHz

# Density

APEX<sup>™</sup> Device Family Offering up to 1 Million Gates

# **Cutting-Edge Software**

Quartus<sup>™</sup> and MAX+PLUS<sup>®</sup> II Software — The Industry's Best Development Tools

# **Powerful Megafunctions**

Powerful Megafunctions from Altera's MegaCore<sup>TM</sup> Function Library and AMPP<sup>SM</sup> Partners

# EDA Teamwork

NativeLink  $^{\rm TM}$  EDA Tool Integration

The Programmable Solutions Company™

# Table of Contents

#### Features

| APEX Devices & Quartus Software: The   |

|----------------------------------------|

| System-on-a-Programmable-Chip Solution |

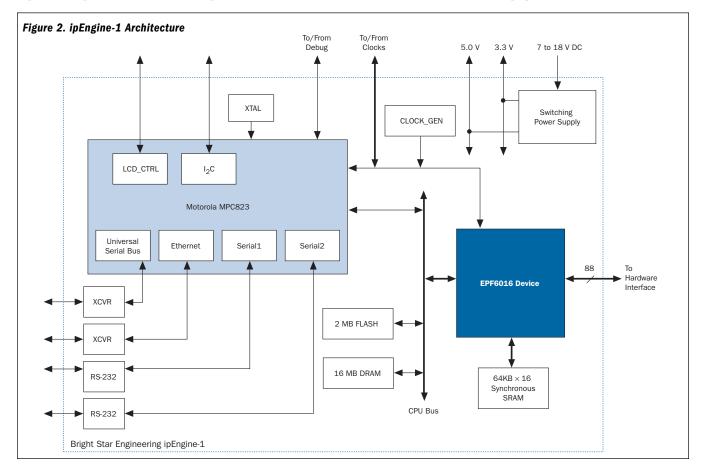

| Customer Application: Bright Star      |

| Engineering & FLEX 6000 Devices        |

| Connect Products to the Internet       |

#### Altera News

| \$20K for APEX 20K                         | . 20 |

|--------------------------------------------|------|

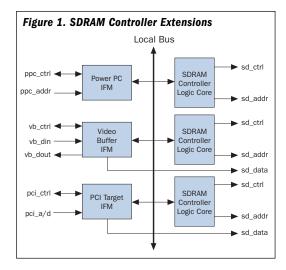

| NWL Provides SDRAM Controller              |      |

| Integration with PCI/C                     | . 21 |

| Synplify/Quartus Integration Streamlines   |      |

| APEX Designs & Design Flows                | . 22 |

| SignalTap Embedded Logic Analyzer Provides |      |

| Visibility of Internal PLD Signals         | . 24 |

| Altera Tools for Training Program          | . 34 |

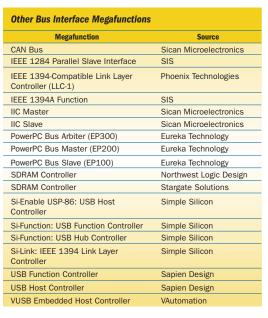

| PCI & Other Bus Interface Megafunctions    | . 35 |

#### **Devices & Tools**

| EP20K400 Devices Now Available              | . 7 |

|---------------------------------------------|-----|

| 0.22-µm EPF10K100E Devices Available        | . 7 |

| Introducing EPF10K200S & EPF10K50S Devices  | . 7 |

| Software Support for New FLEX 10KE Packages | . 8 |

| FLEX 10K Device Availability                | . 8 |

| FLEX 10K Product Transitions                | . 8 |

| FLEX 10KE Industrial-Temperature Devices    | . 8 |

| FLEX 10KE Devices Available with PLLs       | . 9 |

| Industrial-Temperature FLEX 6000            |     |

| Devices Available                           | . 9 |

| FineLine BGA Packages Coming Soon for   |    |

|-----------------------------------------|----|

| FLEX 6000 Devices                       | 9  |

| MAX 7000S Device Availability           | 10 |

| MAX 7000A Device Availability           | 10 |

| New MAX 7000B Device                    | 10 |

| New MAX 3000A Devices                   | 11 |

| Download the Quartus Preview Today      | 11 |

| New Quartus Simulator Features          | 11 |

| Quartus Static Timing Analyzer Features | 12 |

| Quartus License Files                   | 12 |

| MAX+PLUS II BASELINE Version 9.23       |    |

| Now Available                           | 12 |

| Discontinued Devices Update             | 35 |

#### **Technical Articles**

| Simplified Designs through Selectable          |    |

|------------------------------------------------|----|

| I/O Standards                                  | 13 |

| CAM Accelerates Applications in APEX Devices 2 | 14 |

| Design Tips: Hierarchical Instantiation        |    |

| Organizes Your Design                          | 16 |

| Questions & Answers                            | 27 |

#### In Every Issue

| 20 |

|----|

| 29 |

| 29 |

| 31 |

| 34 |

|    |

Altera, APEX, APEX 20K, ASCEND, ACCESS, AMPP, BitBlaster, ByteBlaster, ByteBlaster, W, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, EPC2, FastTrack, FineLine BGA, FLEX, FLEX 10K, FLEX 10KE, FLEX 10KA, FLEX 8000, FLEX 6000, JLEX 6000, Jam, MastePlaster, MAX 9000, MAX 9000A, MAX 7000B, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000A, MAX 7000B, MAX 5000, MAX 3000A, MAX, MAX+PLUS, MAX+PLUS II, MegaCore, MegaLAB, MegaWizard, MultiCore, MultiVolt, NativeLink, nSTEP, OpenCore, Quartus, SignalTap, System-on-a-Programmable-Chip, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: Boulder Creek Engineering is a registered trademark of Boulder Creek Engineering. Bright Star Engineering, inc. Motrobal is a registered trademark of Motorola, Inc. Northwest Logic Design. Palm VII is a trademark of 3Com Corporation. Rochester Electronics is a registered trademark of Rochester Electronics, Inc. Synplicity and Synplify are registered trademarks of Synplicity, Inc. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service specifications before relying on any published information and before placing orders for products or services. The actual availability of Altera's products and features could differ from those projected in this publication and are provided solely as an estimate to the reader.

Copyright © 1999 Altera Corporation. All rights reserved.

Erica Heidinger, Publisher Greg Steinke, Technical Editor 101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 n v@altera.com

Printed on recycled paper.

May 1999

News & Views Altera Corporation

APEX Devices & Quartus Software: The Systemon-a-Programmable-Chip Solution, continued from page 1

eliminating the need to use multiple devices. Not only does the APEX architecture save valuable board space, it also simplifies design implementation.

The APEX architecture is composed of a series of MegaLAB<sup>TM</sup> structures connected by the fast, continuous FastTrack<sup>®</sup> Interconnect. Each MegaLAB structure contains 16 logic array blocks (LABs), an embedded system block (ESB), and a MegaLAB local interconnect that connects the LABs and the ESB. The ESB can be configured as LUT logic, product-term logic, or memory, including dual-port RAM, first-in first-out (FIFO) buffers, ROM, or contentaddressable memory (CAM).

To ensure that logic is mapped correctly to the APEX architecture, the Quartus Compiler uses the CoreSyn<sup>™</sup> capability. The Compiler analyzes the design and implements functions using the optimal technology for that block: LUT-based logic elements, product-term-based macrocells, or ESBs in the APEX architecture.

As shown in Figure 2, logic options can be set block-by-block. The Assignment Organizer allows the designer to specify whether blocks or

Figure 2. Technology Mapper in Quartus Software

| ssignment Organizer                                                                                                                                                                                   | 2                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| By Node By Category Mode Edit project defaults & Compiler settings B Edit specific entity & node settings for: None: Bovienbgen enbgen G Show assignments inherited from highe Assignment Categories: | er hienarchical levels & project defaultz<br>Description:                                                                                                                                          |

| Acception Lakegonic:                                                                                                                                                                                  | Specifier: whether to tagget look-up table (LUT), product term, or ROM<br>thructures-or whether to allow the Compiler to choose an appropriate<br>thructure-when implementing logic in the device. |

| 4 D                                                                                                                                                                                                   | Stored in accignments for<br>Bipulenbigenvenbigen                                                                                                                                                  |

|                                                                                                                                                                                                       | DK. Cancel Apply                                                                                                                                                                                   |

modules in the project hierarchy should be mapped to LUT logic, product-term logic, or memory. Alternatively, designers can use the *AUTO* mode in the Quartus Technology Mapper, which instructs the Quartus software to determine the best implementation.

#### Attaining Clock Rates of 622 MHz

To help designers verify the performance of their APEX designs, the Quartus software offers extensive timing information. Timing analysis is performed automatically during each compilation because the Timing Analyzer is incorporated into the Quartus Compiler. Designers can monitor the device's actual system operating frequency, the internal operating frequency, and other timing parameters. System  $f_{MAX}$  takes into account  $t_{SU}$  and  $t_{CO}$  times of external devices as well as off-chip delays (where they have been specified). Figure 3 on page 5 shows the  $f_{MAX}$  of a design displayed in the Quartus Report Window.

To increase system clock rates, APEX devices feature up to four phase-locked loops (PLLs) with output frequencies reaching 200 MHz. These PLLs support the performance-based ClockLock<sup>TM</sup>, ClockBoost<sup>TM</sup>, and ClockShift<sup>TM</sup> clock management circuitry. The ClockLock circuitry reduces clock delay and skew and minimizes clock-to-output times while maintaining zero hold times. The ClockBoost circuitry offers flexible-rate clock multiplication and division. The ClockShift circuitry allows the clock phase and delay to be adjusted. These features provide significant improvements in system performance and bandwidth. The Quartus Timing Analyzer supports the APEX clock management circuitry and can perform timing analysis on designs with multiple related clocks.

#### **APEX Devices: The First PLDs with CAM**

The APEX device family is the first programmable logic device (PLD) family to offer CAM. When in CAM mode, the APEX ESB implements 32-word, 32-bit CAM. Wider and deeper CAMs can be implemented by combining multiple CAMs. To create larger CAMs, the CoreSyn synthesis capability of the Quartus software automatically combines ESBs and the necessary logic elements (LEs). Because the logic and CAM are integrated into the device, APEX CAM provides much faster system performance than traditional discrete CAM. The APEX CAM accelerates fast search applications by integrating the parallel comparators into a single block and eliminating on-chip and offchip delays.

#### Million-Gate Designs Require Innovative Approaches

Because of their density and performance, APEX devices give designers the flexibility to address much larger designs in a broader range of applications than traditionally possible in PLDs. However, to deal with such density and to bring complex designs to market on time, teams of designers often need to work on separate sections of a project. The Quartus software is designed specifically for collaborative design projects.

Integrated into the Quartus software is a centralized object-oriented database that can be accessed by multiple engineers across a network. The Quartus software lets you use industrystandard revision control systems to track all of the changes in each project file and link them to a database. Users can check out files, work on them, and then check them back in, documenting the changes that have been made. A log tracks users and the changes they make to a file. Using a revision control system together with the Quartus software safeguards the integrity of a project; users cannot overwrite the work of others, changes are documented, and it is easy to roll back to a previous version of the design if the need arises.

Another consideration when designing for large devices is the time needed for full compilation. Complex designs often require several iterations before the desired results are achieved. The Quartus software includes two new features to speed design processing: multi-processor support and the nSTEP<sup>TM</sup> Compiler.

The Quartus software was designed from the start for multi-processor support. Processorintensive tasks like compilation can be distributed to multiple processors locally, across a network, and across multiple operating systems. Tying together the power of several PCs and workstations can considerably reduce the time needed for compilation.

#### Figure 3. System $f_{\rm MAX}$ in the Quartus Software

| 🖏 Generius - & Trat 2 Villeol - pilleol Compilation Report)<br>🐵 Re. (dl. Yew. (j.). Print: Personing. (j. 16). (j. 16).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |                         |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------|--|

| COHD BLARK ON A SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 | . 000                   |  |

| 38 Longing Longing Pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Interfaced, defended humanismal |                         |  |

| Empland<br>B-1 Barr B-40 B Lepiterce<br>B-10 Barr B-100 Projectioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Duck Name<br>- Registe Hame     | Peopled Inse Astualitie |  |

| Bernered areacomay inder. No paint days days of the first bare of the first bar |                                 |                         |  |

| Pia Helji, pena P1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 | Empharide               |  |

Before the Quartus software, each design iteration required a full compilation. Now, the nSTEP Compiler permits incremental recompilation. Designers can make changes and obtain results without running a full compilation and without affecting placement and timing in the rest of the design. This process allows you to easily evaluate changes, saving valuable time.

#### **LVDS Support**

APEX devices offer support for multiple highbandwidth, low-voltage I/O interfacing standards. The APEX family is the first PLD family to support the low-voltage differential signaling (LVDS) standard with performance up to 622 Mbits per second. Other standards supported by APEX devices include low-voltage transistor-to-transistor logic (LVTTL), stubseries terminated logic (SSTL-3/2), advanced graphics port (AGP), high-speed transceiver logic (HSTL), and Gunning transceiver logic (GTL+). Designers can use the Quartus software to specify high-speed interfaces between SDRAMs, processors, and system backplanes to APEX devices to achieve the desired performance.

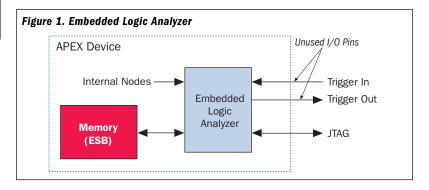

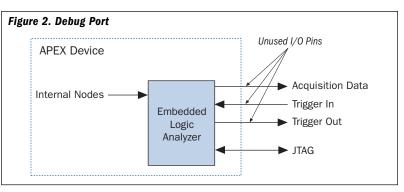

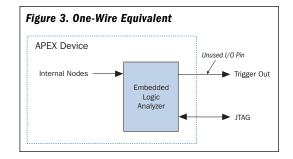

#### APEX JTAG BST Circuitry Connects to the SignalTap Embedded Logic Analyzer

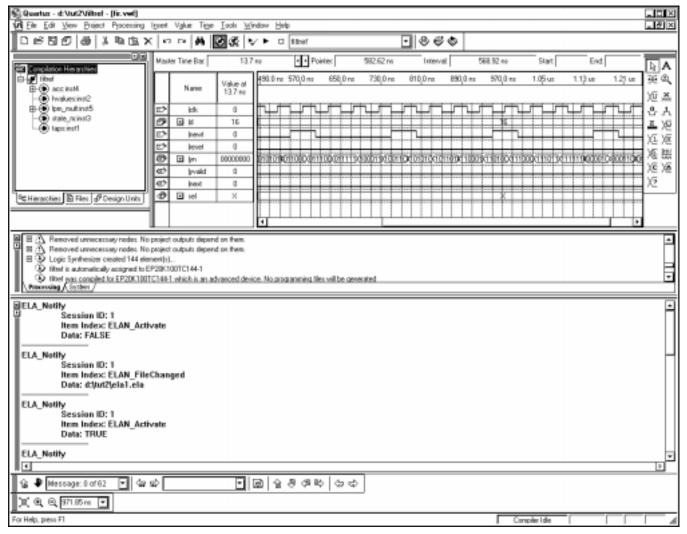

The verification of multi-million gate designs is the most time-consuming part of the design APEX Devices & Quartus Software: The Systemon-a-Programmable-Chip Solution, continued from page 5

process. However, the APEX device family and Quartus software simplify the process and reduce verification time. The APEX device family has dedicated IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry that can be used to monitor the internal logic operation of the devices with the software-implemented Quartus SignalTap<sup>TM</sup> logic analyzer (see Figure 4). The SignalTap logic analyzer allows designers to perform hardware debugging while the circuit is running at speed, significantly enhancing the board-level verification process. The MasterBlaster<sup>TM</sup> communications cable connects the platform running the Quartus software to the printed circuit board (PCB), allowing the SignalTap

logic analyzer to monitor the APEX device. For details on the SignalTap logic analyzer, see "SignalTap Embedded Logic Analyzer Provides Visibility of Internal PLD Signals" on page 24.

#### Conclusion

The powerful features of the Quartus software allow designers to realize the full potential of the state-of-the-art APEX devices, shortening design time and increasing productivity. Together, Altera's Quartus software and APEX devices provide the real solution for implementing System-on-a- Programmable-Chip designs.

APEX devices and the Quartus software are available now. For further details, visit the Altera web site (http://www.altera.com) or contact your local sales representative.

Figure 4. SignalTap Embedded Logic Analyzer

### APEX

#### **EP20K400 Devices Now Available**

The first APEX<sup>TM</sup> device is now available (see Table 1). The 400,000-gate (1 million maximum system gates) EP20K400 device features the MultiCore<sup>TM</sup> architecture, which includes integrated look-up table (LUT) logic, productterm logic, and flexible memory. The APEX MultiCore architecture offers designers complete system-level integration on a single device, eliminating the need for multiple devices, saving board space, and simplifying the implementation of complex designs. The flexible memory structure supports dual-port RAM with independent read/write ports, synchronous or asynchronous operation, and 161-MHz first-in first-out (FIFO) performance in a wide range of widths and depths.

| Table 1. APEX Device Availability |                                                                     |                    |  |  |

|-----------------------------------|---------------------------------------------------------------------|--------------------|--|--|

| Device                            | Package (1)                                                         | Availability       |  |  |

| EP20K100                          | 144-pin TQFP<br>208-pin PQFP<br>240-pin PQFP                        | June 1999          |  |  |

|                                   | 196-pin FineLine BGA<br>324-pin FineLine BGA<br>356-pin BGA         | Q3 1999            |  |  |

| EP20K200                          | 208-pin RQFP<br>240-pin RQFP<br>356-pin BGA<br>484-pin FineLine BGA | Q3 1999            |  |  |

| EP20K400                          | 652-pin BGA<br>655-pin PGA                                          | Now                |  |  |

| EP20K400E                         | 672-pin FineLine BGA<br>208-pin RQFP<br>240-pin RQFP                | Q3 1999<br>Q3 1999 |  |  |

|                                   | 652-pin BGA<br>672-pin FineLine BGA                                 | Q4 1999            |  |  |

| EP20K600E                         | 652-pin BGA<br>672-pin FineLine BGA<br>784-pin FineLine BGA         | Q4 1999            |  |  |

| EP20K1000E                        | 784-pin FineLine BGA<br>984-pin PGA                                 | Q4 1999            |  |  |

#### Note:

(1) PQFP: plastic quad flat pack, RQFP: power quad flat pack, TQFP: thin quad flat pack.

APEX devices are fully 64-bit, 66-MHz peripheral component interconnect (PCI) compliant and deliver clock rates up to 622 MHz. The EP20K400 device has a phaselocked loop (PLL), which features enhanced ClockLock<sup>TM</sup> and ClockBoost<sup>TM</sup> circuitry. The PLL circuitry offers 1×, 2×, and 4× multiplication over an extended frequency range. The device also provides the MultiVolt<sup>TM</sup> I/O interface, which is ideal for mixed-voltage systems, and supports hot-socketing. EP20K400 devices are available in 652-pin ball-grid array (BGA) and 655-pin pin-grid array (PGA) packages, and will be available soon in the 672-pin FineLine BGA<sup>TM</sup> package. For the latest information on APEX devices, go to the Altera web site at http://www.altera.com.

#### FLEX

#### 0.22-µm EPF10K100E Devices Available

EPF10K100E devices are now available. These devices use a state-of-the-art 0.22-μm, 5-layermetal process that provides high-performance and low-power advantages. In addition to 4,992 logic elements (LEs) and 49,152 bits of on-chip dual-port RAM, EPF10K100E devices also feature a programmable delay to support 64-bit, 66-MHz PCI compliance and a PLL for improved pin-to-pin timing. EPF10K100E devices are offered in 208-pin PQFP, 240-pin PQFP, 256-pin FineLine BGA, 484-pin FineLine BGA, and 356-pin BGA packages.

# Introducing EPF10K200S & EPF10K50S Devices

Enhanced versions of the EPF10K200E and EPF10K50E devices, called EPF10K200S and EPF10K50S devices, respectively, include a migration from a 0.25-µm process to a 0.22-µm process for increased performance and lower power consumption, and a programmable delay to provide full 64-bit, 66-MHz PCI compliance. (EPF10K100E, EPF10K130E, and EPF10K30E devices all feature a programmable delay and are

#### Devices & Tools, continued from page 7

fabricated on a 0.22- $\mu m$  process.) EPF10K200S and EPF10K50S devices offer the ClockLock and ClockBoost features.

In addition to the 600-pin BGA and 672-pin FineLine BGA packages already offered for EPF10K200E devices, EPF10K200S devices will be offered in the 240-pin RQFP, 356-pin BGA, and 484-pin FineLine BGA packages. EPF10K50S devices will be available in the same packages as the EPF10K50E device. Advanced support for EPF10K200S and EPF10K50S devices is available in the MAX+PLUS II software version 9.24.

# Software Support for New FLEX 10KE Packages

Altera is offering many new device-package combinations, including 1.27-mm BGA packages and cost efficient quad flat pack (QFP) packages. Advanced software support is shown in Table 2. You can obtain software updates from the Altera web site at http://www.altera.com.

| Table 2. FLEX 10KE Device Software Support |                      |                                    |  |  |

|--------------------------------------------|----------------------|------------------------------------|--|--|

| Device                                     | Package              | MAX+PLUS II<br>Software<br>Version |  |  |

| EPF10K50S                                  | 356-pin BGA          | 9.23                               |  |  |

| EPF10K130E                                 | 356-pin BGA          | 9.23                               |  |  |

| EPF10K130E                                 | 600-pin BGA          | 9.23                               |  |  |

| EPF10K200S                                 | 240-pin RQFP         | 9.24                               |  |  |

| EPF10K200S                                 | 356-pin BGA          | 9.25                               |  |  |

| EPF10K200S                                 | 484-pin FineLine BGA | 9.25                               |  |  |

#### **FLEX 10K Device Availability**

With the introduction of EPF10K50V devices in 484-pin FineLine BGA packages, all FLEX® 10KA devices have been introduced. Table 3 shows the expected availability of all 2.5-V FLEX 10KE devices. MAX+PLUS® II design support is currently available for all device package options.

#### **FLEX 10K Product Transitions**

Altera is migrating selected 3.3-V FLEX 10KA devices from a 0.35-µm process to a 0.30-µm

process. Additionally, selected 5.0-V FLEX 10K devices are moving from a 0.50-µm process to a 0.42-µm process. Table 4 outlines the process migration schedule and lists the reference documentation associated with this migration. You can download these documents from the Customer Notifications page on the Altera web site at http://www.altera.com.

#### **FLEX 10KE Industrial-Temperature Devices**

Table 5 lists the availability of industrialtemperature FLEX 10KE devices.

| Device     | Package (1)  | Speed<br>Grade | Availability<br>(2) |

|------------|--------------|----------------|---------------------|

| EPF10K30E  | 144-pin TQFP | -1, -2, -3     | July                |

|            | 208-pin PQFP | -1, -2, -3     | July                |

|            | 256-pin FBGA | -1, -2, -3     | August              |

|            | 484-pin FBGA | -1, -2, -3     | August              |

| EPF10K50E  | 144-pin TQFP | -1, -2, -3     | Now                 |

|            | 208-pin PQFP | -1, -2, -3     | Now                 |

|            | 240-pin PQFP | -1, -2, -3     | Now                 |

|            | 256-pin FBGA | -1, -2, -3     | Now                 |

|            | 356-pin BGA  | -1, -2, -3     | August              |

|            | 484-pin FBGA | -1, -2, -3     | Now                 |

| EPF10K50S  | 144-pin TQFP | -1, -2, -3     | July                |

|            | 208-pin PQFP | -1, -2, -3     | July                |

|            | 240-pin PQFP | -1, -2, -3     | July                |

|            | 256-pin FBGA | -1, -2, -3     | September           |

|            | 356-pin BGA  | -1, -2, -3     | August              |

|            | 484-pin FBGA | -1, -2, -3     | August              |

| EPF10K100E | 208-pin PQFP | -1, -2, -3     | Now                 |

|            | 240-pin PQFP | -1, -2, -3     | Now                 |

|            | 256-pin FBGA | -1, -2, -3     | June                |

|            | 356-pin BGA  | -1, -2, -3     | June                |

|            | 484-pin FBGA | -1, -2, -3     | June                |

| EPF10K130E | 240-pin PQFP | -1, -2, -3     | Now                 |

|            | 356-pin BGA  | -1, -2, -3     | June                |

|            | 484-pin FBGA | -1, -2, -3     | June                |

|            | 600-pin BGA  | -1, -2, -3     | June                |

|            | 672-pin FBGA | -1, -2, -3     | June                |

| EPF10K200E | 599-pin PGA  | -1, -2, -3     | Now                 |

|            | 600-pin BGA  | -1, -2, -3     | Now                 |

|            | 672-pin FBGA | -1, -2, -3     | Now                 |

| EPF10K200S | 240-pin RQFP | -1, -2, -3     | June                |

|            | 356-pin BGA  | -1, -2, -3     | August              |

|            | 484-pin FBGA | -1, -2, -3     | August              |

|            | 600-pin BGA  | -1, -2, -3     | August              |

|            | 672-pin FBGA | -1, -2, -3     | August              |

Notes:

(1) FBGA: FineLine BGA packages.

(2) All dates refer to calendar-year 1999.

#### Devices & Tools

#### FLEX 10KE Devices Available with PLLs

FLEX 10KE devices will be offered with the PLL feature in -1 and -2 speed grades. These devices will have a "-X" suffix (e.g., EPF10K200EBC600-1X). Table 6 lists the availability of FLEX 10KE devices with PLLs.

| Table 4. FLEX 10K Device Migration |                        |                 |                      |                 |

|------------------------------------|------------------------|-----------------|----------------------|-----------------|

| Device                             | Core<br>Voltage<br>(V) | Date            | Reference            | Process<br>(µm) |

| EPF10K10A                          | 3.3                    | July<br>1999    | PCN 9810             | 0.30            |

| EPF10K30A                          | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K50V                          | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K100A                         | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K10                           | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K20                           | 5.0                    | July<br>1999    | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K30                           | 5.0                    | July<br>1999    | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K40                           | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K50                           | 5.0                    | July<br>1999    | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K70                           | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K100                          | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| Table 5. FLEX 10KE | Industrial-Temperature | Device |

|--------------------|------------------------|--------|

| Availability       |                        |        |

| Device            | Availability |

|-------------------|--------------|

| EPF10K50ETI144-2  | Now          |

| EPF10K50EQI240-2  | Now          |

| EPF10K50EFI256-2  | Now          |

| EPF10K50SQI208-2  | Q3 1999      |

| EPF10K50SBI356-2  | Q3 1999      |

| EPF10K50SFI484-2  | Q3 1999      |

| EPF10K100EQI208-2 | Q3 1999      |

| EPF10K100EFI256-2 | Q3 1999      |

| EPF10K100EFI484-2 | Q3 1999      |

| EPF10K130EQI240-2 | Now          |

| EPF10K130EBI356-2 | Q3 1999      |

| EPF10K130EFI484-2 | Q3 1999      |

| EPF10K200EBI600-2 | Now          |

| EPF10K200SRI240-2 | Q3 1999      |

| EPF10K200SBI356-2 | Q3 1999      |

| EPF10K200SFI672-2 | Q3 1999      |

# Industrial-Temperature FLEX 6000 Devices Available

Altera provides a broad range of FLEX 6000 devices in industrial-temperature grades. Seven device package combinations are shipping in a variety of packages, including TQFP, PQFP, and BGA packages. Table 7 lists available industrialtemperature grade FLEX 6000 devices.

#### FineLine BGA Packages Coming Soon for FLEX 6000 Devices

FLEX 6000 devices in FineLine BGA packages are planned to be available in August 1999. These area-efficient packages require less than half the board space of traditional BGA packages. Table 8 on page 10 shows FLEX 6000 device expected availability.

| Table 6. FLEX 10KE Devices with PLLs |                                                                          |                |  |  |

|--------------------------------------|--------------------------------------------------------------------------|----------------|--|--|

| Device                               | Package (1)                                                              | Availability   |  |  |

| EPF10K30E                            | 144-pin TQFP, 208-pin PQFP,<br>256-pin FBGA, 484-pin FBGA                | August<br>1999 |  |  |

| EPF10K50S                            | 144-pin TQFP, 208-pin PQFP, 240-pin PQFP, 356-pin BGA                    | August<br>1999 |  |  |

|                                      | 256-pin FBGA, 484-pin FBGA                                               | Sept. 1999     |  |  |

| EPF10K100E                           | 208-pin PQFP, 240-pin PQFP                                               | July 1999      |  |  |

|                                      | 256-pin FBGA, 356-pin BGA,<br>484-pin FBGA                               | August<br>1999 |  |  |

| EPF10K130E                           | 240-pin PQFP, 356-pin BGA,<br>484-pin FBGA, 600-pin BGA,<br>672-pin FBGA | August<br>1999 |  |  |

| EPF10K200S                           | 240-pin RQFP, 356-pin BGA,<br>484-pin FBGA, 600-pin BGA,<br>672-pin FBGA | Sept. 1999     |  |  |

Note:

(1) FBGA: FineLine BGA packages.

| Table 7. Industrial-Temperature FLEX 6000 Device<br>Availability |              |              |  |  |

|------------------------------------------------------------------|--------------|--------------|--|--|

| Device                                                           | Package      | Availability |  |  |

| EPF6016TI144-3                                                   | 144-pin TQFP | Now          |  |  |

| EPF6016QI208-3                                                   | 208-pin PQFP | Now          |  |  |

| EPF6016ATI100-2                                                  | 100-pin TQFP | Now          |  |  |

| EPF6016ATI144-3                                                  | 144-pin TQFP | Now          |  |  |

| EPF6016AQI208-3                                                  | 208-pin PQFP | Now          |  |  |

| EPF6024AQI208-3                                                  | 208-pin PQFP | Now          |  |  |

| EPF6024ABI256-2                                                  | 256-pin BGA  | Now          |  |  |

continued on page 10

FLEX 10KE devices will be offered with the PLL feature in -1 and -2 speed grades.

| Package              | Device      |              |              |              |

|----------------------|-------------|--------------|--------------|--------------|

|                      | EPF6010A    | EPF6016      | EPF6016A     | EPF6024A     |

| 100-pin TQFP         | ~           |              | $\checkmark$ |              |

| 100-pin FineLine BGA | August 1999 |              | August 1999  |              |

| 144-pin TQFP         | ~           | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 208-pin PQFP         |             | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 240-pin PQFP         |             | $\checkmark$ |              | $\checkmark$ |

| 256-pin BGA          |             | $\checkmark$ |              | $\checkmark$ |

| 256-pin FineLine BGA | August 1999 |              | August 1999  | August 1999  |

#### Devices & Tools, continued from page 9

#### MAX 7000A Device Availability

All MAX 7000A devices are now available. MAX 7000A devices range from 32 to 512 macrocells with propagation delays as fast as 4.5 ns. MAX 7000A devices support ISP, MultiVolt I/O pins, hot-socketing, and pin compatibility with the industry-standard MAX 7000 devices. All MAX 7000A devices are available in industrial-temperature grades. Table 10 shows MAX 7000A device commercial package and speed grade options.

#### Table 10. MAX 7000A Commercial-Temperature **Device Packages**

| Device    | Package              | Speed Grade      |

|-----------|----------------------|------------------|

| EPM7032AE | 44-pin PLCC          | -4, -7, -10      |

|           | 44-pin TQFP          | -4, -7, -10      |

| EPM7064AE | 44-pin PLCC          | -4, -7, -10      |

|           | 44-pin TQFP          | -4, -7, -10      |

|           | 100-pin TQFP         | -4, -7, -10      |

|           | 100-pin FineLine BGA | -4, -7, -10      |

| EPM7128A  | 84-pin PLCC          | -6, -7, -10, -12 |

|           | 100-pin TQFP         | -6, -7, -10, -12 |

|           | 100-pin FineLine BGA | -6, -7, -10, -12 |

|           | 144-pin TQFP         | -6, -7, -10, -12 |

|           | 256-pin FineLine BGA | -6, -7, -10, -12 |

| EPM7128AE | 84-pin PLCC          | -5, -7, -10      |

|           | 100-pin TQFP         | -5, -7, -10      |

|           | 100-pin PQFP         | -5, -7, -10      |

|           | 144-pin TQFP         | -5, -7, -10      |

|           | 256-pin FineLine BGA | -5, -7, -10      |

| EPM7256A  | 100-pin TQFP         | -7, -10, -12     |

|           | 144-pin TQFP         | -7, -10, -12     |

|           | 208-pin PQFP         | -7, -10, -12     |

|           | 256-pin FineLine BGA | -7, -10, -12     |

| EPM7256AE | 100-pin TQFP         | -6, -7, -10      |

|           | 100-pin FineLine BGA | -6, -7, -10      |

|           | 144-pin TQFP         | -6, -7, -10      |

|           | 208-pin PQFP         | -6, -7, -10      |

|           | 256-pin FineLine BGA | -6, -7, -10      |

| EPM7512AE | 144-pin TQFP         | -7, -10, -12     |

|           | 208-pin PQFP         | -7, -10, -12     |

|           | 256-pin BGA          | -7, -10, -12     |

|           | 256-pin FineLine BGA | -7, -10, -12     |

#### New MAX 7000B Device

The new MAX 7000B devices are 2.5-V, product-term-based programmable logic devices (PLDs). The devices support new I/O standards, such as Gunning transceiver logic (GTL+), stub-series terminated logic-

### MAX

#### MAX 7000S Device Availability

All MAX® 7000S devices are now available. These devices feature speed grades of 5 ns, insystem programmability (ISP), an open-drain output option, and IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry in devices with 128 or more macrocells. All MAX 7000S devices are available in industrial-temperature grades. Table 9 shows the packages and speed grades available in the commercial-temperature grade.

| Device   | Package      | Speed Grade      |

|----------|--------------|------------------|

| EPM7032S | 44-pin PLCC  | -5, -6, -7, -10  |

|          | 44-pin TQFP  | -5, -6, -7, -10  |

| EPM7064S | 44-pin PLCC  | -5, -6, -7, -10  |

|          | 44-pin TQFP  | -5, -6, -7, -10  |

|          | 84-pin PLCC  | -5, -6, -7, -10  |

|          | 100-pin TQFP | -5, -6, -7, -10  |

| EPM7128S | 84-pin PLCC  | -6, -7, -10, -15 |

|          | 100-pin TQFP | -6, -7, -10, -15 |

|          | 100-pin PQFP | -6, -7, -10, -15 |

|          | 160-pin PQFP | -6, -7, -10, -15 |

| EPM7160S | 84-pin PLCC  | -6, -7, -10      |

|          | 100-pin TQFP | -6, -7, -10      |

|          | 160-pin PQFP | -6, -7, -10      |

| EPM7192S | 160-pin PQFP | -7, -10, -15     |

| EPM7256S | 208-pin PQFP | -7, -10, -15     |

| Table 9. Commercial-Temperature | MAX | 7000S |

|---------------------------------|-----|-------|

| Device Packages                 |     |       |

Devices & Tools

(SSTL-) 2, and SSTL-3, offer propagation delays as fast as 3.5 ns, and range in density from 32 to 512 macrocells (see Table 11). MAX 7000B devices support ISP, MultiVolt I/O pins, hot socketing, and pin compatibility with the industry-standard MAX 7000 devices.

Table 11. MAX 7000B Commercial-Temperature

| Device Packages |                      |             |  |

|-----------------|----------------------|-------------|--|

| Device          | Package              | Speed Grade |  |

| EPM7032B        | 44-pin PLCC          | -3, -5, -7  |  |

|                 | 44-pin TQFP          | -3, -5, -7  |  |

| EPM7064B        | 44-pin PLCC          | -3, -5, -7  |  |

|                 | 44-pin TQFP          | -3, -5, -7  |  |

|                 | 100-pin FineLine BGA | -3, -5, -7  |  |

|                 | 100-pin TQFP         | -3, -5, -7  |  |

| EPM7128B        | 100-pin FineLine BGA | -4, -7, -10 |  |

|                 | 100-pin TQFP         | -4, -7, -10 |  |

|                 | 144-pin TQFP         | -4, -7, -10 |  |

|                 | 256-pin FineLine BGA | -4, -7, -10 |  |

| EPM7256B        | 100-pin FineLine BGA | -5, -7, -10 |  |

|                 | 100-pin TQFP         | -5, -7, -10 |  |

|                 | 144-pin TQFP         | -5, -7, -10 |  |

|                 | 208-pin PQFP         | -5, -7, -10 |  |

|                 | 256-pin FineLine BGA | -5, -7, -10 |  |

| EPM7512B        | 144-pin TQFP         | -6, -7, -10 |  |

|                 | 208-pin PQFP         | -6, -7, -10 |  |

|                 | 256-pin FineLine BGA | -6, -7, -10 |  |

#### **New MAX 3000A Devices**

The MAX 3000A device family is a new 3.3-V product-term-based PLD family targeted for high-volume, low-cost applications. The devices have enhanced support for ISP and densities from 32 to 256 macrocells (see Table 12). With propagation delays as fast as 4.5 ns, MAX 3000A devices provide customers with the highest performance at the lowest price per macrocell.

| Table 12. MAX 3000A Devices |              |             |  |  |

|-----------------------------|--------------|-------------|--|--|

| Device                      | Package      | Speed Grade |  |  |

| EPM3032A                    | 44-pin PLCC  | -4, -7, -10 |  |  |

|                             | 44-pin TQFP  | -4, -7, -10 |  |  |

| EPM3064A                    | 44-pin PLCC  | -4, -7, -10 |  |  |

|                             | 44-pin TQFP  | -4, -7, -10 |  |  |

|                             | 100-pin TQFP | -4, -7, -10 |  |  |

| EPM3128A                    | 100-pin TQFP | -5, -7, -10 |  |  |

|                             | 144-pin PQFP | -5, -7, -10 |  |  |

| EPM3256A                    | 144-pin TQFP | -6, -7, -10 |  |  |

|                             | 208-pin PQFP | -6, -7, -10 |  |  |

### TOOLS

#### **Download the Quartus Preview Today**

For an early look at Altera's fourth-generation design software for System-on-a-Programmable-Chip<sup>™</sup> solutions, visit the Altera web site at http://www.altera.com and download the Quartus Preview. The Quartus Preview presents self-running demos of the Quartus software's latest features.

The Quartus Preview demonstrates the seamless integration of the NativeLink<sup>™</sup> feature and accelerated verification process using the SignalTap<sup>™</sup> embedded logic analyzer. You can also see the ease of submitting a service request to Altera Applications directly from the Quartus software, the first fully Internet-aware PLD software. As device densities increase, design methodologies for PLDs must continue to evolve. Download the Quartus Preview to see first-hand how the Quartus software is reshaping programmable logic design.

#### **New Quartus Simulator Features**

The Quartus Simulator has several new features, including support for testbenches. The new Simulator supports both waveform entry (which provides compatibility with existing MAX+PLUS II simulation files) and testbench entry.

You can set multiple time bars in the Waveform Editor. The Quartus Simulator supports nine different signal level values (1, 0, X, U, Z, H, L, W, and DC).

The new Node Finder allows users to create customized filters to extract nodes from the post-synthesis or floorplan netlist, making it easy to locate nodes. The Node Finder can also add output pins to Vector Waveform Files (.vwf) and check the output values against expected values at the end of simulation.

#### continued on page 12

#### Devices & Tools, continued from page 11

#### **Quartus Static Timing Analyzer Features**

The Quartus static Timing Analyzer has several new features.

- Multi-clock frequency analysis allows you to analyze timing for designs containing register-to-register paths that are controlled by different clocks.

- The ability to detect combinatorial loops drastically reduces the analysis times of designs that contain combinatorial loops.

- The Timing Analyzer can display either the system  $f_{MAX}$  or the internal  $f_{MAX}$ . The system  $f_{MAX}$  has the ability to include delays to the device.

- Timing for critical paths can be broken down into data path, clock path, and setup time. Each delay path can also be broken down into increments.

- You can perform pin-to-pin or combinatorial timing analysis. This process is analogous to the delay matrix in the MAX+PLUS II software.

#### **Quartus License Files**

If you have a current software subscription, you will automatically receive the Quartus software when it is released. However, you may need a new license file to enable the software.

To ensure a smooth transition for the release of the Quartus software, in April 1999, the Altera web-based license server started issuing license files that enable both the MAX+PLUS II and

Figure 1. Example License File

Quartus software to all users with a current software subscription. If your license.dat file has a Quartus FEATURE line, your license will enable the Quartus software. Figure 1 shows a sample license file that enables both the Quartus and MAX+PLUS II software.

If you have a current software subscription, you can obtain a new license file that enables both the Quartus and MAX+PLUS II software from the Altera web-based license server at http://www.altera.com.

#### MAX+PLUS II BASELINE Version 9.23 Now Available

The MAX+PLUS II BASELINE software version 9.23 includes a full-featured functional and timing gate-level simulator, making it the industry's complete free PLD development software. The software is available for free download from the Altera web site at http://www.altera.com.

The MAX+PLUS II BASELINE software version 9.23 supports a wide range of programmable logic devices including EPF10K10, EPF10K10A, EPM9320, EPM9320A, EPF8452A, EPF8282A, EPF6010A, EPF6016, EPF6016A, MAX 7000, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000AE, MAX 5000, and Classic devices. Features supported include schematic and text-based (AHDL) design entry; full-featured timing simulation, and static timing analysis. It is an ideal development tool for low- to mid-density programmable logic design.

| 🖹 license                 | .dat - Notepad                                                                                        | × |

|---------------------------|-------------------------------------------------------------------------------------------------------|---|

| <u>F</u> ile <u>E</u> dit | <u>S</u> earch <u>H</u> elp                                                                           |   |

| FEATURE                   | maxplus2 alterad 2030.12 permanent uncounted 23A6AE84AD45 \<br>HOSTID=GUARD_ID=T000001297             |   |

| FEATURE                   | quartus alterad 2030.12 permanent uncounted F1B39D3CC049 \<br>HOSTID=GUARD_ID=T000001297              |   |

| FEATURE                   | maxplus2verilog alterad 2030.12 permanent uncounted \<br>E73C33913CAC H0STID=GUARD_ID=T000001297      |   |

| FEATURE                   | <pre>maxplus2vhd1 alterad 2030.12 permanent uncounted FA4FDD712B01 \ H0STID=GUARD_ID=T000001297</pre> | ▽ |

| 4                         | 1                                                                                                     |   |

# Technical Articles

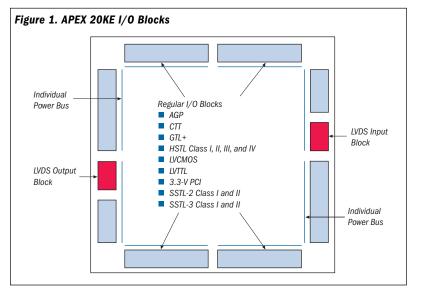

## Simplified Designs through Selectable I/O Standards

High-performance, low-voltage I/O standards have been introduced into the market to keep pace with increasing clock speeds and new lowvoltage levels. These I/O standards must support memory, microprocessors, backplanes, and peripheral devices. Designers who want to use these new standards with programmable logic need flexible, high-performance, multi-standard I/O buffers. Altera's revolutionary APEX<sup>TM</sup> 20KE devices meet this challenge by providing the highest density, highest performance programmable logic solution with the necessary I/O standards for the communication and computer industries.

With the new programmable I/O standards supported by APEX 20KE devices, a single device can interface with high-speed, lowvoltage memory buses and backplanes at up to 622-MBPS data rates. APEX 20KE devices are the first programmable logic devices (PLDs) to support the low-voltage differential signaling (LVDS) standard. Combined with the highest densities available, APEX devices are the perfect programmable solution.

Programmable I/O standards help simplify your board design. For example, you do not need dedicated devices such as LVDS drivers to interface APEX PLDs to backplanes.

#### Supported APEX 20KE I/O Standards

APEX 20KE I/O blocks support 17 I/O standards. The APEX 20KE I/O buffers meet the voltage, drive strength, and AC characteristics necessary to comply with the I/O standards listed in Table 1.

| Table 1. APEX 20KE Supported I/O Standards |                    |                                     |                                                       |                                                         |  |

|--------------------------------------------|--------------------|-------------------------------------|-------------------------------------------------------|---------------------------------------------------------|--|

| I/O Standard (1)                           | Туре               | Reference Voltage<br>(VREF) (V) (2) | Output Supply Voltage<br>(V <sub>CCIO</sub> ) (V) (2) | Board Termination<br>Voltage (V <sub>TT</sub> ) (V) (2) |  |

| LVTTL                                      | Single-ended       | N/A                                 | 3.3                                                   | N/A                                                     |  |

| LVCMOS                                     | Single-ended       | N/A                                 | 3.3                                                   | N/A                                                     |  |

| 2.5 V                                      | Single-ended       | N/A                                 | 2.5                                                   | N/A                                                     |  |

| 1.8 V                                      | Single-ended       | N/A                                 | 1.8                                                   | N/A                                                     |  |

| PCI                                        | Single-ended       | N/A                                 | 3.3                                                   | N/A                                                     |  |

| LVDS                                       | Differential       | N/A                                 | 3.3                                                   | N/A                                                     |  |

| GTL+                                       | Open-drain         | 1.0                                 | N/A                                                   | 1.5                                                     |  |

| SSTL-2 Class I and II                      | Voltage referenced | 1.25                                | 2.5                                                   | 1.25                                                    |  |

| SSTL-3 Class I and II                      | Voltage referenced | 1.5                                 | 3.3                                                   | 1.5                                                     |  |

| HSTL Class I                               | Voltage referenced | 0.75                                | 1.5                                                   | 0.75                                                    |  |

| HSTL Class II                              | Voltage referenced | 0.75                                | 1.5                                                   | 0.75                                                    |  |

| HSTL Class III                             | Voltage referenced | 0.9                                 | 1.5                                                   | 0.9                                                     |  |

| HSTL Class IV                              | Voltage referenced | 0.9                                 | 1.5                                                   | 0.9                                                     |  |

| AGP                                        | Voltage referenced | 1.32                                | 3.3                                                   | N/A                                                     |  |

| CTT                                        | Voltage referenced | 1.5                                 | 3.3                                                   | 1.5                                                     |  |

Notes:

AGP: advanced graphics port, CTT: center-tap-terminated, GTL+: Gunning transceiver logic, HSTL: high-speed transceiver logic, LVCMOS: low-voltage complementary metal-oxide semiconductor, LVTTL: low-voltage transistor-to-transistor logic, PCI: peripheral component interconnect, SSTL: stub-series terminated logic.

(2) The values shown for  $V_{REF}$ ,  $V_{CCIO}$ , and  $V_{TT}$  are typical values.

continued on page 14

With the new programmable I/O standards supported by APEX 20KE devices, a single device can interface with highspeed, low-voltage memory buses and backplanes.

#### Simplified Designs through Selectable I/O Standards, continued from page 13

APEX 20KE devices have six programmable I/O blocks and two dedicated LVDS I/O blocks. The LVDS I/O blocks can also support any other I/O standard. Figure 1 shows the representation of the I/O blocks.

The programmable I/O blocks have individual power planes with separate VCCIO pins for each I/O block. Each VCCIO plane supports 3.3-V, 2.5-V, or 1.8-V levels.

#### LVDS

The LVDS I/O standard is a high-speed, lowvoltage swing, low-power, general-purpose I/O interface standard that is independent of process and architecture. LVDS requires a differential input, but does not need an input reference voltage. Typical uses for LVDS interfaces are high-bandwidth data transfer, backplane driver, and clock distribution applications.

Two key industry standards define LVDS: IEEE Std. 1596.3 SCI-LVDS and ANSI/TIA/EIA-644. Both standards have similar key features, but the IEEE standard supports a maximum data transfer of 250 MBPS. APEX 20KE devices are designed to meet the ANSI/TIA/EIA-644 standard at up to 622 MBPS.

#### Conclusion

Altera remains the programmable solutions leader by offering devices that meet designers' needs. The I/O standards and features allow programmers to interface APEX 20KE devices directly with microprocessors, memory devices, and backplanes, without using interface logic. This process saves board space, decreases timeto-market, and increases profits.

# **CAM Accelerates Applications in APEX Devices**

Because CAM is embedded inside APEX 20KE devices, it provides faster system performance than traditional discrete CAM. Most memory devices store and retrieve data by addressing specific memory locations. Searching for an item in memory can take many clock cycles. The time required to find an item stored in memory can be reduced if it can be identified for access by the data content, rather than its address. Content-addressable memory (CAM) works in this way, making it ideal for high-speed search applications. Altera® APEX<sup>TM</sup> 20KE devices contain integrated blocks of CAM.

#### **CAM Integration**

Traditionally, most applications have used discrete CAM, in which the CAM is

implemented as an individual device. A designer who wanted to use CAM had to add a CAM device to their printed circuit board (PCB), which increased design time and reduced the amount of useable PCB space. Discrete CAM also reduced system performance because it introduced additional on-chip and off-chip delays.

APEX 20KE devices, which contain on-chip CAM, eliminate the disadvantages of discrete CAM. Because CAM is embedded inside APEX 20KE devices, it provides faster system performance than traditional discrete CAM.

#### Using APEX 20KE CAM

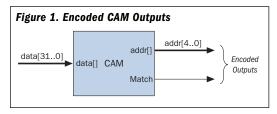

Each embedded system block (ESB) in APEX 20KE devices can implement 32-word × 32-bit CAM. CAM searches all data in parallel and flags the address in which a particular word is stored.

CAM can be pre-loaded with data during configuration, or it can be written during system operation. A design can write "don't care" bits into words of the CAM; bits set to "don't care" do not affect matching.

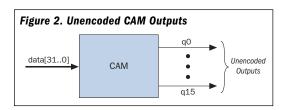

Output from CAM is either encoded or unencoded. The ESB can output an encoded address of the data location, which is better suited for designs without duplicate data in the memory. Reading this type of output only takes one clock cycle. See Figure 1.

If it is necessary for duplicate data to be written to multiple locations, an unencoded output should be used. In this mode, an ESB uses 16 outputs and reads the outputs in two cycles, 16 bits at each cycle, for a 32-bit word line. Each output represents one word of the CAM and goes high if the data matches that word of the CAM. See Figure 2.

#### **CAM Applications**

CAM is used to optimize telecommunications, file-storage management, table look-up, pattern recognition, and other applications. This section describes how APEX CAM can be used in the following applications:

- Data Compression

- Network Switches

- Internet Protocol Filters

- PCI Applications

#### Data Compression

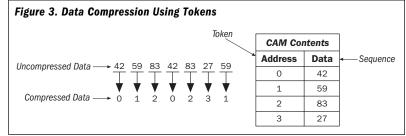

Data compression removes redundancy in a piece of information, producing an equivalent but shorter message (see Figure 3). CAM lookup is performed after each word is presented. If the specific code is not found in the CAM, another word is shifted in. When the code is found, the CAM outputs the appropriate symbol and the input register is flushed. CAM generates a result in a single transaction regardless of the table size or length of the search list. CAM is used to optimize telecommunications, file-storage management, table look-up, pattern recognition, and other applications.

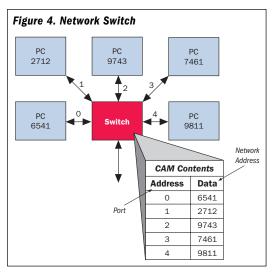

#### Switch Applications

CAM is used in switch applications to extract and process the address information from incoming packets. To switch a packet to the correct outgoing port, the incoming network address is compared with a table of network addresses stored in CAM. CAM outputs the destination for each data packet. See Figure 4.

continued on page 17

## **Hierarchical Instantiation Organizes Your Design**

This article is the last of a four-part series that discusses practical design tips from Altera Applications, and focuses on the importance of hierarchical instantiation. Hierarchical instantiation plays a particularly large role in VHDL designs and large digital designs. You should consider using a hierarchical design methodology to maximize your design's effectiveness and to focus your project.

Hierarchical instantiation involves dividing projects into an extensive tree of smaller design entities. Each entity has a specific purpose and a carefully declared method for interacting with other entities.

The principal benefit of hierarchical instantiation is organization. Each block serves a specific purpose and can be considered its own entity, allowing designers to focus on one design functionality at a time. This design technique also permits a high-level view of the design's overall structure, making it easier to uncover critical paths and potential trouble spots.

#### **Labor Division**

Well-divided projects lend themselves to proper labor division. Designers must often split a project between multiple engineers, and welldefined barriers can ease this task. Designers can easily separate projects and assign sections for individual attention.

#### **Documentation & Revision Control**

The organized nature of hierarchical designs creates key benefits in documentation and revision control. Individual, well-focused modules lead to the creation of complete documentation describing each block's functionality and how it interfaces with others. Thorough documentation also aids the debugging process and helps bring new engineers up to speed quickly. Revision control is also improved, because each change serves a well-defined purpose and can be carefully monitored and fully documented.

#### **Error Detection**

Hierarchical instantiation can facilitate error detection in assembled projects. Simulated nodes are easier to find because they can be referenced by their hierarchical location. Critical paths in timing analysis also stand out, especially within parallel modules that are instantiated in multiple locations.

#### **Hierarchical Methodologies**

Two fundamental design practices critical to hierarchical design include top-down design and bottom-up design methodology. Both methodologies contain their own strengths and break large designs into more manageable pieces. The best designs often use a mixture of these two design methodologies.

#### Top-Down Designs

Top-down designs start with a high-level understanding of a design's overall flow. Each design block's general functionality is described prior to developing the building blocks themselves. Top-down methodologies tend to create more organized designs, because designers must first evaluate the design's overall structure. In addition, by focusing on structure and leaving details of a design undefined, designers can delay technical considerations until they are at more manageable levels.

#### Bottom-Up Designs

In a bottom-up methodology, designers first create the lower-level blocks and then integrate these blocks into higher-level structures. Designers focus their attention on individual sub-blocks rather than the design as a whole. Thus, individual blocks can be verified prior to building the entire design.

Bottom-up designs also highlight the benefits of reusable code. Splitting projects into smaller modules helps designers find redundant sections in a project. Designers can then reuse individual blocks of code, which saves time. In addition, designers can assemble commonly used functions into their regular design library, allowing blocks of code to be reused from project to project.

Re-useable code also lends itself to more efficient synthesis, as seen in the third article of this series, *Using Arithmetic Operators in MAX+PLUS II VHDL*. In that example, the careful placement of multiplexers allowed the use of one adder module where two might have been required otherwise. However, if the adder was not located in an instantiated block, it would have been difficult to discern this optimization.

Finally, parameterizable code can enhance design reuse. By creating parameterizable code, specific blocks can be targeted for multiple uses in the same design. This ability is what makes library of parameterized modules (LPM) functions, as well as numerous Altera functions, so effective.

For more information on creating an effective hierarchical design, contact Altera Applications at **sos@altera.com** or at (800) 800-EPLD. Designers can assemble commonly used functions into their regular design library, allowing blocks of code to be reused from project to project.

# CAM Accelerates Applications in APEX Devices, continued from page 15

#### Internet Protocol Filters

An Internet protocol filter is a security feature that allows you to keep unauthorized users from accessing local-area network (LAN) resources. The feature can also restrict Internet protocol traffic over a wide-area network (WAN) link. With an Internet protocol filter, LAN users can be restricted to specific applications on the Internet (such as e-mail). CAM works as a filter to block all access except for packets that have permission. The addresses with certain permissions are written into the CAM; when the address is sent to the memory, CAM reports whether it contains the address. If the address resides within CAM, it has permission for a particular activity. See Figure 5.

#### PCI Applications

On power-up, the peripheral component interconnect (PCI) bus must be configured so that each device's I/O and memory functions occupy mutually exclusive address ranges. Therefore, the system must be able to detect

#### Figure 5. Using CAM as an IP Filter

| CAM Col | ntents |               |            |

|---------|--------|---------------|------------|

| Address | Data   | Routed Packet | Permission |

| 0       | 01     | 27            | Permit     |

| 1       | 27     | ЗA            | Permit     |

| 2       | ЗA     | 4F            | Denied     |

| 3       | 4D     | 25            | Denied     |

how many memory and I/O address ranges a device requires and the size of each. The base address registers permit this relocation and provide a mechanism for mapping devices into address spaces. Each interface can have up to six registers. CAM can be used to report which register is being accessed. Using CAM for a PCI application speeds up the register search, while using fewer logic elements (LEs).

#### **CAM Speeds Applications**