# MAX 7000B Devices Provide Solutions for High-Performance Applications

The feature-rich, product-term-based MAX<sup>®</sup> 7000B devices offer propagation delays as fast as 3.5 ns and support for advanced I/O standards such as Gunning transceiver logic plus (GTL+). These features make MAX 7000B devices ideal for high-performance applications such as telecommunications switches, highdensity storage systems, and medical imaging equipment. The devices range in density from 32 to 512 macrocells and feature 2.5-V insystem programmability (ISP) and Jam<sup>TM</sup> Standard Test and Programming Language (STAPL), JEDEC standard JESD-71 support. MultiVolt<sup>TM</sup> I/O operation allows MAX 7000B devices to interface with 1.8-V, 2.5-V, and 3.3-V devices. Table 1 compares MAX 7000 device features.

#### **High Performance**

MAX 7000B devices offer propagation delays (t<sub>PD</sub>) as fast as 3.5 ns. At such fast speeds, MAX 7000B devices can implement counters operating at frequencies in excess of 200 MHz. With peripheral component interconnect (PCI)-compatible, high-performance devices across the entire product family, MAX 7000B devices are ideal for a variety of high-speed applications ranging from address decoding to complex control circuits.

continued on page 4

| Table 1. MAX 7000 Performance Enhancements Over Time |              |              |              |                       |  |

|------------------------------------------------------|--------------|--------------|--------------|-----------------------|--|

| Feature                                              | MAX 7000     | MAX 7000S    | MAX 7000A    | MAX 7000B             |  |

| Macrocell Range                                      | 32 to 256    | 32 to 256    | 32 to 512    | 32 to 512             |  |

| Supply Voltage                                       | 5.0 V        | 5.0 V        | 3.3 V        | 2.5 V                 |  |

| Fastest <b>t<sub>PD</sub></b>                        | 7.5 ns       | 5.0 ns       | 4.5 ns       | 3.5 ns                |  |

| MultiVolt I/O                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ | ✓                     |  |

| ISP Support                                          |              | $\checkmark$ | $\checkmark$ | ✓                     |  |

| Hot Socketing                                        |              |              | $\checkmark$ | <ul> <li>✓</li> </ul> |  |

| FineLine BGA and 0.8-mm<br>BGA Packaging             |              |              | ~            | ~                     |  |

| Advanced I/O Standards                               |              |              |              | <ul> <li>✓</li> </ul> |  |

| Year of Introduction                                 | 1991         | 1995         | 1998         | 1999                  |  |

# 64-Bit, 66-MHz PCI Master/Target Core

- 64-Bit, 66-MHz Peripheral Component Interconnect (PCI)-Compliant Solution with APEX<sup>™</sup> 20K and FLEX<sup>®</sup> 10KE Devices

- Up to 528-Mbytes/Second Throughput

- 64-Bit Addressing

- Up to Six Base Address Registers (BARs)

- Compact PCI Hot-Swap

- Host Bridge Support

## **100% PCI-Compliant Solutions**

| MegaCore Solutions | ;                                                                                                                                                                 |                         |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Megafunction       | Features                                                                                                                                                          | Logic Elements Utilized |

| PCI/C              | 64-Bit, 66-MHz PCI Compliant, Master/Target Interface, Up to 528-Mbytes/Second Throughput, Zero-Wait-State Master and Target                                      | 1,200                   |

| PCI/B              | 32-Bit, 33-MHz Master/Target Interface, Supports Host Bridge<br>Applications, Independent Master and Target Operations, Up to<br>132-Mbytes/Second Read and Write | 1,050                   |

| PCI/A              | 32-Bit, 33-MHz Master/Target Interface, Integrated DMA and EAB Buffer, Zero Wait-State                                                                            | 1,050                   |

| PCIT1              | 32-Bit, 33-MHz Burst Target Only Interface, Zero Wait-State,<br>Type Zero Configuration Space                                                                     | 550                     |

# Test-drive the megafunction before purchase with the OpenCore<sup>™</sup> feature from the Altera web site.

# http://www.altera.com/IPmegastore

# Table of Contents

#### Features

| MAX 7000B Devices Provide Solutions for |     |

|-----------------------------------------|-----|

| High-Performance Applications           | . 1 |

| Customer Application: Altera PLDs Allow |     |

| GENICOM to Out-Print Competition        | 23  |

#### Altera News

| Design Automatic | on Conference | 1999:      |       |

|------------------|---------------|------------|-------|

| Where Tools &    | Design Metho  | dology Mee | et 25 |

#### **Devices & Tools**

| EP20K100 & EP20K200 Devices Now Availab    | ole 6 |

|--------------------------------------------|-------|

| New APEX Family Members                    | 6     |

| PLLs in APEX Devices                       | 7     |

| Newest 0.22-µm FLEX 10KE Devices           | 7     |

| FLEX 10K Device Availability               | 7     |

| FLEX 10K Product Transitions               | 8     |

| FLEX 10KE Industrial-Temperature Devices   | 8     |

| FLEX 6000 FineLine BGA Package Support     | 8     |

| MAX 7000B Devices                          |       |

| MAX 7000A Devices                          | 9     |

| MAX 7000S Devices                          |       |

| MAX 3000A Devices                          | 9     |

| Expanded Support for EPC2                  |       |

| Configuration Device                       | 10    |

| Obtain a License File that Enables Quartus |       |

| Version 1999.06 Software                   | 10    |

|                                            |       |

| Quartus Software is Now Shipping 10       |

|-------------------------------------------|

| Quartus Operating System Support          |

| Quartus System Requirements               |

| Help Using the Quartus Software 11        |

| MAX+PLUS II Version 9.3 Software          |

| Reduces Compilation Times 11              |

| MAX+PLUS II BASELINE Version 9.3 Software |

| Expands Device Support 12                 |

| Discontinued Devices Update               |

#### **Technical Articles**

| FIR Compiler Speeds Design Cycles              | 3 |

|------------------------------------------------|---|

| Implementing Programmable Product              |   |

| Terms with CAM15                               | 5 |

| Faster Programming Times with the              |   |

| HP 3070 Tester 17                              | 7 |

| Developing Tcl Scripts for Quartus Software 19 | 9 |

| Verifying PLD Designs Using SmartModels 21     | 1 |

| Questions & Answers                            |   |

#### In Every Issue

| Current Software Versions     | 5  |

|-------------------------------|----|

| New Altera Publications       | 12 |

| Altera Programming Support    | 26 |

| How to Contact Altera         | 28 |

| Altera Device Selection Guide | 29 |

Altera, APEX, APEX 20K, ACCESS, AMPP, BitBlaster, ByteBlaster, ByteBlaster, MV, Classic, ClockBoost, ClockLock, ClockShift, CoreSyn, EPC2, FastTrack, FineLine BGA, FLEX, FLEX 10KE, FLEX 10KE, FLEX 10KA, FLEX 8000, FLEX 6000, FLEX 6000A, Jam, MasterBlaster, MAX 9000, MAX 9000A, MAX 7000, MAX 7000E, MAX 7000S, MAX 7000A, MAX 7000AE, MAX 7000B, MAX 5000, MAX 3000, MAX 3000A, MAX, MAX+PLUS, MAX+PLUS II, MegaCore, MegaLAB, MegaWizard, MultiCore, MultiVolt, NativeLink, nSTEP, OpenCore, Quartus, SignaTTap, System-on-a-Programmable-Chip, and specific device designations are trademarks and/or services marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks, of other organizations for their respective products or services mentioned in this document, specifically: GENICOM Corporation and GENICOM are registered trademarks, and microLaser 320 is a trademark of GENICOM Corporation. Microsoft and Windows are registered trademarks of Microsoft Corporation. Rochester Electronics is a registered trademark of Solaris is a trademark of Microsoft Corporation. Rochester Electronics is a registered trademark of Synopsys, Inc. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any while herein except and before the except as expressly agreed to device specifications before relying on any

published information and before placing orders for products are avoided using the actual availability of Altera's products and features could differ from those projected in this publication and are provided solely as an estimate to the reader.

Copyright © 1999 Altera Corporation. All rights reserved.

Ken Lau, Publisher Greg Steinke, Technical Editor

Technical Editor 101 Innovation Drive San Jose, CA 95134 Tel: (408) 544-7000 Fax: (408) 544-7809 n v@altera.com

August 1999

News & Views Altera Corporation

rate control.

#### MAX 7000B Devices Provide Solutions for High-Performance Applications, continued from page 1

#### Advanced I/O Interface Standard Support

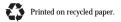

Figure 1 shows the MAX 7000B I/O blocks. Each of the two I/O blocks can be configured separately, allowing multiple I/O standards on programmable slewthe same device. MAX 7000B devices are the product-term leader in I/O standard support, and are the only product-term-based devices to support the following I/O standards:

- GTL+

- Stub series terminated logic, 2.5 V (SSTL-2) Class I. II

- SSTL-3, Class I, II

Altera® MAX 7000B devices also support the following I/O standards:

- 64-bit, 66-MHz PCI applications

- Low-voltage transistor-to-transistor logic (LVTTL)

- Low-voltage CMOS (LVCMOS)

#### Feature Rich

Altera MAX 7000B devices offer ISP. Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry, and support for Jam STAPL, which is a vendor-independent JEDEC-approved language. MAX 7000B devices also provide paths to migrate to higher densities in the same package. Table 2 shows vertical migration available for the MAX 7000B family. Users can migrate their designs between check-marked devices in the same column.

MAX 7000B device features include global clocking, fast input registers, and programmable slew-rate control. A programmable powersaving feature allows 50% or greater power reduction in each macrocell. High-speed global clocks, 3.5-ns propagation delays, and fast setup times create superior system performance with high-speed device-to-device communication. Advanced support for MAX 7000B devices is available in the MAX+PLUS<sup>®</sup> II version 9.3 software. Table 3 lists MAX 7000B features.

#### State-of-the-Art Packaging Solutions

Altera MAX 7000B devices are available in innovative FineLine BGA<sup>™</sup> and 0.8-mm BGA

| Table 2. MAX 70 | 000B PIn M     | igration       |                |                         |                            |                 |                 |                          |                 |                            |                |

|-----------------|----------------|----------------|----------------|-------------------------|----------------------------|-----------------|-----------------|--------------------------|-----------------|----------------------------|----------------|

| Device          |                | Package        |                |                         |                            |                 |                 |                          |                 |                            |                |

|                 | 44-Pin<br>PLCC | 44-Pin<br>TQFP | 48-Pin<br>TQFP | 49-Pin<br>0.8-mm<br>BGA | 100-Pin<br>FineLine<br>BGA | 100-Pin<br>TQFP | 144-Pin<br>TQFP | 169-Pin<br>0.8-mm<br>BGA | 208-Pin<br>PQFP | 256-Pin<br>FineLine<br>BGA | 256-Pin<br>BGA |

| EPM7032B        | $\checkmark$   | $\checkmark$   | $\checkmark$   |                         |                            |                 |                 |                          |                 |                            |                |

| EPM7064B        | $\checkmark$   | $\checkmark$   | $\checkmark$   | $\checkmark$            | $\checkmark$               | $\checkmark$    |                 |                          |                 |                            |                |

| EPM7128B        | $\checkmark$   | $\checkmark$   | $\checkmark$   |                         | $\checkmark$               | $\checkmark$    | $\checkmark$    | $\checkmark$             |                 | $\checkmark$               | $\checkmark$   |

| EPM7256B        |                |                |                |                         |                            | $\checkmark$    | $\checkmark$    |                          | $\checkmark$    | $\checkmark$               | $\checkmark$   |

| EPM7512B        |                |                |                |                         |                            | $\checkmark$    | $\checkmark$    |                          | $\checkmark$    | $\checkmark$               | $\checkmark$   |

#### MAX 7000B device *features include global* clocking, fast input registers, and

packages. These 1.0-mm and 0.8-mm ball pitch packages are ideal for space-constrained designs. FineLine BGA and 0.8-mm BGA packages are available with the SameFrame<sup>™</sup> pin-out feature, which provides footprint compatibility between packages with different ball counts. This layout feature permits easy migration from one FineLine BGA package to another FineLine BGA package, or one 0.8-mm BGA package to another 0.8-mm BGA package, without the need to redesign the board.

#### Support for High-Performance Applications

With fast timing and support for multiple I/O interfacing standards, MAX 7000B devices provide high-performance, product-term-based solutions in the smallest possible board space. Features such as ISP, low-power modes, and state-of-the-art packaging make these MAX devices ideal for a variety of applications.

These 1.0-mm and 0.8-mm ball pitch packages are ideal for space-constrained designs.

| Feature                  | EPM7032B    | EPM7064B                                | EPM7128B                                                                         | EPM7256B                | EPM7512B                |

|--------------------------|-------------|-----------------------------------------|----------------------------------------------------------------------------------|-------------------------|-------------------------|

| Usable gates             | 600         | 1,250                                   | 2,500                                                                            | 5,000                   | 10,000                  |

| Macrocells               | 32          | 64                                      | 128                                                                              | 256                     | 512                     |

| Maximum user I/O<br>pins | 36          | 68                                      | 100                                                                              | 164                     | 212                     |

| t <sub>PD</sub> (ns)     | 3.5         | 3.5                                     | 4.5                                                                              | 5.0                     | 6.0                     |

| f <sub>CNT</sub> (MHz)   | 200         | 200                                     | 192                                                                              | 178.6                   | 147.1                   |

| Packages (1)             | 44-pin PLCC | 44-pin PLCC                             | 44-pin PLCC                                                                      | 100-pin TQFP            | 100-pin TQFP            |

|                          | 44-pin TQFP | 44-pin TQFP                             | 44-pin TQFP                                                                      | 144-pin TQFP            | 144-pin TQFP            |

|                          | 48-pin TQFP | 48-pin TQFP                             | 48-pin TQFP                                                                      | 208-pin PQFP            | 208-pin PQFP            |

|                          |             | 49-pin<br>0.8-mm BGA                    | 49-pin<br>0.8-mm BGA                                                             | 256-pin<br>FineLine BGA | 256-pin<br>FineLine BGA |

|                          |             | 100-pin TQFP<br>100-pin<br>FineLine BGA | 100-pin TQFP<br>100-pin<br>FineLine BGA<br>144-pin TQFP<br>169-pin<br>0.8-mm BGA | 256-pin BGA             | 256-pin BGA             |

|                          |             |                                         | 256-pin<br>FineLine BGA<br>256-pin BGA                                           |                         |                         |

#### Note:

(1) PLCC: plastic J-lead chip carrier; PQFP: plastic quad flat pack; TQFP: thin quad flat pack.

### **Current Software Versions**

The Quartus<sup>™</sup> version 1999.06 software is currently available for the Microsoft Windows 98, Windows NT 4.0, and Sun Solaris 2.6 operating systems. The Quartus version 1999.06 software will be available for the HP-UX operating system in the fourth quarter of 1999.

The MAX+PLUS<sup>®</sup> II version 9.3 software is currently available for the following operating systems:

- Microsoft Windows 95 and Windows 98

- Microsoft Windows NT version 3.51 and higher

- Sun Solaris version 2.5 and higher

- HP-UX version 10.20 and higher; however, HP-UX version 11.0 and higher are not yet supported

- AIX version 4.1 and higher

### APEX

# EP20K100 & EP20K200 Devices Now Available

Two new APEX<sup>TM</sup> devices, the 100,000-gate (263,000 maximum system gates) EP20K100 device and the 200,000-gate (526,000 maximum system gates) EP20K200 device, are now available. EP20K100 devices are available in 144-pin thin quad flat pack (TQFP), 208-pin plastic quad flat pack (PQFP), and 240-pin PQFP packages. EP20K200 devices, with 8,320 logic elements (LEs) and 106,496 bits of on-chip RAM, are available in 208-pin and 240-pin power quad flat pack (RQFP) packages. EP20K100 and EP20K200 devices are also offered in 1.27-mm ball-grid array (BGA) packages and 1.0-mm FineLine BGA<sup>™</sup> packages that support SameFrame<sup>™</sup> migration. For the latest information on APEX devices, see the Altera<sup>®</sup> web site at http://www.altera.com.

Tables 1 and 2 list the APEX 20K and APEX 20KE software support schedules. All 2.5-V APEX 20K devices are now available. The first 1.8-V APEX 20K device, the EP20K400E device, will be available in September 1999, followed by the EP20K600E in November 1999.

| Table 1. A<br>Support A | PEX 20K Devices & Q<br>vailability | uartus Software                  |  |  |

|-------------------------|------------------------------------|----------------------------------|--|--|

| Device                  | Package                            | Software Support<br>Availability |  |  |

| EP20K100                | 144-pin TQFP                       | Now                              |  |  |

|                         | 196-pin FineLine BGA               | October 1999                     |  |  |

|                         | 208-pin PQFP                       | Now                              |  |  |

|                         | 240-pin PQFP                       | Now                              |  |  |

|                         | 324-pin FineLine BGA               | Now                              |  |  |

|                         | 356-pin BGA                        | October 1999                     |  |  |

| EP20K200                | 208-pin RQFP                       | Now                              |  |  |

|                         | 240-pin RQFP                       | Now                              |  |  |

|                         | 356-pin BGA                        | October 1999                     |  |  |

|                         | 484-pin FineLine BGA               | Now                              |  |  |

| EP20K400                | 652-pin BGA                        | Now                              |  |  |

|                         | 655-pin PGA                        | Now                              |  |  |

|                         | 672-pin FineLine BGA               | Now                              |  |  |

#### **New APEX Family Members**

Two new devices, the 1.5-million-gate EP20K1500E device and the 60,000-gate EP20K60E device, have been added to the

| Device     | Package              | Software                |  |  |

|------------|----------------------|-------------------------|--|--|

|            |                      | Support<br>Availability |  |  |

| EP20K60E   | 144-pin TQFP         | October 1999            |  |  |

|            | 196-pin FineLine BGA | October 1999            |  |  |

|            | 208-pin PQFP         | October 1999            |  |  |

|            | 240-pin PQFP         | October 1999            |  |  |

|            | 324-pin FineLine BGA | October 1999            |  |  |

|            | 356-pin BGA          | October 1999            |  |  |

| EP20K100E  | 144-pin TQFP         | Now                     |  |  |

|            | 196-pin FineLine BGA | October 1999            |  |  |

|            | 208-pin PQFP         | Now                     |  |  |

|            | 240-pin PQFP         | Now                     |  |  |

|            | 324-pin FineLine BGA | Now                     |  |  |

|            | 356-pin BGA          | October 1999            |  |  |

| EP20K160E  | 144-pin TQFP         | October 1999            |  |  |

|            | 208-pin PQFP         | October 1999            |  |  |

|            | 240-pin PQFP         | October 1999            |  |  |

|            | 356-pin BGA          | October 1999            |  |  |

|            | 484-pin FineLine BGA | October 1999            |  |  |

| EP20K200E  | 208-pin PQFP         | Now                     |  |  |

|            | 240-pin PQFP         | Now                     |  |  |

|            | 356-pin BGA          | October 1999            |  |  |

|            | 484-pin FineLine BGA | Now                     |  |  |

|            | 652-pin BGA          | October 1999            |  |  |

|            | 672-pin FineLine BGA | October 1999            |  |  |

| EP20K300E  | 208-pin RQFP         | October 1999            |  |  |

|            | 240-pin RQFP         | October 1999            |  |  |

|            | 652-pin BGA          | October 1999            |  |  |

|            | 672-pin FineLine BGA | October 1999            |  |  |

| EP20K400E  | 652-pin BGA          | Now                     |  |  |

|            | 672-pin FineLine BGA | Now                     |  |  |

| EP20K600E  | 652-pin BGA          | Now                     |  |  |

|            | 672-pin FineLine BGA | Now                     |  |  |

|            | 1,020-pin            | October 1999            |  |  |

|            | FineLine BGA         |                         |  |  |

| EP20K1000E | 652-pin BGA          | October 1999            |  |  |

|            | 672-pin FineLine BGA | October 1999            |  |  |

|            | 984-pin PGA          | October 1999            |  |  |

|            | 1,020-pin            | October 1999            |  |  |

|            | FineLine BGA         |                         |  |  |

| EP20K1500E | 652-pin BGA          | February 2000           |  |  |

|            | 984-pin PGA          | February 2000           |  |  |

|            | 1,020-pin            | February 2000           |  |  |

|            | FineLine BGA         |                         |  |  |

٦

APEX device offerings. The EP20K1500E device offers 2,524,416 maximum system gates, and contains 54,720 LEs and 466,944 bits of on-chip RAM. EP20K1500E devices will be introduced in the second quarter of 2000. EP20K60E devices, which contain 2,560 LEs and 32,768 bits of on-chip RAM, will be introduced at the same time.

#### **PLLs in APEX Devices**

APEX devices have a phase-locked loop (PLL) capability, designated with an "X" suffix in the ordering code (e.g., EP20K400BC652-1X). All -1X and -2X speed grade APEX devices will contain the ClockLock<sup>™</sup> and ClockBoost<sup>™</sup> options, which reduce clock delay and skew and perform internal clock multiplications of 1×, 2×, and 4×, allowing for simpler board designs. APEX 20KE devices have up to four PLLs per device and also support the ClockShift<sup>™</sup> feature, enabling programmable delays and phase shifting. The APEX 20K PLL option is currently supported by the Quartus software.

### FLEX

#### Newest 0.22-µm FLEX 10KE Devices

The newest FLEX® 10KE devices are now on a 0.22-µm, 5-layer-metal process and are loaded with features. These devices, which include EPF10K30E, EPF10K50S, EPF10K100E, EPF10K130E, and EPF10K200S devices, contain all FLEX 10KE features, such as a programmable delay, to provide full 64-bit, 66-MHz PCI compliance, and a PLL in -1 and -2 speed grades.

The MAX+PLUS<sup>®</sup> II version 9.3 software currently supports all FLEX 10KE devices, including the PLL feature, and will be sent to customers with a current software subscription. You can obtain software updates from the Altera web site at http://www.altera.com.

#### FLEX 10K Device Availability

MAX+PLUS II design support is available now for all 2.5-V FLEX 10KE device/package

combinations, as shown in Table 3. This includes FLEX 10KE devices in -1 and -2 speed grades offered with the ClockLock feature, and designated with an "X" suffix (e.g., EPF10K100EQC240-1X).

| Device     | Package            | Speed<br>Grade | Software<br>Support<br>Availability |

|------------|--------------------|----------------|-------------------------------------|

| EPF10K30E  | 144-pin TQFP       | -1, -2, -3     | Now                                 |

|            | 208-pin PQFP       | -1, -2, -3     | Now                                 |

|            | 256-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       |                |                                     |

|            | 484-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       |                |                                     |

|            | PLL (all packages) | -1X, -2X       | Now                                 |

| EPF10K50S  | 144-pin TQFP       | -1, -2, -3     | Now                                 |

|            | 208-pin PQFP       | -1, -2, -3     | Now                                 |

|            | 240-pin PQFP       | -1, -2, -3     | Now                                 |

|            | 256-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       |                |                                     |

|            | 356-pin BGA        | -1, -2, -3     | Now                                 |

|            | 484-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       |                |                                     |

|            | PLL (all packages) | -1X, -2X       | Now                                 |

| EPF10K100E | 208-pin PQFP       | -1, -2, -3     | Now                                 |

|            | 240-pin PQFP       | -1, -2, -3     | Now                                 |

|            | 256-pin            |                |                                     |

|            | FineLine BGA       | -1, -2, -3     | Now                                 |

|            | 356-pin BGA        | -1, -2, -3     | Now                                 |

|            | 484-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       |                |                                     |

|            | PLL (all packages) | -1X,-2X        | Now                                 |

| EPF10K130E | 240-pin PQFP       | -1, -2, -3     | Now                                 |

|            | 356-pin BGA        | -1, -2, -3     | Now                                 |

|            | 484-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       |                |                                     |

|            | 600-pin BGA        | -1, -2, -3     | Now                                 |

|            | 672-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       | 11 01          | New                                 |

|            | PLL (all packages) | -1X, -2X       | Now                                 |

| EPF10K200S |                    | -1, -2, -3     | Now                                 |

|            | 356-pin BGA        | -1, -2, -3     | Now                                 |

|            | 484-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       | 1 0 0          | New                                 |

|            | 600-pin BGA        | -1, -2, -3     | Now                                 |

|            | 672-pin            | -1, -2, -3     | Now                                 |

|            | FineLine BGA       | 14 24          | Now                                 |

|            | PLL (all packages) | -1X, -2X       | NOW                                 |

continued on page 8

FLEX

#### Devices & Tools, continued from page 7

#### FLEX 10K Product Transitions

Selected 3.3-V FLEX 10KA devices are migrating from a 0.35-µm process to a 0.30-µm process, and all 5.0-V FLEX 10K devices are moving from a 0.50-µm process to a 0.42-µm process. EPF10K50E and EPF10K200E devices are migrating from a 0.25-µm process to a 0.22-µm process. Table 4 outlines the process migration schedule and lists the reference documentation associated with this migration. You can

| Table 4. FLEX 10K Device Migration |                        |                 |                      |                 |

|------------------------------------|------------------------|-----------------|----------------------|-----------------|

| Device                             | Core<br>Voltage<br>(V) | Date            | Reference            | Process<br>(µm) |

| EPF10K10A                          | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K30A                          | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K50V                          | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K100A                         | 3.3                    | Done            | PCN 9810             | 0.30            |

| EPF10K10                           | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K20                           | 5.0                    | Done            | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K30                           | 5.0                    | Done            | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K40                           | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K50                           | 5.0                    | Done            | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K70                           | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K100                          | 5.0                    | October<br>1999 | PCN 9901<br>ADV 9909 | 0.42            |

| EPF10K50E                          | 2.5                    | Q4<br>1999      | PCN 9911             | 0.22            |

| EPF10K200E                         | 2.5                    | Q4<br>1999      | PCN 9911             | 0.22            |

download these documents from the Customer Notifications page on the Altera web site at http://www.altera.com.

#### FLEX 10KE Industrial-Temperature Devices

Table 5 lists the expected availability of industrial-temperature FLEX 10KE devices.

# Table 5. FLEX 10KE Industrial-TemperatureDevices & MAX+PLUS II Software SupportAvailability

| Device            | Software Support<br>Availability |

|-------------------|----------------------------------|

| EPF10K50ETI144-2  | Now                              |

| EPF10K50EQI240-2  | Now                              |

| EPF10K50EFI256-2  | Now                              |

| EPF10K50SQI208-2  | Now                              |

| EPF10K50SBI356-2  | Now                              |

| EPF10K50SFI484-2  | Now                              |

| EPF10K100EQI208-2 | Now                              |

| EPF10K100EFI256-2 | Now                              |

| EPF10K100EFI484-2 | Now                              |

| EPF10K130EQI240-2 | Now                              |

| EPF10K130EBI356-2 | Now                              |

| EPF10K130EFI484-2 | Now                              |

| EPF10K200EBI600-2 | Now                              |

| EPF10K200SRI240-2 | Now                              |

| EPF10K200SBI356-2 | Now                              |

| EPF10K200SFI672-2 | Now                              |

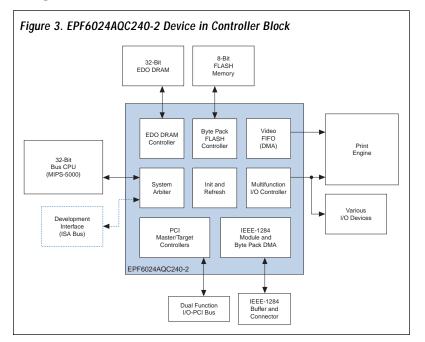

#### FLEX 6000 FineLine BGA Package Support

Support for FLEX 6000 devices in area-efficient FineLine BGA packages is available now in the MAX+PLUS II version 9.3 software. Selected FLEX 6000 FineLine BGA devices are currently available. Table 6 shows FLEX 6000 device expected availability.

|                    |                        |            |                | <u> </u> |

|--------------------|------------------------|------------|----------------|----------|

| Table 6 FLEX 60    | 000 Device Availabilit | ' & MAX+PI | US II Software | Support  |

| 10010 01 1 22/1 00 | ooo borroo mamabini    |            |                | cappone  |

| Package              |          | De      | vice     |          |

|----------------------|----------|---------|----------|----------|

|                      | EPF6010A | EPF6016 | EPF6016A | EPF6024A |

| 100-pin TQFP         | Now      |         | Now      |          |

| 100-pin FineLine BGA |          |         | Now      |          |

| 144-pin TQFP         | Now      | Now     | Now      | Now      |

| 208-pin PQFP         |          | Now     | Now      | Now      |

| 240-pin PQFP         |          | Now     |          | Now      |

| 256-pin BGA          |          | Now     |          | Now      |

| 256-pin FineLine BGA |          |         | Now      | Now      |

Selected 3.3-V FLEX 10KA devices are migrating from a 0.35-µm process to a 0.30-µm process

MAX

### MAX

#### MAX 7000B Devices

2.5-V MAX<sup>®</sup> 7000B devices range from 32 to 512 macrocells with propagation delays ( $t_{PD}$ ) as fast as 3.5 ns. MAX 7000B devices support advanced I/O standards such as Gunning transceiver logic plus (GTL+), stub series terminated logic for 2.5 V (SSTL-2), and SSTL-3. These devices also feature enhanced insystem programmability (ISP), MultiVolt<sup>TM</sup> I/O pins, hot socketing, and pin compatibility with the industry-standard MAX 7000 devices.

#### MAX 7000A Devices

All MAX 7000A devices are now available. 3.3-V MAX 7000A devices have propagation delays as fast as 4.5 ns and range from 32 to 512 macrocells. These devices support enhanced ISP, MultiVolt I/O pins, and hot socketing, and are pin compatible with the industry-standard MAX 7000 devices. All MAX 7000A devices are available in both industrial- and commercialtemperature grades. Table 7 shows MAX 7000AE device commercial package and speed grade options.

#### MAX 7000S Devices

5.0-V MAX 7000S devices are all available and feature 5-ns speed grades, ISP, an open-drain output option, and IEEE Std. 1149.1 Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry in devices with 128 or more macrocells. All MAX 7000S devices are available in both industrial- and commercial-temperature grades. Table 8 shows the packages and speed grades available in the commercial-temperature grade.

#### MAX 3000A Devices

The 3.3-V MAX 3000A devices are targeted for high-volume, low-cost designs. These devices have an enhanced ISP feature set and range in density from 32 to 256 macrocells (see Table 9 on page 10). With propagation delays as fast as 4.5 ns, MAX 3000A devices provide exceptional performance at the lowest price per macrocell among Altera MAX products.

| Device    | Package              | Speed Grade  |

|-----------|----------------------|--------------|

| EPM7032AE | 44-pin PLCC          | -4, -7, -10  |

|           | 44-pin TQFP          | -4, -7, -10  |

| EPM7064AE | 44-pin PLCC          | -4, -7, -10  |

|           | 44-pin TQFP          | -4, -7, -10  |

|           | 49-pin 0.8-mm BGA    | -4, -7, -10  |

|           | 100-pin TQFP         | -4, -7, -10  |

|           | 100-pin FineLine BGA | -4, -7, -10  |

| EPM7128AE | 84-pin PLCC          | -5, -7, -10  |

|           | 100-pin TQFP         | -5, -7, -10  |

|           | 100-pin FineLine BGA | -5, -7, -10  |

|           | 144-pin TQFP         | -5, -7, -10  |

|           | 169-pin 0.8-mm BGA   | -5, -7, -10  |

|           | 256-pin FineLine BGA | -5, -7, -10  |

| EPM7256AE | 100-pin TQFP         | -5, -7, -10  |

|           | 100-pin FineLine BGA | -5, -7, -10  |

|           | 144-pin TQFP         | -5, -7, -10  |

|           | 208-pin PQFP         | -5, -7, -10  |

|           | 256-pin FineLine BGA | -5, -7, -10  |

| EPM7512AE | 144-pin TQFP         | -7, -10, -12 |

|           | 208-pin PQFP         | -7, -10, -12 |

|           | 256-pin BGA          | -7, -10, -12 |

|           | 256-pin FineLine BGA | -7, -10, -12 |

## Table 8. Commercial-Temperature MAX 7000SDevice Packages

| Device   | Package Speed Grade |                  |  |

|----------|---------------------|------------------|--|

| EPM7032S | 44-pin PLCC         | -5, -6, -7, -10  |  |

|          | 44-pin TQFP         | -5, -6, -7, -10  |  |

| EPM7064S | 44-pin PLCC         | -5, -6, -7, -10  |  |

|          | 44-pin TQFP         | -5, -6, -7, -10  |  |

|          | 84-pin PLCC         | -5, -6, -7, -10  |  |

|          | 100-pin TQFP        | -5, -6, -7, -10  |  |

| EPM7128S | 84-pin PLCC         | -6, -7, -10, -15 |  |

|          | 100-pin TQFP        | -6, -7, -10, -15 |  |

|          | 100-pin PQFP        | -6, -7, -10, -15 |  |

|          | 160-pin PQFP        | -6, -7, -10, -15 |  |

| EPM7160S | 84-pin PLCC         | -6, -7, -10      |  |

|          | 100-pin TQFP        | -6, -7, -10      |  |

|          | 160-pin PQFP        | -6, -7, -10      |  |

| EPM7192S | 160-pin PQFP        | -7, -10, -15     |  |

| EPM7256S | 208-pin PQFP        | -7, -10, -15     |  |

#### MAX 7000A devices have propagation delays as fast as 4.5 ns and range from 32 to 512 macrocells.

#### Devices & Tools, continued from page 9

| Table 9. MAX 3000A Devices |              |             |  |

|----------------------------|--------------|-------------|--|

| Device                     | Package      | Speed Grade |  |

| EPM3032A                   | 44-pin PLCC  | -4, -7, -10 |  |

|                            | 44-pin TQFP  | -4, -7, -10 |  |

| EPM3064A                   | 44-pin PLCC  | -4, -7, -10 |  |

|                            | 44-pin TQFP  | -4, -7, -10 |  |

|                            | 100-pin TQFP | -4, -7, -10 |  |

| EPM3128A                   | 100-pin TQFP | -5, -7, -10 |  |

|                            | 144-pin PQFP | -5, -7, -10 |  |

| EPM3256A                   | 144-pin TQFP | -6, -7, -10 |  |

|                            | 208-pin PQFP | -6, -7, -10 |  |

all communication you receive from Altera, including the quarterly *News & Views*. The ID is also available from the Quartus support web site at https://websupport.altera.com. You must have a current software subscription to receive the license file with the Quartus FEATURE line.

#### Quartus Software is Now Shipping

The Quartus version 1999.06 software is now shipping to all customers who have a current software subscription. With revolutionary features like SignalTap<sup>™</sup> logic analysis and NativeLink<sup>™</sup> integration with third-party EDA tools, the Quartus software truly enables System-on-a-Programmable-Chip<sup>™</sup> designs.

The Quartus version 1999.06 software supports the APEX 20K devices listed in Table 10.

### CONFIGURATION

# Expanded Support for EPC2 Configuration Device

The FLASH-based reprogrammable EPC2 configuration device is now offered in industrial-temperature grades in both 32-pin TQFP and 20-pin PLCC packages.

### TOOLS

# Obtain a License File that Enables Quartus Version 1999.06 Software

The Quartus version 1999.06 software requires a license file with a Quartus FEATURE line. You can request license files using Altera's web-based license generator at http://www.altera.com. You can also access Altera's web-based license generator directly from within the Quartus software.

You must provide your Altera ID in addition to either your software guard number, host ID, or NIC number to access the license file generator. Your Altera ID is printed on the mailing label of

## Table 10. Quartus Version 1999.06 Support forAPEX Devices

| Support         | Device    | Package                  |

|-----------------|-----------|--------------------------|

| Compilation and | EP20K100  | 144-pin TQFP             |

| Programming     |           | 208-pin PQFP             |

| Support         |           | 240-pin PQFP             |

|                 | EP20K200  | 208-pin RQFP             |

|                 |           | 240-pin RQFP             |

|                 | EP20K400  | 652-pin BGA              |

|                 |           | 655-pin PGA              |

|                 |           | 672-pin FineLine BGA     |

| Compilation     | EP20K100  | 324-pin FineLine BGA     |

| Support Only    | EP20K100E | 144-pin TQFP             |

|                 | (1)       | 208-pin PQFP             |

|                 |           | 240-pin PQFP             |

|                 |           | 324-pin FineLine BGA     |

|                 | EP20K200  | 484-pin FineLine BGA     |

|                 | EP20K200E | 208-pin RQFP             |

|                 |           | 240-pin RQFP             |

|                 |           | 484-pin FineLine BGA     |

|                 | EP20K400  | 652-pin BGA (2)          |

|                 |           | 672-pin FineLine BGA (2) |

|                 | EP20K400E | 652-pin BGA              |

|                 | (1)       | 672-pin FineLine BGA     |

|                 | EP20K600E | 652-pin BGA              |

|                 | (1)       | 672-pin FineLine BGA     |

Notes:

- The Quartus version 1999.06 software will only support the speed and density features of these devices.

- (2) Devices with the ClockLock feature are available in these packages.

#### Quartus Operating System Support

The initial Quartus software release version 1999.06 supports the operating systems listed in Table 11.

| Table 11. Quartus Operating System Support |                       |  |

|--------------------------------------------|-----------------------|--|

| Platform Operating System                  |                       |  |

| PC                                         | Windows NT/Windows 98 |  |

| UNIX                                       | Solaris (1)           |  |

|                                            | HP-UX (2)             |  |

Notes:

- (1) Version 2.6.

- (2) Support for the HP-UX operating system will be available in Q4 1999.

#### **Quartus System Requirements**

Table 12 lists the minimum system configuration requirements necessary to run the Quartus software on either a PC or UNIX operating system. In addition to the hardware listed in Table 12, the amount of RAM and hard drive swap space necessary varies with the density of the target APEX device. Table 13 lists the required RAM and additional hard drive swap space for different design densities.

| Table 12. Minimum Quartus System Requirements<br>(PC & UNIX Workstation) |                                                        |       |

|--------------------------------------------------------------------------|--------------------------------------------------------|-------|

| Platform                                                                 | latform System Minimum Hard<br>Drive Space<br>(Mbytes) |       |

| PC                                                                       | 400-MHz Pentium                                        | 750   |

| UNIX                                                                     | 300-MHz Ultra Sparc II                                 | 2,000 |

| Table 13. Device-Specific Quartus SystemRequirements (PC & UNIX Workstation) |                                             |                                                            |  |

|------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------|--|

| Target<br>APEX<br>Device                                                     | Minimum<br>Main Memory<br>(RAM)<br>(Mbytes) | Minimum Additional<br>Hard Drive<br>Swap Space<br>(Mbytes) |  |

| EP20K100<br>EP20K100E<br>EP20K200<br>EP20K200E                               | 256                                         | 256                                                        |  |

| EP20K400<br>EP20K400E<br>EP20K600E                                           | 512                                         | 512                                                        |  |

| EP20K1000E                                                                   | 1,024                                       | 1,024                                                      |  |

#### Help Using the Quartus Software

The Quartus software ships with manuals to allow you to get started on your multi-milliongate designs immediately. Additional documentation such as application notes and technical briefs are available for customers to learn more about the Quartus software. Table 14 lists some of the documentation available from the Altera web site or Altera Literature Services. Altera has introduced many new features with the Quartus software including SignalTap logic analysis, NativeLink support, and integration capabilities with revision control software. You can request additional documentation describing these and many other features of the Quartus software.

| Table 14. Quartus Documentation                                                     |                                                                                                                          |  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Document Title                                                                      | Description                                                                                                              |  |

| SignalTap Embedded Logic<br>Analyzer Megafunction Data<br>Sheet (A-DS-SIGNALTAP-01) | Description of the<br>SignalTap megafunction,<br>which is provided with the<br>Quartus software.                         |  |

| AN 118: Scripting with Tcl in<br>the Quartus Software<br>(A-AN-118-01)              | Explains how to develop<br>and run scripts in Tcl to<br>perform a wide range of<br>functions in the Quartus<br>software. |  |

| TB 51: Advantages of Quartus<br>Internet Integration<br>(M-TB-051-01)               | Brief overview of Quartus<br>Internet integration<br>capabilities.                                                       |  |

| TB 52: Increasing<br>Performance using ATOM<br>Netlist Files<br>(M-TB-052-01)       | Description of improved<br>results for designs<br>synthesized from third-<br>party tools into ATOM<br>netlists.          |  |

| TB 54: Quartus Revision<br>Control Software Support<br>(M-TB-054-01)                | Overview of the Quartus<br>software's abilities to<br>integrate with standard<br>revision control software<br>packages.  |  |

documentation such as application notes and technical briefs are available for customers to learn more about the Quartus software.

Additional

#### MAX+PLUS II Version 9.3 Software Reduces Compilation Times

MAX+PLUS II version 9.3 software compilation algorithms are optimized to speed up timingdriven compilation times. 70 designs were benchmarked for compilation times using the MAX+PLUS II software versions 9.2 and 9.3. These designs were compiled for the FLEX 10K device family, ranging in density from EPF10K20 to EPF10K250A devices. On average, compilation times for version 9.3 were onethird the times obtained with version 9.2. The registered performance did not vary significantly.

continued on page 12

#### Devices & Tools, continued from page 11

Timing-driven compilations with clock-tooutput delay ( $t_{CO}$ ) and clock setup time ( $t_{SU}$ ) assignments allow the MAX+PLUS II version 9.3 software to place appropriate registers in the I/O cells of the device. This capability significantly improves I/O performance for a design.

MAX+PLUS II version 9.3 software also offers a Jam Composer and Player that supports Jam Standard Test and Programming Language (STAPL), JEDEC standard JESD-71 format and full compilation support for over 30 new device/ package combinations, including 2.5-V MAX 7000B and 0.22-µm FLEX 10KE devices.

#### MAX+PLUS II BASELINE Version 9.3 Software Expands Device Support

MAX+PLUS II BASELINE version 9.3 software adds compilation support for EPF10K30, EPF10K30A, EPF10K30E, EPF6024A, MAX 7000B, and MAX 3000A devices. You can download the MAX+PLUS II BASELINE software for free from the Altera web site (http://www.altera.com), or install it from the Altera digital library (ADL) or MAX+PLUS II installation CD-ROM. A six-month license to enable the software is available from the Altera web site.

### **New Altera Publications**

New publications are available from Altera Literature Services. Individual documents are available on the Altera web site at http://www.altera.com. Document part numbers are shown in parentheses.

- Altera Digital Library CD-ROM, version 6 (P-CD-ADL-06)

- APEX 20K Programmable Logic Device Family Data Sheet (A-DS-APEX20K-02.01)

- FIR Compiler MegaCore Function User Guide (A-UG-FIRCOMPILER-01)

- Quartus Installation & Licensing for PCs (P25-04731-01)

- SignalTap User's Guide (P25-04733-00)

- AN 100: In-System Programmability Guidelines (A-AN-100-03)

- AN 107: Using Altera Devices in Multiple Voltage Systems (A-AN-107-01)

- AN 118: Scripting with Tcl in the Quartus Software (A-AN-118-01)

- AN 119: Implementing High-Speed Search Applications with APEX CAM (A-AN-119-01)

- SB 39: I<sup>2</sup>C Master Interface Megafunction (A-SB-039-01)

- SB 40: I<sup>2</sup>C Slave Interface Megafunction (A-SB-040-01)

- SB 41: FIR Compiler MegaCore Function (A-SB-041-01)

- SB 42: Interleaver/Deinterleaver MegaCore Function (A-SB-042-01)

- SB 44: 64-Bit PCI Master/Target MegaCore Function (A-SB-045-01)

- TB 51: Advantages of Quartus Internet Integration (M-TB-051-01)

- TB 53: Comparison of Quartus Software with Xilinx Alliance Series Version 2.1i Software (M-TB-053-01)

# Technical Articles

### FIR Compiler Speeds Design Cycles

Many communications systems use digital processing to remove unwanted noise, to provide spectral shaping for communications channels, or to perform signal detection and analysis. Finite impulse response (FIR) filters have an inherently stable structure and are used in many systems which require linear phase. Typical filter applications include signal preconditioning, band selection, and low-pass filtering.

The FIR compiler is the first complete digital signal processing (DSP) development tool in the programmable logic device (PLD) industry to boost the design cycle of high-performance FIR filters. The FIR compiler generates highly optimized FIR filter megafunctions and cycle accurate simulation models for system-level analysis tools (e.g., MATLAB, Simulink) and hardware description languages (HDL) for simulation (VHDL, Verilog HDL).

#### **FIR Filter Overview**

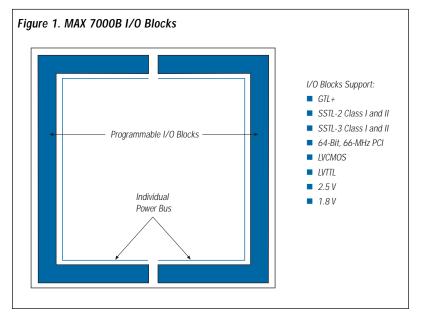

The filter design process involves identifying coefficients that match the frequency response specified for the system. The coefficients determine the structure of the filter. You can change which signal frequencies pass through the filter by changing the coefficient values or adding more coefficients. Figure 1 shows a diagram of a basic FIR filter.

A FIR filter design cycle has two main phases: system-level specification and hardware implementation. The number of taps (*N*) and the value of each coefficient are based on the system requirements such as the sample frequency, filter type, cut-off frequencies, stopband reject, and pass-band ripple. After defining the bus precision, the designer selects a device to which the function should be mapped. The FIR compiler allows the user to enter floating-point coefficients and perform the floating-to-fixedpoint conversion all within the tool. The user can select an architecture that is optimal for a

particular design. The FIR compiler provides a complete integration of these two phases. The user can optimize their design for either speed or area by adjusting a few parameters in the DSP designer.

#### High-Performance FIR Filter

When implementing the FIR filter in a traditional DSP processor, the amount of filter data throughput is shown in the following equation:

throughput =

$$\frac{\text{processor clock}}{N}$$

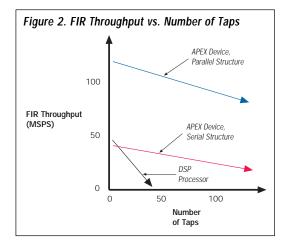

Therefore, high-performance filters that require a large number of taps are quickly limited by the data rates they can handle. However, with PLDs, the increase in filter length does not affect the throughput.

A fully parallel, pipelined FIR filter implemented in a PLD can operate at data rates above 100 megasamples per second (MSPS), making PLDs ideal for high-speed filtering applications. The FIR compiler offers multiple architectures, such as parallel or serial implementations; the designer can decide to

continued on page 14

# FIR Compiler Speeds Design Cycles, continued from page 13

trade resource usage for performance. The user can choose to have the design run faster or be more resource efficient, depending on the priority. Figure 2 illustrates the difference in performance between the different hardware architectures.

The FIR compiler takes advantage of the APEX MultiCore architecture to reduce resource usage while maintaining high throughput.

The FIR compiler creates FIR filters that run between 70 to 140 MHz. Depending on the options chosen, these implementations use a few hundred to several thousand logic cells. The FIR compiler takes advantage of the APEX<sup>™</sup> MultiCore<sup>™</sup> architecture to reduce resource usage while maintaining high throughput. For example, the FIR tap delay line is mapped to ESBs, and the multiplication and addition operations of the filter (e.g., the partial product and the adder tree) are mapped to look-up tables (LUTs).

#### **Design Entry**

The FIR compiler can import coefficient values from third-party DSP tools such as MATLAB, SPW, or COSSAP in floating point or fixed point format. You can use the FIR compiler MegaWizard plug-in (see Figure 3) to compute the floating-point value of the coefficients. The coefficient generator supports high pass, low pass, band pass, band reject, raised cosine, and root raised cosine filter types, as well as rectangular, Hamming, Hanning, and Blackman

#### Figure 3. Coefficient Generator Window

window types. The coefficient generator displays the frequency response of the filter based on the parameters.

The FIR compiler generates a system-level model for MATLAB Simulink (see Figure 4) as well as a HDL model for VHDL and Verilog HDL simulators.

#### Conclusion

The FIR compiler is highly optimized for Altera device architectures, and supports parallel or serial arithmetic architectures. The MegaWizard Plug-In allows the designer to easily design the filter and create MATLAB Simulink, VHDL, and Verilog HDL simulation models.

#### Figure 4. MATLAB Simulink Window

### Implementing Programmable Product Terms with CAM

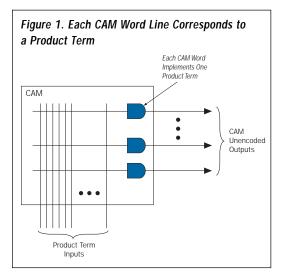

Content addressable memory (CAM) is memory accessed by its content rather than its address. CAM provides a performance advantage over other memory search algorithms, such as binary or tree-based searches or look-aside tag buffers, by comparing the desired information against the entire list of pre-stored entries simultaneously, often resulting in a large reduction in the search time. One application that takes advantage of CAM's fast searches is a programmable product term.

Each APEX<sup>TM</sup> 20KE embedded system block (ESB) can implement a 32-word × 32-bit CAM block. Within the ESB, each word in CAM corresponds to a product term (see Figure 1). Since CAM can be re-written during configuration or system operation, the product terms linked to each CAM line can be reprogrammed to perform different functions. The CAM output should be in an unencoded format so there is only one output per CAM word line. The unencoded outputs can use lookup tables (LUTs) to make combinatorial logic.

# Multi-Format Video Decoding Application with CAM

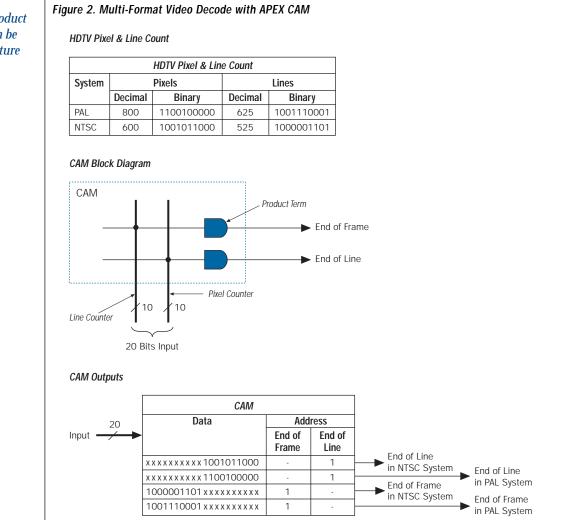

Programmable product terms in CAM can be used for multi-feature video decoding. In most broadcast video applications, a number of decodes from a set of master line and pixel counters are required to control the operation of the device or system. Traditionally, this function has been performed using a number of comparators and multiplexors. However, problems arise in systems that require a large number of decodes. In this instance, the number of required comparators becomes very large and can cause a performance bottleneck, especially at high-definition television (HDTV) clock rates.

The problem is further compounded if the device supports multiple formats; the number of decodes required is multiplied by the number of formats supported. For example, if a device requires 32 decodes from a mixture of line and pixel counters per format, it would require 96 decodes or comparators to support three formats. An alternative is to use dynamic comparators; the decode values are downloaded by the system's CPU when it switches from one format to another. The drawback is that dynamic comparators can consume many logic elements (LEs).

A better solution is to use APEX 20KE CAM to perform these decodes at very high speeds. Each CAM word line is a decode of the inputs (line and pixel counters). An unencoded output acts as a system or device decode, which controls the rest of the system or device. With unencoded outputs, each ESB reads 16 outputs in two cycles: 16 bits at each cycle to represent 32 words in the CAM block. (Although an ESB supports 32 input bits, only 31 input bits are used for data in unencoded output form; one input bit is used by the select line to choose one

continued on page 16

# Implementing Programmable Product Terms with CAM, continued from page 15

of the two 16-bit banks to output.) Figure 2 on page 18 shows how CAM can help to decode the incoming data and distinguish which format has been requested.

#### APEX CAM Advantages

APEX CAM provides other advantages. The design performance is improved, only limited by the CAM access time (4 ns). The printed circuit board (PCB) space used with APEX CAM is small and fixed compared to the dynamic decoder design. Additionally, CAM can be configured at system power-up with the default format's decode.

The use of programmable product terms can be extended to any design requiring a relatively large number of decodes, especially those requiring dynamically alterable decodes. Because CAM searches through its contents simultaneously, it can implement programmable product terms efficiently to improve a design. See *Application Note 119* (*Implementing High-Speed Search Applications* with APEX CAM) for more information on APEX CAM.

Programmable product terms in CAM can be used for multi-feature video decoding.

### Faster Programming Times with the HP 3070 Tester

#### Introduction

In-system programming has become a mainstream feature in programmable logic devices (PLDs), offering system designers and test engineers significant cost benefits by integrating PLDs into board-level testing. These benefits include reduced inventory of preprogrammed devices, lower costs, fewer devices damaged by handling, and increased flexibility in engineering changes. Altera<sup>®</sup> provides software and device support that integrates insystem programmability (ISP) into existing test flows for the HP 3070 system (ISP is occasionally referred to as "on-board programming"). This article discusses how to use the HP 3070 test system to achieve faster programming times for Altera devices that support ISP.

#### **Device Support**

In-system programming is achieved with either an adaptive or a constant (i.e., fixed) algorithm. Altera devices tested with a constant algorithm should be used when programming with HP 3070 systems. These devices are designated by an "F" suffix in the ordering code and are marked with an "F" in the bottom right-hand corner of the device. Table 1 shows which devices are supported when programming with the HP 3070 test system.

"F" devices allow programming hardware to program all devices from a set of pre-defined vectors. This process allows in-circuit testers, such as the HP 3070, to apply programming vectors in the simplest and fastest manner possible. In addition, fixed algorithm devices provide a uniform "beat-rate" (number of devices programmed per minute). Because these devices use the same algorithm and vector set, each device has the same programming time. This scenario is desirable in a production environment where a consistent, predictable beat-rate is necessary for smooth operation of the manufacturing line.

| Table 1. "F" Device Support for the HP 3070 Test<br>System |                    |  |

|------------------------------------------------------------|--------------------|--|

| Family Supported Devices                                   |                    |  |

| MAX 7000S                                                  | "F"                |  |

| MAX 7000A                                                  | MAX 7000AE         |  |

| MAX 7000AE                                                 | All Ordering Codes |  |

| MAX 9000, MAX 9000A                                        | "F"                |  |

#### HP 3070 Development Flow

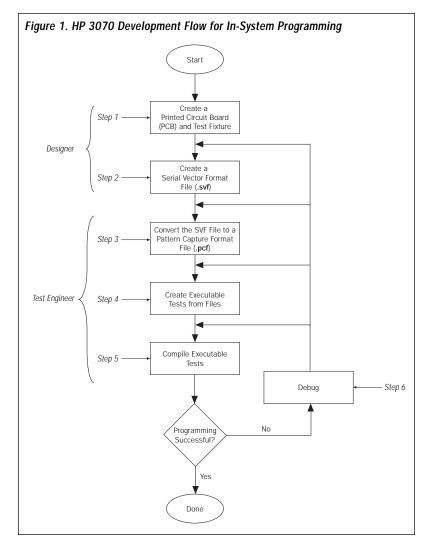

Programming devices with the HP 3070 tester requires several simple steps, which are not specific to an on-board programming flow. Rather, the flow is identical to the development of any other kind of test that requires a specific vector set. See Figure 1 on page 14.

The MAX+PLUS® II software tool makes generating Serial Vector Format Files (.svf) for every Joint Test Action Group (JTAG) device chain simple and straightforward. Once generated, the SVF File is converted to HP Pattern Capture Format File (.pcf) via the Altera svf2pcf utility. This utility can be downloaded from the Altera ftp site (ftp.altera.com) and supports both Windows and HP-UX operating systems.

Once the programming vectors are placed in the PCF format, the remaining flow is identical to any other test. For more detailed information on printed circuit board (PCB) layout, software flow, or debugging, see *Application Note 109* (Using the HP 3070 Tester for In-System Programming).

#### **Programming Times**

Programming times on the HP 3070 are very consistent; the only variable is the TCK frequency, which affects programming times. The faster the clock, the less time is spent

continued on page 18

The MAX+PLUS II software tool makes generating Serial Vector Format Files (.svf) for every Joint Test Action Group (JTAG) device chain simple and straightforward.

Faster Programming Times with the HP 3070 Tester, continued from page 17

shifting data into the device. *Application Note 85* (*In-System Programming Times for MAX Devices*) provides detailed programming time data for in-circuit testers.

The following example provides detailed data points from a specific test case. The data shown provides a general idea of the typical programming times that can be expected, as well as information on file sizes and resources utilized on the host workstation. In this example, four EPM7128SQC160-7F devices are programmed in a chain, using the HP 3070. An SVF File is generated targeting all four EPM7128S devices, and the test flow is used to convert the PCF Files into executable vectors. The results are shown in Tables 2 and 3.

#### Table 2. Data for Programming Four EPM7128SQC160-7F Devices

| Description                                         | Results                                  |

|-----------------------------------------------------|------------------------------------------|

| HP 3070 software revision                           | B.02.54                                  |

| Controller type                                     | 725/100                                  |

| Number of PCF Files created                         | 15                                       |

| Number of vectors per file                          | About 700,000                            |

| Total number of vectors executed                    | 9,925,512                                |

| Size of each PCF File                               | 5.4 Mbytes                               |

| Total disc storage for PCF Files                    | 78.7 Mbytes                              |

| Total size of each object file<br>(15 object files) | 1.5 Mbytes (about<br>100,000 bytes each) |

| Total size of each debug object<br>(15 objects)     | 430,901 (about<br>28,800 bytes each)     |

| Total compilation time                              | 3 hours, 17 minutes                      |

# Table 3. Programming Times—FourEPM7128SQC160-7FDevices

| Description                                                   | TCK = 500 kHz   | TCK = 2 MHz |

|---------------------------------------------------------------|-----------------|-------------|

| Vector cycle time                                             | 1,000 ns (1 µs) | 250 ns      |

| Test time to program<br>all four devices (first<br>run)       | 52 seconds      | 41 seconds  |

| Test time to program<br>all four devices<br>(subsequent runs) | 23 seconds      | 6 seconds   |

Application Note 85 (In-System Programming Times for MAX Devices) lists programming times as a function of the TCK frequency and the number of devices being programmed. The data provided in this article is based on theoretical calculations. However, as tests have shown, these numbers are accurate to within less than one second of actual programming times on the HP 3070 tester. The programming times stated are for MAX® 7000S devices. Programming times for MAX 7000AE devices are reduced even further (up to 50%).

As expected, the programming time is a function of the TCK clock rate. Over this frequency range, the relationship between the frequency and programming time is linear. At higher frequencies, the programming time begins to asymptotically approach the theoretical programming time reported in *Application Note 85 (In-System Programming Times for MAX Devices)*. Additionally, the example shows that the concurrent algorithm

reduces the programming time of the four devices to the programming time of only one EPM7128S device.

#### Conclusion

Altera provides complete solutions for programming all ISP-capable devices using the HP 3070 test system. Fast programming times are achieved within the existing test flow for the HP 3070 tester. Additionally, Altera offers "F" devices, which provide fast, consistent programming times in a production environment. With both software and device support, the opportunity for cutting costs and increasing manufacturing productivity is available to any HP 3070 user.

## **Developing Tcl Scripts for Quartus Software**

#### Introduction

The Quartus<sup>™</sup> software allows designers to develop and run scripts in the tool command language (Tcl) to perform a wide range of simple or complex functions (e.g., compiling a design or writing procedures to automate common tasks). This article describes how to develop Tcl scripts for the Quartus software.

#### What is Tcl?

Tcl is a popular scripting language that is similar to many shell scripting and high-level programming languages. It provides enough programmability with its syntax to support control structures, variables, network socket access, and application programming interfaces (APIs) for integration.

Compared to languages like C++, Tcl is easy to learn and use. Because Tcl is an interpretive language, development is easier and faster than with other languages. When the desired functionality is not available, Tcl allows you to create your own commands or procedures from existing commands. You can use Tcl for multiplatform programming because it works seamlessly across development platforms such as UNIX and Windows NT.

#### Using Tcl

The Quartus API details a set of interface functions that can be called from different languages (e.g., Tcl or C++). Users with some knowledge of Tcl can use the API to write scripts that automate tasks within the Quartus software. A single script can control the project design, start and stop compilation, make assignments, and run simulations.

The basic syntax for a Tcl command is:

<command> [<argument1> <argument2> <argument3>...]

The command syntax is either the name of the built-in command, a procedure, or a set of commands. Spaces separate a command and its arguments, and a new line or semicolon terminates commands. Arguments to commands are passed as strings.

#### Running Tcl Scripts Interactively

You can enter Tcl commands directly in the Quartus Tcl/Tk Console window. To launch the Tcl/Tk Console window, choose **Auxiliary Windows > Tcl/Tk Console** (View menu). See Figure 1.

Figure 1. Tcl/Tk Console

continued on page 20

When the desired functionality is not available, Tcl allows you to create your own commands or procedures from existing commands.

# Developing Tcl Scripts for Quartus Software, continued from page 19

The Tcl/Tk Console window supports a command history. It does not allow commands to span more than one line. Tcl messages appear in the System tab in the Messages window.

Running Tcl Scripts in Batch Mode

Once you create a Tcl script file (.tcl), you can run it by typing the following command in the Tcl/Tk Console window:

```

source <script file> ←

```

cmp stop

You can also run a script by choosing **Run Script** (Tools menu).

#### Running Tcl Scripts from DOS or UNIX

The Quartus software also supports "-f <*script file*>" command line arguments. This command is equivalent to choosing **Run Script** (Tools

```

Figure 2. Running a Simple Compilation in Tcl

```

```

# Change to the working directory

cd E:/Tcl

# Create a project called myproject

project create myproject

# Open the project

project open myproject

# Add a source file to the Project

project add_assignment "" "" " SOURCE_FILE my_design.v

# Create compilation settings

project create_cmp my_design_entity

# Make this setting the active compiler setting

project set_active_cmp my_design_entity

# Assign a device

cmp add_assignment my_design_entity "" " DEVICE AUTO

# Start compilation

cmp start

while { [cmp is_running] } {

after 10

FlushEventQueue

}

```

menu). Use the following syntax for running commands from the DOS or UNIX prompt:

quartus\_cmd −f <*script file*> ←

For a detailed list of Tcl commands, search for "Tcl Script API" in Quartus Help.

#### Sample Tcl File

Figure 2 shows a sample file that creates a project, makes assignments, and runs a simple compilation in Tcl.

Altera provides extensive documentation to help you design with the Quartus software. For technical support, contact Altera® Applications at (800) 800-EPLD. You can also e-mail your technical questions to Altera at **sos@altera.com** or connect directly to the Quartus Web Support web site from within the Quartus software. The Quartus software supports Tcl version 8.03, which is supplied by Scriptics Corporation (http://www.scriptics.com).

SYNOPSYS

### Verifying PLD Designs Using SmartModels

Effective verification of complex systems, printed circuit boards (PCBs), and programmable logic devices (PLDs) requires accurate simulation models of the devices in the target system. Designers can create and maintain these models themselves, but it would detract from the main task of actually designing. A better alternative are the Logic Modeling SmartModels from Synopsys.

All PLD models in the Synopsys SmartModel library include the SmartCircuit feature, which provides the designer with the advanced verification and debugging features that are required to verify a PLD design quickly and successfully. Models with the SmartCircuit feature are basically templates of unconfigured devices, and a design netlist is loaded into the model in the EDIF format.

#### SmartModel Overview

The SmartCircuit feature allows the designer to focus on the design and system verification tasks rather than on simulation details. To generate an EDIF output file (.edo) that targets SmartModels from Altera's Quartus<sup>TM</sup> or MAX+PLUS<sup>®</sup> II Compiler, choose **EDIF Netlist Writer Settings** (Interfaces menu). Select **Synopsys** from the *Vendor* drop-down list, and select *EDIF 3 0 0* as the EDIF version.

SmartModels are behavioral simulation models that offer complete representations of device behavior and timing. Each model includes unique automatic error-checks to put design analysis power right into the model, making it easier to use the component properly. SmartModels are compatible with most thirdparty VHDL, Verilog HDL, and board-level simulators.

#### **Advanced Debugging**

A key factor in successfully verifying a design is the ability to debug functional and timing errors. The schematic of the design is a good starting point for a debugging effort. Visual SmartBrowser (VSB), a tool within PLD SmartModel models, displays the PLD netlist using an on-demand viewing technique. Users can expand or collapse the view of their design depending on the level of detail they require. With today's large, complex designs, such as Altera® FLEX® 10KE designs, designers are usually interested in debugging only a small section of the netlist at one time. VSB allows the designer to concentrate on only the section in which they are interested. Figure 1 shows the connection view of the VSB.

#### Figure 1. VSB Connection View

#### **Causal Tracing**