Parameterized for Data Width

Choice of Input Buffers

Choice of Output Buffers (ProASIC3/E only)

Choice of Bidirectional buffers (ProASIC3/E only)

Axcelerator, ProASIC3/E, Fusion

SmartGen can generate Dual Data Rate Registers parameterized for a specific Data Width and with a choice of the type of Input Buffers.

In ProASIC3/E, the DDR Registers may also be combined with output buffers or bi-directional buffers.

The Bidirectional enable signal polarity (TriEN) is selectable.

|

Parameter Description |

|

Parameter |

Value |

Function |

|

WIDTH |

1-128 |

Data Width |

|

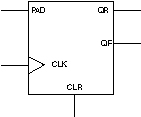

Port Description - Input Buffer plus DDR Register for Axcelerator |

|

Port Name |

Size |

Type |

Req/Opt |

Function |

|

PAD |

WIDTH |

Input |

Req. |

Input Data |

|

QR |

WIDTH |

Output |

Req. |

Output Data |

|

QF |

WIDTH |

Output |

Req. |

Ouput Data |

|

E |

1 |

Input |

Req. |

Enable |

|

CLK |

1 |

Input |

Req. |

Clock |

|

CLR |

1 |

Input |

Req. |

Clear |

|

PRE |

1 |

Input |

Req. |

Preset |

|

Port Description - Input Buffer plus DDR Register for ProASIC3/E |

|

Port Name |

Size |

Type |

Req/Opt |

Function |

|

PAD |

WIDTH |

Input |

Req. |

Input Data |

|

QR |

WIDTH |

Output |

Req. |

Output Data |

|

QF |

WIDTH |

Output |

Req. |

Ouput Data |

|

CLK |

1 |

Input |

Req. |

Clock |

|

CLR |

1 |

Input |

Req. |

Clear |

|

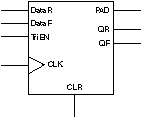

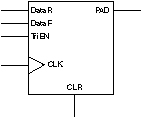

Port Description - Bidirectional Buffer plus DDR Register for ProASIC3/E |

|

Port Name |

Size |

Type |

Req/Opt |

Function |

|

PAD |

WIDTH |

Input/Output |

Req. |

Input/Output Data |

|

DataR |

WIDTH |

Input |

Req. |

Input Data |

|

DataF |

WIDTH |

Input |

Req. |

Input Data |

|

QR |

WIDTH |

Output |

Req. |

Output Data |

|

QF |

WIDTH |

Output |

Req. |

Output Data |

|

TriEN |

1 |

Input |

Req. |

Bibuf-Enable |

|

CLK |

1 |

Input |

Req. |

Clock |

|

CLR |

1 |

Input |

Req. |

Clear |

|

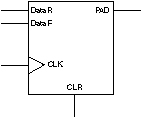

Port Description - DDR Register plus Output Buffer for ProASIC3/E |

|

Port Name |

Size |

Type |

Req/Opt |

Function |

|

PAD |

WIDTH |

Output |

Req. |

Output Data |

|

DataR |

WIDTH |

Input |

Req. |

Input Data |

|

DataF |

WIDTH |

Input |

Req. |

Input Data |

|

CLK |

1 |

Input |

Req. |

Clock |

|

CLR |

1 |

Input |

Req. |

Clear |

|

Port Description - Tri-State Buffer plus DDR Register for ProASIC3/E |

|

Port Name |

Size |

Type |

Req/Opt |

Function |

|

PAD |

WIDTH |

Input/Output |

Req. |

Output Data |

|

DataR |

WIDTH |

Input |

Req. |

Input Data |

|

DataF |

WIDTH |

Input |

Req. |

Input Data |

|

TriEN |

1 |

Input |

Req. |

Tribuf Enable |

|

CLK |

1 |

Input |

Req. |

Clock |

|

CLR |

1 |

Input |

Req. |

Clear |