The SmartGen tool automatically cascades FIFO blocks to create wider memories by choosing the most efficient aspect ratio. It also handles the grounding of unused bits.

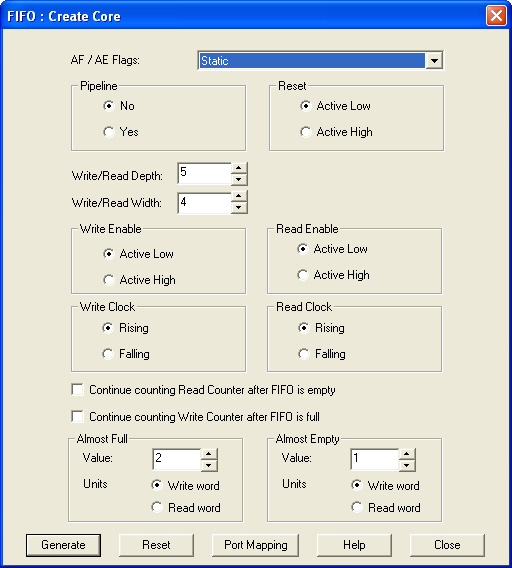

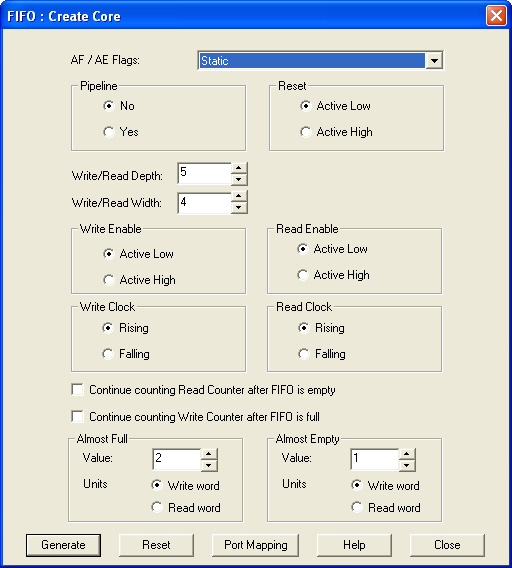

FIFO Configuration Screen

Specify the following parameters in SmartGen to create a FIFO:

User is allowed to choose among Static, Dynamic and No flags. When No flags is chosen, SmartGen grounds AFVAL, AEVAL and AFULL, AEMPTY signals do not appear as ports on the top level. When Static Flags are chosen SmartGen configures the AFVAL and AEVAL accordingly. For Dynamic Flags users drive the AFVAL and AEVAL through a signal and can change the thresholds dynamically. However, care must be taken that the functionality of the AFVAL and AEVAL is fully understood. For more information on these signals please refer to the FIFO Flags Usage section.

Users can choose to have a pipelined or non-pipelined read. SmartGen configures the PIPE signal accordingly. This is a static selection and cannot be changed dynamically by driving it with a signal.

SmartGen supports the generation of FIFO having a write or read depth between 1 and 4096. Write and Read Depth values can be different.

SmartGen supports the generation of RAM having a write or read width between 1 and 576. Write and Read Width values can be different.

SmartGen will instantiate inverters as necessary to achieve the requested polarity.

SmartGen will instantiate inverters as necessary to achieve the requested polarity.

Selecting this option means SmartGen will configure the FIFO in such a way that ESTOP is tied low and counter will keep counting even after FIFO is empty.

Selecting this option means SmartGen will configure the FIFO in such a way that FSTOP is tied low and counter will keep counting even after FIFO is full.

For more information on the above two options refer to the ESTOP, FSTOP Usage section.

This choice is applicable only in the Static Almost Full/Empty selection. The threshold for Almost Full is specified in terms of Write Words or Read Words.

This choice is applicable only in the Static Almost Full/Empty selection. The threshold for Almost Empty is specified in terms of Write Words or Read Words.

For more information on these choices please refer to the FIFO Flags Usage section.

Data: Input Data for the FIFO

Q: Output Data for FIFO

FULL, EMPTY: Full and Empty FIFO flags

AFULL, AEMPTY: Programmable Almost Full and Almost Empty flags (available only in static/dynamic flags configuration)

AFVAL, AEVAL: Signals to specify the thresholds for AFULL and AEMPTY (available only in dynamic flag configuration)

WClock, RClock: Write and Read Clocks

WE, RE: Write and Read Enables

RESET: FIFO Reset

The ESTOP pin is used to stop the read counter from counting any further once the FIFO is empty (i.e. the EMPTY flag goes high). Likewise, the FSTOP pin is used to stop the write counter from counting any further once the FIFO is full (i.e. the FULL flag goes high). These are configuration pins that should not be dynamically reconfigured. SmartGen will configure these signals based on user selection.

The FIFO counters in ProASIC3E, start the count from 0, reach the maximum depth for the configuration (e.g. 511 for a 512X9 configuration), and then re-start from 0. A potential application for the ESTOP, where the read counter keeps counting would be, writing to the FIFO once and reading the same content over and over, without doing a write again. Other applications for this feature need to be identified.

A typical user would not need to use these features and should leave these options un-checked in the GUI.

The AEVAL and AFVAL pins are used to specify the almost empty and almost full threshold values, respectively. They are 12-bit signals. In order to handle different read and write aspect rations, the values specified by the AEVAL and AFVAL pins are to be interpreted as the address of the last word stored in the FIFO. The FIFO actually contains separate write address (WADDR) and read address (RADDR) counters. These counters calculate the 12-bit memory address that is a function of WW and RW, respectively. WADDR is incremented every time a write operation is performed and RADDR is incremented every time a read operation is performed. Whenever the difference between WADDR and RADDR is greater than or equal to AFVAL, the AFULL output is raised. Likewise, whenever the difference between WADDR and RADDR is less than or equal to AEVAL, the AEMPTY output is raised.

To handle different read and write aspect ratios, the AFVAL and AEVAL are expressed in terms of total data bits instead of total data words. When users specify the AEVAL and AEVAL in terms of Read or Write words, SmartGen translates them into bit addresses and configures these signals.

For example, you have a 2KX2 write and a 4KX1 read. If you want the almost full to assert after writing 1000 words and almost empty after reading 1000 words, you need to specify 1000 WW for AFVAL and 1000 RW for AEVAL. SmartGen configures AFVAL to be 1000*2 = 2000 and AEVAL to be 1000*1 = 1000. It is applicable even in the case where read width and write width are the same.

In the case of 512X9 and 256X18 aspect ratios, since only 4096 bits can be addressed by 12 bits of the AFVAL/AEVAL and these configurations mean a total of 4608 bits, the number of words must be multiplied by 8 and 16, instead of 9 and 18. SmartGen automatically handles this. Users must keep this in mind when choosing dynamic flags.

To avoid half words being written or read, which could happen if different read and write aspect ratios are specified, the FIFO will assert the FULL or EMPTY as soon as at least a minimum of one word cannot be written or read. For example, if a 2-bit word is written and a 4-bit word is being read, FIFO will remain in the empty state when the first word is written, even though the FIFO is not completely empty, because at this time, a single word cannot be read. The same is applicable on the full state. If 4-bit word is written and 2-bit word is read, if the FIFO is full and one word is read, FULL flag will remain asserted because a complete word cannot be written at this point.

Depth cascading is currently not supported in SmartGen. Therefore the maximum depth supported is only 4096.

It supports wide cascading up to 64 blocks.

SmartGen does not generate a FIFO based on a specific device. It is the user’s responsibility to make sure the FIFO fits physically on the device.

Dynamic configuration of any signal with exception of AFVAL/AEVAL is not supported in SmartGen.

SmartGen will give a configuration error for unsupported configurations.

WBLK and RBLK are always grounded in SmartGen, which means the FIFO block always remains enabled. Users should control the FIFO with WEN and REN.

Since wide cascading is not possible in the case of different read/write aspect ratios, such configurations are supported only if they can fit in 1 FIFO block. Cascading is not supported for different read/write aspect ratios in FIFO at this point.