SmartGen automatically cascades RAM blocks to create wider and deeper memories by choosing the most efficient aspect ratio. It also handles the grounding of unused bits. SmartGen supports the generation of memories that have different Read and Write aspect ratios.

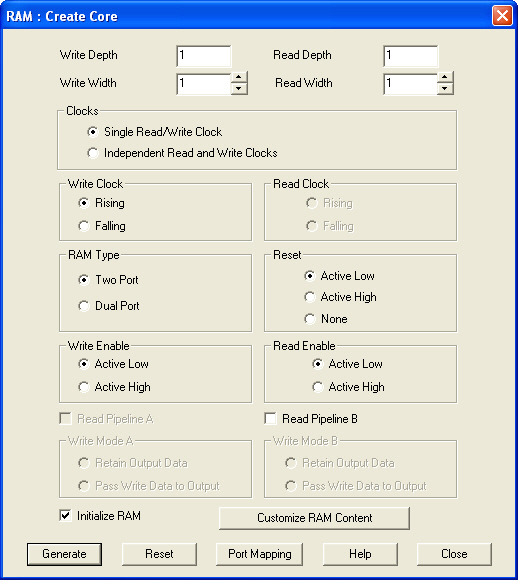

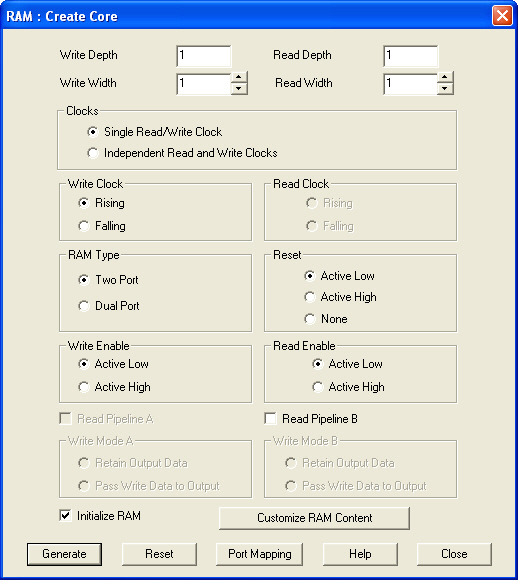

Specify the following parameters in SmartGen to create a RAM:

ProASIC3E RAM Configuration Dialog Box

You may choose between a Two Port and a Synchronous Dual Port configuration. In Dual Port mode, possible aspect ratios are: 4096x1, 2048x2, 1024x4, or 512x9. In Two Port mode, SmartGen supports aspect ratios of 512x9 or 256x18.

Different read and write aspect ratios are not supported in Dual Port mode. Also, the RAM512X18 element cannot be used to implement a dual port RAM. Using a dual port RAM can potentially increase the number of resources required.

For example, a 256X18 RAM can be created in one RAM block for Two Port, but requires 2 RAM Blocks for Dual Port. SmartGen always creates Dual Port RAM when this selection is made even if it consumes more resources.

When switching from two port to dual port, the GUI names are not displayed properly. In Two Port mode the naming correctly labels the Write and Read ports. However, when you select a Dual Port Memory, wherever the GUI displays Write it corresponds to PORTA, and where ever it displays Read it corresponds to PORTB.

You may choose to have the same clock driving both RCLK and WCLK and Two Port Mode or CLKA and CLKB in Dual Port Mode. Or you may choose to have independent Read and Write Clocks.

SmartGen supports the generation of RAM having a write or read width between 1 and 576. However, all depths are not available in all configurations. Write and Read Width values can be different. When choosing a Dual Port RAM only Write width is available as different aspect ratios are not supported in dual port mode.

SmartGen instantiates inverters as necessary to achieve the requested polarity. In the case of a single Read/Write clock both Read and Write Clock polarities are selectable when independent clocks are used and only Write Clock polarity is selectable when single read/write clock is used.

SmartGen configures the WMODE signals based on your selection. This is a static selection and cannot be changed dynamically by driving it with a signal. Write Mode is only available for Dual Port RAMs.

The RAM512X18 element has no WMODE selection and the default behavior of output data for this element is to hold the previously read data. In a case where you specify pass-through mode for WMODE then SmartGen uses RAM4K9 even if it results in usage of more resources. This situation arises only in the Two Port configurations, as RAM512X18 is not used for dual port RAM.

SmartGen configures the PIPEA and PIPEB signals to make the output pipelined or non-pipelined based on your selection. This is a static selection and cannot be changed dynamically by driving it with a signal. For Two Port RAM only Read Pipeline B is available.

DataA, DataB: Input Data for Dual Port RAM

QA, QB: Output Data for Dual Port RAM

AddressA, AddressB: Address Busses for Dual Port RAM

CLKA, CLKB: Clocks for Dual Port RAM for independent Clocks

Clock: Clock for Dual Port RAM for Single Clock

RWA, RWB: Signals to switch between Read and Write Modes for Dual Port RAM; Low = Write, High = Read

BLKA, BLKB: Active Low Block Enables for Dual Port RAM

RESET: Output Reset

Data: Input Data For Two Port RAM

Q: Output Data for Two Port RAM

WAddress, RAddress: Write and Read Address Busses for Two Port RAM

WEN, REN: Write and Read Enable For Two Port RAM

Wclock, Rclock: Write and Read Clocks for Two Port RAM for independent Clocks

Clock: Clock for Read and Write for Two Port RAM for single Clock

RESET: Output Rest

SmartGen will not generate Dual Port RAM for different Read and Write aspect ratios.

It also does not support configurations that use a word width of 1,2 or 4 for Write and a word width of 9 for Read. This configuration causes the MSB of the output to be undefined. However, configurations that do not use the 9th bit, like writing 1024X4 and reading 512X8 are possible.

SmartGen supports deep and wide RAM cascading only up to 64 blocks.

SmartGen does not generate RAM based on a specific device. It is your responsibility to make sure the RAM fits physically on the device.

Dynamic configuration of any signal is not supported in SmartGen.

SmartGen will give a configuration error for unsupported configurations.

Writing different data to same address using both ports in Dual Port RAM is undefined and should be avoided.

Writing to and reading from the same address is undefined and should be avoided.

Aspect Ratios should not be dynamically reconfigured.

All unused inputs must be grounded.

WMODE is ignored during read operation.

RESET does not reset the memory contents. It resets only the output.

When using the RAM4K9 in Two Port mode, care should be taken that Read and Write operations are not going on simultaneously, by properly driving the WEN and BLK signals. This becomes extremely important in cases where multiple RAM blocks are cascaded for deeper memories. In such case, BLK must be used for address decoding.