## Introduction

This document contains the latest information about the AVR data book and the AVR data sheets.

All references to the data book refers to the August 1999 version of the "AVR $^{\mbox{\tiny B}}$  RISC MICROCONTROLLER DATA BOOK".

All references to the AVR data sheets refer to the latest version of the AVR data sheets on Atmel's web page <u>www.atmel.com</u>.

The data sheets on Atmel's web page are updated more frequently than the printed data book. All known errors in each data sheet are corrected when a new version is released.

This document contains known errors that have not been corrected yet. All designers using AVR microcontrollers should use this document together with the data sheets. It is updated frequently, and should contain a complete list of all known documentation errors at any given time.

Please note that this document only covers errors in the AVR documentation. For errors in the AVR microcontrollers, see the errata sheet for each device.

If you find errors in the documentation that are not listed in this document, please send an email to the AVR support line <u>avr@atmel.com</u>.

## **Overview of data sheets**

| Part Number                       | Data Sheet Revision<br>in the August 1999<br>AVR Data Book | Data Sheet Revision<br>on Atmel's web site<br>www.atmel.com |

|-----------------------------------|------------------------------------------------------------|-------------------------------------------------------------|

| AT90S1200                         | 0838E-04/99                                                | 0838E-04/99                                                 |

| AT90S2313                         | 0839E-04/99                                                | 0839E-04/99                                                 |

| AT90S/LS2323 and AT90S/LS2343     | 1004B-04/99                                                | 1004B-04/99                                                 |

| AT90S/LS2333 and AT90S/LS4443     | 1042D-04/99                                                | 1042D-04/99                                                 |

| AT90S4414/8515                    | 0841E-04/99                                                | 0841E-04/99                                                 |

| AT90S/LS4434 and AT90S/LS8535     | 1041E-04/99                                                | 1041E-04/99                                                 |

| AT90C8534                         | 1229A-04/99                                                | 1229A-04/99                                                 |

| ATtiny10/11/12                    | 1006A-04/99                                                | 1006B-10/99                                                 |

| ATtiny15                          | 1187A-06/99                                                | 1187B-11/99                                                 |

| ATtiny22/22L                      | 1273A-04/99                                                | 1273A-04/99                                                 |

| ATmega161/161L                    | 1228A-05/99                                                | 1228A-08/99                                                 |

| ATmega603/603L and ATmega103/103L | 0945D-06/99                                                | 0945E-12/99                                                 |

| AVR Instruction Set               | 0856B-06/99                                                | 0856B-06/99                                                 |

| ATtiny28                          | N/A                                                        | 1062B-10/99                                                 |

# **AVR**<sup>®</sup> Data Book Updates and Changes

## AT90S1200

The latest data sheet on the web is rev. 0838E-04/99.

The data sheet in the printed data book is rev. 0838E-04/99.

### Changes in the AT90S1200 Data Sheet:

### Page: Change or Add:

- 2-3 In feature list under I/O and packages, replace "20-pin PDIP and SOIC" by "20-pin PDIP, SOIC and SSOP".

- 2-20 Table 4: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 2-25 In the note for Table 6, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

In the **EEPROM Read/Write Access** description, **change** "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed."

- 2-26 In the **Bit 0 EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

- 2-27 In the Analog Comparator Control and Status Register description, change the initial value of ACO from "0" to "N/A".

- 2-29 in the **Port B Input Pins Address PINB** description, change the Initial Values from "Hi-Z" to "N/A".

- 2-33 in the Port D Input Pins Address PIND description, change the Initial Values of bits 0 to 6 from "Hi-Z" to "N/A".

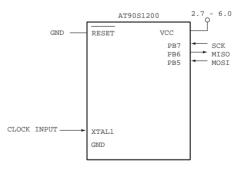

- 2-44 Replace figure 34 by the one below:

Figure 34 Serial Programming and Verify

### 2-49: Replace the row below in **DC characteristics**:

| $V_{ACIO}$ Analog Comparator<br>Input Offset Voltage $V_{CC} = 5V$ 40mV |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

by:

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V$<br>$V_{in} = V_{CC} / 2$ |  |  | 40 | mV |

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

- 2-50 In first line of **Typical Characteristics**, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

- 2-62 In **Register Summary**, replace "2-2-xx" by "2-xx".

## AT90S2313

The latest data sheet on the web is rev. 0839E-04/99.

The data sheet in the printed data book is rev. 0839E-04/99.

### Changes in the AT90S2313 Data Sheet:

### Page: Change or Add:

- 3-28 Table 5: remove this note: "Note: When changing the ISC11/ISC10 bits, INT1 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 3-29 Table 6: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 3-38 On the top of the page, add paragraph "Note: If the compare register contains the TOP value and the prescaler is not in use (CS12..CS10 = 001), the PWM output will not produce any pulse at all, because the up-counting and down-counting values are reached simultaneously. When the prescaler is in use (CS12..CS10 ≠ 001 or 000), the PWM output goes active when the counter reaches the TOP value, but the down-counting compare match is not interpreted to be reached before the next time the counter reaches the TOP-value, making a one period PWM pulse."

- 3-39 In the note for Table 14, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

In the **EEPROM Read/Write Access** description, **change** "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed."

- 3-40 In the **Bit1 EEWE: EEPROM Write Enable** description, **change** "4. Write a logical one to the EEMWE bit in EECR" **to** "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

- 3-41 In the **Bit 0 EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

- 3-47 In the **Analog Comparator Control and Status Register** description, change the initial value of ACO from "0" to "N/A".

- 3-49 in the **Port B Input Pins Address PINB** description, change the Initial Values from "Hi-Z" to "N/A".

- 3-54 in the **Port D Input Pins Address PIND** description, change the Initial Values of bits 0 to 6 from "Hi-Z" to "N/A".

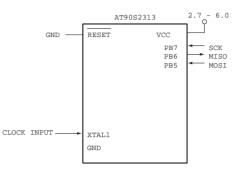

- 3-67 Replace figure 34 by the one below:

Figure 53 Serial Programming and Verify

3-72: Replace the row below in **DC characteristics**:

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V$ |  |  | 40 | mV |  |

|-------------------|-------------------------------------------|---------------|--|--|----|----|--|

|-------------------|-------------------------------------------|---------------|--|--|----|----|--|

by:

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V$<br>$V_{in} = V_{CC} / 2$ |  |  | 40 | mV |

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

3-73 In first line of **Typical Characteristics**, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

3-84 In **Register Summary**, replace "3-3-xx" and "3-3-3-xx" by "3-xx".

## AT90S/LS2323 and AT90S/LS2343

The latest data sheet on the web is rev. 1004B-04/99.

The data sheet in the printed data book is rev. 1004B-04/99.

### Changes in the AT90S/LS2323 and AT90S/LS2343 Data Sheet:

### Page: Change or Add:

#### 4-6 In the **Pin Descriptions AT90S/LS2323** replace the description for **Port B (PB2..PB0)** by

"Port B is a 3-bit bi-directional I/O port with internal pull-up resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low, will source current if the pull-up resistors are activated.

Port B also serves the functions of various special features.

Port pins can provide internal pull-up resistors (selected for each bit). The port B pins are tri-stated when a reset condition becomes active."

#### 4-7 In the **Pin Descriptions AT90S/LS2343** replace the description for **Port B (PB4..PB0)** by

"Port B is a 5-bit bi-directional I/O port with internal pull-up resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low, will source current if the pull-up resistors are activated.

Port B also serves the functions of various special features.

Port pins can provide internal pull-up resistors (selected for each bit). The port B pins are tri-stated when a reset condition becomes active."

- 4-19 In Figure 20, add a box containing "+1" as an input to the summation operator.

- 4-25 In the first paragraph of **Watchdog Reset**, replace "When the Watchdog times out, it will generate a short reset pulse of 1 XTAL cycle duration." by "When the Watchdog times out, it will generate a short reset pulse of 1 CPU clock cycle duration."

- 4-29 Table 9: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 4-34 In the note for Table 11, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

In **EEPROM Read/Write Access**, replace the 6th line "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." by "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When it is read, the CPU is halted for 4 clock cycles."

4-35 In the **Bit1 - EEWE: EEPROM Write Enable** description, change "4. Write a logical one to the EEMWE bit in EECR" to "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

In the **Bit 0 - EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

4-37 in the **Port B Input Pins Address - PINB** description, change the Initial Values of bits 0-4 from "Hi-Z" to "N/A".

# **AVR<sup>®</sup> Data Book Updates and Changes**

- 4-38 Replace the section name "MISO Port B, Bit 1" by "MISO/INTO Port B, Bit 1"

- 4-40 In **High-Voltage Serial Programming**, replace item 1. by

"Power-up sequence: Apply 4.5 - 5.5V between V<sub>CC</sub> and GND. Set RESET and PB0 to "0" and wait at least 100 ns.

Then, if the RCEN Fuse is not programmed; Toggle XTAL1/PB3 at least 4 times with minimum 100ns pulse-width. Set PB3 to "0". Wait at least 100ns.

or if the RCEN Fuse is programmed; Set PB3 to "0". Wait at least 4µs.

In both cases; Then apply 12V to  $\overline{\text{RESET}}$  and wait at least 100 ns before changing PB0. Wait 8  $\mu$ s before giving any instructions."

### 4-40 In High-Voltage Serial Programming, replace in item 5 "Set PB5 to "1"." by "Set RESET to "0"."

4-42 In table 16, replace the entries

L. .

| Read Fuse and<br>Lock bits<br>(AT90S/<br>LS2323) | PB0<br>PB1<br>PB2 | 0_0000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1100_00<br><i>1_2</i> Sxx_xxFx_xx           | Reading <i>1</i> , <i>2</i> , <b>S</b> , <b>F</b> =' 0' means the Fuse/Lock bit is programmed. |

|--------------------------------------------------|-------------------|------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Read Fuse and<br>Lock bits<br>(AT90S/<br>LS2343) | PB0<br>PB1<br>PB2 | 0_0000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1100_00<br><i>1_2</i> \$xx_xx <b>R</b> x_xx | Reading <b>1</b> , <b>2</b> , <b>S</b> , <b>R</b> =' 0' means the Fuse/Lock bit is programmed. |

by the entries (Note: Bit 7 in the 4'th and 5'th column for PB1 has been inverted compared to the original data book)

| Read Fuse and<br>Lock bits<br>(AT90S/<br>LS2323) | PB0<br>PB1<br>PB2 | 0_000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx_xx | 0_0000_0000_00<br>0_0111_1000_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0111_1100_00<br><i>1_2</i> Sxx_xxFx_xx | Reading <i>1</i> , <i>2</i> , <b>S</b> , <b>F</b> =' 0' means the Fuse/Lock bit is programmed. |

|--------------------------------------------------|-------------------|--------------------------------------------------|------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Read Fuse and<br>Lock bits<br>(AT90S/<br>LS2343) | PB0<br>PB1<br>PB2 | 0_000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxxx   | 0_0000_0000_00<br>0_0111_1000_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0111_1100_00<br><i>1_2</i> Sxx_xxRx_xx | Reading <b>1</b> , <b>2</b> , <b>S</b> , <b>R</b> =' 0' means the Fuse/Lock bit is programmed. |

4-43 In figure 35, remove "CLOCK INPUT", "XTAL1/PB3" and the arrow connecting them.

- 4-49 In first line of **Typical Characteristics**, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

- 4-59 In Register Summary, replace all "4-page" by "page". In addition, for TIMSK; replace "page 4 -15" by "page 4-28", for TIFR; replace "page 4-16" by "page 4-28", for MCUCR; replace "page 4-16" by "page 4-29", for MCUSR; replace "page 4-14" by "page 4-26".

| 4-60 | In Instruction Set Summary under BRANCH INSTRUCTIONS, replace |

|------|---------------------------------------------------------------|

|------|---------------------------------------------------------------|

| CPSE | Rd,Rr | Compare, Skip if Equal              | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 |

|------|-------|-------------------------------------|---------------------------------------------------|------|-------|

| SBRC | Rr, b | Skip if Bit in Register Cleared     | if $(Rr(b)=0) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 |

| SBRS | Rr, b | Skip if Bit in Register is Set      | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 |

| SBIC | P, b  | Skip if Bit in I/O Register Cleared | if (P(b)=0) PC $\leftarrow$ PC + 2 or 3           | None | 1 / 2 |

| SBIS | P, b  | Skip if Bit in I/O Register is Set  | if (R(b)=1) PC $\leftarrow$ PC + 2 or 3           | None | 1 / 2 |

| бу   |       |                                 |                                                   |      |           |

|------|-------|---------------------------------|---------------------------------------------------|------|-----------|

| CPSE | Rd,Rr | Compare, Skip if Equal          | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 / 3 |

| SBRC | Rr, b | Skip if Bit in Register Cleared | if $(Rr(b)=0) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1/2/3     |

| SBRS | Rr, b | Skip if Bit in Register is Set      | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                    | None | 1/2/3 |

|------|-------|-------------------------------------|--------------------------------------------------------------------------------------|------|-------|

| SBIC | P, b  | Skip if Bit in I/O Register Cleared | if (P(b)=0) PC $\leftarrow$ PC + 2 or 3                                              | None | 1/2/3 |

| SBIS | P, b  | Skip if Bit in I/O Register is Set  | if $(\mathbf{R}(\mathbf{b})=1) \mathbf{PC} \leftarrow \mathbf{PC} + 2 \text{ or } 3$ | None | 1/2/3 |

## AT90S/LS2333 and AT90S/LS4433

The latest data sheet on the web is rev. 1042D-04/99.

The data sheet in the printed data book is rev. 1042D-04/99.

### Changes in the AT90S/LS2333 and AT90S/LS4433 Data Sheet:

### Page: Change or Add:

- 5-6 In "**Pin Descriptions**", **AVCC**, change "This is the supply voltage for the A/D Converter. It should be externally connected to Vcc via a low-pass filter." to "This is the supply voltage for Port A and the A/D Converter. If the ADC is not used, this pin must be connected to Vcc. If the ADC is used, this pin should be connected to Vcc via a low-pass filter."

- 5-15 In **Figure 20**, add a box containing "+1" as an input to the summation operator.

- 5-28 Table 7: remove this note: "Note: When changing the ISC11/ISC10 bits, INT1 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

Table 8: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 5-34 In "**Timer/Counter Control Register 1B TCCR1B**", bit3 **CTC1**, change the count sequence when prescaler is set to divide by 8 from "...C-1 | C, 0, 0, 0, 0, 0, 0, 0, 0 | ..." to "...C-1 | C, 0, 0, 0, 0, 0, 0 | ..."

- 5-37 Before **table 14**, add paragraph "Note: If the compare register contains the TOP value and the prescaler is not in use (CS12..CS10 = 001), the PWM output will not produce any pulse at all, because the up-counting and down-counting values are reached simultaneously. When the prescaler is in use (CS12..CS10 ≠ 001 or 000), the PWM output goes active when the counter reaches the TOP value, but the down-counting compare match is not interpreted to be reached before the next time the counter reaches the TOP-value, making a one-period PWM pulse."

- 5-39 In the note for Table 16, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

- 5-41 In the **Bit1 EEWE: EEPROM Write Enable** description, change "4. Write a logical one to the EEMWE bit in EECR" to "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

- 5-47..50 In the **UART** description, replace "USR" by "UCSRA" and "UCR" by "UCSRB" everywhere.

- 5-50 In last line, replace "UBRRH" by "UBRRHI".

- 5-52 In "Analog Comparator Control and Status Register ACSR", the initial value of ACO is "N/A".

- 5-59 In "ADC Noise Canceling Techniques" item 3, replace "Figure 47" by "Figure 49".

- 5-60 In **Figure 49**, replace the resistor by a 10 μH inductor. Change capacitor value from 10 nF to 100 nF.

- 5-61 In the **Port B Input Pins Address PINB** description, change the Initial Values from "Hi-Z" to "N/A".

- 5-66 In the **Port C Input Pins Address PINC** description, change the Initial Values from "Hi-Z" to "N/A". Change Initial Values "Q" to "0" (zero).

- 5-68 In the **Port D Input Pins Address PIND** description, change the Initial Values from "Hi-Z" to "N/A".

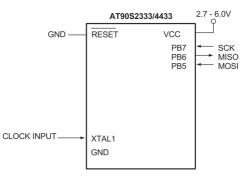

- 5-80 In "**Serial Downloading**", replace Figure 66 by the figure below.

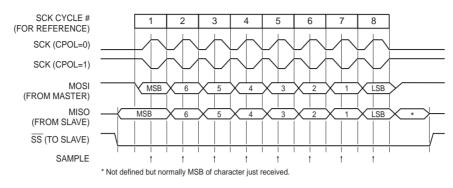

### Figure 66. Serial Programming and Verify

5-86 Replace the row below in **DC characteristics**:

| V <sub>ACIO</sub> Analo<br>Input | og Comparator<br>Offset Voltage | $V_{CC} = 5V$ |  |  | 40 | mV |

|----------------------------------|---------------------------------|---------------|--|--|----|----|

|----------------------------------|---------------------------------|---------------|--|--|----|----|

by:

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V$<br>$V_{in} = V_{CC} /2$ |  |  | 40 | mV |  |

|-------------------|-------------------------------------------|---------------------------------------|--|--|----|----|--|

|-------------------|-------------------------------------------|---------------------------------------|--|--|----|----|--|

5-86 In "**DC Characteristics**", footnote 4, replace "IOL" by "IOH" everywhere.

5-88 In first line of **Typical Characteristics**, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

## AT90S4414/8515

The latest data sheet on the web is rev. 0841E-04/99.

The data sheet in the printed data book is rev. 0841E-04/99.

### Changes in the AT90S4414/8515 Data Sheet:

### Page: Change or Add:

- 6-17 In **Figure 19**, add a box containing "+1" as an input to the summation operator.

- 6-29 Table 6: remove this note: "Note: When changing the ISC11/ISC10 bits, INT1 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 6-30 Table 7: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 6-39 Before **table 14**, add paragraph "Note: If the compare register contains the TOP value and the prescaler is not in use (CS12..CS10 = 001), the PWM output will not produce any pulse at all, because the up-counting and down-counting values are reached simultaneously. When the prescaler is in use (CS12..CS10 ≠ 001 or 000), the PWM output goes active when the counter reaches the TOP value, but the down-counting compare match is not interpreted to be reached before the next time the counter reaches the TOP-value, making a one- period PWM pulse."

- 6-41 In the note for Table 15, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

In the **EEPROM Read/Write Access** description, **change** "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed."

- 6-42 In the **Bit1 EEWE: EEPROM Write Enable description**, **change** "4. Write a logical one to the EEMWE bit in EECR" **to** "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

- 6-43 In the **Bit 0 EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

- 6-54 In the Analog Comparator Control and Status Register description, change the initial value of ACO from "0" to "N/A".

- 6-57 in the Port A Input Pins Address PINA description, change the Initial Values from "Hi-Z" to "N/A".

- 6-59 in the **Port B Input Pins Address PINB** description, change the Initial Values from "Hi-Z" to "N/A".

- 6-64 in the **Port C Input Pins Address PINC** description, change the Initial Values from "Hi-Z" to "N/A".

- 6-66 in the Port D Input Pins Address PIND description, change the Initial Values from "Hi-Z" to "N/A".

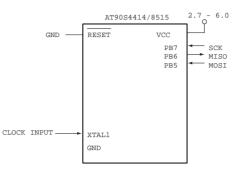

- 6-79 Replace figure 64 by the one below:

### Figure 64 Serial Programming and Verify

### 6-84: Replace the row below in **DC characteristics**:

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V$ |  |  | 40 | mV |

|-------------------|-------------------------------------------|---------------|--|--|----|----|

|-------------------|-------------------------------------------|---------------|--|--|----|----|

by:

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V$<br>$V_{in} = V_{CC} / 2$ |  |  | 40 | mV |

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

6-88 In first line of **Typical Characteristics**, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

6-98 In **Register Summary**, replace all "6-6-xx" by "6-xx".

## AT90S/LS4434 and AT90S/LS8535

The latest data sheet on the web is rev. 1041E-04/99.

The data sheet in the printed data book is rev. 1041E-04/99.

### Changes in the AT90S/LS4434 and AT90S/LS8535 Data Sheet:

### Page: Change or Add:

- 7-6 In "**Pin Descriptions**", **AVCC**, change "This is the supply voltage for the A/D Converter. It should be externally connected to Vcc via a low-pass filter." to "This is the supply voltage for Port A and the A/D Converter. If the ADC is not used, this pin must be connected to Vcc. If the ADC is used, this pin should be connected to Vcc via a low-pass filter."

- 7-15 In **Figure 19**, add a box containing "+1" as an input to the summation operator.

- 7-27 In "Timer/Counter Interrupt Flag Register TIFR", change heading "Bit 6 TOV2: Timer/Counter0 Overflow Flag" to "Bit 6 TOV2: Timer/Counter2 Overflow Flag".

- 7-29 Table 9: remove this note: "Note: When changing the ISC11/ISC10 bits, INT1 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

Table 10: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 7-30 In the **Power Down Mode** section, replace paragraph 2 ("Note that if a level triggered interrupt... ...on page 7-98.") to "Note that when a level triggered interrupt is used for wake-up from power down, the low level must be held for a time longer than the reset delay time-out period t<sub>TOUT</sub>."

- 7-30 At the end of the **Power Save Mode** section, add the paragraph "If the asynchronous timer is NOT clocked asynchronously, Power Down Mode is recommended instead of Power Save Mode because the contents of the registers in the asynchronous timer should be considered undefined after wake up in Power Save Mode, even if AS2 is 0."

- 7-36 In "Timer/Counter Control Register 1B TCCR1B", bit3 CTC1, change the count sequence when prescaler is set to divide by 8 from "...C-1 | C, 0, 0, 0, 0, 0, 0, 0, 0 | ..." to "...C-1 | C, 0, 0, 0, 0, 0, 0 | ..."

- 7-39 Before **table 16**, add paragraph "Note: If the compare register contains the TOP value and the prescaler is not in use (CS12..CS10 = 001), the PWM output will not produce any pulse at all, because the up-counting and down-counting values are reached simultaneously. When the prescaler is in use (CS12..CS10 ≠ 001 or 000), the PWM output goes active when the counter reaches the TOP value, but the down-counting compare match is not interpreted to be reached before the next time the counter reaches the TOP-value, making a one-period PWM pulse."

- 7-45 Replace last paragraph on page:

"When asynchronous operation is selected, the 32 kHz oscillator for Timer/Counter2 is always running, except in power down mode. After a power up reset or wake-up from power down, the user should be aware of the fact that this oscillator might take as long as one second to stabilize. Therefore, the content of all Timer/Counter2 registers must be considered lost after a wake-up from power down, due to the unstable clock signal. The user is advised to wait for at least one second before using Timer/Counter2 after power-up or wake-up from power down."

by

"When the asynchronous operation is selected, the 32kHZ oscillator for Timer/Counter2 is always running, except in power down mode. After a power up reset or wake-up from power down, the user should be aware of the fact that this oscillator might take as long as one second to stabilize. The user is advised to wait for at least one second before using Timer/Counter2 after power-up or wake-up from power down. The contents of all Timer/Counter2 reg-

isters must be considered lost after a wake-up from power down due to unstable clock signal upon start-up, regardless of whether the oscillator is in use or a clock signal is applied to the TOSC pin."

- 7-47 In the note for Table 22, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

- 7-49 In the **Bit1 EEWE: EEPROM Write Enable description**, change "4. Write a logical one to the EEMWE bit in EECR" to "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

In the **Bit 0 - EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

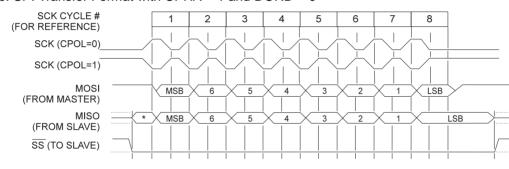

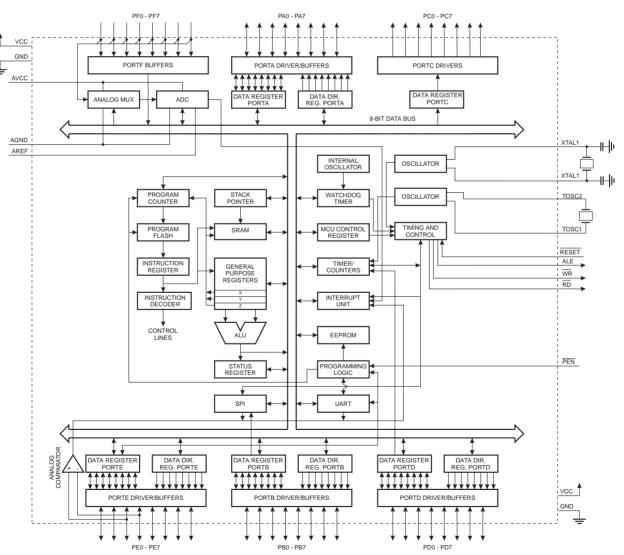

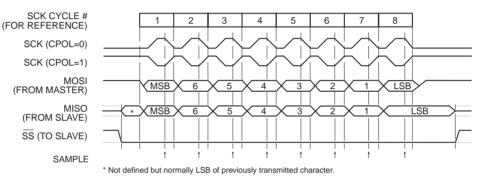

7-52 Change Figure 40 to the figure below.

Figure 40. SPI Transfer Format with CPHA = 1 and DORD = 0

7-60 In "Analog Comparator Control and Status Register - ACSR", the initial value of ACO is "N/A".

7-67 In Figure 50, replace the resistor by a 10 μH inductor. Change capacitor value from 10 nF to 100 nF.

7-69 In the **Port A Input Pins Address - PINA** description, change the Initial Values from "Hi-Z" to "N/A".

- 7-71 In the **Port B Input Pins Address PINB** description, change the Initial Values from "Hi-Z" to "N/A".

- 7-76 In the Port C Input Pins Address PINC description, change the Initial Values from "Hi-Z" to "N/A".

- 7-79 In the **Port D Input Pins Address PIND** description, change the Initial Values from "Hi-Z" to "N/A".

- 7-91 In "Serial Downloading", replace Figure 71 by the figure below.

Figure 71. Serial Programming and Verify

<sup>\*</sup> Not defined but normally LSB of previously transmitted character

### 7-96 Replace the row below in **DC characteristics**:

| $V_{ACIO}$ Analog Comparator<br>Input Offset Voltage $V_{CC} = 5V$ |  | 40 | mV |

|--------------------------------------------------------------------|--|----|----|

|--------------------------------------------------------------------|--|----|----|

by:

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage | $V_{CC} = 5V$<br>$V_{in} = V_{CC} / 2$ |  |  | 40 | mV |

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

|-------------------|-------------------------------------------|----------------------------------------|--|--|----|----|

- 7-98 In first line of **Typical Characteristics**, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

- 7-109 In Register Summary, replace all "7-page" by "page". In addition, replace "page 7-337-" by "page 7-33", "page 7-38", "page 7-467-" by "page 7-46", "page 7-487-" by "page 7-48".

## AT90C8534

The latest data sheet on the web is rev. 1229A-04/99.

The data sheet in the printed data book is rev. 1229A-04/99.

### Changes in the AT90C8534 Data Sheet:

### Page: Change or Add:

16

- 8-5 In "**Pin Descriptions**", **AVCC**, **change** "This is the supply voltage for the A/D Converter. It should be externally connected to Vcc via a low-pass filter." **to** "This is the supply voltage for the A/D Converter. If the ADC is not used, this pin must be connected to Vcc. If the ADC is used, this pin should be connected to Vcc via a low-pass filter."

- 8-16 In Figure 19, add a box containing "+1" as an input to the summation operator.

- 8-26 At the end of the **Interrupt Sense Control 1** description add this text: "When changing the ISC1 bit, an interrupt can occur. Therefore, it is recommended to first disable INT1 by clearing its Interrupt Enable bit in the GIMSK register. Then, the ISC1 bit can be changed. Finally, the INT1 interrupt flag should be cleared by writing a logical one to its Interrupt Flag bit in the GIFR register before the interrupt is re-enabled."

At the end of the **Interrupt Sense Control 0** description add this text: "When changing the ISC0 bit, an interrupt can occur. Therefore, it is recommended to first disable INT0 by clearing its Interrupt Enable bit in the GIMSK register. Then, the ISC0 bit can be changed. Finally, the INT0 interrupt flag should be cleared by writing a logical one to its Interrupt Flag bit in the GIFR register before the interrupt is re-enabled."

- 8-31 In the **EEPROM Read/Write Access** description, **change** "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed."

- 8-32 In the **Bit1 EEWE: EEPROM Write Enable description**, change "4. Write a logical one to the EEMWE bit in EECR" to "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

In the **Bit 0 - EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

## ATtiny10/11/12

The latest data sheet on the web is rev. 1006B-10/99.

The data sheet in the printed data book is rev. 1006A-04/99.

### Changes in the ATtiny10/11/12 Data Sheet on the web:

### Page: Change or Add:

27 Table 13: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

In the first paragraph of Sleep modes for the ATtiny10/11 section, replace the sentence

"On wake-up from Power Down Mode on pin change, the two instructions following SLEEP are executed before the pin change interrupt routine.

by

"On wake-up from Power Down Mode on pin change, 2 instruction cycles are executed before the pin change interrupt flag is updated. During these cycles, the processor executes instructions, but the interrupt condition is not readable, and the interrupt routine has not started yet.

- 32 In the note for Table 16, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset

- 33 In the last sentence of the first paragraph, change "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." to "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed."

In the **EEPROM Control Register** description, change the initial value of EEWE from "0" to "X".

34 In the **Bit 0 - EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

### Changes in the ATtiny10/11/12 section in the data book

### Page: Change or Add:

- 9-3 In both **Pin Configuration** figures, replace RESET with RESET.

- 9-14 In Figure 12, add a box containing "+1" as an input to the summation operator.

9-24 In the first line of the Watchdog Reset section, change "1 XTAL cycle" to "1 CK cycle".

In Figure 22, change "1 XTAL Cycle" to "1 CK Cycle".

9-29 Table 13: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

In the first paragraph of Sleep modes for the ATtiny10/11 section, replace the sentence

"On wake-up from Power Down Mode on pin change, the two instructions following SLEEP are executed before the pin change interrupt routine.

by

"On wake-up from Power Down Mode on pin change, 2 instruction cycles are executed before the pin change interrupt flag is updated. During these cycles, the processor executes instructions, but the interrupt condition is not readable, and the interrupt routine has not started yet.

9-34 In the note for Table 15, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

In the first paragraph of **ATtiny12 Calibrated Internal RC Oscillator** section, add "For details on how to use the pre-programmed calibration value, see the section 'Calibration Byte in ATtiny12' on page 9-42.

In the second paragraph, add "The calibrated oscillator is used to time EEPROM access. If EEPROM is written, do not calibrate to more than 10% above the nominal frequency. Otherwise, the EEPROM write may fail. Table 1 shows the range for OSCCAL. Note that the Oscillator is intended for calibration to 1.0MHz, thus tuning to other values is not guaranteed.

| OSCCAL value | Min. Frequency | Max Frequency |

|--------------|----------------|---------------|

| \$00         | 0.5MHz         | 1.0MHz        |

| \$7F         | 0.7MHz         | 1.5MHz        |

| \$FF         | 1.0MHz         | 2.0MHz        |

#### Table 1. Internal RC Oscillator Frequency Range.

**9-35** In the second line, change "The write access time is in the range of 2.5 - 4ms, depending on the V<sub>CC</sub>." to "The write access time is in the range of 1.9 - 3.4ms, depending on the frequency of the calibrated RC oscillator."

In the last sentence of the first paragraph, change "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." to "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed."

In the **EEPROM Control Register** description, change the initial value of EEWE from "0" to "X".

9-36 In the 14th line, remove "(typically 2.5ms at  $V_{CC} = 5V$  or 4 ms at  $V_{CC} = 2.7V$ )"

In the **Bit1 - EEWE: EEPROM Write Enable description**, change "4. Write a logical one to the EEMWE bit in EECR" to "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

In the **Bit 0 - EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

- 9-37 In the Analog Comparator Control and Status Register description, change the initial value of ACO from "0" to "N/A".

- 9-39 In the **Port B Input Pins Address PINB** description, change the Initial Value of bits 0-5 from "Hi-Z" to "N/A".

- 9-40 In the first line of section Alternate Functions of Port B, change "The alternate pin functions of Port B are:" to "All Port B pins are connected to a pin change detector that can trigger the pin change interrupt. See 'Pin Change Interrupt' on page 9-28 for details. In addition, Port B has the following alternate functions:".

# <sup>8</sup> **AVR**<sup>®</sup> Data Book Updates and Changes

9-42 In the section **Calibration Byte in ATtiny12**, add "At start-up, the user software must read this flash location and write the value to the OSCCAL register."

In the section **ATtiny10/11**, change "The +12V is used for programming enable only, and no current of significance is drawn by this pin." to "Only minor currents (<1mA) are drawn from the +12V pin during programming.".

- 9-44 In Table 21, remove the entire first row. In the first cell of the second row, remove "(ATtiny12)".

- 9-45 In the note on the bottom of the page, change "9, 6 = RSTISBL Fuse" to "9, 6 = RSTDISBL Fuse".

- 9-46 In Table 22, remove the "t<sub>WLWH CE</sub> "row.

In Figure 30, remove "CLOCK INPUT", "PB3 (XTAL1)" and the arrow connecting them.

9-47 In the sixth line, change "Either an external clock is supplied at pin XTAL1 or a crystal needs to be connected across pins XTAL1 and XTAL2" to "The device can be clocked by any clock option during Low-Voltage Serial Programming.".

In the two last lines of the first paragraph, change "2 XTAL clock cycles" to "2 CK clock cycles".

In the first entry of the **Low-Voltage Serial Programming Algorithm**, change "If a crystal is not connected across pins XTAL1 and XTAL2, apply a clock signal to the XTAL1 pin." to "In accordance with the setting of CKSEL fuses, apply a crystal/resonator, external clock or RC network, or let the device run on the internal RC oscillator.".

In the fifth entry, change the first " $t_{WD_{PROG}}$ " to " $t_{WD_{FLASH}}$  or  $t_{WD_{EEPROM}}$ ". Change the second " $t_{WD_{PROG}}$ " to " $t_{WD_{FLASH}}$  and  $t_{WD_{EEPROM}}$ ".

- 9-48 In the **Data Polling** section, change the first "t<sub>WD\_PROG</sub>" to "t<sub>WD\_FLASH</sub> or t<sub>WD\_EEPROM</sub>". Change the second and third "t<sub>WD PROG</sub>" to "t<sub>WD EEPROM</sub>".

- 9-50 Replace Table 25 and Table 26 with these tables:

| Symbol                | Minimum Wait Delay |

|-----------------------|--------------------|

| t <sub>WD_ERASE</sub> | 3.4 ms             |

| Symbol                 | Minimum Wait Delay |

|------------------------|--------------------|

| t <sub>WD_FLASH</sub>  | 1.7 ms             |

| t <sub>WD_EEPROM</sub> | 3.4 ms             |

### 9-52 In the DC Characteristics table, replace

| Symbol             | Parameter            | Condition                                                      | Min | Тур | Max | Units |

|--------------------|----------------------|----------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>CC</sub> Po | Power Supply Current | Active 4MHz, $V_{CC} = 3V$                                     |     |     | 3.0 | mA    |

|                    |                      | Idle 4MHz, $V_{CC} = 3V$                                       |     | 1.0 | 1.2 | mA    |

|                    |                      | Power Down <sup>(5)</sup> , $V_{CC} =$ 3V, WDT enabled         |     | 9.0 | 15  | μA    |

|                    |                      | Power Down <sup>(5)</sup> , V <sub>CC</sub> = 3V. WDT disabled |     | <1  | 2   | μA    |

| Symbol | Parameter                       | Condition                            | Min | Тур        | Max | Units |

|--------|---------------------------------|--------------------------------------|-----|------------|-----|-------|

| Vacio  | Analog Comp<br>Input Offset V   | $V_{CC} = 5V$                        |     |            | 40  | mV    |

| Iaclk  | Analog Comp<br>Input leakage A  | $V_{CC} = 5V$<br>$V_{IN} = V_{CC}/2$ | -50 |            | 50  | nA    |

| Tacpd  | Analog Comp<br>Propagation Del. | $V_{CC} = 2.7V$ $V_{CC} = 4.0V$      |     | 750<br>500 |     | ns    |

with

| Symbol            | Parameter                                  | Condition                                                      | Min | Тур        | Мах | Units |

|-------------------|--------------------------------------------|----------------------------------------------------------------|-----|------------|-----|-------|

|                   |                                            | Active 1MHz, V <sub>CC</sub> = 3V<br>(ATtiny12V)               |     |            | TBD | mA    |

|                   |                                            | Active 2MHz, V <sub>CC</sub> = 3V<br>(ATtiny10/11L)            |     |            | TBD | mA    |

|                   |                                            | Active 4MHz, V <sub>CC</sub> = 3V<br>(ATtiny12L)               |     |            | 3.0 | mA    |

|                   |                                            | Active 6MHz, V <sub>CC</sub> = 5V<br>(ATtiny10/11)             |     |            | TBD | mA    |

|                   |                                            | Active 8MHz, V <sub>CC</sub> = 5V<br>(ATtiny12)                |     |            | TBD | mA    |

| 1                 | Power Supply Current                       | Idle 1MHz, V <sub>CC</sub> = 3V<br>(ATtiny12V)                 |     |            | TBD | mA    |

| I <sub>CC</sub>   |                                            | Idle 2MHz, V <sub>CC</sub> = 3V<br>(ATtiny10/11L)              |     |            | TBD | mA    |

|                   |                                            | Idle 4MHz, V <sub>CC</sub> = 3V<br>(ATtiny12L)                 |     | 1.0        | 1.2 | mA    |

|                   |                                            | Idle 6MHz, V <sub>CC</sub> = 5V<br>(ATtiny10/11)               |     |            | TBD | mA    |

|                   |                                            | Idle 8MHz, V <sub>CC</sub> = 5V<br>(ATtiny12)                  |     |            | TBD | mA    |

|                   |                                            | Power Down <sup>(5)</sup> , $V_{CC}$ = 3V, WDT enabled         |     | 9.0        | 15  | μΑ    |

|                   |                                            | Power Down <sup>(5)</sup> , V <sub>CC</sub> = 3V. WDT disabled |     | <1         | 2   | μΑ    |

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$ $V_{IN} = V_{CC}/2$                              |     |            | 40  | mV    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | $V_{CC} = 5V$ $V_{IN} = V_{CC}/2$                              | -50 |            | 50  | nA    |

| T <sub>ACPD</sub> | Analog Comparator<br>Propagation Delay     | $V_{CC} = 2.7V$ $V_{CC} = 4.0V$                                |     | 750<br>500 |     | ns    |

9-53 In the first table, change the title from "External Clock Drive" to "External Clock Drive ATtiny12" and add this table:

### **External Clock Drive ATtiny10/11**

|                     |                      | $\mathbf{V}_{\mathbf{CC}} = \mathbf{2.7V} \text{ to } \mathbf{4.0V}$ |     | V <sub>CC</sub> = 4.0V to 5.5V |     |       |

|---------------------|----------------------|----------------------------------------------------------------------|-----|--------------------------------|-----|-------|

| Symbol              | Parameter            | Min                                                                  | Max | Min                            | Max | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                                                                    | 2   | 0                              | 6   | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 500                                                                  |     | 167                            |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 200                                                                  |     | 67                             |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 200                                                                  |     | 67                             |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                                                                      | 1.6 |                                | 0.5 | μs    |

| t <sub>CHCL</sub>   | Fall Time            |                                                                      | 1.6 |                                | 0.5 | μs    |

- 9-54 In the first line, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

- 9-72 In row 12 (MCUSR) of the table, change "WDTR" to "WDRF" and "BODR" to "BORF".

## ATtiny15L

The latest data sheet on the web is rev. 1187B-11/99.

The data sheet in the printed data book is rev. 1187A-06/99.

## Changes in the ATtiny15L Data Sheet on the web:

None.

## Changes in the ATtiny15L section in the data book:

The data sheet for ATtiny15 has gone through serious improvements and corrections since the printing of the "AVR RISC MICROCONTROLLER DATA BOOK AUGUST 1999". The user is advised to download the complete new ATtiny15 data sheet from the Web, since correcting the present data book would not give a user friendly result.

## ATtiny22/22L

The latest data sheet on the web is rev. 1273A-04/99.

The data sheet in the printed data book is rev. 1273A-04/99.

### Changes in the ATtiny22/22L Data Sheet:

Generally: The external clock option does not exist in ATtiny22/L. Therefore, all references to the RCEN fuse and external clock are wrong, and the part comes as ATtiny22L only, not ATtiny22.

### Page: Change or Add:

- All For all "ATtiny22/L" read "ATtiny22L".

- 11-3 In the feature list, replace the following lines

- Special Microcontroller Features

- ...

- Selectable On-chip RC Oscillator

- Power Consumption at 4 MHz, 3V,  $25^\circ C$

- Active: 2.4 mA

- Idle Mode: 0.5 mA

- Power Down Mode: <1 μA</p>

- Operating Voltages

- 2.7 6.0V (ATtiny22L)

- 4.0 6.0V (ATtiny22)

- Speed Grades

- 0 4 MHz (ATtiny22L)

- 0 8 MHz (ATtiny22)

by the following description;

Special Microcontroller Features

- ...

- On-chip RC Oscillator

- Power Consumption at 3V, 25°C

- Active: 1.5 mA

- Idle Mode: 100µA

- Power Down Mode:  $<1 \,\mu A$

- Operating Voltages

- 2.7 6.0V

- Speed Grade

- Internal Oscillator ~1MHz@5.0V

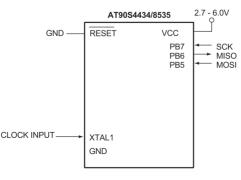

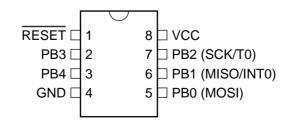

- 11-3 Replace Pin Configuration by the figure shown below.

### 11-5 In the **Pin Descriptions ATtiny22/L** replace the description for **Port B (PB4..PB0)** by

"Port B is a 5-bit bi-directional I/O port with internal pull-up resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low, will source current if the pull-up resistors are activated.

Port B also serves the functions of various special features.

Port pins can provide internal pull-up resistors (selected for each bit). The port B pins are tri-stated when a reset condition becomes active."

- 11-5 Remove the description "CLOCK" under **Pin Descriptions ATtiny22/L.**

- 11-5 The whole section "Clock options" including Figure 2 should be replaced by "Clock Source

The ATtiny22L is clocked by an on-chip RC oscillator. This RC oscillator runs at a nominal frequency of 1 MHz (VCC = 5V)."

- 11-16 In Figure 18, add a box containing "+1" as an input to the summation operator.

- 11-16 Replace second paragraph under **Memory Access and Instruction Execution Timing**, "The AVR CPU is driven by the System Clock Ø, directly generated from the external clock signal applied to the CLOCK pin." by "The AVR CPU is driven by the System Clock Ø, directly generated from the internal RC oscillator."

- 11-21 In Power-On Reset, replace the first paragraph; "The ATtiny22/L is designed for use in systems where it can operate from the internal RC oscillator or in applications where a clock signal is provided by an external clock source. After V<sub>CC</sub> has reached V<sub>POT</sub>, the device will start after the time t<sub>TOUT</sub> (see Figure 23). If the clock signal is provided by an external clock source, the clock must not be applied until V<sub>CC</sub> has reached the minimum voltage defined for the applied frequency. " by "The ATtiny22L is designed for use in systems where it can operate from the internal RC oscillator. After V<sub>CC</sub> has reached V<sub>POT</sub>, the device will start after the time t<sub>TOUT</sub> (see Figure 23)."

- 11-23 In the first paragraph of Watchdog Reset, replace "When the Watchdog times out, it will generate a short reset pulse of 1 CPU cycle duration." by "When the Watchdog times out, it will generate a short reset pulse of 1 clock cycle duration."

- 11-27 Table 7: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

- 11-31 In the note for Table 9, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."

- 11-32 In line number 6, replace "When the EEPROM is read or written, the CPU is halted for two clock cycles before the next instruction is executed." by "When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed. When it is read, the CPU is halted for 4 clock cycles."

- 11-33 In the **Bit1 EEWE: EEPROM Write Enable description**, change "4. Write a logical one to the EEMWE bit in EECR" to "4. Write a logical one to the EEMWE bit in EECR (to be able to write a logical one to the EEMWE bit, the EEWE bit must be written to zero in the same cycle)."

In the **Bit 0 - EERE: EEPROM Read Enable** description, **change** "When EERE has been set, the CPU is halted for two clock cycles before the next instruction is executed." **to** "When EERE has been set, the CPU is halted for four clock cycles before the next instruction is executed."

- 11-34 In Table 10, remove the entry for PB3.

- 11-34 In the **Port B Input Pins Address PINB** description, change the Initial Values of bits 0-4 from "Hi-Z" to "N/A".

- 11-35 Remove section, CLOCK Port B, Bit 3.

## <sup>24</sup> **AVR**<sup>®</sup> Data Book Updates and Changes

#### 11-35 Replace the section name "MISO - Port B, Bit 1" by "MISO/INTO - Port B, Bit 1"

- 11-36 In section Fuse Bits, replace the first sentence; "The ATtiny22/L has two Fuse bits, SPIEN and RCEN." by "The ATtiny22L has one Fuse bit, SPIEN.", and remove the second bullet item which is a description of the RCEN fuse.

- 11-37 In Table 13, delete one of the rows saying

| ATtiny22/L | 2.7 - 6.0V | 4.5 - 5.5V |

|------------|------------|------------|

- 11-37 In High-Voltage Serial Programming Algorithm, replace item 1 by "Power-up sequence: Apply 4.5 5.5V between V<sub>CC</sub> and GND. Set RESET and PB0 to "0" and wait at least 100 ns. Set PB3 to "0". Wait at least 4µs. Apply 12V to RESET and wait at least 100 ns before changing PB0. Wait 8 µs before giving any instructions."

- 11-37 In High-Voltage Serial Programming Algorithm, replace in item 5 "Set PB5 to "1"." by "Set RESET to "0"."

- 11-38 In Figure 31, replace "XTAL1/PB3" by "PB3".

- 11-38 In table 14, replace the entries

| Write Fuse bits            | PB0               | 0_0100_0000_00                                 | 0_11 <b>S</b> 1_111 <b>R</b> _00               | 0_0000_0000_00                                                      | 0_0000_0000_00 | Wait t <sub>WLWH_PFB</sub> after Instr.3 for the                                               |

|----------------------------|-------------------|------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------|

|                            | PB1               | 0_0100_1100_00                                 | 0_0010_1100_00                                 | 0_0110_0100_00                                                      | 0_0110_1100_00 | Write Fuse bits cycle to finish. Set <b>S</b> , <b>R</b>                                       |

|                            | PB2               | x_xxxx_xxx                                     | x_xxxx_xxxx_xx                                 | x_xxxx_xxx                                                          | x_xxxx_xxx     | = "0" to program, "1" to unprogram.                                                            |

| Read Fuse and<br>Lock bits | PB0<br>PB1<br>PB2 | 0_0000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1100_00<br><i>1_2</i> Sxx_xx <b>R</b> x_xx |                | Reading <i>I</i> , <i>2</i> , <b>S</b> , <b>R</b> = "0" means the Fuse/Lock bit is programmed. |

by the entries (Note: For Read Fuse and Lock bits; Bit 7 in the 4'th and 5'th column for PB1 have been inverted compared to the original data book.

| Write Fuse bit             | PB0               | 0_0100_0000_00                                 | 0_11 <b>S</b> 1_1110_00                        | 0_0000_0000_00                                             | 0_0000_0000_00 | Wait $t_{WLWH_PFB}$ after Instr.3 for the                                           |

|----------------------------|-------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------|

|                            | PB1               | 0_0100_1100_00                                 | 0_0010_1100_00                                 | 0_0110_0100_00                                             | 0_0110_1100_00 | Write Fuse bit cycle to finish. Set $S =$                                           |

|                            | PB2               | x_xxxx_xxx                                     | x_xxxx_xxxx_xx                                 | x_xxxx_xxx                                                 | x_xxxx_xxx     | "0" to program, "1" to unprogram.                                                   |

| Read Fuse and<br>Lock bits | PB0<br>PB1<br>PB2 | 0_0000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0111_1000_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0111_1100_00<br><i>1_2</i> Sxx_xx0x_xx |                | Reading <i>I</i> , <i>2</i> , <b>S</b> = "0" means the Fuse/Lock bit is programmed. |

and delete the note " $\mathbf{R}$  = RCEN Fuse" to this table.

- 11-40 In figure 33, remove "CLOCK INPUT", "XTAL1/PB3" and the arrow connecting them.

- 11-40 In last paragraph, replace "Either an external clock is applied to the XTAL1/PB3 pin or the device must be clocked from the internal RC-oscillator." by "The device is clocked from the internal RC-oscillator."

- 11-41 In item "1. Power-up sequence", replace "RESET" by "RESET" (two occurrences) and delete "If the device is programmed for external clocking, apply a 0 to 8 MHz clock to the PB3 pin. If the internal RC oscillator is selected as the clock source, no external clock source needs to be applied."

- 11-43 In table 17, replace the entries

| Read Lock and<br>Fuse Bits | 0101 1000 | xxxx xxxx         | XXXX XXXX | 12Sx xxxR | Read Lock and Fuse bits. '0' = programmed, '1' = unprogrammed.                           |

|----------------------------|-----------|-------------------|-----------|-----------|------------------------------------------------------------------------------------------|

| Write RCEN Bit             | 1010 1100 | 1011 111 <b>R</b> | XXXX XXXX | XXXX XXXX | Write RCEN Fuse. Set bit $\mathbf{R} = '0'$ to program, '1' to unprogram. <sup>(1)</sup> |

by the entry (Remove the entry "Write RCEN Bit"):

| Read Lock and | 0101 1000 | xxxx xxxx | xxxx xxxx | <b>125</b> x xxx0 | Read Lock and Fuse bit. '0' =   |

|---------------|-----------|-----------|-----------|-------------------|---------------------------------|

| Fuse Bit      |           |           |           |                   | programmed, '1' = unprogrammed. |

and remove the notes " $\mathbf{R}$  = RCEN Fuse" and "When the state of the RCEN bit is changed, the device must be power cycled for the changes to have any effect."

- 11-44 Above Table 18, add "The period of the internal RC oscillator  $t_{CLCL}$  is voltage dependent as shown in "Typical characteristics", and delete the entries for  $1/t_{CLCL}(V_{CC} = 2.7 4.0V)$ ,  $t_{CLCL}(V_{CC} = 2.7 4.0V)$ ,  $1/t_{CLCL}(V_{CC} = 4.0 6.0V)$ ,  $t_{CLCL}(V_{CC} = 4.0 6.0V)$ ,

- 11-45 In **DC Characteristics**, replace the entries:

| I <sub>CC</sub> | Power Supply Current | Active 4 MHz, $V_{CC} = 3V$                                     |  | 3.0  | mA |

|-----------------|----------------------|-----------------------------------------------------------------|--|------|----|

|                 |                      | Idle 4 MHz, $V_{CC} = 3V$                                       |  | 1.1  | mA |

|                 |                      | Power Down 4 MHz <sup>(2)</sup> ,<br>$V_{CC} = 3V$ WDT Enabled  |  | 25.0 | μΑ |

|                 |                      | Power Down 4 MHz <sup>(2)</sup> ,<br>$V_{CC} = 3V$ WDT Disabled |  | 20.0 | μΑ |

### by the entries

| I <sub>CC</sub> | Power Supply Current | Active, $V_{CC} = 3V$                     |  | 1.5  | mA |

|-----------------|----------------------|-------------------------------------------|--|------|----|

|                 |                      | Idle, $V_{CC} = 3V$                       |  | 100  | μΑ |

|                 |                      | Power Down,<br>$V_{CC} = 3V$ WDT Enabled  |  | 25.0 | μΑ |

|                 |                      | Power Down,<br>$V_{CC} = 3V$ WDT Disabled |  | 20.0 | μΑ |

### 11-46 Remove the sections **External Clock Drive Waveforms** and **External Clock Drive**.

- 11-46 In first line of **Typical Characteristics**, change "These data are characterized, but not tested." to "These figures are not tested during manufacturing.".

- 11-46 For last sentence in second paragraph of the section Typical Characteristics, replace "The dominating factors are the operating voltage and frequency" by "The dominating factor is the operating voltage, as the frequency of ATtiny22L is also a function of the operating voltage."

- 11-47 Remove Figure 37 and Figure 38

- 11-48 Remove Figure 40

- 11-49 Remove Figure 41

- 11-56 In Register Summary, replace all "11-page" by "page". In addition, for TIMSK; replace "page 11-15" by "page 11-26", for MCUCR; replace "page 11-16" by "page 11-26", for MCUSR; replace "page 11-14" by "page 11-24"

# AVR<sup>®</sup> Data Book Updates and Changes

#### 11-56 In Register Summary, replace

| \$21 (\$41) | WDTCR | - | - | - | WDTO | WDE | WDP2 | WDP1 | WDP0 | Page 11-30 |

|-------------|-------|---|---|---|------|-----|------|------|------|------------|

| · · · ·     | •     |   |   |   |      |     |      |      |      |            |

| by          |       |   |   |   |      |     |      |      |      |            |

| \$21 (\$41) | WDTCR | - | - | - | WDTOE | WDE | WDP2 | WDP1 | WDP0 | Page 11-30 |

|-------------|-------|---|---|---|-------|-----|------|------|------|------------|

#### 11-57 In Instruction Set Summary under BRANCH INSTRUCTIONS, replace

| CPSE | Rd,Rr | Compare, Skip if Equal              | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 |

|------|-------|-------------------------------------|---------------------------------------------------|------|-------|

| SBRC | Rr, b | Skip if Bit in Register Cleared     | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3          | None | 1 / 2 |

| SBRS | Rr, b | Skip if Bit in Register is Set      | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 |

| SBIC | P, b  | Skip if Bit in I/O Register Cleared | if (P(b)=0) PC $\leftarrow$ PC + 2 or 3           | None | 1 / 2 |

| SBIS | P, b  | Skip if Bit in I/O Register is Set  | if (R(b)=1) PC $\leftarrow$ PC + 2 or 3           | None | 1 / 2 |

bv

| ~y   |       |                                     |                                                   |      |           |

|------|-------|-------------------------------------|---------------------------------------------------|------|-----------|

| CPSE | Rd,Rr | Compare, Skip if Equal              | if $(Rd = Rr) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 / 3 |

| SBRC | Rr, b | Skip if Bit in Register Cleared     | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3          | None | 1 / 2 / 3 |

| SBRS | Rr, b | Skip if Bit in Register is Set      | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$ | None | 1 / 2 / 3 |

| SBIC | P, b  | Skip if Bit in I/O Register Cleared | if (P(b)=0) PC $\leftarrow$ PC + 2 or 3           | None | 1 / 2 / 3 |

| SBIS | P, b  | Skip if Bit in I/O Register is Set  | if (R(b)=1) PC $\leftarrow$ PC + 2 or 3           | None | 1/2/3     |

|      |       |                                     |                                                   |      |           |

### 11-59 Replace the Ordering Information

| Power Supply | Speed (MHz) | Ordering Code                    | Package    | <b>Operation Range</b>        |

|--------------|-------------|----------------------------------|------------|-------------------------------|

| 2.7 - 6.0V   | 4           | ATtiny22L-4PC8P3ATtiny22L-4SC8S2 |            | Commercial<br>(0°C to 70°C)   |

|              |             | ATtiny22L-4PI<br>ATtiny22L-4SI   | 8P3<br>8S2 | Industrial<br>(-40°C to 85°C) |

| 4.0 - 6.0V   | 8           | ATtiny22-8PC<br>ATtiny22-8SC     | 8P3<br>8S2 | Commercial<br>(0°C to 70°C)   |

|              |             | ATtiny22-8PI<br>ATtiny22-8SI     | 8P3<br>8S2 | Industrial<br>(-40°C to 85°C) |

Note: The speed grade refers to maximum clock rate when using an external clock drive. The internal RC oscillator has the same nominal clock frequency for all speed grades."

### by the following Ordering Information

"

| Power Supply | Speed (MHz)                 | Ordering Code                  | Package    | <b>Operation Range</b>        |

|--------------|-----------------------------|--------------------------------|------------|-------------------------------|

| 2.7 - 6.0V   | Internal Osc.<br>~1MHz@5.0V | ATtiny22L-1PC<br>ATtiny22L-1SC | 8P3<br>8S2 | Commercial<br>(0°C to 70°C)   |

|              |                             | ATtiny22L-1PI<br>ATtiny22L-1SI | 8P3<br>8S2 | Industrial<br>(-40°C to 85°C) |

"

## ATtiny28L/V

The latest data sheet on the web is rev. 1062B-10/99.

This data sheet is not in the printed data book.

## Changes in the ATtinyL /V Data Sheet on the web:

None.

## ATmega161/161L

The latest data sheet on the web is rev. 1228A-08/99.

The data sheet in the printed data book is rev. 1228A-05/99.

### Changes in the ATmega161/161L data sheet:

### Page: Change or Add:

12-25 Add the following note below **table 2**: "note: if BOOTRST fuse is programmed, the reset vector is located on program address \$1e00, see table 38 on page 12-98 for details".

Add this code example below the existing **code example**: When the BOOTRST fuse is programmed, the most typical and general program setup for the Reset and Interrupt Vector Addresses are:

| Address     | Labels | Code Comments                                    |                                               |         |

|-------------|--------|--------------------------------------------------|-----------------------------------------------|---------|

| .org \$002  |        |                                                  | ; Reset is located at \$1e                    | ≥000    |

| \$002       |        | jmp                                              | EXT_INT0 ; IRQ0 Handler                       |         |

| \$004       |        | jmp                                              | EXT_INT1 ; IRQ1 Handler                       |         |

| \$006       |        | jmp                                              | EXT_INT2 ; IRQ2 Handler                       |         |

| \$008       |        | jmp                                              | TIM2_COMP ; Timer2 Compare Handler            |         |

| \$00a       |        | jmp                                              | TIM2_OVF ; Timer2 Overflow Handler            |         |

| \$00c       |        | jmp                                              | TIM1_CAPT ; Timer1 Capture Handler            |         |

| \$00e       |        | jmp                                              | TIM1_COMPA ; Timer1 CompareA Handler          |         |

| \$010       |        | jmp                                              | TIM1_COMPB ; Timer1 CompareB Handler          |         |

| \$012       |        | jmp                                              | TIM1_OVF ; Timer1 Overflow Handler            |         |

| \$014       |        | jmp                                              | TIM0_COMP ; Timer0 Compare Handler            |         |

| \$016       |        | jmp                                              | TIM0_OVF ; Timer0 Overflow Handler            | :       |

| \$018       |        | jmp                                              | <pre>SPI_STC; ; SPI Transfer Complete H</pre> | Iandler |

| \$01a       |        | jmp                                              | UART_RXC0 ; UARTO RX Complete Handl           | .er     |

| \$01c       |        | jmp                                              | UART_RXC1 ; UART1 RX Complete Handl           | er      |

| \$01e       |        | jmp                                              | UART_DRE0 ; UDR0 Empty Handler                |         |

| \$020       |        | jmp                                              | UART_DRE1 ; UDR1 Empty Handler                |         |

| \$022       |        | jmp                                              | UART_TXC0 ; UARTO TX Complete Handl           | .er     |

| \$024       |        | jmp                                              | UART_TXC1 ; UART1 TX Complete Handl           | .er     |

| \$026       |        | jmp                                              | EE_RDY ; EEPROM Ready Handler                 |         |

| \$028       |        | jmp                                              | ANA_COMP ; Analog Comparator Handl            | .er     |

| ;           |        |                                                  |                                               |         |

| \$02a       | MAIN:  | ldi rl                                           | ,high(RAMEND); Main program start             |         |

| \$02b       |        | out SPI                                          | I,r16                                         |         |

| \$02c       |        | ldi rl                                           | ,low(RAMEND)                                  |         |

| \$02d       |        | out SPI                                          | 1,r16                                         |         |

| \$02e       |        | <instr:< td=""><td>· xxx</td><td></td></instr:<> | · xxx                                         |         |

| ;           |        |                                                  |                                               |         |

| .org \$1e00 |        |                                                  |                                               |         |

| \$1e00      |        | jmp                                              | RESET ; Reset handler                         |         |

| •••         |        |                                                  |                                               |         |

12-35 Table 7: remove this note: "Note: When changing the ISC11/ISC10 bits, INT1 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

Table 8: remove this note: "Note: When changing the ISC01/ISC00 bits, INT0 must be disabled by clearing its Interrupt Enable bit in the GIMSK register. Otherwise an interrupt can occur when the bits are changed."

At the end of the **Interrupt Sense Control 2** description add this text: "When changing the ISC2 bit, an interrupt can occur. Therefore, it is recommended to first disable INT2 by clearing its Interrupt Enable bit in the GIMSK register. Then, the ISC2 bit can be changed. Finally, the INT2 interrupt flag should be cleared by writing a logical one to its Interrupt Flag bit in the GIFR register before the interrupt is re-enabled."

- 12-36 At the end of the **Power Save Mode** section, add the paragraph "If the asynchronous timer is NOT clocked asynchronously, Power Down Mode is recommended instead of Power Save Mode because the contents of the registers in the asynchronous timer should be considered undefined after wake up in Power Save Mode even if AS2 is 0."

- 12-46 Replace last paragraph on page,

"When asynchronous operation is selected, the 32 kHz oscillator for Timer/Counter2 is always running, except in power down mode. After a power up reset or wake-up from power down, the user should be aware of the fact that this oscillator might take as long as one second to stabilize. Therefore, the content of all Timer/Counter2 registers must be considered lost after a wake-up from power down, due to the unstable clock signal. The user is advised to wait for at least one second before using Timer/Counter2 after power-up or wake-up from power down."

#### by

"When the asynchronous operation is selected, the 32 kHZ oscillator for Timer/Counter2 is always running, except in power down mode. After a power up reset or wake-up from power down, the user should be aware of the fact that this oscillator might take as long as one second to stabilize. The user is advised to wait for at least one second before using Timer/Counter2 after power-up or wake-up from power down. The contents of all Timer/Counter2 registers must be considered lost after a wake-up from power down due to unstable clock signal upon start-up, regardless of whether the oscillator is in use or a clock signal is applied to the TOSC pin."

- 12-55 In the note for Table 20, add "To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select."