## **Relevant Devices**

This application note applies to the following devices: C8051F000, C8051F001, C8051F002, C8051F005, C8051F006, C8051F010, C8051F011, C8051F012, C8051F020, C8051F021, C8051F022, and C8051F023.

# Introduction

C8051F0xx devices are equipped with an SMBus serial I/O device that is compliant with the System Management Bus Specification version 1.1, as well as the  $I^2C$  serial bus. The SMBus is a bi-directional, 2-wire interface capable of communication with multiple devices. SMBus is a trademark of Intel;  $I^2C$  is a trademark of Philips Semiconductor.

This application note describes configuration and operation of the SMBus. Example assembly and C code is given: (1) Interfacing a single EEPROM with 1-byte address space, in assembly; (2) Interfacing multiple EEPROMs with 2-byte address space, in C; and (3) Peerto-peer communication between two C8051F0xx devices, in C.

# **SMBus Specification**

This section presents a description of the SMBus protocol. The SMBus discussion begins in the next section--Using the SMBus.

## SMBus Structure

An SMBus system is a 2-wire network, where each device has a unique address and may be addressed by any other device on the network. All transfers are initiated by a master device; if a device recognizes its own address and responds, it becomes the slave device for that transfer. It is important to note that assigning one specified master device is not necessary. Any device may assume the role of master or slave for any particular transfer. In the case that two devices attempt to initiate a transfer simultaneously, an arbitration scheme forces one device to give up the bus. This arbitration scheme is non-destructive (one device wins and no information is lost). Arbitration is discussed in depth in the arbitration section.

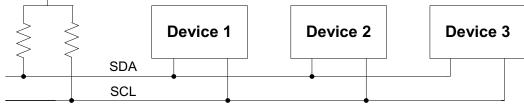

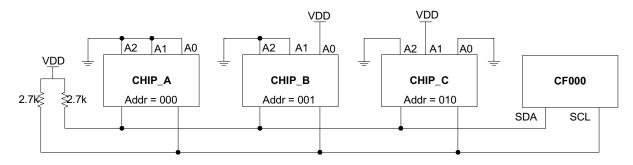

Two wires are used in SMBus communication: SDA (serial data), and SCL (serial clock). Each line is bi-directional, with direction depending on what modes the devices are in. The master always supplies SCL; either device may transmit on SDA. Both lines should be connected to a positive power supply through a pull-up circuit. All devices on the SMBus line should have an open-drain or open collector output, so that the lines may remain high when the bus is free. The line is pulled low if one or more devices attempts to output a LOW signal. All devices must output a HIGH for the line to stay high. A typical SMBus configuration is shown in Figure 1 on page 2.

#### CYGNAL Integrated Products, Inc.

4301 Westbank Drive Suite B-100 Austin, TX 78746 <u>www.cygnal.com</u> Copyright © 2002 Cygnal Integrated Products, Inc. (All rights reserved) AN013-1.1 JUL02

Figure 1. Typical SMBus Configuration

# Handshaking

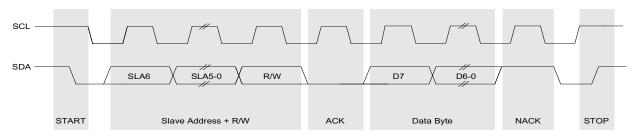

SMBus employs various line conditions as handshaking between devices. Note that during a data transfer, SDA is only allowed to change levels while SCL is low. Changes on SDA while SCL is high represent START and STOP signals, as follows:

**START**: This initiates a transfer. It consists of a falling edge on SDA while SCL is high.

**STOP**: This ends a transfer. It consists of a rising edge on SDA while SCL is high.

**ACKNOWLEDGE**: Also referred to as an ACK, this is transmitted by a receiving device as a confirmation. For example, after device\_X receives a byte, it transmits an ACK to confirm the transfer. An ACK consists of a low level on SDA sampled when SCL is high.

**NOT\_ACKNOWLEDGE**: Also referred to as a NACK, this is a high SDA while SCL is high. When a receiving device fails to ACK, the sending device sees a NACK. In typical transfers, a received NACK indicates that the addressed slave is not ready for transfer, or is not present on the bus. A receiving master may transmit a NACK to indicate the last byte of a transfer. Both of these situations are discussed further in the next section. Figure 2 illustrates the handshaking signals.

## Transfer Modes

Two types of transfers are possible: a WRITE (transfer from master to slave) and a READ (transfer from slave to master). During a transfer, any device may assume one of four roles. These four roles are explained below. Note that 'slave address + R/W' refers to an 8 bit transfer (7 address, 1 R/W).

Figure 2. SMBus Timing

1) Master Transmitter: In this mode, the device transmits serial data on SDA and drives the clock on SCL. The device initiates the transfer with a START condition, sends the slave address + W, and waits for an ACK from the slave. After the ACK, the device transmits one or more bytes of data, with each byte ACK'ed by the slave. After the last byte, the device transmits a STOP.

2) Master Receiver: In this role, the device receives serial data on SDA while driving the clock on SCL. The device initiates the transfer with a START followed by the slave address + R. After the slave ACK's the address, the device will output the clock on SCL, and receive data on SDA. After the last byte, the device will issue a NACK followed by a STOP. 3) Slave Transmitter: In this role, a device outputs serial data on SDA and receives the clock on SCL. The device receives a START followed by its own slave address + R, then ACK's, and enters slave transmitter mode. The device transmits serial data on SDA and receives an ACK after each byte. After the last byte, the master will issue a NACK followed by a STOP.

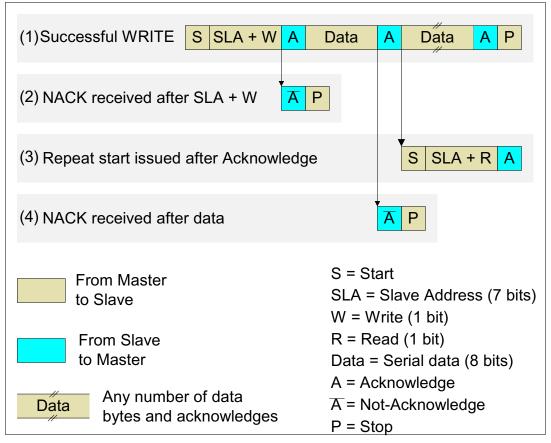

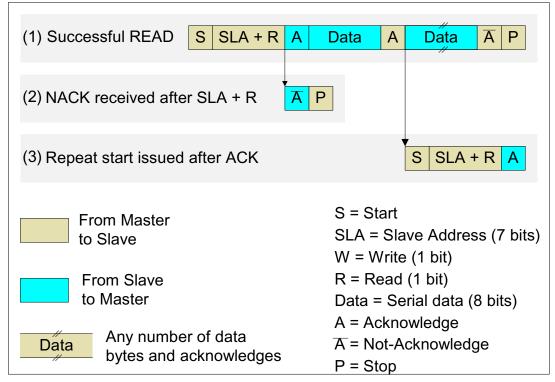

4) Slave Receiver: In this role, a device receives a START followed by its own slave address + W from a master device. The device sends an ACK and enters slave receiver mode. The device now receives serial data on SDA and the clock on SCL. The device ACK's after each byte is received, and exits slave mode after the master issues a STOP. Figure 3 shows

#### Figure 3. Typical WRITE Transfer Scenarios

the typical WRITE scenarios. (1) shows a successful transfer.

In (2), the master receives a NACK after sending the slave address + W. This occurs when a slave is 'offline', meaning it is not responding to its own address. In this case, the master should issue a STOP or repeated START. To retry the transfer, the master follows the STOP with a START and the slave address + W again. The master will repeat the cycle until it receives an ACK. This is referred to as "acknowledge polling".

In (3), the master issues a repeated START after an ACK. This process allows the master to initiate a new transfer without giving up the bus (to switch from a WRITE to a READ, for example). The repeated START is commonly used in EEPROM memory access applications, where a memory READ must be directly preceded by a WRITE of the desired memory

location. The repeated START is demonstrated in all three code examples.

In (4), a NACK is received after a data byte. In typical SMBus systems, this is how the receiving device indicates an error. The master sends a STOP, and retries the transfer as in (2), or gives up the transfer. Note that the use of NACKs is not restricted to error situations; the acknowledge level is a user-definable characteristic, and may vary in different applications.

Figure 4 shows the typical READ scenarios. (1) shows a successful READ operation. In (2), the master receives a NACK after sending the slave address + R. This situation is handled in the same fashion as in (2) of the WRITE discussion. The master can use acknowledge polling to retry the transfer, or it can give up the transfer. (3) Shows the master sending a repeated START after sending a byte of data. This is the same repeated START state as in the WRITE discussion. A master may send a

#### Figure 4. Typical Read Scenarios

repeated START after any data byte, and may initiate a READ or a WRITE following the repeated START. Generally a repeated START is used to change direction (R/W) or to change addresses (slave devices).

Note that the READ and WRITE diagrams show only the typical scenarios. Bus errors, time outs, and arbitration are also possible occurrences. Timeouts are used to detect when a transfer has stalled or when the bus is free. Often a device may hold SCL low until it is ready to continue a transfer. This process allows a slower slave device to communicate with a faster master, since stalling the bus effectively reduces the SCL frequency. The SMBus protocol specifies that all devices on the SMBus must declare any SCL signal held low for more than 25 ms a "timeout". In this case, all devices on the bus must reset communication. A high SCL timeout may also occur. If both SDA and SCL remain high for more than 50 µsec, the bus is designated as free.

## Arbitration

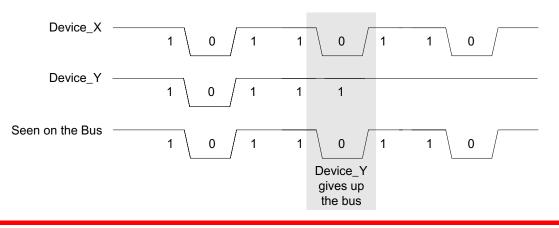

If multiple masters are configured on the same SMBus system, it is possible that two will attempt to initiate a transfer at the same time. If this happens, an arbitration scheme is employed to force one device to give up the bus. What the scheme is: both masters continue to transmit until one attempts a HIGH while the other attempts a LOW. Due to the open-drain bus, the device attempting a LOW will win the bus. The HIGH device gives up the bus, and the other device continues its transfer. Note that the collision is non-destructive: one device always wins.

How it works: Assume device\_X and device\_Y contend for the bus. The winner, device\_X, is not affected at all by the arbitration. Since data is shifted into the SMBus data register as it is shifted out, device\_Y does not miss any data. Figure 5 shows an example output sequence between two devices during arbitration. Note that Device\_Y begins receiving data after it gives up the bus.

# Using the SMBus

The SMBus can operate in both master and slave modes. The hardware provides timing and shifting control for the serial transfers; byte-wise control is user-defined. The SMBus hardware performs the following applicationindependent tasks:

Timing Control: In master mode, the hardware generates the clock signal on SCL and synchronizes the data on SDA. Hardware also recognizes timeouts and bus errors.

#### Figure 5. Arbitration Sequence

Serial Data Transfers: The hardware controls all shifting of data to and from SDA, including the acknowledge level. The acknowledge level is user-defined, as explained in the register definitions below.

Slave Address Recognition: The hardware recognizes a START from another device, and reads the following slave address. If the slave address matches the contents of the SMBus Address Register (defined below), then the hardware acknowledges the address. Note that this features is only enabled if AA (Address Acknowledge) is set.

## **Configuration and Control**

SMBus operation is determined by the contents of the following registers.

**SMB0STA.** The SMBus Status Register holds an 8-bit status code for the current state of the SMBus. The contents of SMB0STA are only defined when the SI bit is set. There are 28 possible states, all of which have a unique code (the codes are multiples of 8). SMB0STA should never be written to. The 28 possible states and their descriptions are given in Table 1 on page 12.

**SMB0CN.** The SMBus control register is used to enable the SMBus and navigate the possible SMBus states. This register includes START and STOP control, as well as interrupt, acknowledge, and timeout control.

A transfer is initiated by setting the STA bit. The SMBus hardware will wait until the bus is free, then transmit a START. **Note that STA is not cleared by hardware.** User software must manually clear STA so that an unwanted repeated START is not generated. **User software must also manually clear STO prior to setting STA.**  A transfer is ended by setting the STO bit. In master mode, setting STO will cause a STOP condition to be generated. If STA is set when STO is set, a STOP followed by a START will be transmitted. In slave mode, setting STO will cause the hardware to act as if a STOP was received, though no STOP condition is transmitted.

The SI bit is set when any of the possible 28 SMBus states are entered (excluding the idle state). This bit is not automatically cleared by hardware. **Note that SCL is held low while SI is set.** This means that the bus is stalled until SI is cleared, synchronizing the master with the slave.

The AA bit determines the type of acknowledge returned during the acknowledge cycle. If AA=1, an ACK will be sent; if AA=0, a NACK will be sent. This means the device will respond to its slave address only if AA is set.

SCL high and low timeout detection is enabled by setting the FTE and TOE bits, respectively.

The SMBus is enabled by setting the SMBus enable bit, ENSMB.

**SMB0CR.** The SMBus clock register is used to control the SCL clock rate when the device is in master mode. The 8 bits held in the SMB0CR register determine the clock rate as follows:

$$SMB0CR \cong -\frac{SYSCLK}{2 \times F_{SCL}}$$

<1>

Where SMB0CR is a 2's complement negative number. So for a SCL frequency of 100 kHz and a SYSCLK of 16 MHz, SMB0CL should be loaded with -80, or 0xB0.

SMB0CR also defines the limit for the bus free time period (high SCL timeout). The bus free time is defined by the following equation, where SMB0CR is a 2's complement negative number. Note that  $T_{Free}$  is about 5 bit periods.

$$T_{Free} = -\frac{(10 \times SMB0CR) + 1}{SYSCLK} \qquad <2>$$

**SMB0ADR.** The SMBus Address Register holds the slave address that the device will respond to in slave mode. Bits(7:1) hold the slave address; bit0 is the General Call Enable. If bit0 is set, the device will respond to the general call address (0x00).

**SMB0DAT**. The SMBus Data Register is used to hold data to be transmitted or data that has just been received by the SMBus. Data read from this register is only valid while SI = 1. When SI is not set, the SMBus may be in the process of shifting data in or out of SMB0DAT. Note that when transmitting, data shifted out of the most significant bit of SMB0DAT is shifted back into the least significant bit, so that after a transmit the original data is still contained in SMB0DAT.

## Implementation Choices

User software controls the SMBus on a stateby-state basis. Upon each state change, the SI bit is set by hardware, and an interrupt generated if interrupts are enabled. The SMBus is then halted until user software services the state change and clears the SI bit. The SMBus operation is most easily defined in a state table; however, note that it is not necessary to define all 28 states. For example, if the SMBus is the only master in the system, the slave and arbitration states may be left undefined. If the SMBus will never operate as a master, the master states may be left undefined. If states are left undefined, a default response should be programmed to account for unexpected or error situations.

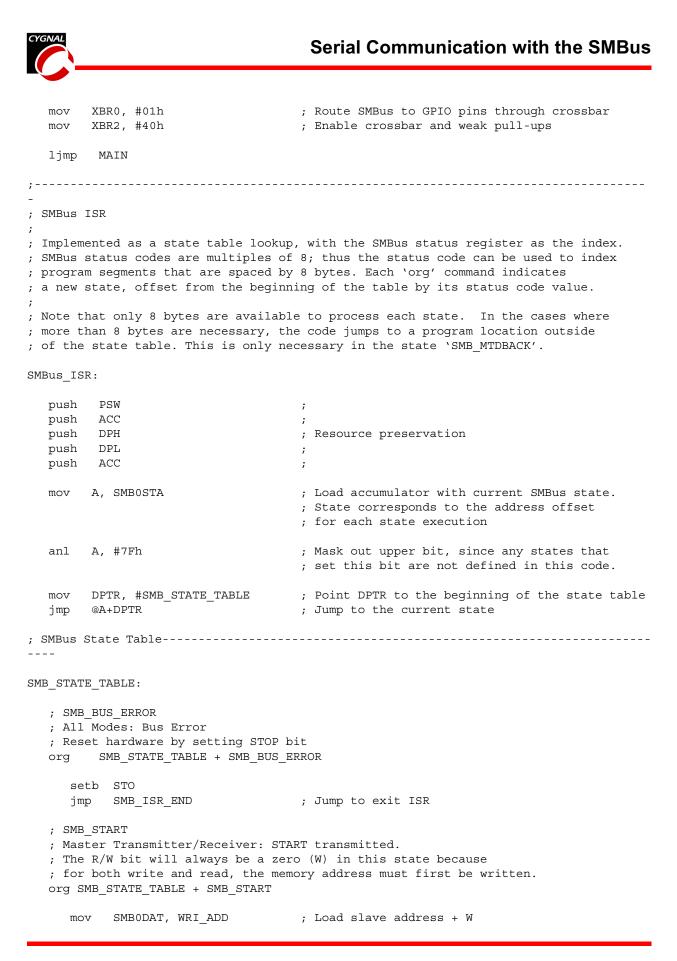

The SMBus state table lends itself to a caseswitch statement definition in C. However, for simple or time-restricted systems, an assembly state decoding can be more efficient. Note that the status codes held in SMB0STA are multiples of 8. If the SMBus states are programmed in 8-byte segments, SMB0STA may be used as a software index. In this case, a status code is decoded in 3 assembly commands. However, only 8 bytes of code space are available for each state definition. For states that require more than 8 bytes, the program must branch out of the state table so that subsequent states are not disturbed.

# Examples

Three examples are provided: a single EEPROM with 1-byte address space, in assembly; multiple EEPROMs with 2-byte address space, in C; and a peer-to-peer interface between two devices, in C. Each example uses interrupt-driven operation.

## Single EEPROM

This is a simple interface between the SMBus and a 256-byte EEPROM. The SMBus acts as the master at all times. The transfer procedure is similar to that of any 2-wire EEPROM interface.

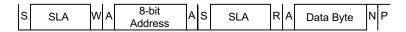

The Send operation is a 1-byte random WRITE. The SMBus sends a START followed by three bytes: the EEPROM's device address + W (this address is found in the EEPROM datasheet), the memory location to be written, and then the data byte. The slave should ACK after each byte. If the master receives an ACK after each byte, it sends a STOP and the transfer is over. If at any time the master receives a NACK, it will retry the transfer using

acknowledge polling. It is common for an EEPROM to NACK if multiple read/write operations are performed sequentially, since most self-timed EEPROMs go offline to actually perform the memory write. Figure 6 shows SDA for the Single EEPROM send operation.

Figure 6. Single EERPOM Send Sequence

| s | SLA | WA | 8-bit   | A | Data Byte | A | P |

|---|-----|----|---------|---|-----------|---|---|

|   |     |    | Address |   | 2414 2910 |   |   |

The Receive operation is a 1-byte random READ. The transfer begins, as in the WRITE function, with the master sending a START followed by the EEPROM device address + W (a WRITE is used to set the EEPROM's "current address"). After the slave ACK's, the master sends the memory location to be read. Upon receipt of an ACK, the master then issues a repeated START followed by the slave address + R. Now after the slave ACK's, it will send the data byte read from the location given in the preceding "aborted" WRITE. The master sends a NACK (since this data is the last and only byte), followed by a STOP. The repeated START is used in this case so that no other transfers may begin between the WRITE of the memory address and the READ of the data byte. Figure 7 shows SDA for a Single **EEPROM** Receive operation.

The software for this example was written in assembly to demonstrate the advantage of using SMB0STA as a software index. The SMBus state table written in 8-byte memory segments (8 bytes for each state). This is accomplished through the use of an 'org' statement for each state, offset from the beginning of the table by the corresponding status code. For example, if the state table is labeled STATE\_TABLE, and State\_1 is 0x08, the code segment for State\_1 should begin with:

```

; State_1

org STATE_TABLE + 08h

; State_1 code

```

Now when SMB0STA holds 0x80, State\_1 may be accessed with the following:

```

; Load current State

mov A, SMBOSTA;

; Point DPTR to start of table

mov DPTR, #STATE_TABLE;

; Jump to indexed state

jmp @A+DPTR;

```

This process allows for very efficient state decoding. However, it is important to note that only 8 bytes of code space are available for each state. If a state requires more than 8 bytes, the program must jump to a segment outside of the state table, so that the next state definition is not disturbed.

To keep the states simple and understandable, the SMBus is assumed to be the only master in the system. The slave states are not defined, and the arbitration states ignore any received data. Also, the repeated START state may assume the transfer is a READ. The code listing begins on page 14.

#### Figure 7. Single EEPROM Receive Sequence

## Multiple EEPROMs

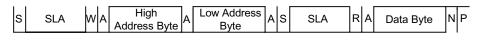

Example 2 uses multiple EEPROMs with 2byte address space. The software is written in C. The three EEPROMs used are 8k-bytes. Note that three identical EEPROMs are used. The EEPROMs have three address selection pins, A0 - A2, that are used to set the slave address for the devices. The four high bits of the device address are set in EEPROM to "0101"; the lower three bits of the slave address are determined by the setting of the address pins (VDD for 1, GND for 0). Figure 9 shows the device configuration.

The distinction with this example is that the EEPROMs have a 2-byte address space. This means that the READ and WRITE operations must send an extra address byte for each transfer (see Figure 8). When the Interrupt Service Routine reaches the "Data Transmitted, ACK Received" state, it must know which byte was transmitted--the high address byte, the low address byte, or the data byte. This information is kept in the BYTE\_NUMBER state variable.

The SMBus ISR is implemented as a caseswitch statement, with the SMBus status code (SMB0STA) used as the switch variable. The code listing for this example begins on page 23.

#### Figure 9. Multiple EEPROM Configuration

## Peer-to-Peer Interface

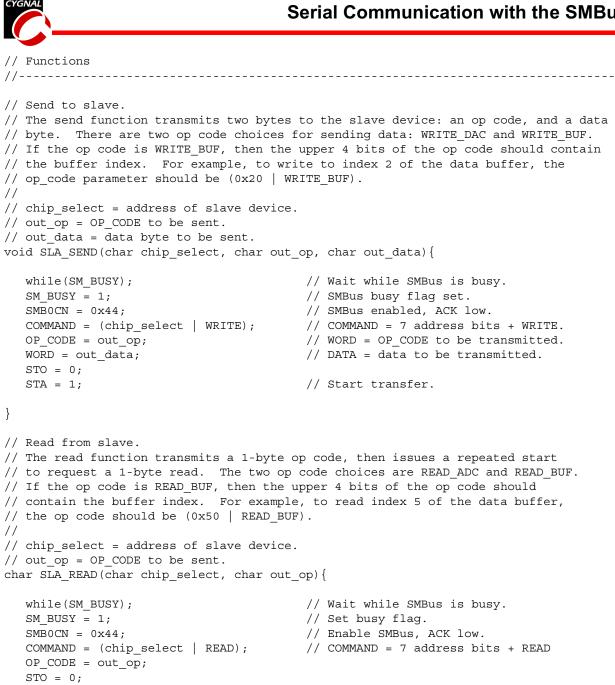

The final example features two C8051F0xx devices configured to communicate as peers. The peer-to-peer interface uses a set of op codes to perform the set of tasks below. Either device may initiate a transfer.

Write to slave DAC: The master device sends a WRITE\_DAC op code followed by a byte of data. Upon receipt, the slave device writes the data to its DAC0 port.

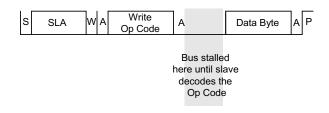

Write to buffer: The master device sends a WRITE\_BUF op code, followed by a byte of data for the receiving device to store in a buffer. The upper 4 bits of the WRITE\_BUF op code hold the buffer index. Figure 10 shows a peer-to-peer WRITE sequence (same for both DAC and buffer writes).

#### Figure 10. Peer-to-Peer Write Sequence

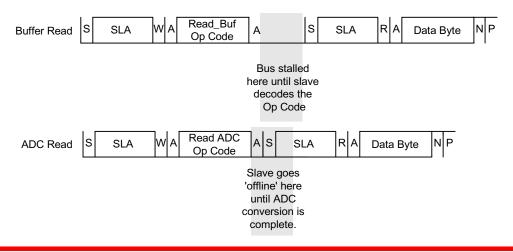

Read ADC: The master device sends a READ ADC op code followed by a repeated START. The slave reads its ADC input, and places the data in its SMB0DAT register. In this case, the slave clears AA to go 'offline' during the ADC conversion. While the slave is offline, the master receives a NACK after the repeated START and slave address. The master continues acknowledge polling until the slave responds. This technique is useful if the slave's operation is time-consuming, since other devices may use the bus while the slave is offline. The slave sets AA=1 when it is ready, and the transfer continues. The master requests a READ after the slave acknowledges. See Figure 11 for the transmission sequence.

**Read buffer:** The master sends a READ\_BUF op code followed by a repeated START. The upper 4 bits of the op code hold the buffer index. In this case the slave holds the SCL line low while it decodes the op code. While SCL is held low, the master cannot attempt to continue the transfer. Additionally, no other masters on the bus may attempt a transfer. This bus stalling technique is useful when the slave's delay is short. The slave releases SCL when it has finished decoding the op code and is ready to transmit the data. The master issues the repeated START and the slave address + R. See Figure 11.

#### Figure 11. Peer-to-Peer Read Sequence

The SMBus operation in this example is defined as a case-switch statement in the SMBus ISR. All possible states are defined, including the arbitration states. If arbitration occurs, the losing device stores its current transfer data (target slave address, op code, relevant data) and responds to the received op code. After the transfer is finished, the losing device retries the transfer by reverting to the saved transfer data.

An OP\_CODE\_HANDLER function runs in polled mode to process received data. When the device receives a valid op code, the OP\_CODE\_HANDLER decodes it and reacts appropriately.

To test the bus, comment out the OP\_CODE\_HANDLER call in the code for CHIP\_A. This will allow CHIP\_A to run the provided test code. Note that the constant MY\_ADD must be unique to each device on the bus.

The code listing for this example begins on page 29.

| Mode               | Status<br>Code                                     | SMBus State                                   | Typical Action                                                                                                                   |  |  |

|--------------------|----------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| μĸ                 | 0x08                                               | START condition transmitted.                  | Load SMB0DAT with Slave Address +<br>R/W                                                                                         |  |  |

| MT/<br>MR          | 0x10 Repeated START condition transmitted.         |                                               | Load SMB0DAT with Slave Address + R/W                                                                                            |  |  |

|                    | 0x18                                               | Slave Address + W transmitted. ACK received.  | Load SMB0DAT with data to be transmit-<br>ted. Clear STA                                                                         |  |  |

| mitter             | 0x20 Slave Address + W transmitted. NACK received. |                                               | Acknowledge poll to retry. Set STO + STA                                                                                         |  |  |

| Master Transmitter | 0x28 Data byte transmitted. ACK received.          |                                               | <ol> <li>Load SMB0DAT with next byte, OR</li> <li>Set STO, OR</li> <li>Clear STO, then set STA for repeated<br/>START</li> </ol> |  |  |

| Mas                | 0x30                                               | Data byte transmitted. NACK received.         | 1) Retry transfer OR<br>2) Set STO                                                                                               |  |  |

|                    | 0x38                                               | Arbitration Lost.                             | Save current data                                                                                                                |  |  |

| er                 | 0x40                                               | Slave Address + R transmitted. ACK received.  | Clear STA. Wait for received data.                                                                                               |  |  |

| Receiv             | 0x48                                               | Slave Address + R transmitted. NACK received. | Acknowledge poll to retry. Set STO + STA                                                                                         |  |  |

| Master Receiver    | 0x50                                               | Data byte received. ACK transmitted.          | Read SMB0DAT. Wait for next byte. If next byte is last byte, clear AA                                                            |  |  |

| Ma                 | 0x58                                               | Data byte received. NACK transmitted.         | Set STO                                                                                                                          |  |  |

#### Table 1. SMBus Status Codes and States

Table 1. SMBus Status Codes and States

| Mode              | Status<br>Code                                                          | SMBus State                                                                                                | Typical Action                                                                    |  |

|-------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

|                   | 0x60                                                                    | Own slave address + W received. ACK trans-<br>mitted.                                                      | Wait for data                                                                     |  |

|                   | 0x68                                                                    | Arbitration lost in sending SLA + R/W as mas-<br>ter. Own address + W received. ACK transmit-<br>ted.      | Save current data for retry when bus is free. Wait for data                       |  |

| <b>_</b>          | 0x70                                                                    | General call address received. ACK transmit-<br>ted.                                                       | Wait for data                                                                     |  |

| Slave Receiver    | 0x78                                                                    | Arbitration lost in sending SLA + R/W as mas-<br>ter. General call address received. ACK trans-<br>mitted. | Save current data for retry when bus is free.                                     |  |

| Slave             | 0x80                                                                    | Data byte received. ACK transmitted.                                                                       | Read SMB0DAT. Wait for next byte or STOP                                          |  |

| 0)                | 0x88                                                                    | Data byte received. NACK transmitted.                                                                      | Set STO to reset SMBus                                                            |  |

|                   | 0x90 Data byte received after general call address.<br>ACK transmitted. |                                                                                                            | Read SMB0DAT. Wait for next byte or STOP                                          |  |

|                   | 0x98                                                                    | Data byte received after general call address.<br>NACK transmitted.                                        | Set STO to reset SMBus                                                            |  |

|                   | 0xA0                                                                    | STOP or repeated START received.                                                                           | No action necessary                                                               |  |

|                   | 0xA8                                                                    | Own address + R received. ACK transmitted.                                                                 | Load SMB0DAT with data to transmit.                                               |  |

| Slave Transmitter | 0xB0                                                                    | Arbitration lost in transmitting SLA + R/W as<br>master. Own address + R received. ACK<br>transmitted.     | Save current data for retry when bus is free. Load SMB0DAT with data to transmit. |  |

| Tra               | 0xB8                                                                    | Data byte transmitted. ACK received.                                                                       | Load SMB0DAT with data to transmit.                                               |  |

| ave               | 0xC0                                                                    | Data byte transmitted. NACK received.                                                                      | Wait for STOP                                                                     |  |

| S                 | 0xC8                                                                    | Last data byte transmitted (AA=0). ACK received.                                                           | Set STO to reset SMBus                                                            |  |

| Slave             | 0xD0 SCL Clock High Timer per SMB0CR timed out                          |                                                                                                            | Set STO to reset SMBus                                                            |  |

| _                 | 0x00                                                                    | Bus Error (illegal START or STOP)                                                                          | Set STO to reset SMBus                                                            |  |

| All               | 0xF8                                                                    | ldle                                                                                                       | State does not set SI                                                             |  |

# Software Examples for the C8051F00x and C8051F01x series

```

_____

; -

; Copyright 2001 Cygnal Integrated Products, Inc.

; Program: SMBus EX1.asm

; Created on: 2/21/01

; Created by: JS

; Example code to interface a single 256-byte EEPROM to a C8051F00x via the SMBus

; Code assumes a single EEPROM with slave address 1010000 is connected on

; the SDA and SCL lines, and no other masters are on the bus.

; The SEND routine performs a 1-byte write to the EEPROM. This consists of (1) START,

; (2) slave address + W, (3) memory location byte write, and (4) a data byte write.

; STEPS FOR WRITING TO EEPROM:

1) Load slave address into SLA ADD

2) Load memory address into MEM_ADD

3) Load data byte into TRANSMIT BYTE.

4) Call SEND

; The RECEIVE routine performs a 1-byte read from the EEPROM. This consists of (1)

; START, (2) slave address + W, (3) memory location byte write, (4) repeated START,

; (5) slave address + R, (6) data byte read.

; STEPS FOR RECEIVING DATA:

1) Load slave address into SLA ADD

:

2) Load memory address into MEM ADD

3) Call RECEIVE

4) Read RECEIVE_BYTE

; The SMBus state table is broken into 8-byte state segments, allowing the SMBus

; status code (SMB0STA) to be used as a state index. Note that this leaves only

; 8 bytes of code space per SMBus state definition. As a result, certain tasks

; have been altered to limit state definition lengths:

; 1) The SMB_MTDBACK state (Master transmitter, data byte sent, ACK received) is

; reduced to a bit-check and branch operation. The branch is outside of the state

; table, so that a larger code segment may be executed for this state.

; 2) Three data bytes are used for slave address storage: SLA_ADD, WRI_ADD, READ_ADD.

; Rather than using bit-wise operations in the SMBus states, each transfer routine

; pre-loads the address values. Since a RECEIVE includes both a WRITE and READ

; transfer, two address bytes are necessary - WRI ADD and READ ADD. SLA ADD is used

; as a generic slave chip select before a function call.

; Note that SLA_ADD is equivalent to WRI_ADD, since WRI_ADD = SLA_ADD + W (W=0).

; The two are left separate to clarify the demonstration.

```

; -

\_\_\_\_\_

; EQUATES

| \$include (c8051f000.inc)                                                                                                                                                                                |                                                               | inc)                                                     | ; Include register definition file.     |                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITE                                                                                                                                                                                                    | EQU                                                           | 00h                                                      | ;                                       | SMBus WRITE command                                                                                                                                                                                                                                                                          |

| READ                                                                                                                                                                                                     | EQU                                                           | 01h                                                      | ;                                       | SMBus READ command                                                                                                                                                                                                                                                                           |

| CHIP_A                                                                                                                                                                                                   | EQU                                                           | 0A0h                                                     | ;                                       | EEPROM slave address                                                                                                                                                                                                                                                                         |

| ; SMBus States                                                                                                                                                                                           |                                                               |                                                          |                                         |                                                                                                                                                                                                                                                                                              |

| SMB_BUS_ERROR                                                                                                                                                                                            | EQU                                                           | 00h                                                      |                                         | (all modes) BUS ERROR                                                                                                                                                                                                                                                                        |

| SMB_START                                                                                                                                                                                                | EQU                                                           | 08h                                                      |                                         | (MT & MR) START transmitted                                                                                                                                                                                                                                                                  |

| SMB_RP_START                                                                                                                                                                                             | EQU                                                           | 10h                                                      |                                         | (MT & MR) repeated START                                                                                                                                                                                                                                                                     |

| SMB_MTADDACK                                                                                                                                                                                             | EQU                                                           | 18h                                                      |                                         | (MT) Slave address + W transmitted;                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |                                                               |                                                          | ;                                       | ACK received                                                                                                                                                                                                                                                                                 |

| SMB_MTADDNACK                                                                                                                                                                                            | EQU                                                           | 20h                                                      | ;                                       | (MT) Slave address + W transmitted;                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |                                                               |                                                          | ;                                       | NACK received                                                                                                                                                                                                                                                                                |

| SMB_MTDBACK                                                                                                                                                                                              | EQU                                                           | 28h                                                      | ;                                       | (MT) data byte transmitted; ACK rec'vd                                                                                                                                                                                                                                                       |

| SMB_MTDBNACK                                                                                                                                                                                             | EQU                                                           | 30h                                                      |                                         | (MT) data byte transmitted; NACK rec'vd                                                                                                                                                                                                                                                      |

| SMB_MTARBLOST                                                                                                                                                                                            | EQU                                                           | 38h                                                      | ;                                       | (MT) arbitration lost                                                                                                                                                                                                                                                                        |

| SMB_MRADDACK                                                                                                                                                                                             | EQU                                                           | 40h                                                      | ;                                       | (MR) Slave address + R transmitted;                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |                                                               |                                                          | ;                                       | ACK received                                                                                                                                                                                                                                                                                 |

| SMB_MRADDNACK                                                                                                                                                                                            | EQU                                                           | 48h                                                      | ;                                       | (MR) Slave address + R transmitted;                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |                                                               |                                                          | ;                                       | NACK received                                                                                                                                                                                                                                                                                |

| SMB_MRDBACK                                                                                                                                                                                              | EQU                                                           | 50h                                                      | ;                                       | (MR) data byte rec'vd; ACK transmitted                                                                                                                                                                                                                                                       |

| SMB_MRDBNACK                                                                                                                                                                                             |                                                               | 58h                                                      |                                         | (MR) data byte rec'vd; NACK transmitted                                                                                                                                                                                                                                                      |

| ARIABLES                                                                                                                                                                                                 |                                                               |                                                          |                                         |                                                                                                                                                                                                                                                                                              |

| ARIABLES                                                                                                                                                                                                 |                                                               |                                                          |                                         |                                                                                                                                                                                                                                                                                              |

| ARIABLES<br>G                                                                                                                                                                                            |                                                               |                                                          |                                         |                                                                                                                                                                                                                                                                                              |

| ARIABLES<br>G                                                                                                                                                                                            |                                                               |                                                          |                                         |                                                                                                                                                                                                                                                                                              |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:                                                                                                                                                               | DS                                                            | 1                                                        | ;                                       | Holds a byte to be transmitted by the SMBu                                                                                                                                                                                                                                                   |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:                                                                                                                                                               | DS                                                            | 1                                                        | ;                                       | -                                                                                                                                                                                                                                                                                            |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:                                                                                                                                              | DS                                                            | 1                                                        | ;;                                      | Holds a byte to be transmitted by the SMBu                                                                                                                                                                                                                                                   |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:                                                                                                                                  | DS<br>DS                                                      | 1<br>1                                                   | ;;;;                                    | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE                                                                                                                                          |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:                                                                                                                      | DS<br>DS<br>DS                                                | 1<br>1<br>1                                              | ;;;;                                    | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address                                                                                                                                                                             |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>READ_ADD:                                                                                                         | DS<br>DS<br>DS<br>DS<br>DS                                    | 1<br>1<br>1<br>1                                         | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE                                                                                                                                          |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>READ_ADD:                                                                                                         | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS                  | 1<br>1<br>1<br>1<br>1<br>1                               | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ                                                                                                        |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>READ_ADD:<br>MEM_ADD:<br>; Variables us                                                                           | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS                  | 1<br>1<br>1<br>1<br>1<br>1                               | ;;;;;                                   | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ                                                                                                        |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>READ_ADD:<br>MEM_ADD:<br>; Variables us<br>TEST_COUNT:                                                            | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>Sed for             | 1<br>1<br>1<br>1<br>1<br>1<br>1                          | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ<br>EEPROM memory location to be accessed                                                               |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>WRI_ADD:<br>MEM_ADD:<br>; Variables us<br>TEST_COUNT:<br>TEST_CUNT:                                               | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>Sed for<br>DS             | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1      | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ<br>EEPROM memory location to be accessed<br>Test counter variable                                      |

| ARIABLES<br>G<br>Org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>READ_ADD:<br>MEM_ADD:<br>; Variables us<br>TEST_COUNT:<br>TEST_COUNT:<br>TEST_BYTE:<br>TEST_ADDR:                 | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>Sed for<br>DS<br>DS       | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ<br>EEPROM memory location to be accessed<br>Test counter variable<br>Test data                         |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>READ_ADD:<br>MEM_ADD:<br>; Variables us<br>TEST_COUNT:<br>TEST_BYTE:<br>TEST_ADDR:<br>G                           | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>Sed for<br>DS<br>DS       | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ<br>EEPROM memory location to be accessed<br>Test counter variable<br>Test data                         |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>READ_ADD:<br>MEM_ADD:<br>; Variables us<br>TEST_COUNT:<br>TEST_COUNT:<br>TEST_BYTE:<br>TEST_ADDR:<br>G<br>org 00h | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>Sed for<br>DS<br>DS       | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ<br>EEPROM memory location to be accessed<br>Test counter variable<br>Test data                         |

| ARIABLES<br>G<br>org 30h<br>TRANSMIT_BYTE:<br>RECEIVE_BYTE:<br>SLA_ADD:<br>WRI_ADD:<br>WRI_ADD:<br>KEAD_ADD:<br>MEM_ADD:<br>; Variables us<br>TEST_COUNT:<br>TEST_BYTE:<br>TEST_ADDR:<br>G               | DS<br>DS<br>DS<br>DS<br>DS<br>DS<br>Sed for<br>DS<br>DS<br>DS | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1      | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Holds a byte to be transmitted by the SMBu<br>Holds a byte just received by the SMBus<br>Holds the slave address<br>Holds the slave address + WRITE<br>Holds the slave address + READ<br>EEPROM memory location to be accessed<br>Test counter variable<br>Test data<br>Test memory location |

1: EEPROM memory address sent ; 0: Data byte sent ; ;------; RESET and INTERRUPT VECTORS ;------CSEG ; Reset Vector org 00h ljmp Reset ISR ; SMBus Interrupt Vector org 03Bh ljmp SMBus\_ISR ;------; MAIN PROGRAM MAIN: acall SMBus Init ; Initialize SMBus setb EA ; Enable global interrupts mov TEST BYTE, #0ffh ; mov TEST ADDR, #00h ; Load initial test values mov TEST COUNT, #0feh ; ; TEST CODE-----TEST: ; Send TEST BYTE to memory location TEST ADDR mov SLA ADD, #CHIP A ; Load slave address movTRANSMIT\_BYTE, TEST\_BYTE; Load transmit data into TRANSMIT\_BYTEmovMEM\_ADD, TEST\_ADDR; Load memory address into MEM\_ADD acall SEND ; Call send routine ; Read memory location TEST ADDR into RECEIVE BYTE mov SLA\_ADD, #CHIP\_A ; Load slave address mov MEM\_ADD, TEST\_ADDR ; Load memory address into MEM\_ADD acall RECEIVE ; Call receive routine ; Compare byte received to byte sent mov A, RECEIVE\_BYTE ; Load received byte into accumulator ; Compare sent byte to received byte cjne A, TEST\_BYTE, END\_TEST ; Jump to END\_TEST if not equal ; Change test variables ; If sent=received, change test variables dec TEST BYTE inc TEST\_ADDR ; and cycle through again. ; Cycle through again if TEST\_COUNTER not zero

A, #99h ; Load accumulator with 99h if test successful. mov END\_TEST: jmp \$ ; Spin ;-----\_\_\_\_\_ ; SUBROUTINES ;------ -;------; SEND subroutine. Assumes that the slave address, memory location, and transmit ; data have all been loaded into their associated variables. This routine manages ; the SM\_BUSY bit, sets RW=WRITE, loads the WRI\_ADD, and initiates the transfer. ; SEND: push ACC ; Preserve accumulator jb SM\_BUSY, \$ ; Wait for SMBus to be free clr RW ; RW = 0 (WRITE) A, SLA ADD ; Store SLA ADD + WRITE mov A, #WRITE ; in WRI\_ADD orl WRI ADD, A mov ; setb SM BUSY ; Occupy SMBus setb STA ; Initiate Transfer ACC ; Restore accumulator рор ret ; RECEIVE subroutine. Assumes that the slave address and memory location have been ; loaded into their associated variables. This routine manages the SM\_BUSY bit, sets ; RW=READ, loads the READ ADD and WRI ADD, and initiates the transfer. ; Note that the RECEIVE transfer consists of a WRITE of the memory location to be accessed, ; followed by a repeated START and a READ operation. Therefore, both WRI ADD ; and READ\_ADD are used by this routine. RECEIVE: push ACC ; Preserve accumulator jb SM BUSY, \$ ; Wait for SMBus to be free ; RW = 1 (READ) setb RW mov A, SLA ADD ; Store SLA\_ADD + WRITE ; in WRITE ADD A, #WRITE orl WRI\_ADD, A mov ; A, SLA\_ADD ; Store SLA\_ADD + READ mov A, #READ ; in READ\_ADD orl mov READ ADD, A ;

```

setb SM BUSY

; Occupy SMBus

setb STA

; Initiate Transfer

SM_BUSY, $

jb

; Wait for receive to finish

ACC

; Restore accumulator

рор

ret

;------

- -

; SMBus Init

; SMbus initialization routine

;

; - Configures and enables the SMBus.

; - Sets SMBus clock rate.

; - Enables SMBus interrupt.

; - Clears SM_Busy flag for first transfer.

SMBus Init:

; Configure SMBus to send ACKs on acknowledge cycle

SMBOCN, #04h

mov

; SMBus clock rate = 100KHz, per SMB0CR equation:

mov SMB0CR, #0B0h

; SMB0CR = -(SYSCLK)/(2*Fscl)

orl SMB0CN, #40h

; Enable SMBus

orl

EIE1, #02h

; Enable SMBus interrupts

clr SM BUSY

ret

; INTERRUPT VECTORS

;------

; Reset Interrupt Service Routine

; - Disables Watchdog Timer

; - Routes SDA and SCL to GPIO pins via the crossbar

; - Enables crossbar

; - Jumps to MAIN

Reset_ISR:

WDTCN, #0DEh

; Disable Watchdog Timer

mov

WDTCN, #0ADh

mov

```

```

; Set internal oscillator to highest setting ; (16 MHz)

```

orl OSCICN, #03h

```

clr

STA

; Manually clear START bit

SMB_ISR_END

; Jump to exit ISR

jmp

; SMB_RP_START

; Master Transmitter/Receiver: Repeated START transmitted.

; This state should only occur during a read, after the memory

; address has been sent and acknowledged.

SMB_STATE_TABLE + SMB_RP_START

orq

SMBODAT, READ_ADD

; Load slave address + R

mov

clr

STA

; Manually clear START bit

SMB ISR END

jmp

; SMB_MTADDACK

; Master Transmitter: Slave address + WRITE transmitted.

; ACK received

org SMB STATE TABLE + SMB MTADDACK

SMBODAT, MEM ADD

; Load memory address

mov

setb BYTE SENT

; BYTE_SENT=1: In the next ISR call,

; the memory address will have just been

; sent.

SMB ISR END

jmp

; SMB MTADDNACK

; Master Transmitter: Slave address + WRITE transmitted.

; NACK received. The slave is not responding. Try again with

; acknowledge polling. Send STOP + START.

org SMB_STATE_TABLE + SMB_MTADDNACK

setb STO

setb STA

jmp SMB ISR END

; SMB MTDBACK

; Master Transmitter: Data byte transmitted. ACK received.

; This state is used in both read and write operations.

; Check BYTE_SENT; if 1, memory address has just been sent. Else,

; data has been sent.

SMB STATE TABLE + SMB MTDBACK

orq

BYTE SENT, ADDRESS SENT

; If BYTE SENT=1, clear bit and

jbc

; jump to ADDRESS SENT to process

; outside of state table.

jmp

DATA SENT

; If BYTE_SENT=0, data has just been sent,

; transfer is finished.

; jump to end transfer

; SMB MTDBNACK

; Master Transmitter: Data byte transmitted. NACK received.

; Slave not responding. Send STOP followed by START to try again.

org SMB STATE TABLE + SMB MTDBNACK

setb STO

setb STA

```

```

SMB_ISR_END

jmp

; SMB MTARBLOST

; Master Transmitter: Arbitration Lost.

; Should not occur. If so, restart transfer.

org SMB STATE TABLE + SMB MTARBLOST

setb STO

setb STA

SMB_ISR_END

jmp

; SMB MRADDACK

; Master Receiver: Slave address + READ transmitted. ACK received.

; Set to transmit NACK after next transfer since it will be the

; last (only) byte.

org SMB_STATE_TABLE + SMB_MRADDACK

clr

AA

; NACK sent on acknowledge cycle

jmp

SMB ISR END

; SMB MRADDNACK

; Master Receiver: Slave address + READ transmitted. NACK received.

; Slave not responding. Send repeated START to try again.

org SMB STATE TABLE + SMB MRADDNACK

clr

STO

setb STA

jmp

SMB ISR END

; SMB MRDBACK

; Master Receiver: Data byte received. ACK transmitted.

; Should not occur because AA is cleared in previous state.

; Send STOP if state does occur.

org SMB STATE TABLE + SMB MRDBACK

setb STO

SMB ISR END

jmp

; SMB MRDBNACK

; Master Receiver: Data byte received. NACK transmitted.

; Read operation completed. Read data register and send STOP

org SMB STATE TABLE + SMB MRDBNACK

RECEIVE_BYTE, SMB0DAT

mov

setb STO

setb AA

; Set AA for next transfer

clr

SM BUSY

jmp

SMB ISR END

; End of State Table------

;-----

; Program segment to handle SMBus states that require more than 8 bytes of program

; space.

; Address byte has just been sent. Check RW. If R (1), jump to RW_READ.

; If W, load data to transmit into SMB0DAT.

```

CYGNAL

ADDRESS\_SENT:

jb RW, RW\_READ SMB0DAT, TRANSMIT\_BYTE ; Load data mov SMB\_ISR\_END jmp ; Jump to exit ISR ; Operation is a READ, and the address byte has just been sent. Send ; repeated START to initiate memory read. RW\_READ: clr STO setb STA ; Send repeated START jmp SMB\_ISR\_END ; Jump to exit ISR ; Operation is a WRITE, and the data byte has just been sent. Transfer ; is finished. Send STOP, free the bus, and exit the ISR. DATA\_SENT: ; Send STOP and exit ISR. setb STO clr SM\_BUSY ; Free SMBus jmp SMB ISR END ; Jump to exit ISR ;-----; SMBus ISR exit. ; Restore registers, clear SI bit, and return from interrupt. SMB\_ISR\_END: clr SI pop ACC рор DPL pop DPH pop ACC pop PSW reti END

```

11

// Copyright 2001 Cygnal Integrated Products, Inc.

11

// FILE NAME

: SMB_Ex2.c

// TARGET DEVICE : C8051F000

: 2/20/01

// CREATED ON

// CREATED BY

: JS

11

11

// Example code for interfacing a C8051F0xx to three EEPROMs via the SMBus.

// Code assumes that three 16-bit address space EEPROMs are connected

// on the SCL and SDA lines, and configured so that their slave addresses

// are as follows:

// CHIP A = 1010000

// CHIP_B = 1010001

// CHIP C = 1010010

11

// Slave and arbitration states are not defined. Assume the CF000 is the only

// master in the system.

// Functions: SM Send performs a 1-byte write to the specified EEPROM

// SM Receive performs a 1-byte read of the specified EEPROM address (both include

// memory address references).

11

// Includes test code section.

//-----

// Includes

//-----

#include <c8051f000.h>

// SFR declarations

//-----

// Global CONSTANTS

//-----

#define WRITE 0x00

// SMBus WRITE command

#define READ 0x01

// SMBus READ command

// Device addresses (7 bits, lsb is a don't care)

// Device address for chip A

#define CHIP A 0xA0

// Device address for chip B

#define CHIP B 0xA2

#define CHIP C 0xA4

// Device address for chip C

// SMBus states:

// MT = Master Transmitter

// MR = Master Receiver

// (all modes) BUS ERROR

#define SMB BUS ERROR 0x00

// (MT & MR) START transmitted

#define SMB START

0x08

#define SMB_RP_START

// (MT & MR) repeated START

0x10

#define SMB_MTADDACK 0x18

// (MT) Slave address + W transmitted;

// ACK received

// (MT) Slave address + W transmitted;

#define SMB MTADDNACK 0x20

// NACK received

#define SMB_MTDBACK

// (MT) data byte transmitted; ACK rec'vd

0x28

#define SMB_MTDBNACK 0x30

// (MT) data byte transmitted; NACK rec'vd

#define SMB_MTARBLOST 0x38

// (MT) arbitration lost

#define SMB MRADDACK 0x40

// (MR) Slave address + R transmitted;

```

// ACK received #define SMB\_MRADDNACK 0x48 // (MR) Slave address + R transmitted; // NACK received #define SMB\_MRDBACK // (MR) data byte rec'vd; ACK transmitted 0x50 // (MR) data byte rec'vd; NACK transmitted #define SMB\_MRDBNACK 0x58 //-----//Global VARIABLES //-----// Holds the slave address + R/W bit for char COMMAND; // use in the SMBus ISR. char WORD; // Holds data to be transmitted by the SMBus // OR data that has just been received. char BYTE NUMBER; // Used by ISR to check what data has just been // sent - High address byte, Low byte, or data // byte unsigned char HIGH ADD, LOW ADD; // High & Low byte for EEPROM memory address // This bit is set when a send or receive bit SM BUSY; // is started. It is cleared by the // ISR when the operation is finished. //-----// Function PROTOTYPES //----void SMBus ISR (void); void SM Send (char chip select, unsigned int byte address, char out byte); char SM Receive (char chip select, unsigned int byte address); //-----// MAIN Routine //-----11 // Main routine configures the crossbar and SMBus, and tests // the SMBus interface between the three EEPROMs void main (void) { unsigned char check; // Used for testing purposes WDTCN = 0xde;// disable watchdog timer WDTCN = 0xad;OSCICN  $| = 0 \times 03;$ // Set internal oscillator to highest setting // (16 MHz) // Route SMBus to GPIO pins through crossbar XBR0 = 0x01;XBR2 = 0x40;// Enable crossbar and weak pull-ups SMBOCN = 0x44;// Enable SMBus with ACKs on acknowledge // cycle // SMBus clock rate = 100kHz. SMB0CR = -80;

```

EIE1 |= 2;

// SMBus interrupt enable

EA = 1;

// Global interrupt enable

// Free SMBus for first transfer.

SM_BUSY = 0;

SM_Send(CHIP_C, 0x0010, 0x77);

SM Send(CHIP B, 0x0333, 0xF0);

SM_Send(CHIP_A, 0x0242, 0xF0);

check = SM Receive(CHIP A, 0x0088); // Read address 0x88 on CHIP A

check = SM_Receive(CHIP_B, 0x0001); // Read address 0x01 on CHIP_B

check = SM Receive(CHIP C, 0x0010);

check = SM Receive(CHIP B, 0x0333);

check = SM Receive(CHIP_A, 0x0242);

}

// SMBus byte write function------

// Writes a single byte at the specified memory location.

11

// out byte = data byte to be written

// byte address = memory location to be written into (2 bytes)

// chip select = device address of EEPROM chip to be written to

void SM Send (char chip select, unsigned int byte address, char out byte)

while (SM BUSY);

// Wait for SMBus to be free.

SM BUSY = 1;

// Occupy SMBus (set to busy)

SMBOCN = 0x44;

// SMBus enabled,

// ACK on acknowledge cycle

BYTE NUMBER = 2;

// 2 address bytes.

COMMAND = (chip_select | WRITE);

// Chip select + WRITE

HIGH ADD = ((byte address >> 8) & 0x00FF);// Upper 8 address bits

LOW ADD = (byte address & 0x00FF);

// Lower 8 address bits

WORD = out_byte;

// Data to be writen

STO = 0;

STA = 1;

// Start transfer

}

// SMBus random read function------

// Reads 1 byte from the specified memory location.

11

// byte address = memory address of byte to read

// chip select = device address of EEPROM to be read from

char SM_Receive (char chip_select, unsigned int byte_address)

{

```

```

while (SM_BUSY);

// Wait for bus to be free.

SM BUSY = 1;

// Occupy SMBus (set to busy)

SMBOCN = 0x44;

// SMBus enabled, ACK on acknowledge cycle

// 2 address bytes

BYTE NUMBER = 2;

COMMAND = (chip select | READ);

// Chip select + READ

HIGH_ADD = ((byte_address >> 8) & 0x00FF);// Upper 8 address bits

LOW_ADD = (byte_address & 0x00FF); // Lower 8 address bits

STO = 0;

STA = 1;

// Start transfer

while (SM BUSY);

// Wait for transfer to finish

return WORD;

}

//-----

// Interrupt Service Routine

//-----

// SMBus interrupt service routine:

void SMBUS_ISR (void) interrupt 7

switch (SMB0STA) {

// Status code for the SMBus (SMB0STA register)

// Master Transmitter/Receiver: START condition transmitted.

// The R/W bit of the COMMAND word sent after this state will

// always be a zero (W) because for both read and write,

// the memory address must be written first.

case SMB START:

SMB0DAT = (COMMAND & 0xFE); // Load address of the slave to be accessed.

STA = 0;

// Manually clear START bit

break;

// Master Transmitter/Receiver: Repeated START condition transmitted.

// This state should only occur during a read, after the memory address has been

// sent and acknowledged.

case SMB RP START:

SMB0DAT = COMMAND;

// COMMAND should hold slave address + R.

STA = 0;

break;

// Master Transmitter: Slave address + WRITE transmitted. ACK received.

case SMB MTADDACK:

SMB0DAT = HIGH ADD;

// Load high byte of memory address

// to be written.

break;

// Master Transmitter: Slave address + WRITE transmitted. NACK received.

// The slave is not responding. Send a STOP followed by a START to try again.

case SMB MTADDNACK:

STO = 1;

STA = 1;

break;

```

```

// Master Transmitter: Data byte transmitted. ACK received.

// This state is used in both READ and WRITE operations. Check BYTE_NUMBER

// for memory address status - if only HIGH_ADD has been sent, load LOW_ADD.

// If LOW_ADD has been sent, check COMMAND for R/W value to determine

// next state.

case SMB MTDBACK:

switch (BYTE NUMBER) {

// If BYTE_NUMBER=2, only HIGH_ADD

case 2:

SMB0DAT = LOW_ADD;

// has been sent.

// Decrement for next time around.

BYTE_NUMBER--;

break;

case 1:

// If BYTE_NUMBER=1, LOW_ADD was just sent.

if (COMMAND & 0x01) { // If R/W=READ, sent repeated START.

STO = 0;

STA = 1;

} else {

// If R/W=WRITE, load byte to write.

SMB0DAT = WORD;

BYTE NUMBER--;

}

break;

// If BYTE NUMBER=0, transfer is finished.

default:

STO = 1;

SM BUSY = 0;

// Free SMBus

}

break;

// Master Transmitter: Data byte transmitted. NACK received.

// Slave not responding. Send STOP followed by START to try again.

case SMB MTDBNACK:

STO = 1;

STA = 1;

break;

// Master Transmitter: Arbitration lost.

// Should not occur. If so, restart transfer.

case SMB MTARBLOST:

STO = 1;

STA = 1;

break;

// Master Receiver: Slave address + READ transmitted. ACK received.

// Set to transmit NACK after next transfer since it will be the last (only)

// byte.

case SMB MRADDACK:

AA = 0;

// NACK sent on acknowledge cycle.

break;

// Master Receiver: Slave address + READ transmitted. NACK received.

// Slave not responding. Send repeated start to try again.

case SMB MRADDNACK:

STO = 0;

STA = 1;

break;

```

```

// Data byte received. ACK transmitted.

// State should not occur because AA is set to zero in previous state.

// Send STOP if state does occur.

case SMB_MRDBACK:

STO = 1;

SM_BUSY = 0;

break;

// Data byte received. NACK transmitted.

// Read operation has completed. Read data register and send STOP.

case SMB_MRDBNACK:

WORD = SMB0DAT;

STO = 1;

SM_BUSY = 0;

// Free SMBus

break;

// All other status codes meaningless in this application. Reset communication.

default:

STO = 1;